差分对的约束设置

第一步,差分对的设置

差分对的设置有很多方法,下面介绍两种最常用的方法。

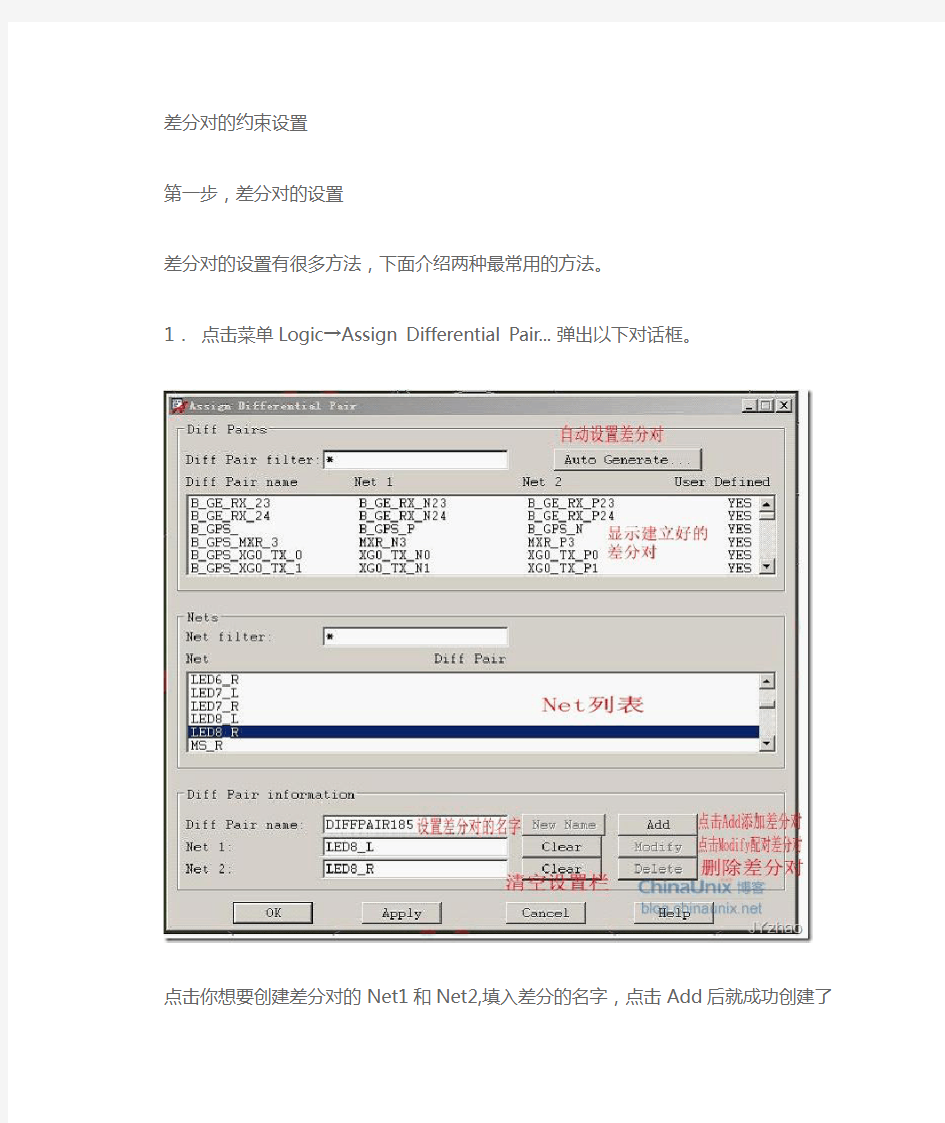

1.点击菜单Logic→Assign Differential Pair... 弹出以下对话框。

点击你想要创建差分对的Net1和Net2,填入差分的名字,点击Add后就成功创建了差分对。

点击Auto Generate按钮后,弹出以下对话框:

在第一个输入框填入Net的主要名字后,在下面的框中填入差分线的标志如N,P。点击Generate即可自动产生差分对。

2.在约束管理器中设置差分对。

在DSN上点击右键,在菜单中选择Create→Differential Pair。即可弹出下面的对话框。

和上一种方法的设置差不多,这里就不再叙述了。

第二步差分对约束规则的设置

差分对各项约束可以在约束管理器中的

Electric→Net→routing→Differential Pair中直接在各差分对上填入各项约束数值就可生效,但更好的方法是创建约束规则后赋给各个差分对。

在DSN上点击右键,在菜单中选择Create→Electrical CSet后,弹出下面的对话框;

输入规则名后点Ok,在Electric→constraimt set→outing→Differential Pair中可以看到新规则。

在表格中输入各项数值即可完成新规则的设置。如图所示

差分对约束参数主要有以下几个:

1coupling paramaters 主要包括了

Primary Gap 差分对最优先线间距(边到边间距)。

Primary Width 差分对最优先线宽。

Neck Gap 差分对Neck模式下的线间距(边到边间距),用于差分对走线在布线密集区域时切换到Neck值。

Neck Width差分对Neck模式下的线宽,用于差分对走线在布线密集区域时切换到Neck值。如图所示

设置数值时在表格中右键菜单中选择change,会出现以下各层数值表格,可以在每一层上设置不同的数值。

需要注意的是在物理(physical)约束中同样可以设置差分规则,但是电气规则约束在布线时更优先,同时电气规则可以设置更多的约束,推荐在电气规则中设置差分走线的约束。

2 Min Line Specing 差分对最小间距,一定要小于或等于"Primary gap"与(-)tolerance的数值,并且也要小于或等于"Neck gap"与(-)tolerance的数值。对于不符合约束的差分对,会显示“DS”的DRC错误提示。

3 Dynamic Phase:动态相位检查,在16.3版本新加入的功能。对差分对路径中每个转角之间造成的路径差异进行检查。如在整个差分对网络中,正向与反向之间的走线差距不能超过“x mils”。如果整个路径中的某一个位置,发生了两个信号之间相位偏移超过了规定的“x mils”,这个误差必须在“y mils”范围内

补偿回来。如下图x=20,y=600.设定约束时tolerance填入x值,max length 填入y值。

对于不符合约束的走线的路径会以高亮显现,并且显示DY错误。

4 Static Phase Tolerance 这个约束设置了两根差分线之间的差值,单位是mil或ns。

设置了此项后,在走线时会实时的显示走线差,在绿灯时符合约束。如图

在Net→routing→Differential Pair中也可以看到实际的值。

需要注意的是布线时“SPhase”显示的是裕量值(Margin),而并非实际值(Actual)。

裕量值的范围

如图所示在-∞到+-公差区间内,实际线长比目标线长要短,裕量值为实际值—目标值+公差。绿灯0意为实际值比目标值少公差值长,+裕量值越大意为实际线长越接近目标线长。

在+∞到+-公差区间内,实际线长比目标线长要长,裕量值为实际值—目标值—公差。

—裕量值越大意为实际线长越接近目标线长。

对于不符合约束的差分对会显示”DP”的DRC错误提示。

5 Uncoupled length:该约束限制了差分对的一对网络之间的不匹配长度。差分对刚刚从芯片出来的走线通常是不耦合的,“gather contrlo”可以设置为“ignore(忽略)”和“include(包括)”,意思为在计算不匹配长度时是否包含差分对刚从芯片出来的这段不耦合的线长。在在

Net→routing→Differential Pair可以查看具体的数值。

对于不符合约束的差分对,会显示“DU”的DRC错误提示。

间距约束规则设置

间距约束设置有两种方法;1,直接在spacing→net→all layer中填入各项数值。

2,创建约束规则,赋给各net。这种方法管理方便,在 Physical 和 Spacing 设置中用后者比较好。

1,创建规则

如图,点击右键后选择Create→Spacing Cset。

输入名字后点OK。

2.设计规则

图示中的为all layer-line中的内容,可以设置连线到各个要素的约束,在all layer中还有其他的内容的约束,和图示内容基本一样,可以分别设置。

设置好后可以在all layer-all中查看一下,这里包括了所有约束的内容。

3.赋予规则

在net-all layer中,设置Referenced Spacing Cset栏即可选择不同的约束规则,如图所示。

Net class-class的间距设置

NCIs(NET CLASS)由众多nets或者buses、differential pairs、Xnet所组成的类,可对其赋予相似的约束。

NCC(Net Class-Class)也就是设置不同class组相遇后的间距设置。

首先建立class组。

首先在net-all layer中复选多个对象,右键后选择Create-Class。

输入Class名后即可建立class。

设置class-class规则

如图,在Net Class-Class –all layer中点击右键选择Creat- Class-Class,即可弹出以下对话框。

分别选择不同的class组后即可建立class-class对。

如图,CCls LED设置的是class组LED内部的间距规则。

CCls 48设置的是class组LED对class组48的间距规则。

same net spacing工作表

在Spacing工作表下还有same net spacing工作表,用于对同一网络上的不同元素进行间距约束。在16.2以前的版本中只能选择是否开启same net DRC检查,16.2后专门独立出一个工作表,可以设置详细的数值。

规则设置和Spacing规则设置没有多少差异,可以和Spacing规则设置的一样。需要在Analysis – Analysis Modes -- same net spacing Modes中开启分析选项,如图。

并在same net spacing – Options中开启相应层的DRC选项,如图。

为了避免和Spacing DRC混淆,Same Net Spacing DRC显示为小写,如图。

区域约束规则设置

region约束就是15.X 的 Area 约束。在pcb布线时有些区域比如bga封装区因为过孔密集需要特殊的线宽线距约束,此时设置region就可以满足要求

首先,创建region区域。

在physical或者 spacing工作表下新建一个区域(Region)约束。

输入名字。

建立完成后,在pcb板上画出一个区域。选择 shape-regtanglar,注意在右边的options 窗口中,active class subclass 选择 constrait region,选定你需要约束的那一层,在 assign to region 里选择刚刚建好的好个区域规则(RGN2)将这个规则指定到这个区域中。

建好了region就可以赋予相应的规则了。

建立区域物理规则

如图,在菜单中选择Create – region-class,弹出的对话框中选择需要约束的class组,就可以建立在该区域下class组的走线物理约束规则。

设定好约束后,在region区域就会按照特定的规则走,出了region后就按照一般的规则走。

建立区域间距约束规则

创建region-class规则

如图,在菜单中选择Create – region-class,弹出的对话框中选择需要约束的class组,就可以建立在该区域下class组的走线间距约束规则。

创建region-class-class规则、

如图,在菜单中选择Create – region-class-class,弹出的对话框中选择需要约束的两组class组,就可以建立在该区域下两组class组相遇时的走线间距约束规则。

如图所示,在区域内设置两线最小间距1mil,布线时间距不少于1mil就不会有DRC错误。

等长约束设置

差分对的约束设置 第一步,差分对的设置 差分对的设置有很多方法,下面介绍两种最常用的方法。 1.点击菜单Logic→Assign Differential Pair... 弹出以下对话框。 点击你想要创建差分对的Net1和Net2,填入差分的名字,点击Add后就成功创建了差分对。 点击Auto Generate按钮后,弹出以下对话框:

在第一个输入框填入Net的主要名字后,在下面的框中填入差分线的标志如N,P。点击Generate即可自动产生差分对。 2.在约束管理器中设置差分对。 在DSN上点击右键,在菜单中选择Create→Differential Pair。即可弹出下面的对话框。

和上一种方法的设置差不多,这里就不再叙述了。 第二步差分对约束规则的设置 差分对各项约束可以在约束管理器中的 Electric→Net→routing→Differential Pair中直接在各差分对上填入各项约束数值就可生效,但更好的方法是创建约束规则后赋给各个差分对。 在DSN上点击右键,在菜单中选择Create→Electrical CSet后,弹出下面的对话框; 输入规则名后点Ok,在Electric→constraimt set→outing→Differential Pair中可以看到新规则。 在表格中输入各项数值即可完成新规则的设置。如图所示 差分对约束参数主要有以下几个:

1coupling paramaters 主要包括了 Primary Gap 差分对最优先线间距(边到边间距)。 Primary Width 差分对最优先线宽。 Neck Gap 差分对Neck模式下的线间距(边到边间距),用于差分对走线在布线密集区域时切换到Neck值。 Neck Width差分对Neck模式下的线宽,用于差分对走线在布线密集区域时切换到Neck值。如图所示 设置数值时在表格中右键菜单中选择change,会出现以下各层数值表格,可以在每一层上设置不同的数值。 需要注意的是在物理(physical)约束中同样可以设置差分规则,但是电气规则约束在布线时更优先,同时电气规则可以设置更多的约束,推荐在电气规则中设置差分走线的约束。 2 Min Line Specing 差分对最小间距,一定要小于或等于"Primary gap"与(-)tolerance的数值,并且也要小于或等于"Neck gap"与(-)tolerance的数值。对于不符合约束的差分对,会显示“DS”的DRC错误提示。

【差分约束】Cashier Employment(出纳员的雇佣) Time Limit:1000MS Memory Limit:65536K Total Submit:2 Accepted:2 Description 出纳员的雇佣(cashier.pas/c/cpp) 【问题描述】 Tehran的一家每天24小时营业的超市,需要一批出纳员来满足它的需要。超市经理雇佣你来帮他解决他的问题——超市在每天的不同时段需要不同数目的出纳员(例如:午夜时只需一小批,而下午则需要很多)来为顾客提供优质服务。他希望雇佣最少数目的出纳员。 经理已经提供你一天的每一小时需要出纳员的最少数量——R(0), R(1), ..., R(23)。R(0)表示从午夜到上午1:00需要出纳员的最少数目,R(1)表示上午1:00到2:00之间需要的,等等。每一天,这些数据都是相同的。有N人申请这项工作,每个申请者I在没24小时中,从一个特定的时刻开始连续工作恰好8小时,定义tI (0 <= tI <=23)为上面提到的开始时刻。也就是说,如果第I个申请者被录取,他(她)将从tI 时刻开始连续工作8小时。你将编写一个程序,输入R(I)(I = 0..23)和tI (I = 1..N),它们都是非负整数,计算为满足上述限制需要雇佣的最少出纳员数目。在每一时刻可以有比对应的R(I)更多的出纳员在工作。 Input 第一行为测试点个数(<= 20)。每组测试数据的第一行为24个整数表示R(0),R(1),..., R(23)(R(I)<= 1000)。接下来一行是N,表示申请者数目(0 <= N <= 1000),接下来每行包含一个整数tI (0 <= tI <= 23)。两组测试数据之间没有空行。Output 对于每个测试点,输出只有一行,包含一个整数,表示需要出纳员的最少数目。如果无解,你应当输出“No Solution”。 Sample Input 1

数与图的完美结合 -------浅析差分约束系统 华中师大一附中冯威 [摘要] 在面对多种多样的问题时,我们经常会碰到这样的情况:往往我们能够根据题目题面意思来建立一些简单的模型,但却面对这些模型无从下手。这时我们应该意识到,也许能够将这种模型与其他的模型之间搭起一座桥梁,使我们能够用更简单直接的方式解决它。这里我们介绍一种方法,它很好地将某些特殊的不等式组与图相联结,让复杂的问题简单化,将难处理的问题用我们所熟知的方法去解决,它便是差分约束系统。这里我们着重介绍差分约束系统的原理和其需要掌握的bellman-ford算法。然后通过zju1508和zju1420两道题目解析差分约束系统在信息学题目中的应用,并逐渐归纳解决这类问题的思考方向。 [目录] ◆关键字 (2) ◆Bellman-ford算法 (2) ◇算法简单介绍 (2) ◇算法具体流程 (2) ◇例题一ZJU2008 (4) ◆差分约束系统 (5) ◇例题二ZJU1508 (5) ◇线性程序设计 (7) ◇差分约束系统 (7) ◇例题三ZJU1420 (8) ◆结语 (9) ◆附录 (9)

[关键字] 差分约束系统、不等式、单元最短路径、转化 [正文] 在分析差分约束系统之前,我们首先介绍一个解决单元最短路径问题的Bellman Ford算法,它的应用十分广泛,在差分约束系统中更充当着重要的角色。 Bellman-ford 算法 算法简单介绍 这个算法能在更一般的情况下解决最短路的问题。何谓一般,一般在该算法下边的权值可以为负,可以运用该算法求有向图的单元最长路径或者最短路径。我们这里仅以最短路径为例。 Bellman ford 类似于Dijkstra算法,对每一个节点v∈V,逐步减小从起点s到终点v最短路的估计量dist[v]直到其达到真正的最短路径值mindist[v]。Bellman-ford算法同时返回一个布尔值,如果不存在从源结点可达的负权回路,算法返回布尔值TRUE,反之返回FALSE。 算法具体流程 1.枚举每条边(u,v)∈E(G)。 2.对枚举到的边进行一次更新操作。 3.回到步骤1,此过程重复n-1次,以确定没有更可以优化的情况。 4.枚举每条边(u,v)若仍然存在可以更新的边,则说明有向图中出现了负权回路,于是返回布尔值FALSE。 5.返回布尔值TRUE。 注:这里的更新操作是一种松弛技术,以单元最短路径为例这个操作就是保证 dist[v]<=dist[u]+w[u,v],即if dist[v]>dist[u]+w[u,v] then dist[v]=dist[u]+w[u,v],如果是最长路径则是保证dist[v]>=dist[u]+w[u,v]。 定义一个有向图G=(V,E),w(u,v)表示由结点u到v的边的权值。 伪代码如下:

1)pair 名称: Allegro菜单点击logic-->Assign differential pair,在net filter 中选择所要设的net1,net2, 或直接在board file 中点选net,在Rule Name 中key 入pair 名称﹐点右下方的Add 后会自动增加到上方的Rule Selection Area 中﹐可以点Modify或Delete 来修改或删除所设的pair. 2)设置差分线规则类型 给pair 定义一个net spacing type property(规则类型),如CLK-CLK:点Attach property, net...,注意find 窗口中选property 而非net,再点more...,从左边选取先前设的pair,如CK0R-CK0R,点apply﹐在弹出的对话框中点net_spacing_type﹐在右边的value 值中输入CLK-CLK。 3)设置差分线规则参数 set net spacing constrains values , 设定走线线距规则参数值:点constraints 窗口的spacing rule set 下的set values,在出现的对话框中右边空格输入CLK-CLK, 点add 增加到constraint set name 栏。然后按guideline 设定各项spacing.ˉ line to line 指的是此对pair 和其它线的间距。 注1: Length Tolerance indicates the amount of tolerance allowed between the total length or delay of the two nets. (两net 之间的误差范围) 注2:Primary Max Sep indicates the maximum edge to edge spacing between a differential pair. (指该pair 本身的间距) 注3:Secondary Max Sep indicates an edge to edge spacing that is greater that the Primary Max Sep value. This allows an increase in thespacing between the differential pair when necessary. The total amount of etch/conductor on a net can not exceed this amount.(必要时允许增大该pair 本身的间距到此值) 4)布线技巧 route differential pair 时的技巧:routing 时发现本身的两根net 没有按规则挤线会弹的很开。原因可能是设rule 时﹐选的不是property,而是net 。如果选的是property 仍然不行﹐可以在setup> user preferences>drc>drc_diff_pair_overlide 中添加0。

Allegro 16.3约束规则设置 约束管理器是一个交叉的平台,以工作簿和工作表的形式在 Cadence PCB设计流程中用于管理所有工具的高速电子约束。可以使用约束管理器和SigXplorer Expert 开发电路的拓扑并得出电子约束,可以包含定制约束、定制测量和定制激励。 所谓约束就是用户定义的限制条件,当在板上走线和放置元件时会遵守这些约束。电子约束(ECSets)就是限制PCB 上与电行为有关的对象,比如可以设置某个网络最大传输延迟为2ns。 以下图为一约束设置窗口。 一、说明 先解释一下约束的类型以及约束中用到的简写名词,如下图所示:

1、NCIs(NET CLASS) 由众多nets或者buses、differential pairs、Xnet所组成的类,可对其赋予相似的约束。如下图所示。 2、NCC(Net Class-Class) 一般用在约束组与组之间的间距的时候使用,如下图。 3、DPr(Differential Pairs)差分对 一组差分对一般由两条Xnet或者net以差分走线的方式组成,如下图。差分对的形成有两种方式:一是由模型指定的差分对,再者就是由用户自己定义的差分对。 ?模型定义的差分对:可以在器件信号模型中指定差分对,可以使用PCB Design,PCB SI,SigXplores 来将模型指定给相应的元件。 ?用户定义的差分对:可以在约束管理器中 Net 一级的对象中创建差分对,可以灵活的更改差分对命名和更改差分对成员,但是没有模型指定差分对的精确性。 以下是设置差分对规则时,需要赋予约束的项。

针对以上约束中用到的一些约束点进行解释说明:

(本文假设读者已经有以下知识:最短路径的基本性质、Bellman-Ford算法。)比如有这样一组不等式: X1 - X2 <= 0 X1 - X5 <= -1 X2 - X5 <= 1 X3 - X1 <= 5 X4 - X1 <= 4 X4 - X3 <= -1 X5 - X3 <= -3 X5 - X4 <= -3 不等式组(1) 全都是两个未知数的差小于等于某个常数(大于等于也可以,因为左右乘以-1就可以化成小于等于)。这样的不等式组就称作差分约束系统。 这个不等式组要么无解,要么就有无数组解。因为如果有一组解{X1, X2, ..., Xn}的话,那么对于任何一个常数k,{X1 + k, X2 + k, ..., Xn + k}肯定也是一组解,因为任何两个数同时加一个数之后,它们的差是不变的,那么这个差分约束系统中的所有不等式都不会被破坏。 差分约束系统的解法利用到了单源最短路径问题中的三角形不等式。即对于任何一条边u -> v,都有: d(v) <= d(u) + w(u, v) 其中d(u)和d(v)是从源点分别到点u和点v的最短路径的权值,w(u, v) 是边u -> v的权值。 显然以上不等式就是d(v) - d(u) <= w(u, v)。这个形式正好和差分约束 系统中的不等式形式相同。于是我们就可以把一个差分约束系统转化成一张图,每个未知数Xi对应图中的一个顶点Vi,把所有不等式都化成图中的一条边。对于不等式Xi - Xj <= c,把它化成三角形不等式:Xi <= Xj + c,就可以化成 边Vj -> Vi,权值为c。最后,我们在这张图上求一次单源最短路径,这些三角形不等式就会全部都满足了,因为它是最短路径问题的基本性质嘛。 话说回来,所谓单源最短路径,当然要有一个源点,然后再求这个源点到其他所有点的最短路径。那么源点在哪呢?我们不妨自已造一个。以上面的不等式组为例,我们就再新加一个未知数X0。然后对原来的每个未知数都对X0随便加一个不等式(这个不等式当然也要和其它不等式形式相同,即两个未知数的差小于等于某个常数)。我们索性就全都写成Xn - X0 <= 0,于是这个差分约束系 统中就多出了下列不等式: X1 - X0 <= 0 X2 - X0 <= 0 X3 - X0 <= 0 X4 - X0 <= 0

Allegro16.6约束规则设置详解 前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。 目录: 一、基本约束规则设置 1、线间距设置 2、线宽设置 3、设置过孔 4、区域约束规则设置 5、设置阻抗 6、设置走线的长度范围 7、设置等长 7.1、不过电阻的NET等长 7.2、过电阻的XNET等长 7.3、T型等长 8、设置通用属性 9、差分规则设置 9.1、创建差分对 9.2、设置差分约束 10、Pin Delay

二、高级约束规则设置 11、单个网络长度约束 12、a+b类长度约束 13、a+b-c类长度约束 14、a+b-c在最大和最小传播延迟中的应用

1、线间距设置 (1)、设置默认间距规则 点击CM图标,如下图所示,打开约束管理器。 单击Spacing,再点击All Layers,如下图所示。右边有一个DEFAULT就是默认规则,我们可以修改其值。

按住Shift键,点击第一个和最后一个即可选中所示,然后输入一个值,这样就都修改了,如下图所示 (2)、定义特殊的间距约束 点选Default按鼠标右键,执行Create-Spacing CSet

加入新规则。取一个有意义点的名字,如下图所示,单击OK。 其值是从默认规则拷贝的,先修改其值。 按住Shift键选中所有,输入12,回车。 然后为所需要设置的网络分配规则 单击左边的Net-All Layers,在右边工作簿中,为GND网络设置12MIL_SPACE规则,在Referenced Spacing CSet下选中12MIL_SPACE,如下图所示

算法分块总结 为备战2005年11月4日成都一战,特将已经做过的题目按算法分块做一个全面详细的总结,主要突出算法思路,尽量选取有代表性的题目,尽量做到算法的全面性,不漏任何ACM可能涉及的算法思路。算法设计中,时刻都要牢记要减少冗余,要以简洁高效为追求目标。另外当遇到陌生的问题时,要想方设法进行模型简化,转化,转化成我们熟悉的东西。 图论模型的应用 分层图思想的应用: 用此思想可以建立起更简洁、严谨的数学模型,进而很容易得到有效算法。重要的是,新建立的图有一些很好的性质: 由于层是由复制得到的,所以所有层都非常相似,以至于我们只要在逻辑上分出层的概念即可,根本不用在程序中进行新层的存储,甚至几乎不需要花时间去处理。由于层之间的相似性,很多计算结果都是相同的。所以我们只需对这些计算进行一次,把结果存起来,而不需要反复计算。如此看来,虽然看起来图变大了,但实际上问题的规模并没有变大。 层之间是拓扑有序的。这也就意味着在层之间可以很容易实现递推等处理,为发现有效算法打下了良好的基础。 这些特点说明这个分层图思想还是很有潜力的,尤其是各层有很多公共计算结果这一点,有可能大大消除冗余计算,进而降低算法时间复杂度。 二分图最大及完备匹配的应用: ZOJ place the robots: 二分图最优匹配的应用: 最大网络流算法的应用:典型应用就求图的最小割。 最小费用最大流的应用: 容量有上下界的最大流的应用: 欧拉路以及欧拉回路的应用:主要利用求欧拉路的套圈算法。 最小生成树: 求最小生成树,比较常用的算法有Prim算法和Kruskal算法。前者借助Fibonacci堆可以使复杂度降为O(Vlog2V+E),后者一般应用于稀疏图,其时间复杂度为O(Elog2V)。 最小K度限制生成树: 抽象成数学模型就是: 设G=(V,E,ω)是连通的无向图,v0 ∈V是特别指定的一个顶点,k为给定的一个正整数。 首先考虑边界情况。先求出问题有解时k 的最小值:把v0点从图中删去后,图中可能会出现m 个连通分量,而这m 个连通分量必须通过v0来连接,所以,在图G 的所有生成树中 dT(v0)≥m。也就是说,当k ?? ?????????????????????1. ???????.2.???????? 1??Logic=>Assign Differential Pair… ?1?????????? ?2????????????? ?3??Add,???????????????????????????????????OK? 2???PCB ?? Setup=>Constraints=>Electical… ????????Electrical?NET? ???? ????Objects->Create->Differential Pair??????? Create Differential Pair ??????? ???? ????? Net ???????????? ???????????Selections ??Diff Pair Name ?????????Create ???Close ??????????????? ?? ???????????????????????Eelctrical ??Eelctrical Constraint Set->Routing->Differential Pair ??Objects=>Create=>Eelctrical CSet ????? & ????? ???( ???' ???2. ???? ???? ?????? ' ?????? ???????????????? ? 8 ????????????????? ? 0 / 6????? ? 3 *??????? ? ? ? 3 :???????? ? 1 *?????1 ????? ? ???? ????????? * ?????? ? 1 :?????1 ????????? ???????? : ?????? ??????????????????( ???1 ! ???? ????????5 ? ?????? ????? 约束规则设置 约束管理器是一个交叉的平台,以工作簿和工作表的形式在 Cadence PCB设计流程中用于管理所有工具的高速电子约束。可以使用约束管理器和SigXplorer Expert 开发电路的拓扑并得出电子约束,可以包含定制约束、定制测量和定制激励。 所谓约束就是用户定义的限制条件,当在板上走线和放置元件时会遵守这些约束。电子约束(ECSets)就是限制PCB 上与电行为有关的对象,比如可以设置某个网络最大传输延迟为2ns。 以下图为一约束设置窗口。 一、说明 先解释一下约束的类型以及约束中用到的简写名词,如下图所示: 由众多nets或者buses、differential pairs、Xnet所组成的类,可对其赋予相似的约束。如下图所示。 2、NCC(Net Class-Class) 一般用在约束组与组之间的间距的时候使用,如下图。 3、DPr(Differential Pairs)差分对 一组差分对一般由两条Xnet或者net以差分走线的方式组成,如下图。差分对的形成有两种方式:一是由模型指定的差分对,再者就是由用户自己定义的差分对。 ?模型定义的差分对:可以在器件信号模型中指定差分对,可以使用PCB Design,PCB SI,SigXplores 来将模型 指定给相应的元件。 ?用户定义的差分对:可以在约束管理器中 Net 一级的对象中创建差分对,可以灵活的更改差分对命名和更改差分对成员,但是没有模型指定差分对的精确性。 以下是设置差分对规则时,需要赋予约束的项。 针对以上约束中用到的一些约束点进行解释说明: 差分对的worksheets包含5个主要的约束目录: (1)Pin Delay 此值指一对网络之间管脚封装上的延迟,单位是时间ns 或者长度mil。 (2) 不耦合长度(Uncoupled Length) 不耦合长度约束是用来限制差分对的一对网络之间的不匹配长度。若“gather control”设置为ignore,则实际不不耦合长度不包括两个驱动和接收之间的耦合带之外的长度。若“gather control”设置为“include”,包含出芯片的这段不耦合长度。当不耦合(即在差分对刚刚从芯片出来的走线通常是不耦合的,不耦合有一定的长度)长度超过“max”时产生冲突。 (3)相位偏差(Static Phase Tolerance) 相位偏差约束确保差分对成员在转换时是同相和同步的。实际的数值(actual value)从长度上或者时间上反应了差分对成员之间的差值,当差值超出 tolerance 值时,就会有冲突。 (4)最小线间距(Min Line Spacing) 最小线间距约束指差分对之间的最小距离,如果小于设定的最小值则报错。添加的最小线间距约束值必须小于或者等于Primary Gap减去(-)Tolerance,并且也要小于或者等于Neck Gap减去(-)Tolerance。 (5)耦合参数(Coupling Parameters) 这里面包括6个部分需要设置。1、Primary gap :设置的是差分对之间的边到边理想间距,(+/-)tolerance 值是允许Diff Pairs的偏差值,如果间距偏差在范围内,差分对被认为是耦合的;2、Primary width:差分对成员的理想宽度;3、Neck gap:约束的是最小允许的边到边的差分间距,当在密集区域走线时,可能切换到neck模式,最小可允许的gap 包括Neck Gap 减去(-)Tolerance,当差分对间距小于ECSet 指定给差分对网络的Min neck width 规则值时,Neck Gap 覆盖任何Primary Gap 值,确保 Neck gap 不要低于任何Min line spaing 值,如果设置了(-)tolerance 值,不需要定义Neck gap ,因为已经说明了需要的Neck gap。;4、Neck width:最小可允许的差分对宽度,当在比较密集的区域走线的时,可能需要切换到neck模式;5、(+)Tolerance;6、(-)Tolerance。 使用差分计算器可以完成综合线宽和线距的计算以获得特殊的差分阻抗。在约束管理器中右键点击Primary Gap, 给HC_操行分表增加约束唯一约束和聚集索引 首先唯一性约束不能为空 修改某列的定义 alter table HC_操行分表 alter column HC_姓名varchar(10)not null go alter table HC_操行分表 add constraint PK_caoxingfen primary key Clustered(HC_姓名) go 给操行分定义一个约束,操行分不能超过或不能低于分 alter table HC_操行分表 alter column HC_成绩int not null go alter table HC_操行分表 add constraint CK_checkNum check(HC_成绩between 0 and 100) go ---创建规则绑定到指定的列上 create rule CK_checkNum as @score1 between 0 and 100 GO exec sp_bindrule'CK_checkNum','HC_操行分表.HC_成绩' -给HC_会员信息表增加约束和规则,限制性别为男和女 规则 create rule SexLimit as @sexl in('男','女') GO exec sp_bindrule'SexLimit','HC_会员信息表.HC_性别' GO 约束 alter table HC_会员信息表 add constraint CK_sexlimit check(HC_性别in('男','女')) go ----给电话增加约束为[][][][][][]的形式的约束 alter table HC_会员信息表 add constraint CK_phoNum Doc Scope : Cadence Allegro 15.x Doc Number : SFTCA06001 Author :SOFER Create Date :2005-5-30 Rev :1.00 Allegro 15.x差分线布线规则设置 文档内容介绍: 1.文档背景 (3) 2.Differential Pair信号介绍 (3) 3.如何在Allegro中定义Differential Pair属性 (4) 4.怎样设定Differential Pair在不同层面控制不同线宽与间距 (8) 5.怎样设定Differential Pair对与对之间的间距 (11) 1.文档背景 a)差分信号(Differential Signal)在高速电路设计中的应用越来越广泛,差分线 大多为电路中最关键的信号,差分线布线的好坏直接影响到PCB板子信号质量。 b)差分线一般都需要做阻抗控制,特别是要在多层板中做的各层的差分走线阻抗都 一样,这个一点要在设计时计算控制,否则仅让PCB板厂进行调整是非常麻烦的事情,很多情况板厂都没有办法调整到所需的阻抗。 c)Allegro版本升级为15.x后,差分线的规则设定与之前版本有很大的改变。虽然 Allegro15.0版本已经发布很长时间了,但是还是有很多人对新版本的差分线规则设置不是很清楚。 2.Differential Pair信号介绍 差分信号(Differential Signal)在高速电路设计中的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计,什么另它这么倍受青睐呢?在PCB设计中又如何能保证其良好的性能呢?带着这两个问题,我们进行下一部分的讨论。何为差分信号?通俗地说,就是驱动端发送两个等值、反相的信号,接收端通过比较这两个电压的差值来判断逻辑状态“0”还是“1”。而承载差分信号的那一对走线就称为差分走线。 差分信号和普通的单端信号走线相比,最明显的优势体现在以下三个方面: a.抗干扰能力强,因为两根差分走线之间的耦合很好,当外界存在噪声干扰时,几乎是同时被耦合到两条线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可以被完全抵消。 b.能有效抑制EMI,同样的道理,由于两根信号的极性相反,他们对外辐射的电磁场可以相互抵消,耦合的越紧密,泄放到外界的电磁能量越少。 c.时序定位精确,由于差分信号的开关变化是位于两个信号的交点,而不像普通单端信号依靠高低两个阈值电压判断,因而受工艺,温度的影响小,能降低时序上的误差,同时也更适合于低幅度信号的电路。目前流行的LVDS(low voltage differential signaling)就是指这种小振幅差分信号技术。 …… 由于篇幅问题,这里对差分信号不做深入介绍了。 前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。 目录: 一、基本约束规则设置 1、线间距设置 2、线宽设置 3、设置过孔 4、区域约束规则设置 5、设置阻抗 6、设置走线的长度范围 置详解(图文并茂) 则设约束规.616o r g Alle (为了不侵犯别人的成果,所以在这里做了特殊说明,以示敬意)首先感谢詹书庭编写这篇文章,为我们学习交流Cadence allegro 苦用心! 俗话说的好,社会在发展,技术在进步,技术的进步在于不断的学习交流和实践。所以为了方便大家学习交流,为大家提供一个良好 QQ )! 学习交流 Cadence allegro 请加QQ 群: 一起来学AllegRo 【2】.群号: 331730476 .以下是正文 这篇文章写得很好,操作步骤详细,截图一目了然,通俗易懂,唯一的缺点就是部分截图不是很清晰,我对个别图片做了调整和替 换,不易替换的不清晰图片,仔细看下也能明白其中的意思。 此文章由丹心静居整理---2014.10.13 加入。对原文作者表示歉意的交流平台,在这里留下我们的群原文作者的群拒绝任何人 (QQ 软件提供了丰富的知识和方法。请大家认真学习,不要辜负作者的良 2014-10-13 第 1 页,共 83 页 二、高级约束规则设置 11、单个网络长度约束 12、a+b 类长度约束 13、a+b-c 类长度约束 14、a+b-c 在最大和最小传播延迟中的应用 y a l e D n i P 、10约束分差设置、.29分对差创建、.19设置则分规差、 9属性用置通设、 8等长型T 、.37等长NET X 阻的过电、.27等长NET 阻的电不过、.17置等长 设、 7 差分约束系统 在一个差分约束系统(system of difference constraints)中,线性规划矩阵A的每一行包含一个1和一个-1,A的其他所有元素都为0。因此,由Ax≤b给出的约束条件是m个差分约束集合,其中包含n个未知量,对应的线性规划矩阵A为m行n列。每个约束条件为如下形式的简单线性不等式:xj-xi≤bk。其中1≤i,j≤n,1≤k≤m。 例如,考虑这样一个问题,寻找一个5维向量x=(xi)以满足: 这一问题等价于找出未知量xi,i=1,2,…,5,满足下列8个差分约束条件:x1-x2≤0 x1-x5≤-1 x2-x5≤1 x3-x1≤5 x4-x1≤4 x4-x3≤-1 x5-x3≤-3 x5-x4≤-3 该问题的一个解为x=(-5,-3,0,-1,-4),另一个解y=(0,2,5,4,1),这2个解是有联系的:y中的每个元素比x中相应的元素大5。 引理:设x=(x1,x2,…,xn)是差分约束系统Ax≤b的一个解,d为任意常数。则 x+d=(x1+d,x2+d,…,xn+d)也是该系统Ax≤b的一个解。 约束图 在一个差分约束系统Ax≤b中,m X n的线性规划矩阵A可被看做是n顶点,m条边的图的关联矩阵。对于i=1,2,…,n,图中的每一个顶点vi对应着n个未知量的一个xi。图中的每个有向边对应着关于两个未知量的m个不等式中的一个。 给定一个差分约束系统Ax≤b,相应的约束图是一个带权有向图G=(V,E),其中 V={v0,v1,…,vn},而且E={ (vi,vj) : xj-xi≤bk是一个约束}∪{ (v0,v1) , (v0,v2) , … , (v0,vn) }。引入附加顶点v0是为了保证其他每个顶点均从v0可达。因此,顶点集合V由对应于每个未知量xi的顶点vi和附加的顶点v0组成。边的集合E由对应于每个差分约束条件的边与对应于每个未知量xi的边(v0,vi)构成。如果xj-xi≤bk是一个差分约束,则边(vi,vj)的权 w(vi,vj)=bk(注意i和j不能颠倒),从v0出发的每条边的权值均为0。 定理:给定一差分约束系统Ax≤b,设G=(V,E)为其相应的约束图。如果G不包含负权回路,那么x=( d(v0,v1) , d(v0,v2) , … , d(v0,vn) )是此系统的一可行解,其中d(v0,vi)是约束图中v0到vi的最短路径(i=1,2,…,n)。如果G包含负权回路,那么此系统不存在可行解。 差分约束问题的求解 由上述定理可知,可以采用Bellman-Ford算法对差分约束问题求解。因为在约束图中,从源点v0到其他所有顶点间均存在边,因此约束图中任何负权回路均从v0可达。如果Bellman-Ford算法返回TRUE,则最短路径权给出了此系统的一个可行解;如果返回FALSE,则差分约束系统无可行解。 关于n个未知量m个约束条件的一个差分约束系统产生出一个具有n+1个顶点和n+m条边的约束图。因此采用Bellman-Ford算法,可以再O((n+1)(n+m))=O(n^2+nm)时间内将系 摘抄自C博客 组合数学 计数与统计 2001 - 符文杰:《Pólya原理及其应用》 2003 - 许智磊:《浅谈补集转化思想在统计问题中的应用》 2007 - 周冬:《生成树的计数及其应用》 2008 - 陈瑜希《Pólya计数法的应用》 数位问题 2009 - 高逸涵《数位计数问题解法研究》 2009 - 刘聪《浅谈数位类统计问题》 动态统计 2004 - 薛矛:《解决动态统计问题的两把利刃》 2007 - 余江伟:《如何解决动态统计问题》 博弈 2002 - 张一飞:《由感性认识到理性认识——透析一类搏弈游戏的解答过程》2007 - 王晓珂:《解析一类组合游戏》 2009 - 曹钦翔《从“k倍动态减法游戏”出发探究一类组合游戏问题》 2009 - 方展鹏《浅谈如何解决不平等博弈问题》 2009 - 贾志豪《组合游戏略述——浅谈SG游戏的若干拓展及变形》 母函数 2009 - 毛杰明《母函数的性质及应用》 拟阵 2007 - 刘雨辰:《对拟阵的初步研究》 线性规划 2007 - 李宇骞:《浅谈信息学竞赛中的线性规划——简洁高效的单纯形法实现与应用》 置换群 2005 - 潘震皓:《置换群快速幂运算研究与探讨》 问答交互 2003 - 高正宇:《答案只有一个——浅谈问答式交互问题》 猜数问题 2003 - 张宁:《猜数问题的研究:<聪明的学生>一题的推广》 2006 - 龙凡:《一类猜数问题的研究》 数据结构 数据结构 2005 - 何林:《数据关系的简化》 2006 - 朱晨光:《基本数据结构在信息学竞赛中的应用》 2007 - 何森:《浅谈数据的合理组织》 2008 - 曹钦翔《数据结构的提炼与压缩》 结构联合 2001 - 高寒蕊:《从圆桌问题谈数据结构的综合运用》 2005 - 黄刚:《数据结构的联合》 块状链表 2005 - 蒋炎岩:《数据结构的联合——块状链表》 2008 - 苏煜《对块状链表的一点研究》 动态树 2006 - 陈首元:《维护森林连通性——动态树》 2007 - 袁昕颢:《动态树及其应用》 左偏树 2005 - 黄源河:《左偏树的特点及其应用》 跳表 2005 - 魏冉:《让算法的效率“跳起来”!——浅谈“跳跃表”的相关操作及其应用》 2009 - 李骥扬《线段跳表——跳表的一个拓展》 SBT 2007 - 陈启峰:《Size Balance Tree》 线段树 2004 - 林涛:《线段树的应用》 单调队列 2006 - 汤泽:《浅析队列在一类单调性问题中的应用》 哈希表 2005 - 李羽修:《Hash函数的设计优化》 2007 - 杨弋:《Hash在信息学竞赛中的一类应用》 Splay 2004 - 杨思雨:《伸展树的基本操作与应用》 allegro 目录 第一章约束管理器介绍 (4) 1.1 约束管理器简介 (4) 1.2 约束管理器界面简介 (8) 1.2.1worksheet selector (8) 1.2.2用户接口 (9) 1.2.3View选项 (9) 1.3 启动约束管理器 (11) 第2章OBJECTS介绍 (12) 2.1 P IN-P AIRS (13) 2.1.1Pin-Pair规则 (14) 2.2 N ETS和X NETS (14) 2.3 B USES (15) 2.4 M ATCH G ROUPS (15) 2.4.1如何确定target pin pair (16) 2.4.2相对/匹配的群组规则 (16) 2.5 D IFF P AIRS (16) 2.5.1差分对工作表 (17) 2.5.2差分计算器(Differential Calculator)的使用方法 (19) 2.5.3差分对规则 (19) 2.6 D ESIGNS AND S YSTEMS (20) 第3章设置网络的走线约束 (21) 3.1.1设置网络的最大最小传输延迟 (21) 3.1.2设置网络相对传输延迟 (24) 3.1.3设置差分对约束 (26) 3.1.4查看网络规范格式和物理格式 (28) 第4章设置网络的时序和信号完整性约束 (30) 4.1 设置时序约束 (30) 4.2 设置信号完整性约束 (32) 4.2.1设置电气属性约束 (32) 0 第一章约束管理器介绍 2 4.2.2设置反射属性约束 (33) 第5章电子约束创建和应用 (35) 5.1 创建ECS ET (35) 5.2 指定ECS ET给网络 (40) 5.3 不考虑ECS ET的缺省约束值 (41) 5.4 在原理图中查看ECS ET (41) 第6章ECOS实现 (43) 6.1 在原理图中增加网络 (43) 6.2 在原理图中修改约束 (45) 6.3 在约束管理器中修改约束 (46) 6.4 在约束管理器中删除约束 (46) 6.5 在原理图中重新命名网络 (47) 第7章在原理图和PCB之间同步约束 (50) 7.1 从原理图中输出约束 (50) 7.2 在PCB D ESIGN中查看和添加约束 (50) 7.3 在原理图中导入并查看约束 (51) 7.4 在PCB和原理图之间同步约束的两种模式 (52) 7.4.1用原理图中的约束重写PCB中的约束 (53) 7.4.2在原理图中导入PCB中变更的约束 (56) 第8章约束分析 (58) 8.1 查看工作表单元格和对象 (58) 8.2 定制约束、定制测量和定制激励 (59) 8.2.1定制约束 (59) 8.2.1.1 用户定义的属性 (59) 8.2.1.2 约束的定制测量 (59) 第9章SCHEDULING NETS (61) 9.1 S CHEDULING N ETS (61) 9.2 S CHEDULING N ETS-R EVISITED (65) 第10章相对传输延迟 (68) A llegro中的约束规则设置 Allegrophan 刚好五个字 修订记录 日期版本描述作者2008-12V1.0初版,学完的总结。适用于Cadence15.5版本。Allegrophan 2009-09-08V1.1小改,修改部分措辞Allegrophan 2009-10-14V1.2小改,更正、修改几个错漏之处。添加一些说明性文字。 感谢群里的佳猪、梦姑娘等朋友的指正! Allegrophan 目录 一:Physical(Line/vias)rule物理特性(线宽和过孔)约束设置: (4) 1)“Set values”设置约束特征值 (5) 2)“Attach property”绑定约束 (6) 3)“Assignment table”约束规则分配 (8) 二“Spacing rule”间距约束设置 (9) 1)“Set values”设置约束特征值 (9) 2)“Attach property”绑定约束 (10) 3)“Assignment table”约束规则分配 (11) 三Constraint areas区域约束设置 (12) 四Allegro中走线长度的设置 (13) 1)差分线等长设置 (13) 2)一组Net等长 (16) 3)XNet等长 (17) 线宽、线距、区域的约束主要在“Constraints Sys ”中设置,点击“Setup/Constraints ”或点击图标打开“Constraints Sys ”窗口,如下: “Constraints Sys ”窗口分两个级别,第一级别有两类:Standard design rules 和Exte Extended nded design rules 。Standard design rules 仅有一级分类,点击“Set standard values ”设置默认约束值,如下: ACM常用算法及练习 第一阶段:练经典常用算法,下面的每个算法给我打上十到二十遍,同时自己精简代码,因为太常用,所以要练到写时不用想,10-15分钟内打完,甚至关掉显示器都可以把程序打出来. 1.最短路(Floyd、Dijstra,BellmanFord) 2.最小生成树(先写个prim,kruscal要用并查集,不好写) 3.大数(高精度)加减乘除 4.二分查找. (代码可在五行以内) 5.叉乘、判线段相交、然后写个凸包. 6.BFS、DFS,同时熟练hash表(要熟,要灵活,代码要简) 7.数学上的有:辗转相除(两行内),线段交点、多角形面积公式. 8. 调用系统的qsort, 技巧很多,慢慢掌握. 9. 任意进制间的转换 第二阶段:练习复杂一点,但也较常用的算法。 如: 1. 二分图匹配(匈牙利),最小路径覆盖 2. 网络流,最小费用流。 3. 线段树. 4. 并查集。 5. 熟悉动态规划的各个典型:LCS、最长递增子串、三角剖分、记忆化dp 6.博弈类算法。博弈树,二进制法等。 7.最大团,最大独立集。 8.判断点在多边形内。 9. 差分约束系统. 10. 双向广度搜索、A*算法,最小耗散优先. 相关的知识 图论 路径问题 0/1边权最短路径 BFS 非负边权最短路径(Dijkstra) 可以用Dijkstra解决问题的特征 负边权最短路径 Bellman-Ford Bellman-Ford的Yen-氏优化 差分约束系统 Floyd 广义路径问题 传递闭包 极小极大距离/ 极大极小距离 Euler Path / Tour 圈套圈算法 混合图的Euler Path / Tour Hamilton Path / Tour 特殊图的Hamilton Path / Tour 构造 生成树问题 最小生成树 第k小生成树 最优比率生成树 0/1分数规划 度限制生成树 连通性问题 强大的DFS算法 无向图连通性 割点 割边 二连通分支 有向图连通性 强连通分支 2-SAT 最小点基 有向无环图 拓扑排序 有向无环图与动态规划的关系 二分图匹配问题 一般图问题与二分图问题的转换思路 最大匹配 有向图的最小路径覆盖 0 / 1矩阵的最小覆盖 完备匹配 最优匹配 稳定婚姻 网络流问题 网络流模型的简单特征和与线性规划的关系最大流最小割定理 最大流问题 有上下界的最大流问题 循环流 最小费用最大流/ 最大费用最大流allegro16[1].2建立差分对,设置差分规则,差分走线。

cadence Allegro16.3约束规则

约束和规则

差分线布线规则设置

Allegro16.6约束规则设置详解(图文并茂)

差分约束系统详解

NOI国家集训队论文分类(至2008)(摘抄自C博客)

约束管理器_allegro

Allegro中的约束规则设置V1.2

ACM训练计划