xilinix官方SOPC指导

- 格式:pdf

- 大小:371.58 KB

- 文档页数:19

1.目的规范仪器操作程序和日常维护,指导操作人员正确使用仪器,保证检测工作顺利进行。

2.适用范围适用于本实验室赛默飞ICAP PRO X(ICP-OES)仪器的使用操作。

3.职责3.1操作人员按照本作业指导书操作仪器,对仪器进行日常维护。

3.2保管人员负责监督仪器操作是否符合规程,对仪器进行定期维护、保养。

3.3科室负责人要加强本科室检测设备管理,严格落实检测设备管理责任制。

4.操作程序4.1开机4.1.1 开总电源,开稳压器(220V);电电脑,开仪器电源(在仪器右后方);insrument status灯闪烁;4.1.2 打开软件,界面显示彩色为正常(显示灰色很可能为连接不正常),开氩气(压力在0.55-0.60MPa,并确认氩气罐内剩余气量是否足以支持实验的进行),等1h驱气;4.2点火4.2.1 再次确认氩气是否开够1h,再次确认氩气是否充足;4.2.2 打卡排风(排风风量为1.0-1.4m/s,一般已调整设置好,只需要检查软件-控制面板-排风信号灯是否为绿色,若不是绿色才需要进行调整);打开循环冷水机(水位在80%,水质用RO一级水,温度设置在20-22度,压力在0.3-0.4MPa);注意水机需要等待温度达到设定的才能进行点火操作;4.2.3 卡住泵管(可以设置载气流量为0.5L/min,泵速为45rpm,通过观察进样针是否正常进样、废液管是否正常排液来确认是否卡号;另外需观察主要对应的卡环,共有三道,左右方向要在一个道内,最后主要扳下卡环卡紧,同时要注意泵管进出方向是否对;4.2.4 点击软件的点火图标(控制面板正中间),点火(立即在窗口观察火焰颜色,绿色为正常,出现其他颜色火焰应立即打开炬室门关火),预热30min;中间稍微停顿可以预热15min,停顿时间更短可以预热5min;观察软件,当所有标示为绿色时,可以进行测样操作;4.3建立仪器方法4.3.1 点击软件中LabBooks,依次输入名称、选择位置,点击选择从空白中创建一个新的LabBook选项,在评价中选择eQuant,点击创建;4.3.2 点击方法参数中的分析物,选择分析元素(以下元素选用仪器推荐波长Cr:267nm;Na:589nm;Mg:285nm;Ca:422nm;Al:167nm或396nm)其他元素选用仪器默认设置即可 4.3.3 点击方法参数中的采集参数,选择相应的等离子体观测方式(水平或垂直,水平的优势检出限更低,更灵敏;垂直的优势是干扰更少)4.3.4 点击方法参数中的标准,点击新建,选择元素标准,输入标准名称,选择使用分析物列表创建标准,点击确定;4.3.5 如果使用内标,则执行此步骤,如不使用内标则跳过此步骤。

Cisco FXOS CLI 配置指南 2.1(1)首次发布日期: 2017年01月23日上次修改日期: 2017年03月20日Americas HeadquartersCisco Systems, Inc.170 West Tasman DriveSan Jose, CA 95134-1706USATel: 408 526-4000800 553-NETS (6387)Fax: 408 527-0883本手册中有关产品的规格和信息如有更改,恕不另行通知。

本手册中的所有声明、信息和建议均准确可靠,但我们不为其提供任何明示或暗示的担保。

用户必须承担使用产品的全部责任。

随附产品的软件许可和有限担保在随产品一起提供的信息包中提供,且构成本文的一部分。

如果您无法找到软件许可或有限担保,请与思科代表联系获取副本。

思科所采用的TCP报头压缩是加州大学伯克利分校(UCB)开发的一个程序的改版,是UCB的UNIX操作系统公共域版本的一部分。

保留所有权利。

版权所有©1981,加州大学董事会。

无论本手册中是否有任何其他保证,这些供应商的所有文档文件和软件均按“原样”提供,并可能包含缺陷。

思科和上面所提及的提供商拒绝所有明示或暗示担保,包括(但不限于)适销性、特定用途适用性和无侵权担保,或者因买卖或使用以及商业惯例所引发的担保。

在任何情况下,对于任何间接、特殊、连带发生或偶发的损坏,包括(但不限于)因使用或无法使用本手册而导致的任何利润损失或数据损失或损坏,思科及其供应商概不负责,即使思科及其供应商已获知此类损坏的可能性也不例外。

本文档中使用的任何互联网协议(IP)地址和电话号码并非实际地址和电话号码。

本文档中所含的任何示例、命令显示输出、网络拓扑图和其他图形仅供说明之用。

说明性内容中用到的任何真实IP地址或电话号码纯属巧合,并非有意使用。

思科和思科徽标是思科和/或其附属公司在美国和其他国家/地区的商标或注册商标。

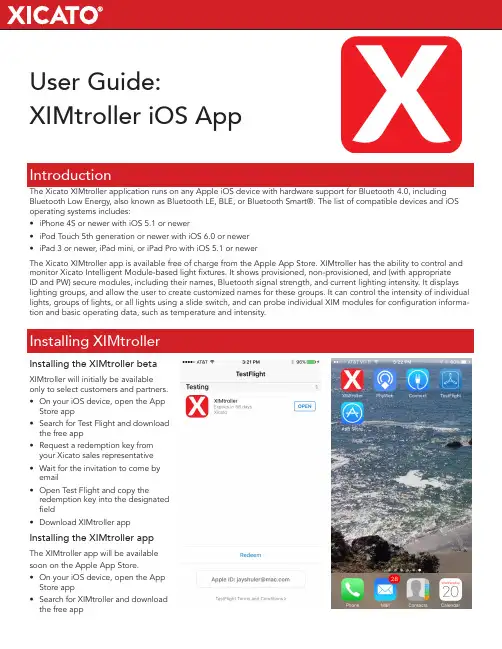

User Guide:XIMtroller iOS AppIntroductionThe Xicato XIMtroller application runs on any Apple iOS device with hardware support for Bluetooth 4.0, including Bluetooth Low Energy, also known as Bluetooth LE, BLE, or Bluetooth Smart®. The list of compatible devices and iOS operating systems includes:• iPhone 4S or newer with iOS 5.1 or newer• iPod Touch 5th generation or newer with iOS 6.0 or newer• iPad 3 or newer, iPad mini, or iPad Pro with iOS 5.1 or newerThe Xicato XIMtroller app is available free of charge from the Apple App Store. XIMtroller has the ability to control and monitor Xicato Intelligent Module-based light fixtures. It shows provisioned, non-provisioned, and (with appropriateID and PW) secure modules, including their names, Bluetooth signal strength, and current lighting intensity. It displays lighting groups, and allow the user to create customized names for these groups. It can control the intensity of individual lights, groups of lights, or all lights using a slide switch, and can probe individual XIM modules for configuration informa-tion and basic operating data, such as temperature and intensity.Installing the XIMtroller beta XIMtroller will initially be availableonly to select customers and partners.• On your iOS device, open the App Store app• Search for Test Flight and download the free app• Request a redemption key from your Xicato sales representative • Wait for the invitation to come by email• Open Test Flight and copy the redemption key into the designated field• Download XIMtroller app Installing the XIMtroller app The XIMtroller app will be available soon on the Apple App Store.• On your iOS device, open the App Store app• Search for XIMtroller and downloadthe free appInstalling XIMtrollerWhen you open the XIMtroller appli-cation, you will immediately see the Dashboard view. When opened, the app will immediately start listening for XIM advertisements and will begin listing the units. The listing process may take several seconds, depending on the number of units and how strong their signals are.At the top in gray, you see the name of the screen and the Settings button, whose icon looks like three horizontal bars. Below that, you see a slider with -/+ “trim” buttons to the left and an on-off switch to the right. By default, the slider is set to 100%, but it does not control the lights unless you tog-gle the On/Off button twice.Below that is a table header bar in darker gray. The columns are:• “Signal”, for signal strength• “Intensity”, for the light intensity • “## Lights” which states the num-ber of lights in the list and is the header for the Name column, and • “All”, showing that you that thecontroller is initially set to control Allof the lightsBelow that is the list of modules.Note that “Signal” is highlighted. Theapp initially lists the units in order ofSignal Strength, which means that theunits closest to you should appearhigher in the list.Alternatively, you can select “Inten-sity” or “## Lights”, which will causethe list to be reordered by outputintensity or name, respectively. If youtouch the same header repeatedly, itwill toggle between ascending anddescending order.The slider shows the current intensi-ty level of the selected unit or units.When “All” is shown, moving theslider or touching the switch will affectAll modules. If you select one module,it will only affect that module, and theword “All” will change to “Deselect”in the table header.Note that the number of bars under“Signal” will change dynamically dueto various signal propagation vari-ables. However, the listed intensitylevel will not change, even if you usethe slider, and the list will not reorder.To reorder the list and update inten-sity levels, either pull the list down bytouching anywhere on or below thetable header and dragging your fingerdown, or shake the iPhone. This willcause the app to start from scratch,listening for modules and reorder-ing them according to the selectedparameter.Module names are color-coded.• Names in Blue are Public modules– those that are not assigned to asecure network and therefore un-protected and able to be controlledby anyone with XIMtroller.• Names in Red are Legacy modules– those that have not been updatedto a supported firmware version.You will be able to see, but notcontrol these modules. You shouldupdate these modules to teh latestfirmware.• Names in Black are Secure mod-ules – those that are assigned toa secure network, and thereforeonly accessible to users who haveadded the secure network to theirXIMtroller app by entering the ap-propriate network name and pass-word through the Settings menu.• Names that have an bullet (•) infront of them are “Unprovisioned”nodes – nodes that have not yetbeen named or configured by theprovisioning or Control Panel app.These nodes carry the name of theirXicato XIM model number.You can scroll through the list byswiping vertically with your finger,and you can switch between theModules Dashboard and the SensorsDashboard by swiping sideways ineither direction.Using XIMtrollerOpening the App: Viewing Units in the DashboardSettingsAt the top right of the display you will see an icon with three horizontal bars.This is the Setting menu. Touching thisbutton should bring up the Settingsscreen.In the Settings screen, you can:• See the current version number of your XIMtroller software• Adjust the brightness and contrast of the app screen• Set “Indicate on touch”, which causes lights to blink 3 times when you select them in the Dashboard screen. This is useful to identify which light is associated with a par-ticular name.• Select “Show legacy modules”. This allows you to see (but not control) XIMs with older, unsupported ver-sions of firmware• Select “Show unassigned mod-ules.” This allows you to see mod-ules that have not yet been named or provisioned by the Control Panel application. Such modules arenamed by their XIM model number, and have a small bullet (•) next totheir name.• Set the “On and Off Fade Time”,which determines how quicklymodules turn on and off when youtoggle them in the Dashboard orDetail screens.Fade time can be in the range of 0-30 seconds, and can be set in • 0.1 second increments up to 5 sec-onds, in• 0.5 second increments from 5-10 seconds,• 1 second increments from 10 to 30 seconds.Fade time is shown to the left of the slider, as are trim buttons that al-low you to fine-tune the setting you choose with the slider.Settings apply to ALL modules. Even if you have first selected a specific module in the Dashboard, going to the Settings menu will set parameters for all modules, not just the selected module.To go back to the previous screen, just select the blue text with the left-point -ing arrow that appears in the extreme upper left of the screen. Or, you can swipe from left to right to “flip the page” back to the previous screen.Controlling individual XIMsFrom the Modules screen, you can select an individual module by touch-ing it once. Note that “All” changes to “Deselect” on the right side of the gray table header bar.Now, if you toggle the On-Off switch at the top right, you will turn that indi-vidual light on and off, using the ramp speed that you set in the Settings menu. If you use the slider, it will only dim or brighten that individual mod-ule. Ramp speed does not apply tothe slider.Viewing XIM StatusFrom the Dashboard, if you touch an individual module name a second time, or tap the right arrow, it will take you to the Module Status screen.At the top left, you can see at a glance the status of the module (“Status OK”). On the right, you can touch the “Indicate” button to cause the light to blink 3 times to make it easy to locate.Under that, you see another slider with trim control that allows you to control the intensity level from this screen, or turn it On/Off using the switch.Below that you see dynamic, real-time data on the status of the module, pre-sented graphically, including:• Signal Strength• Intensity, in 0.1% increments• Input Power in Watts, in 0.1W incre-ments• Input Voltage in 0.1V increments. This is one way to see whether your DC power supply is functioning properly. Much more power statusinformation is available in the Con-trol Panel application.• LED temperature. This shows you whether your modules are running hot or cool, which has implications for lifetime. XIM has a thermal fold-back circuit that detects LED tem-perature and reduces the dim level if it gets too high. This means the unit should never exceed our 90˚C warranty threshold temperature. But this information is useful to prevent and diagnose thermal issues.• Operating Hours – the total num-ber of hours that the unit has been operating at > 0% intensity. This does not include time when the unit is plugged in and under load but “off” (0% intensity), but does include 0.1% intensity. “Off” time can be seen in the Control Panel by pulling the Intensity histogram from the unit. Operating Hours is important because it is the reading that Xicato uses to establish lifetimefor purposes of Warranty support.XIM Configuration InformationFrom the XIM Status screen for an individual module, you can select “More Information” at the bottom to look at static information about the module itself, including:• Its provisioned Name • Network address• Bluetooth firmware revision • XIM hardware revision • XIM firmware revision• Group numbers to which the mod-ule has been assignedThis information is useful for technical diagnosis and support. Eventually, this screen will be configurable by OEMs with their company name and model number.Return to the XIM Status menu by selecting the name and left arrow at the top left of the screen.Viewing XIM GroupsFrom the Dashboard, touch the “All” header to see a complete list of XIM groups, along with the number of XIMmodules that belong to each group.Viewing Group MembersSelecting a group brings up a screen similar to the Dashboard that lists the modules in the group, and allows you to control all of the modules in the group at once.To return to the Groups screen, touch the number in the list header.Naming XIM GroupsGroups are represented in the XIM modules themselves as numbers. XIM modules do not store group names.However, XIMtroller users will soon be able to give custom names to these groups from within the XIMtroller application by selecting the group and pulling up a keyboard. The group names will then be stored in theXIMtroller app, but not the XIMs. This means that other XIMtroller users will not see your group names, but can give the groups their own names.。

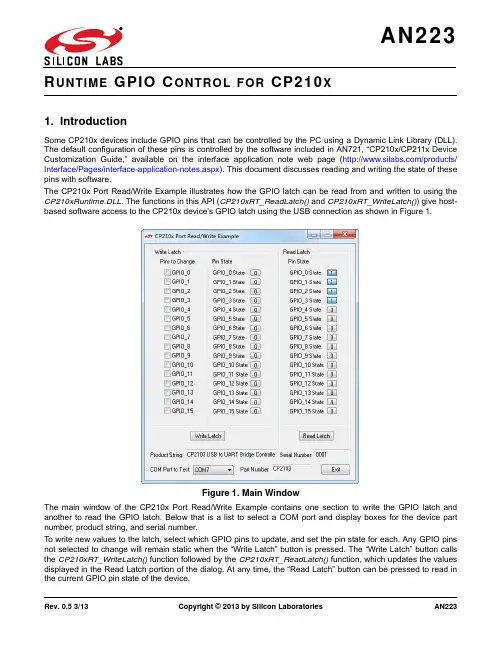

Rev. 0.5 3/13Copyright © 2013 by Silicon LaboratoriesAN2231. IntroductionSome CP210x devices include GPIO pins that can be controlled by the PC using a Dynamic Link Library (DLL).The default configuration of these pins is controlled by the software included in AN721, “CP210x/CP211x DeviceCustomization Guide,” available on the interface application note web page (/products/Interface/Pages/interface-application-notes.aspx ). This document discusses reading and writing the state of thesepins with software.The CP210x Port Read/Write Example illustrates how the GPIO latch can be read from and written to using theCP210xRuntime.DLL . The functions in this API (CP210xRT_ReadLatch() and CP210xRT_WriteLatch()) give host-based software access to the CP210x device’s GPIO latch using the USB connection as shown in Figure 1.Figure 1.Main WindowThe main window of the CP210x Port Read/Write Example contains one section to write the GPIO latch andanother to read the GPIO latch. Below that is a list to select a COM port and display boxes for the device partnumber, product string, and serial number.To write new values to the latch, select which GPIO pins to update, and set the pin state for each. Any GPIO pinsnot selected to change will remain static when the “Write Latch” button is pressed. The “Write Latch” button callsthe CP210xRT_WriteLatch() function followed by the CP210xRT_ReadLatch() function, which updates the valuesdisplayed in the Read Latch portion of the dialog. At any time, the “Read Latch” button can be pressed to read inthe current GPIO pin state of the device.AN2232. Creating Custom Applications using CP210xRuntime.DLLCustom applications can use the CP210x Runtime API implemented in CP210xRuntime.DLL. To use functions implemented in CP210xRuntime.DLL, link CP210xRuntime.LIB with your Visual C++ 6.0 application. Include CP210xRuntimeDLL.h in any file that calls functions implemented in CP210xRuntime.DLL.3. CP210x Runtime API FunctionsThe CP210x Runtime API provides access to the GPIO port latch, and is meant for distribution with the product containing a CP210x device.⏹ CP210xRT_ReadLatch()—Returns the GPIO port latch of a CP210x device.⏹ CP210xRT_WriteLatch()—Sets the GPIO port latch of a CP210x device.⏹ CP210xRT_GetPartNumber()—Returns the 1-byte Part Number of a CP210x device.⏹ CP210xRT_GetProductString ()—Returns the product string programmed to the device.⏹ CP210xRT_GetDeviceSerialNumber ()—Returns the serial number programmed to the device.⏹ CP210xRT_GetDeviceInterfaceString ()—Returns the interface string programmed to the device. Typically, the user initiates communication with the target CP210x device by opening a handle to a COM port using CreateFile() (See AN197: “Serial Communication Guide for CP210x”). The handle returned allows the user to call the API functions listed above. Each of these functions is described in the following sections. Type definitions and constants are defined in the file CP210xRuntimeDLL.h.Note:Functions calls into this API are blocked until completed. This can take several milliseconds depending on USB traffic.3.1. CP210xRT_ReadLatchDescription:Gets the current port latch value from the device.Supported Devices:CP2103, CP2104, CP2105, CP2108Location:CP210x Runtime DLLPrototype:CP210x_STATUS CP210xRT_ReadLatch(HANDLE Handle, LPWORD Latch)Parameters: 1.Handle—Handle to the Com port returned by CreateFile().tch—Pointer for 4-byte return GPIO latch value [Logic High=1, Logic Low=0].Return Value:CP210x_STATUS=CP210x_SUCCESS,CP210x_INVALID_HANDLE,CP210x_DEVICE_IO_FAILEDCP210x_FUNCTION_NOT_SUPPORTEDAN223 3.2. CP210xRT_WriteLatchDescription:Sets the current port latch value for the device.Supported Devices:CP2103, CP2104, CP2105, CP2108Location:CP210x Runtime DLLPrototype:CP210x_STATUS CP210xRT_WriteLatch(HANDLE Handle, WORD Mask, WORD Latch)Parameters: 1.Handle—Handle to the Com port returned by CreateFile().2.Mask—Determines which pins to change [Change = 1, Leave = 0].tch—4-byte value to write to GPIO latch [Logic High = 1, Logic Low = 0]Return Value:CP210x_STATUS=CP210x_SUCCESS,CP210x_INVALID_HANDLE,CP210x_DEVICE_IO_FAILEDCP210x_FUNCTION_NOT_SUPPORTED3.3. CP210xRT_GetPartNumberDescription:Gets the part number of the current device.Supported Devices:CP2101, CP2102, CP2103, CP2104, CP2105, CP2108Location:CP210x Runtime DLLPrototype:CP210x_STATUS CP210xRT_GetPartNumber(HANDLE Handle, LPBYTE PartNum)Parameters: 1.Handle—Handle to the Com port returned by CreateFile().2.PartNum—Pointer to a byte containing the return code for the part number.Return Value:CP210x_STATUS=CP210x_SUCCESS,CP210x_INVALID_HANDLE,CP210x_DEVICE_IO_FAILEDAN2233.4. CP210xRT_GetDeviceProductStringDescription:Gets the product string in the current device.Supported Devices:CP2101, CP2102, CP2103, CP2104, CP2105, CP2108Location:CP210x Runtime DLLPrototype:CP210x_STATUS CP210xRT_GetDeviceProductString(HANDLE cyHandle, LPVOID lpProduct, LPBYTE lpbLength, BOOL bConvertToASCII = TRUE) Parameters: 1.Handle—Handle to the Com port returned by CreateFile().2.lpProduct—Variable of type CP210x_PRODUCT_STRING returning the NULL terminatedproduct string.3.lpbLength—Length in characters (not bytes) not including a NULL terminator.4.ConvertToASCII—Boolean that determines whether the string should be left in Unicode, orconverted to ASCII. This parameter is true by default, and will convert to ASCII.Return Value:CP210x_STATUS=CP210x_SUCCESS,CP210x_INVALID_HANDLE,CP210x_DEVICE_IO_FAILEDCP210x_INVALID_PARAMETER3.5. CP210xRT_GetDeviceSerialNumberDescription:Gets the serial number in the current device.Supported Devices:CP2101, CP2102, CP2103, CP2104, CP2105, CP2108Location:CP210x Runtime DLLPrototype:CP210x_STATUS CP210xRT_GetDeviceSerialNumber(HANDLE cyHandle,LPVOID lpProduct, LPBYTE lpbLength, BOOL bConvertToASCII = TRUE)Parameters: 1.Handle—Handle to the Com port returned by CreateFile().2.lpProduct—Variable of type CP210x_SERIAL_STRING returning the NULL terminated serialstring.3.lpbLength—Length in characters (not bytes) not including a NULL terminator.4.ConvertToASCII—Boolean that determines whether the string should be left in Unicode, orconverted to ASCII. This parameter is true by default, and will convert to ASCII.Return Value:CP210x_STATUS=CP210x_SUCCESS,CP210x_INVALID_HANDLE,CP210x_DEVICE_IO_FAILEDCP210x_INVALID_PARAMETERAN223 3.6. CP210xRT_GetDeviceInterfaceStringDescription:Gets the interface string of the current device.Supported Devices:CP2105, CP2108Location:CP210x Runtime DLLPrototype:CP210x_STATUS CP210xRT_GetDeviceInterfaceString(HANDLE cyHandle, LPVOID lpInterfaceString, LPBYTE lpbLength, BOOL bConvertToASCII = TRUE) Parameters: 1.Handle—Handle to the Com port returned by CreateFile().2.lpInterfaceString—Variable of type CP210x_SERIAL_STRING returning the NULL terminatedinterface string.3.lpbLength—Length in characters (not bytes) not including a NULL terminator.4.ConvertToASCII—Boolean that determines whether the string should be left in Unicode, orconverted to ASCII. This parameter is true by default, and will convert to ASCII.Return Value:CP210x_STATUS=CP210x_SUCCESS,CP210x_INVALID_HANDLE,CP210x_DEVICE_IO_FAILEDCP210x_INVALID_PARAMETERAN223D OCUMENT C HANGE L ISTRevision 0.1 to Revision 0.2⏹Reworded Open Drain Output description for clarityRevision 0.2 to Revision 0.3⏹Added CP210xRT_GetProductString⏹Added CP210xRT_GetDeviceSerialNumber⏹Added CP210xRT_GetDeviceProductString Revision 0.3 to Revision 0.4⏹Added support for CP2104 and CP2105⏹Added CP210xRT_GetDeviceInterfaceString ⏹Added Table 3 and Table 4⏹Added Section 5.6. CP2105 GPIO Mode and Modem Mode ⏹Removed the AppendixRevision 0.4 to Revision 0.5⏹Removed sections regarding port configuration.⏹Updated interfaces to ReadLatch and WriteLatchfrom BYTE/LPBYTE to WORD/LPWORD.⏹Added CP2108 as a supported device to allfunctions. Silicon Laboratories Inc.400 West Cesar ChavezAustin, TX 78701USASimplicity StudioOne-click access to MCU andwireless tools, documentation,software, source code libraries &more. Available for Windows,Mac and Linux!IoT Portfolio/IoT SW/HW /simplicity Quality /quality Support and CommunityDisclaimerSilicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Labs shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.Trademark InformationSilicon Laboratories Inc.® , Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world’s most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.。

M2IDE 用户手册SONiX 8-Bit MCUM2IDE 用户手册Version 1.0SONiX 公司保留对以下所有产品在可靠性、 功能和设计方面的改进做进一步说明的权利。

SONiX 不承担由 本手册所涉及的产品或电路的运用和使用所引起的任何责任。

SONiX 的产品不是专门设计应用于外科植入、生 命维持和任何 SONiX 产品的故障会对个体造成伤害甚至死亡的领域。

如果将 SONiX 的产品应用于上述领域, 即使这些是由 SONiX 在产品设计和制造上的疏忽引起的,用户也应赔偿所有费用、损失、合理的人身伤害或死 亡所直接或间接产生的律师费用, 并且用户保证 SONiX 及其雇员、 子公司、 分支机构和销售商与上述事宜无关。

SONiX TECHNOLOGY CO., LTD.Page 1 of 74Version1.0M2IDE 用户手册修改记录版本 V1.0 时间 2009/8/18 修改说明 初版SONiX TECHNOLOGY CO., LTD.Page 2 of 74Version1.0M2IDE 用户手册目录修改记录 .............................................................................................................................................................................................. 2 目 录 .................................................................................................................................................................................................... 3 第 1 章 系统概要与安装 .................................................................................................................................................................... 5 1.1 M2IDE简介............................................................................................................................................................................ 5 1.2 安装 ....................................................................................................................................................................................... 6 1.2.1 系统配置需求............................................................................................................................................................ 6 1.2.2 硬件安装.................................................................................................................................................................... 6 1.2.3 软件安装.................................................................................................................................................................... 8 第 2 章 视窗界面 .............................................................................................................................................................................. 14 2.1 快速开始 ............................................................................................................................................................................. 14 2.2 菜单—文件/编辑/视图/调试/辅助/窗口/帮助选项 ........................................................................................................... 15 2.2.1 启动M2IDE系统 ..................................................................................................................................................... 15 2.2.2 M2IDE界面 .............................................................................................................................................................. 17 2.2.3 文件菜单(File) ................................................................................................................................................... 20 2.2.4 编辑菜单(Edit) ................................................................................................................................................... 23 2.2.5 视图菜单(View) ................................................................................................................................................. 26 2.2.6 调试菜单(Debug) ............................................................................................................................................... 27 2.2.7 应用菜单(Utility) ............................................................................................................................................... 30 2.2.8 窗口菜单(Window) ............................................................................................................................................ 32 2.2.9 帮助菜单(Help).................................................................................................................................................. 33 2.2.10 窗口管理................................................................................................................................................................ 34 2.3 创建和调试应用程序 ......................................................................................................................................................... 37 2.3.1 创建工程/新建文件................................................................................................................................................. 37 2.3.2 程序的编译和链接.................................................................................................................................................. 42 2.3.3 程序的运行与调试.................................................................................................................................................. 44 2.3.4 编译选项(Code Option选项) ............................................................................................................................. 49 2.3.5 工程文件类型.......................................................................................................................................................... 50 2.4 如何仿真LCD ..................................................................................................................................................................... 51 第 3 章 开发语言 .............................................................................................................................................................................. 52 3.1 指令集 ................................................................................................................................................................................. 52 3.2 伪指令 ................................................................................................................................................................................. 54 3.3 包含文档 ............................................................................................................................................................................. 55 3.4 宏 ......................................................................................................................................................................................... 56 3.5 条件编译控制 ..................................................................................................................................................................... 60 附录 .................................................................................................................................................................................................... 63 附录Ⅰ编译器错误信息说明 .................................................................................................................................................... 63 附录Ⅱ 菜单命令,工具和快捷方式一览表........................................................................................................................... 67 附录Ⅲ 伪指令表 ...................................................................................................................................................................... 70 附录Ⅳ 图片列表 ...................................................................................................................................................................... 71 附录Ⅴ相关FAQ ........................................................................................................................................................................ 73SONiX TECHNOLOGY CO., LTD.Page 3 of 74Version1.0M2IDE 用户手册前言在 SONiX 8 位微控器中,SN8P2XXX 系列开发系统采用的是在线仿真器(ICE),而 PC 机上运行的软件是 M2IDE 或 SN8 C Studio。

Ixia Software Release NotesIxNetwork 5.30 EA SP5 Patch1Build Number: 5.30.90.120 (June 22, 2009)About This ReleaseLicensingInstallation NotesTcl/Tk Support for Client ApplicationsHow to Report ProblemsAdditional DocumentationWhat's New in IxNetworkAbout This ReleaseIxNetwork 5.30 EA SP5 Patch1 is an "Early Adopter" release and now includessupport for IxNetwork-FT (Feature Test) replacing support for the legacy IxRouter application.See the specific IxNetwork-FT sections below for application compatibilityrequirements and known issues. See the Product Compatibility Matrix forIxNetwork-FT hardware support.Upgrading from a release prior to IXOS 5.10 SP2To ensure proper operation of an Ixia chassis with IxOS 5.10 EA SP3, prior toinstalling this release you must un-install all previous versions of Ixia applications,Ixia StatEngine, Ixia StatEngine PCPU packages and IxOS. You should use the Add/Remove utility in the Windows Control Panel. After the uninstallations are complete thechassis must be rebooted.IxOS CompatibilityIxNetwork 5.30 EA SP5 Patch 1 requires minimum IxOS 5.20 GA Patch 2 or IxOS 5.30EA SP2 Patch1 or later versions of IxOS 5.30 to be installed.Previous Release NotesPlease visit the IxNetwork support web page for more information on previous Release Notes.Application CompatibilityNOTE: When you are using one or more of the applications below on a singlechassis configuration, please use the correct application versions so they alignto a common version of IxOS.Application IxOS 5.20 GA Patch2 IxOS 5.30 EA SP2 Patch1IxNetwork 5.30 EA SP5 Patch1 5.30 EA SP5 Patch1IxNetwork-FT 5.30 EA SP5 Patch1 5.30 EA SP5 Patch1HLTAPI 3.40 GA 3.40 GAIxAccess 2.40 GA Patch2 N/AIxAdmin 1.00 GA SP2 1.00 GA SP2IxANVL 7.55 EA 7.55 EAIxAuthenticate 2.0 GA SP2 Patch2 N/AIxAutomate 6.60 GA 6.60 GAIxChariot 6.70 EA N/AIxDefend 3.20 EA 3.20 EAIxLoad-VoIP N/A 3.70 EAIxLoad 4.10 EA SP1 Patch1 4.20 EA (*)IxSAN N/A 1.00 EA SP1IxVPN 3.00 GA SP3 Patch3 3.00 GA SP3 Patch3Licensing 2.50 GA Patch3 2.70 EA SP1Stack Manager 3.35 EA 3.35 EATest Conductor 2.10 EA 2.10 EAVNIC 2.50 EA 2.50 EAFor the latest compatibility information to include releases occurring after thisdate, please refer to the online Product Compatibility Matrix at the link below.An Ixia website account is required before accessing./support/product_compatibility_matrixIxNetwork Load Module SupportNOTE: Not all hardware listed below is currently supported by IxNetwork-FT.See the online Product Compatibility Matrix for IxNetwork-FT specific Load Modulesupport.Module Type Supported Function M odule Part Number10G Ethernet Control Plane Testing LSM10G1-01, LSM10GXL6-01 (LAN), LSM10GXL6-02 (LAN/W AN), LSM10GXM3-01, LSM10GXMR3-01, LM10GE700F1-P, LM10GE700F1B-P, LM10GULF-P, LM10GUPF-XFP, LSM10GXM2XP-01, LSM10GXM4-01, LSM10GXM4XP-01, LSM10GXMR2-01, LSM10GXMR4-01, LSM10GXM8-01, LSM10GXM8XP-01, LSM10GXMR8-01, LSM10GR1-01, 10GBaseT-ADAP-01, LSM10GXM2S-01, LSM10GXM4S-01, LSM10GXM8S-01, LSM10GXMR2S-01, LSM10GXMR4S-01, LSM10GXMR8S-01Stateless Data Plane Test L SM10G1-01, LSM10GXL6-01 (LAN), LSM10GXL6-02 (LAN/W AN), LSM10GXM3-01, LSM10GXMR3-01, LSM10GL1-01, LSM10GXM2XP-01, LSM10GXM4-01, LSM10GXM4XP-01, LSM10GXMR2-01, LSM10GXMR4-01, LSM10GXM8-01, LSM10GXM8XP-01, LSM10GXMR8-01, LSM10GR1-01, 10GBaseT-ADAP-01, LSM10GXM2S-01, LSM10GXM4S-01, LSM10GXM8S-01, LSM10GXMR2S-01,LSM10GXMR4S-01, LSM10GXMR8S-01Application Traffic LM10GE700F1-P, LM10GE700F1B-P, LSM10G1-01, LM10GXM3-01, 10GBaseT-ADAP-01, LSM10GXM2XP-01, LSM10GXM4-01, LSM10GXM4XP-01, LSM10GXM8-01, LSM10GXM8XP-01, LSM10GR1-01, LSM10GXM2S-01, LSM10GXM4S-01, LSM10GXM8S-0110/100/1G Ethernet C ontrol Plane Testing ASM1000XMV12X-01, LM1000STXS2, LM1000STXS4, LM1000STXS4-256, LM1000TXS4, LM1000STXR4, OLM1000STXS24, LM1000SFPS4, ALM1000T8, ELM1000ST2, CPM1000T8, LSM1000XMS12-01, LSM1000XMSR12-01, LSM1000XMV4-01, LSM1000XMVR4-01, LSM1000XMV8-01, LSM1000XMVR8-01, LSM1000XMV12-01, LSM1000XMVR12-01, LSM1000XMV16-01, LSM1000XMVR16-01, ACCELERON-NP-01 (Non-Aggregate Mode), ACCELERON-XP-01 (Non-Aggregate Mode)Stateless Data Plane Test A SM1000XMV12X-01, LM1000STXS4, LM1000STXS4-256, LM1000TXS4, LM1000STXR4, OLM1000STXS24, LM1000SFPS4, LSM1000XMS12-01, LSM1000XMSR12-01, LSM1000XMV4-01, LSM1000XMVR4-01, LSM1000XMV8-01, LSM1000XMVR8-01, LSM1000XMV12-01, LSM1000XMVR12-01, LSM1000XMV16-01, LSM1000XMVR16-01, ACCELERON-NP-01 (Non-Aggregate Mode), ACCELERON-XP-01 (Non-Aggregate Mode)Application Traffic ASM1000XMV12X-01, LM1000STXS4, LM1000STXS4-256, LM1000TXS4, LM1000SFPS4, ALM1000T8, CPM1000T8, LSM1000XMS12-01, LSM1000XMV4-01, LSM1000XMV8-01, LSM1000XMV12-01, LSM1000XMV16-01OC192 SONET Control / Stateless Data Plane Testing MSM10G1-01, MSM10G1-02OC48 SONET Control / Stateless Data Plane Testing MSM2.5G1-01OC3/12 SONET/A TM Control / Stateless Data Plane Testing LM622MR, LSM622MR-512Load modules with 32MB or less of memory are not supported by IxNetwork 5.30 EA SP5 Patch1.There are several models of Ixia OC-192 and 10G Ethernet modules in thiscategory. Memory upgrades are available:- TRI-045: LMOC192c 128MB Memory Upgrade- TRI-046: LM10GE 128 MB Memory UpgradePlease contact Ixia for details.LicensingIxNetwork 5.30 EA SP5 Patch1 requires that a license for its use be installed for eachchassis used by IxNetwork. That license may be installed on each chassis or on aserver on your network, referred to as the central license server.NOTE: IxOS 5.00 SP2 and later versions of IxOS also require a license. Pleaseread the IxOS release notes for license operation and installationinstructions.IxNetwork 5.30 EA SP5 Patch1 ships with Ixia Licensing 2.70 EA SP1.Installing a LicenseIf you wish to use a central license server, make sure to install the Licensing Package on that server. This can be downloaded from the Ixia Support website.If you are upgrading from an earlier version of IxNetwork or IxRouter or are evaluating IxNetwork, please jump ahead to "Using a Temporary License".If this is a new installation of IxNetwork, you should have received an emailwith your Registration Number and Password. If you have not received it yet, please jump ahead to "Using a Temporary License".Your license is installed using the Ixia Registration Utility (IRU) from thestart menu (Start->Ixia->Licensing->IRU). You may run the IRU from the chassisor from any Windows host connected to the chassis. Select the Register choiceand press the Start button. Follow the instructions on the screen. In Step 2,enter the name or IP address of the chassis that the license will apply to. Instep 3, if you are using a central license server, select 'No' and enter the nameof the license server. If you are not using a central license server, select'Yes' instead.Using a License ServerIf you will be using a central license server with IxNetwork, make sure to setthe name of the server in IxNetwork's Settings->Preferences menu choice.To allow use of a central license server by the Tcl API, a new system environment variable "IXN_LICENSE_SERVER" must be set on the client PC. If you are running your Tcl program on a UNIX client, the environment variable must be set on the host running the Tcl Server. Environment variables are set on a UNIX host through the user's shell initialization script. Environment variables are set on a Windows host by using the following instructions:1. Right-click on the My Computer icon on the desktop and then left-click onProperties.2. Choose the Advanced tab from the System Properties dialog box.3. Press the Environment Variable button at the bottom of the page.4. In either the "User variables for..." or "System variables" list,if IXN_LICENSE_SERVER does not exist in the list, press New, otherwise pressEdit.5. The name of the variable should be IXN_LICENSE_SERVER and the value should bethe name or IP address of the license server machine.Updating LicensesIxia has made changes to its licensing technology to minimize license update requirements. In the past license updates were required with every software upgrade. Moving forward license updates will be required at most once every year when software maintenance is renewed.In order to move to this new licensing paradigm, current users of IxNetwork willneed to update their existing licenses once. For some customers (if you boughtor renewed maintenance for IxNetwork in the first couple of months of 2007) this process will not be necessary.The process to update a license is as follows:1. Run the Ixia Registration Utility (IRU) from the start menu (Start->Ixia->Licensing->IRU).2. You may run the IRU from the chassis or from any Windows host connected tothe chassis.3. Select the Update option and follow the instructions on the screen tocomplete this process.Using a Temporary LicenseIt is possible to use IxNetwork for a period of time prior to installation of a permanent license through the use of a temporary license. When you first connect IxNetwork to a chassis, if there is no license found for the chassis, you willbe offered the opportunity to install a temporary license. A permanent licenseshould be installed before the expiration of the temporary license. You willreceive warnings from IxNetwork prior to the expiration of the temporary license.Installing Licensing SoftwareThe Ixia licensing package is installed as part of the IxNetwork server component installation. In some cases you will receive the following message:"In order for Ixia licensing software to work correctly, it will be necessaryto make a change to your system. If you are connected to the Internet, all ofyour licenses for this chassis will automatically be adjusted. If not, pleasefollow the instructions in the Release Notes prior to rebooting.Other, non-Ixia applications may require re-licensing."If you receive this message and your computer is not connected to the Internet,please use the following instructions after rebooting:1) Using the IRU (Start->Ixia->Licensing->IRU):a. Use the Manage Licenses choice to identify all of the licenses on thechassis.b. For each:i. Find your original registration emails.ii. Deregister all of the licenses using the IRU's Deregister function.2) For each of the licenses identified in 1a:a. Register the license using the IRU's Register function.Installation NotesUpgrading from a release prior to IXOS 5.10 SP2To ensure proper operation of an Ixia chassis with IxOS 5.10 EA SP3 or later versionsof IxOS 5.10 EA, prior to installing this release you must un-install all previousversions of Ixia applications, Ixia StatEngine, Ixia StatEngine PCPU packages and IxOS. You should use the Add/Remove utility in the Windows Control Panel. After theun-installations are complete the chassis must be rebooted.Prerequisite Installation NotesAs part of the IxNetwork installation, the installer installs Microsoft SQL2005 Express, Microsoft .Net Framework 1.1 SP1 and Microsoft .Net Framework 2.0.If you experience any issue related to the installation of these prerequisites,please refer to the following notes.NOTE: During installation you may be presented with a error dialog declaring a 1935 error has occurred. One possible cause of this is the presenceof anti-adware or anti-virus software running on the target machine. Pleasedisable these applications prior to your next installation attempt.NOTE: IxNetwork requires Microsoft .NET 1.1 SP1 and 2.0. This can take several minutes to install.NOTE: Installation of Microsoft .Net 1.1 SP1 Framework may fail on Windows 2003 Server. Please refer to the following Microsoft knowledgebase item toattempt resolution: 830646.NOTE: Installation of .NET Framework service packs is not completed if you first install security update MS05-004. Please refer to the following Microsoftknowledgebase item to attempt resolution: 899619.NOTE: If you receive a "Microsoft .NET Framework 1.1 Service Pack 1 (KB867460) cannot be installed" error message when you install the .NET Framework1.1 Service Pack 1. Please refer to the following Microsoftknowledgebase item to attempt resolution: 889109.IxNetwork InstallationIxNetwork has two components. The 'chassis' component needs to be installed on the Ixia chassis being used. The 'client' component needs to be installed on the user workstation where the IxNetwork GUI will be run. The installer will determinewhich is appropriate depending on which IxOS components are installed. Generally, when IxServer is installed, the IxNetwork 'chassis' component is installed.It is also required to install IxOS before installing the IxNetwork 'chassis' component.IxNetwork Download from Ixia WebsiteIxNetwork is available either on a CD-ROM or as a download from the Ixia website.1. Download IxNetwork software from the Ixia website to an Ixia chassis orclient PC. The installer package is in the form of a self-extracting ZIPfile. To unzip the file, double-click on the file from within WindowsExplorer.2. Follow the on-screen instructions provided by the installer.NOTE: If you are upgrading from a CD-ROM, the installer will be launched automatically. The files on the CD-ROM will be the same files as the onesunzipped by the above process.Chassis Installation RequirementsWhen installing IxNetwork 5.30 EA SP5 Patch1 on a chassis, a minimum of 512MB of installed RAM and 200MB of free disk space on Drive C: is required. In addition,be sure to have 700MB of temporary space available. In heavily-loaded chassis configurations, it is recommended to have 1GB RAM installed on the chassis.If your chassis does not meet these requirements, please contact Customer Supportat support@ or 1-877-FOR-IXIA about appropriate upgrades.NOTE: When installing from CD, some virus scanning configurations presenta malicious code alert during execution of the Windows autorun feature. Ifthis occurs, right-click the CD-ROM drive icon in Explorer and 'Explore'the CD. At the root of the CD, double-click on the index.htm file.NOTE: IxNetwork installs the Ixia Stat Engine component. This component is shared by other Ixia applications. It can be manually uninstalled from thetarget machine by using the Windows Add/Remove Programs applet.The following sequence must be followed exactly for the setup to work properlyon Ixia chassis.1. Uninstall any previous versions of IxNetwork and IxOS and restart thechassis.2. Install the required IxOS version.3. Install IxNetwork, and the IxNetwork installer will automatically install theChassis Component. The client component of IxNetwork cannot be installed onthe Ixia Chassis.4. Restart IxServer.Client Installation RequirementsWhen installing IxNetwork 5.30 EA SP5 Patch1 on a client computer, a minimum of 1GB RAM, an Intel P4 Processor (or equivalent), and 500MB of free disk space on DriveC: is required. In addition, be sure to have 200MB of temporary space available.The minimum recommended display resolution is 1024x768, with a DPI setting of Normal size (96 dpi). For configurations involving large port counts , a minimum of 2GB RAMis recommended for the IxNetwork 'client'.Operating System Support* Windows 2000 Professional SP4(US English only)* Windows XP Professional SP2(US English only)* Windows 2003 Server (US English Only)* Windows Vista 32-bit (US English Only)* Linux Kernel 2.2.14, 2.2.15, 2.4.20 (Mandrake 7.2, RedHat 6.2, RedHat 7.0,RedHat 9.0) - Tcl API support only* Solaris 7 (SunOS 5.7), Solaris 8 (SunOS 5.8), Solaris 9 (SunOS 5.9) - Tcl API support onlyThe following sequence must be followed exactly for the setup to work properly on a client PC:1. Uninstall any previous versions of IxNetwork and restart the PC.2. Install IxNetwork. The IxNetwork installer will install only the Clientcomponent on the user PC.UNIX Installation NotesTcl API support on UNIX operating systems is for the Tcl API only.Other versions of Win32, Linux and Solaris platforms may operate properly, but they are not officially supported.To obtain build or install scripts for UNIX platforms not listed above, please contact Customer Support at support@ or 1-877-FOR-IXIA.UNIX Tcl Client Installation NotesIn order to run the GUI installer, your client machine must be configured withan operational X-windows server.Be sure to set your DISPLAY environment variable to the host name or IP address of the client machine on which you want the installer GUI to display. Below are examples for setting the DISPLAY environmental variable using various shell environments. If you need environment configuration assistance beyond this, please consult your System Administrator.// enable connections to X Serverxhost + or xhost [remote hostname]// set DISPLAY environment variable// determine shellecho $SHELL// depending on what shell you use - Bourne shell (bsh or sh),// Bash (bash - Bourne shell again), C shell (csh) or Korn shell (ksh);// set DISPLAY environment variable:// bash:export DISPLAY=hostname:0// bsh or kshDISPLAY=hostname:0export DISPLAY// csh:setenv DISPLAY hostname:0If you are updating an existing installation, be sure to run the installer as thesame user which initially installed the software.Always run the uninstaller prior to removing any files manually.If installing as root and the install location is a network-mounted filesystem, ensure root has write permission to the file system prior to startingthe installer.Tcl/Tk Support for Client ApplicationsInstallation of Tcl Server is required to support execution of UNIX-based legacy Tcl scripts. Installation of Tcl Server is not required to support execution of UNIX-based IxNetwork API (new) Tcl scripting, but utilizes a IxNet GUI client started inTcl Server mode. Please refer to the IxNetwork documentation for guidance on its usage.How to Report ProblemsNorth America Customer Support Hours: 6:00am PST to 6:00pm PSTEmail: support@Phone: Toll Free within USA:1-877-367-4942, Option #1 for SupportFrom outside the USA:1-818-871-1800, Option #1 for Supporte-Fax: 1-818-449-0992Europe, Middle East, and Africa Customer Support Hours: 07:00 to 17:30 GMT Email: eurosupport@Phone: +44-1628-405797India Customer Support Hours: 09:00 to 17:30 local timeEmail: support-india@Phone: +91-80-22161000Asia Pacific Customer Support Hours: 09:00 to 17:30 local time (Singapore) Email: support-asiapac@Phone: +65-6332-0126Fax: +65-6332-0127Additional DocumentationPlease refer to our website at /library. PDF and HTMLversions of all documentation are available there.You will be required to provide a login and password to enter this section ofthe web site. If you do not have the username and password, please forward yourrequest to mailto:support@.What's New in IxNetwork5.30 EA SP5 Patch1 FeaturesIxNetwork-Load ModuleSupport added for the new ACCELERON-NP and ACCELERON-XP Load Modules in 1GigE Non-Aggregate Mode。

用户使用手册客户服务WestlawNext技术支持与检索协助(24小时客服)如有任何关于WestlawNext的一般及技术问题,请拨打客服电话1-800-937-8529或者发送邮件到West.WLNextTech@。

如需要关于WestlawNext的检索协助,请拨打支持律师的电话1-800-733-2889或者发送邮件到West.WestlawNextResearch@。

付费与账户服务如需要付费与账户方面的帮助,请拨打客服电话1-800-328-4880或者发送邮件到West.WestlawNextCustServ@。

有关付费与账户服务,也可以访问/support.访问支持关于汤森路透公司的信息访问规定,请访问/accessibility.参考材料关于参考材料,请访问/guides. WestlawNext也提供在线帮助。

本用户手册的信息于2013年八月校准ALR, Am Jur, KeyCite, United States Code Annotated, USCA, West Key Number System, WestlawNext, 和West Search是West Publishing Corporation 的注册商标。

Case Notebook是汤森路透加拿大有限公司的注册商标。

Amazon Kindle是亚马逊科技有限公司的注册商标。

Google是谷歌有限公司的注册商标。

FireFox是莫斯拉基金的注册商标。

iPad, iTunes, Mac, and Safari是苹果有限公司的注册商标。

Microsoft, Internet Explorer, 和Windows是微软公司的注册商标。

汤森路透版权所有。

汤森路透610 Opperman DriveEagan, MN 55123-1396目录登录WestlawNext (4)选择客户代码 (5)通过全文搜索引擎完成检索任务 (8)检索法律问题 (8)使用WestSearch搜索引擎进行搜索 (9)钥匙码检索系统(West Key Number System) (10)使用Boolean术语与连接符检索 (11)高级检索 (12)浏览框(Browse)内容:案例(Cases) (13)浏览框(Browse)内容:法令(Statutes) (14)内容类型:案例 (17)文献页面 (19)概述 (19)工作流程工具(Workflow Tools) (21)利用关键引用(KeyCite)核查引用 (23)检查引用了该案例的相关资源 (25)文献传送 (26)项目文件夹 (27)文件夹概览 (28)历史 (30)提醒(Alerts) (31)偏好设置 (32)帮助与技术支持 (33)系统要求 (34)欢迎使用WestlawNext iPad App (35)登录WestlawNext完成以下步骤以登陆WestlawNext1.登录2.在OnePass Usename和Password的文本框内输入用户名与密码∙如果希望每次登录的时候能够自动输入用户名,点击Remember my username,。

消息中间件3.6iXCom瘦客户端使用指南版权说明上海宝信软件股份有限公司版权所有,并保留对本文档及本声明的最终解释权和修改权。

本文档的版权归上海宝信软件股份有限公司所有。

未得到上海宝信软件股份有限公司的书面许可,任何人不得以任何方式或形式对本文档内的任何部分进行复制、摘录、备份、修改、传播、翻译成其它语言、将其全部或部分用于商业用途。

上海宝信软件股份有限公司版权所有1998-2012 All Rights Reserved.目录1概述 (1)1.1目的 (1)1.2产品功能介绍 (1)1.3词汇表...................................................................................................... 错误!未定义书签。

2软件结构 (1)3配置说明 (2)4接口说明 (4)5使用说明 (4)5.1UNIX平台 (4)5.2WINDOWS平台 (5)6附录-接口代码示例 (6)7联系方式 (7)1概述1.1目的iXcom产品系列是宝信自主研发的外部通讯中间件产品,目前已经到3.6版本。

该产品系列在宝信所承担的项目中普遍的并越来越多的被采用,且07年已形成体系对外销售。

为了更好的支撑宝信所承担的项目,需要对iXcom 进行持续的升级,以逐步完善其功能,提高成熟度和产品化程度,满足业务不断变化的需求,并尝试进入国内的消息中间件市场,提高宝信在系统集成领域的竞争力和知名度。

iXcom 新版本将继续延续iXcom产品系列的消息中间件路线,向下兼容前期版本,并修正优化前期版本的一些数据交换区、进程并发处理问题,提高产品运行的稳定性,重点升级产品的数据处理速度,根据市场的需要和趋势为新版本增添新功能,扩展系统接口,重构管理及监控界面。

瘦客户端是宝信消息中间件iXCom的附带简易版本,具有功能简化、协议固定、配置简单、资源消耗小、消息处理速度快、多平台支持等特点,适用于系统终端无数据库环境与完整iXCom 进行消息通信。

SuperSonix®-NGSoftware Update/Reinstall Instructions1.0 INTRODUCTION (1)2.0 REQUIREMENTS (1)3.0 UPDATING/REINSTALLING THE SOFTWARE (1)3.1 F ROM N ETWORK (O VER THE I NTERNET ) (2)3.2 F ROM USB D RIVE (T HROUGH A SOFTWARE FILE DOWNLOAD ) (2)4.0 FIRMWARE UPDATE ....................................................................................................... 3 1.0 IntroductionThe latest SuperSonix-NG software, manual, and readme file (which contains the software release notes) can always be found on the SuperSonix-NG support page at:/knowledgebase/supersonix-ng .The SuperSonix-NG software release may contain both a software and firmware update. This document details how to update/reinstall the software and firmware. 2.0 RequirementsTo perform the software update/reinstall, one of the following is required:• The SuperSonix-NG connected to a network with Internet access (for updating “FROM NETWORK”), or• The SuperSonix-NG with your own USB flash drive. The USB flash drive must be formatted FAT32 or NTFS (for updating “FROM USB DRIVE”) 3.0 Updating/Reinstalling the SoftwareThere are two methods available to update/reinstall the SuperSonix-NG software:A. FROM NETWORK – Over the Internet through a network connection.B. FROM USB DRIVE –Through a software file download onto a USB flash drive.3.1 From Network (Over the Internet)The SuperSonix-NG software can be updated/reinstalled by connecting the SuperSonix-NG to a network with Internet access.1. Connect the SuperSonix-NG to a network with Internet access and turn theSuperSonix-NG on.2. From the main menu on the SuperSonix-NG, locate and tap the SoftwareUpdates icon on the left side.3. Select From Network . The SuperSonix-NG will check for software on Logicube’sserver. After a few seconds, one of the following messages will appear:•Newer version available – This message will appear if there is a newer software version found. Tap the OK icon to continue. •Up to date – This message will appear if the software version found is the same as the version currently installed. Tap the OK icon to continue. • No new version found – This message will appear if the SuperSonix-NGdoes not have any internet access. Tap the OK icon to continue. If thismessage is seen, try the following:i. Go to the About tab in the Statistics screen and check the N/WInterfaces to make sure the SuperSonix-NG is connected to anetwork and has a valid IPAddress , orii. Make sure the network the SuperSonix-NG is connected to hasInternet access, oriii.Try using the “From USB DRIVE” option (see Section 3.2). 4. Tap the Update icon to begin the update/reinstall. The SuperSonix-NG shouldbegin the update/reinstall process. Do not interrupt this process. It may takeseveral minutes. Once completed, a screen will appear stating the update iscomplete and will prompt you to turn the unit off then back on.5. Turn the SuperSonix-NG off. Wait at least 5 seconds then turn the SuperSonix-NGback on.6.Verify the software version by going to the Software Updates screen then go tosection 4.0 Firmware Update to check if there is a firmware update available.3.2 From USB Drive (Through a software file download)Aside from the network option, the latest software can also be downloaded fromLogicube’s website and be placed onto a USB flash drive to perform the softwareupdate/reinstall. It is recommended to use an empty USB flash drive.ing a computer, download the latest software from the SuperSonix-NG productsupport page at /knowledgebase/supersonix-ng.2.Extract the contents of the downloaded zip file to the root of the USB flash drive.3.Turn the SuperSonix-NG on. When the main software screen appears, connectthe USB flash drive (that has the extracted software from step 2) to the USB_Mport (the USB port on the left side).4.From the main menu on the SuperSonix-NG, locate and tap the SoftwareUpdates icon on the left side.5.Select From USB Drive. The SuperSonix-NG will check for the version of thesoftware on the USB drive. After a few seconds, one of the following messagesshould appear:•Software found –A software version is found on the USB flash drive. Tapthe OK icon to continue.•No new version found –The SuperSonix-NG did not find any softwareon the USB flash drive or could not detect the USB flash drive. If thismessage is seen, try the following:i.Make sure the correct software was downloaded and the fileswere extracted to the root of the USB flash drive, orii.Format and use a different USB flash drive, oriii.Try using the “From Network” option (see Section 3.1)6.Tap the Update icon to begin the update/reinstall. The SuperSonix-NG shouldbegin the update/reinstall process. Do not interrupt this process. It may takeseveral minutes. Once completed, a screen will appear stating the update iscomplete and will prompt you to turn the unit off then back on.7.Turn the SuperSonix-NG off. Wait at least 5 seconds then turn the SuperSonix-NGback on.8.Verify the software version by going to the Software Updates screen then go tosection 4.0 Firmware Update to check if there is a firmware update available.4.0 Firmware UpdateSuperSonix-NG software releases may contain a firmware update. This section provides instructions on how to check if a firmware update is required, and how to perform the firmware update.1.After the software is updated/reinstalled on the SuperSonix-NG, locate and tap the SoftwareUpdates icon on the left side.2.Tap the “Firmware Update” tab. One of two screens will appear:•FIRMWARE UPGRADE AVAILABLE– Tap the Update icon. A message will appear: “FIRMWARE UPDATE COULD TAKE UP TO A FEW MINUTES TO COMPLETE; PLEASE DO NOT INTERRUPT POWER DURING THIS TIME. ON COMPLETION THE UNIT WILL AUTO-RESTART AND CONFIRM THE UPDATE.” Tap the OK icon to start the firmware update process.•FIRMWARE UPGRADE NOT AVAILABLE –This message will appear if the device does not require a firmware update. No further action is necessary if this message appears.。

(机器翻译成中文)Xillybus host application programming guide for LinuxXillybus Ltd.Version3.0本文档已由计算机自动翻译,可能会导致语言不清晰。

与原始文件相比,该文件也可能略微过时。

如果可能,请参阅英文文档。

This document has been automatically translated from En-glish by a computer,which may result in unclear language.This document may also be slightly outdated in relation tothe original.If possible,please refer to the document in English.Xillybus Ltd.(机器翻译成中文) 1介绍52同步streams与异步streams72.1概述 (7)2.2异步streams的动机 (7)2.3Streams从FPGA到host (8)2.4Streams从host到FPGA (8)2.5不确定性与latency (10)3I/O编程实践113.1概述 (11)3.2读取数据指南 (11)3.3数据写入指南 (13)3.4在异步downstreams上执行flush (15)3.5select()和nonblocking I/O (17)3.6监控driver的buffers中的数据量 (18)3.7XillyUSB:需要监控物理data link的质量 (18)4高速连续I/O204.1基础知识 (20)4.2大driver的buffers (21)4.3user space中的RAM buffers (22)4.4fifo.c演示应用程序概述 (23)4.5fifo.c改装笔记 (24)4.6RAM FIFO功能 (24)4.6.1fifo_init() (25)4.6.2fifo_destroy() (25)4.6.3fifo_request_drain() (25)4.6.4fifo_drained() (26)4.6.5fifo_request_write() (26)4.6.6fifo_wrote() (27)Xillybus host application programming guide for Linux2Xillybus Ltd.(机器翻译成中文)4.6.7fifo_done() (27)4.6.8FIFO_BACKOFF define variable (27)5循环frame buffers285.1介绍 (28)5.2改编FIFO示例代码 (28)5.3丢弃和重复frames (29)6具体的编程技术316.1Seekable streams (31)6.2双向同步streams (33)6.3分组通信 (33)6.4模拟hardware interrupts (34)6.5Timeout (35)6.6Coprocessing/Hardware acceleration (38)A内部结构:streams是如何实现的40A.1介绍 (40)A.2“Classic”DMA与Xillybus (40)A.3FPGA至host(upstream) (41)A.3.1概述 (41)A.3.2#1阶段:Application logic到中间FIFO (41)A.3.3#2阶段:中间FIFO到DMA buffer (42)A.3.4Stage#3:DMA buffer到用户软件应用程序 (42)A.3.5buffers部分满载交接条件 (43)A.3.6例子 (44)A.3.7实际结论 (45)A.4Host至FPGA(downstream) (46)A.4.1概述 (46)A.4.2Stage#1:DMA buffer的用户软件应用程序 (46)A.4.3#2阶段:DMA buffer到中间FIFO (47)Xillybus host application programming guide for Linux3Xillybus Ltd.(机器翻译成中文)A.4.4#3阶段:中间FIFO到application logic (48)A.4.5一个例子 (48)A.4.6实际结论 (48)Xillybus host application programming guide for Linux4Xillybus Ltd.(机器翻译成中文)1介绍Xillybus旨在为Linux host提供一个简单而知名的界面,具有自然和预期的行为。

Course NumberCCPS45Course PurposeThis blended-media course introduces students to the communication capabilities of RSLinx® software through hands-on practice and the interactive simulations of COURSE AGENDADAY 1• Setting Up an SLC 500 System on a DH+ Network • Troubleshooting Program Flow and Interrupt Routines • Troubleshooting STI Routines• Troubleshooting DII RoutinesDAY 2SLC 500 Processors SLC 500 and RSLogix 500 Advanced Maintenance and TroubleshootingWHO SHOULD ATTENDIndividuals who are responsible for maintaining and troubleshooting advanced SLC 500 applications using RSLogix 500® software should attend this course.PREREQUISITESTo successfully complete this course, the following prerequisites are required:• Experience maintaining electrically controlled systems• Experience operating a personal computer within a Microsoft Windows 2000 or Windows XP environment • Completion of the SLC 500 and RSLogix 500Maintenanceand Troubleshooting (Course No. CCPS43)STUDENT MATERIALSTo enhance and facilitate the students’ learningexperiences, the following materials are provided as part of the course package:• Student Manual– Includes the key concepts, definitions, examples, and activities presented in this course • Lab Book–Provides learning activities and hands-on practice. Solutions are included after each exercise for immediate feedback • RSLogix 500 and SLC 500 Procedures Guide– Provides all the steps required to complete common RSLogix 500 software tasks, including the tasks in the exercises. By following the procedures in this job aid, you can immediately apply what is learned in the course to your own job.• SLC 500 and RSLogix 500 Troubleshooting Guide –Contains diagnostic algorithms that efficiently lead the user to possible maintenance and troubleshooting solutionsHANDS-ON PRACTICEDiagnostic and problem-solving skills are sharpened through hands-on exercises using a variety of hardware devices and software applications, including SLC 500 processors, Universal I/O Simulators, PanelView terminals, RSView32 applications, and the Automated System Trainer, a complete hardware system containing real-world inputs and outputs.NEXT LEARNING LEVELOnce you have mastered the maintaining andtroubleshooting skills covered in this course, you may want to expand your application skills and knowledge by attending a maintaining and troubleshooting course focusing on networks.COURSE LENGTH This is a four-day course.Allen-Bradley, Logix5000, PanelView, RSLogix 500, RSView and SLC are trademarks of Rockwell Automation, Inc.Trademarks not belonging to Rockwell Automation are property of their respective companies. Publication GMST10-PP211E -EN-E – January 2020 | Supersedes Publication GMST10-PP211D -EN-E – January 2018Copyright © 2020 Rockwell Automation, Inc. All Rights Reserved. Printed in USA.To be respectful of the environment, Rockwell Automation is transitioning some of its training courses to a paperless format. Students are asked tocomplete downloads and bring personal devices to these classes. A full list of digital/paperless courses is currently available through your local distributor.。

本文部分内容来自网络整理,本司不为其真实性负责,如有异议或侵权请及时联系,本司将立即删除!== 本文为word格式,下载后可方便编辑和修改! ==诺西基本操作指导书篇一:诺西基本操作指导书--李名杰诺西基本操作指导书诺西远程客户端登陆1、电脑IP地址修改2、打开电脑远程连接(快捷键:Windows+R)3、编辑远程桌面备注:远程客户端最大LISENCE用户数未10个,超过该数量则无法登陆。

登陆ENODEB,查看、修改参数1、登陆BTS Site Manager2、登陆界面后可查看小区状态、告警及告警原因3、点击绿色灯泡,查看CI、PCI、带宽、功率上下行中心频点等4、进入Site Manager后,点击最左边的Commissioning,进入配置介面。

勾选BTS site下BTS,选择Reconfiguration,点击Go to Radio Netwok Configuration page5、查看、修改LNBTS、LNCEL、LNADJ级参数附件为各参数所在级及简介:RL35_Parameter.xls6、功率、TM模式查看、修改篇二:诺西操作快速入门手册NOKIA系统操作快速入门手册1 如果取话务报表 .................................................................. (2)1.1.1 如何通过NOKIA OMC网管来取话务报表 (2)1.1.2 如何通过超级终端来取话务报表 (4)如何提取网络中得基本参数 .................................................................. . (4)基本操作命令 .................................................................. . (5)3.1.1 锁定/解锁小区及载波 .................................................................. .. (5)3.1.2 修改某个小区的频点 .................................................................. (6)3.1.3 如何创建/删除邻区关系 .................................................................. . (6)3.1.4 修改邻区关系相关参数 .................................................................. .. (6)3.1.5 修改某个小区的BSIC码 .................................................................. .. (6)3.1.6 如何创建及删除载波 .................................................................. (7)3.1.7 如何创建及删除BTS ................................................................. (7)3.1.8 如何查看告警信息 .................................................................. . (9)3.1.9 如何查询传输故障 .................................................................. .. (10)MSC侧的相关基本操作 .................................................................. .. (11)4.1.1 如果查看交换数据(LAC/CI)是否创建并放开 (11)4.1.2 如何查看BSC号(MSC中定义的) (11)4.1.3 如何查看或修改MSC下相关功能是否开启 ............................................... 11 2 3 41 如何取话务报表NOKIA话务报表可以通过两种方式,一种是直接通过NOKIA OMC网管来取,另一种可以通过超级终端来取,以下对每个方式进行描述:1.1.1 如何通过NOKIA OMC网管来取话务报表目前NOKIA OMC可以利用XMANAGER软件来进入,需要配置IP地址即可,进入后得主界面为如下图示:(NOKIA OMC 主界面)在以上图片得左上角有个“人”图标就是取报表得按钮,双击它即可进入如下界面:然后输入用户名及密码即可进入报表提取界面了(其中用户名及密码需要向局方咨询)在上图中得取报表主界面中键入“6”,就可以取所想要得报表了,如800报表、163报表、182报表等等。

实验4 创建基本应用程序Targeting MicroBlaze on the Spartan-3E Starter Kit创建基本的应用程序实验: PowerPC 处理器实验介绍本实验指导我们通过处理器创建一个基本的应用程序。

应用程序将 控制Spartan-3E starter kit 上的LEDs 。

你将添加一个 OPB BRAM 控制器,和修改OPB BRAM 中原有的连接部分插入文本。

最后你将会发现系统就像你当初设计的一样运行。

实验目的完成本次实验,你将具有以下会达到以下目的: • 添加一个外部 RAM 控制器• 编写一个访问外围设备IP 的基本应用程序 • 更新连接文本• 划分可执行的部分到 LMB 和OPB 存储空间 • 生成一个位文件• 下载位文件并在 Spartan-3E 开发板上检验实验步骤前三个实验为处理器系统定义了硬件。

这个实验由几个步骤组成,包括添加一个存储控制器,编写一个访问Spartan-3E 开发板上的LED 的基本应用软件。

以下给出的每个总体步骤下面,你都可以发现有一步一步的详细操作说明和的图解说明。

如果你能完成某一步骤,你可以跳过那些详细的说明,直接进入下一步。

更新项目 步骤1创建在 d:\Lab\下创建 lab4mb 文件夹。

可以按照前三个实验的流程创建一个工程,也可以直接把lab3内的文件拷贝到此目录。

启动 Xilinx Platform Studio (XPS) ,打开C:\xup\embedded\labs\lab4工程 (如果你想继续你的设计)。

n 如果你想继续你的设计,那么C:\xup\embedded\ppc\labs 目录下新建一个lab4文件夹,在拷贝lab3的文件到此文件夹。

o 点击 Start → Programs → Xilinx Platform Studio 8.2i → Xilinx Platform Studio 打开XPSStep 1: Update the designStep 2: Create aBSPStep 3: Update a Basic C ProgramStep 4: LinkerScriptp选择Open Recent Project,点击 OK,打开C:xup\embedded\ppc\labs\lab4q选择system.xmp打开工程r从IP目录中添加下列IP到嵌入式设计中•opb_bram_if_cntlr 1.00.a•bram_block 1.00.as更改实例的名称,对照下图建立连接。

图4-1 添加内部 OPB 存储控制器t在addresses 表中,选择为opb_bram控制器分配8K的空间,并点击Generate Addresses(生成地址)图4-2 BRAM内存控制器的地址和存储空间大小的详细说明创建一个BSP步骤2在 Software Platform Settings 下查看各项设置。

BSP 是基于设计中的外设创建的 。

n 选择 Software → Software Platform Settings图4-3 microblaze_0 实例的Software Platform Settings (软件设置)对话框 注意:你不但可以选择系统中的各个外设的驱动,还可以选择它们的内核和操作系统。

另外,如果要用到库的话,还可以选择库文件。

Step 1: Update thedesignStep 2: Create aBSPStep 3: Update a Basic C ProgramStep 4: LinkerScripto 选择 Software Platform 标签,检校下列参数。

:图4-4 PPC405_0 实例的Software Platform Parameters (软件参数)p 选择 OS and Libraries 标签,确认 stdin 和 stdout 选择 RS232_DCE .,microblaze_exceptions 和 enable_sw_intrusive_profiling 的Current Value 一项选 false ,其它的都按下图所示的设置。

图4-5 OS 数据参数q 在Drivers (驱动)部分,检查确认系统中的各个外设的驱动。

Figure 4-6. Driver Configurationr在Interrupt Handlers(中断管理)部分,注意所有的外设都应该是没有中断,因为本设计中没有外设支持中断。

s点击OK 保存设置。

生成 BSP.n 在XPS 中,双击 System 图标下的 system.mss 打开工程的MSS 文件。

图4-7 System 标签XPS 把SPS(Software Platform Settings)中设置的参数都分类写到 system.mss 文件中。

o 查看 MSS 文件,你会发现文件中的参数都是和SPS 中设置的相对应,关闭 system.mss文件。

p 选择Software → Generate Libraries and BSPs 或者点击,生成BSP本操作是在system.mss 中运行LibGen ,生成BSP 库文件。

1. 列出在lab4文件夹中的microblaze_0 文件夹下创建的子文件夹,它们的内容和它们的用途。

________________________________________________________________________________________________________________________________________________________________________________________________?更新基本 C 文件 Step 3更新 Lab 3中的C 程序,实现LED 显示DIP 的开关设置。

n 在 Applications 标签下,拷贝lab3.c 中的TestApp_Memory 工程到 lab4.c注意, lab4.c 和lab3.c 是一样的,你将通过添加代码扩展 功能,实现LEDs 的显示开关控制。

.o 在System Assembly View (系统体视图)中,右击 LEDs_8Bit 外设,选择Driver:gpio_v2_01_a J View API Documentation图4-8 访问外设 API 文件o 在页面的顶部,选择 File List 查看与 GPIO 相关的C 文件和头文件。

p 点击头文件 xgpio.h 查看调用GPIO 可以实现的功能。

在软件应用中必须进行如下操作,才能对GPIO 进行写入: 1) GPIO 初始化 2) 设置数据方向 3)写数据o 找出下列功能的描述:XGpio_Initialize (XGpio *InstancePtr, Xuint16 DeviceId)Step 1: Update the designStep 2: Create aBSPStep 3: Update a Basic C ProgramStep 4: LinkerScript°InstancePtr是 XGpio实例的指针。

指针指向的地址必须通过调用者进行预先分配。

以后通过 XGpio API操作必须由此指针构成。

°DeviceId是XGpio 组件控制的器件的唯一识别号。

通过识别号,可以在调用或升级应用时通过识别号将XGpio类型实例调用到一个特定的器件。

XGpio_SetDataDirection (XGpio * InstancePtr, unsigned Channel, Xuint32 DirectionMask)°InstancePtr是指向将要使用的Xgpio实例的指针。

°Channel是GPIO(1或2)将要工作的信道。

°DirectionMask是离散信号输入输出标志位。

0表示输出,1表示输入。

XGpio_DiscreteWrite (XGpio *InstancePtr, unsigned channel, Xuint32 data){InstancePtr. 是指向将要使用的Xgpio实例的指针。

{Channel是GPIO(1或2)将要工作的信道。

{Data写入离散寄存器中的数据p在Applications 标签页,双击TestApp_Memory项目中microblaze_0 实例的Generated Header: microblaze_0/include/xparameters.h图4-9 双击 Generated Header 文件{xparameters.h 文件中的LibGen,提供对驱动功能调用的测试信息。

{在 xparameters.h 文件中, #define后面的是确定 LEDs_8Bit的外设。

#define XPAR_LEDS_8BIT_DEVICE_ID注意: LEDS_8BIT 是与外设的MHS 文件中指定的实例名称相匹配的。

#define 可以作为 XGpio_Intialize 功能调用使用。

q 如下图所示修改C 语言程序。

图4-10 部分 C 文件r 保存文件 s 点击编译按钮 ,编译程序。

Note: The number might be different链接脚本文件步骤 4分析汇编目标文件和怎样使用objdump有效地链接它们。

打开 Cygwin 页面,执行目标可执行程序,分析输出。

n点击Project → Launch EDK shell 打开Cygwin页面。

o通过cd命令更改路径到C:/xup/embedded/ppc/labs/lab4/TestApp_Memory 。

你可以通过pwd命令检验你的路径。

p在Xygwin 页面窗口下,按提示键入mb-objdump –h executable.elf,列出程序的各个部分,包括各个程序段的起始地址和大小。

Step 1:Update thedesignStep 2:Create aBSPStep 3:Create aBasic CProgramStep 4:LinkerScript图4-11 在OPB BRAM 中.text 目标存放的结果更改文本部分存放的位置,使它存放在LMB存储器中。

重新编译代码,重新执行 objdump命令,分析输出。

n在Applications标签的 Project:TestApp_Memory右击鼠标,选择Generate Linker Script.Note the start address ofthe text section residesin the opb_bram space图4-12 生成链接文本o选择 ilmb_cntlr_dlmb_cntlr 作为指令(.text部分)的存储空间。