第7章 时序逻辑电路

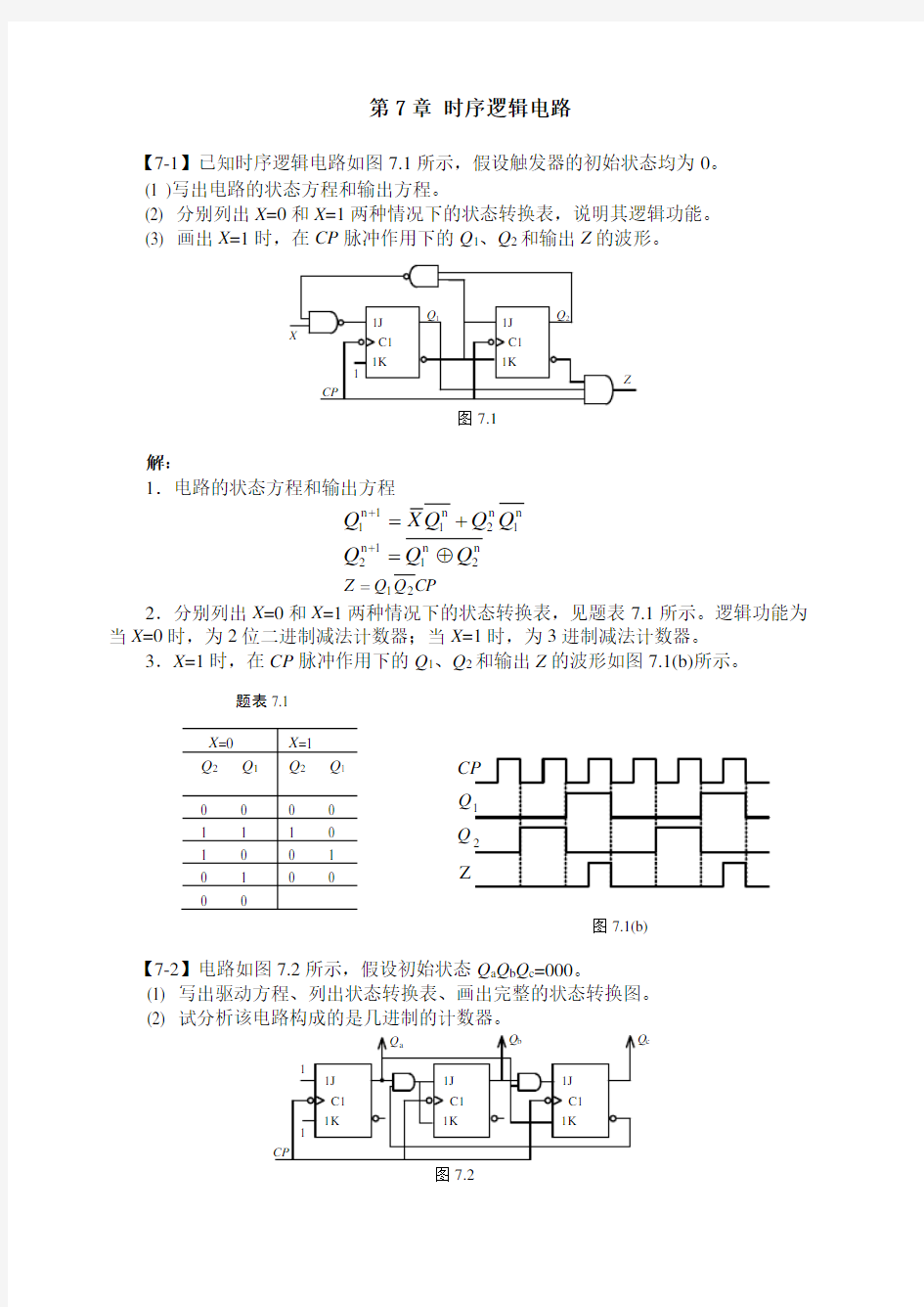

【7-1】已知时序逻辑电路如图7.1所示,假设触发器的初始状态均为0。 (1 )写出电路的状态方程和输出方程。

(2) 分别列出X =0和X =1两种情况下的状态转换表,说明其逻辑功能。 (3) 画出X =1时,在CP 脉冲作用下的Q 1、Q 2和输出Z 的波形。

1J 1K

C11J 1K

C1Q 1

Q 2

CP

X

Z

1

图7.1

解:

1.电路的状态方程和输出方程

n 1n

2n 11n 1Q Q Q X Q +=+ n 2

n 11n 2Q Q Q ⊕=+ CP Q Q Z 21=

2

.分别列出X =0和X =1两种情况下的状态转换表,见题表7.1所示。逻辑功能为 当X =0时,为2位二进制减法计数器;当X =1时,为3进制减法计数器。

3.X =1时,在CP 脉冲作用下的Q 1、Q 2和输出Z 的波形如图7.1(b)所示。

题表7.1

Q Q Z

图7.1(b)

【7-2】电路如图7.2所示,假设初始状态Q a Q b Q c =000。

(1) 写出驱动方程、列出状态转换表、画出完整的状态转换图。 (2) 试分析该电路构成的是几进制的计数器。

Q c

图7.2

解:

1.写出驱动方程

1a a ==K J n

c

n a b b Q Q K J ?== n b n a c Q Q J = n a c Q K = 2.写出状态方程

n a 1n a Q Q =+ n a n a n a n a n c n a 1n b Q Q Q Q Q Q Q +=+ n

c n a n c n b n a 1n b Q Q Q Q Q Q +=+

3.列出状态转换表见题表7.2,状态转换图如图7.2(b)所示。

图7.2(b)

表7.2状态转换表

CP n

a n

b

c Q Q Q 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 1

6 0 0 0

n

4.由FF a 、FF b 和FF c 构成的是六进制的计数器。

【7-3】在二进制异步计数器中,请将正确的进位端或借位端(Q 或Q )填入下表

解:

题表7-3

下降沿触发 由 Q 端引出进位 由Q 端引出借位

触发方式 加法计数器 减法计数器上升沿触发 由Q 端引出进位 由Q 端引出借位

【7-4】电路如图7.4(a)所示,假设初始状态Q 2Q 1Q 0=000。 1. 试分析由FF 1和FF 0构成的是几进制计数器;

2. 说明整个电路为几进制计数器。列出状态转换表,画出完整的状态转换图和CP 作用下的波形图。

1J 1K

C11J 1K

C11J 1K

C1CP

FF1FF2FF0CP

Q 0Q 2

Q 1

(a) (b) 图7.4

解:

1、由FF 1和FF 0构成的是三进制加法计数器(过程从略)

2、整个电路为六进制计数器。状态转换表(略),完整的状态转换图 和CP 作用下的波形图如下图。

CP Q0Q1

Q2

【7-5】某移位寄存器型计数器的状态转换表如表7.5所示。请在图7.5中完成该计数器的逻辑图,可以增加必要的门电路。要求:写出求解步骤、画出完整的状态转换图。(Q 3为高位)

图7.5

解:

(1) 根据状态转换表画次态卡诺图,求出状态方程。

0001111001

0001

1000

0000

00111100

′′′′′′′′

11100111

′′′′′′′′

′′′′′′′′′′′′′′′′′′′′n 1Q n 0Q n 3Q n 2

Q n+13Q n+12Q 1Q 0

Q n+1n+1

n+1n n 310Q Q Q =; n+1n 23Q Q =; n+1n 12Q Q =; n+1n

11Q Q =

(2) 由状态方程写驱动方程。

n n 310D Q Q =; n 23D Q =; n 12D Q =; n 01D Q =

(3) 验证自启动,画完整状态转换图。 电路可自启动。

(4) 电路图如下图。

CP

【7-6】在图7.6(a)所示电路中,由D 触发器构成的六位移位寄存器输出Q 6 Q 5 Q 4 Q 3 Q 2 Q 1的初态为010100,触发器FF 的初态为0,串行输入端D SR =0。请在图7.6 (b)中画出A 、Q 及B 的波形。

CP

CP

(a)

(b)

图7.6

解:波形图如图7.6(b)所示。

CP A Q B

图7.6(b)

【7-7】分析图7.7所示电路,说明它们是多少进制计数器?

Q D 74LS161RCO Q C Q B Q A ET EP D C B A CR LD

CP

CP

1

1

1

(a) (b)

图7.7

解:

图(a),状态转换顺序[Q D Q C Q B Q A ]=0→1→2→3→4→5→6→0,是7进制计数器; 图(b),[Q D Q C Q B Q A ]=6→7→8→9→10→11→12→13→14→15→6,是10进制计数器;

【7-8】分析图7.8所示电路的工作过程

1. 画出对应CP 的输出Q a Q d Q c Q b 的波形和状态转换图(采用二进制码的形式、 Q a 为高位)。

2. 按Q a Q d Q c Q b 顺序电路给出的是什么编码?

3. 按Q d Q c Q b Q a 顺序电路给出的编码又是什么样的?

P

C

图7.8 解:

1 状态转换图为

2按Q a Q d Q c Q b 顺序电路给出的是5421码。 3. 按Q d Q c Q b Q a 顺序电路给出的编码如下

0000→0010→0100→0110→1000→0001→0011→0101→0111→1001→0000

【7-10】试用2片4位二进制计数器74LS160采用清零法和置数法分别实现31进制加法计数器。

解:答案略。

【7-9】图7.9为由集成异步计数器74LS90、74LS93构成的电路,试分别说明它 们是多少进制的计数器。

Q Q C Q D

Q A B 74LS93

CP A

CP B P

C R 0(1)

R 0(2)Q Q C Q D

Q A B 74LS90

CP A CP B

P

C R 0(1)

R 0

(2)S 0(1)S 0(2)

(a) (b)

(c)

图7.9

解:

图(a),状态转换顺序[Q D Q C Q B ]=0→1→2→0,是3进制计数器; 图(b),状态转换顺序[Q D Q C Q B ]=0→1→2→3→0,是4进制计数器; 图(c),是37进制计数器。

【7-11】图7.12所示为一个可变进制计数器。其中74LS138为3线/8线译码器,当S 1=1且032==S S 时,进行译码操作,即当A 2A 1A 0从000到111变化时,71~Y Y 依次被选中而输出低电平。74LS153为四选一数据选择器。试问当MN 为各种不同取值时,可组成几种不同进制的计数器?简述理由。

Y 0Y 1Y 2Y 3Y 4Y 5Y 6Y 7

E 3E 2E 1

B 0B 1B 2

D 0

D 1

D 2D 3

A 0A 1S

L 74LS138

74LS1531J 1K C11J 1K C11J 1K C11J 1K

C1CP

1

Q 1

Q 2

Q 3

Q 4

R

R

R

R

图7.11

解:

4个JK 触发器构成二进制加法计数器,当计数到 [Q 4Q 3Q 2Q 1]=10000时,74LS138满足使能条件,对[Q 3Q 2Q 1]的状态进行译码,译码器的输出Y 经过4选1数据选择器74LS153,在[MN ]的控制下,被选中的Y 信号,以低电平的形式对计数器清零。不同的[MN ]即可改变图7.11所示电路的计数进制,具体见下表。

第8章存储器

【8-1】填空

1.按构成材料的不同,存储器可分为磁芯和半导体存储器两种。磁芯存储器利用

来存储数据;而半导体存储器利用来存储数据。两者相比,前者一般容量较;而后者具有速度的特点。

2.半导体存储器按功能分有和两种。

3.ROM主要由和两部分组成。按照工作方式的不同进行分类,ROM可分为、和三种。

4.某EPROM有8条数据线,13条地址线,则存储容量为。

5.DRAM 速度SRAM,集成度SRAM。

6.DRAM是RAM,工作时(需要,不需要)刷新电路;SRAM是RAM,工作时(需要,不需要)刷新电路。

7. FIFO的中文含义是。

解:

1.正负剩磁,器件的开关状态,大,快。

2.ROM,RAM。

3.地址译码器,存储矩阵,固定内容的ROM 、PROM,EPROM三种。

4.213×8。

5.低于,高于。

6.动态,需要;静态,不需要。

7.先进先出数据存储器。

【8-2】图8.2是16×4位ROM,A3A2A1A0为地址输入,D3D2D1D0为数据输出,试分别写出D3、D2、D1和D0的逻辑表达式。

A

A

A

A

3 2 1 0

图8.2

解:

??

?????

?

?∑=?

=∑==)m(0,5,9,133

12,15)m(3,6,9,12100D A A D D A D

【8-3】用16×4位ROM 做成两个两位二进制数相乘(A 1A 0×B 1B 0)的运算器,列出真值

表,画出存储矩阵的阵列图。 解:

图8.3

【8-4】由一个三位二进制加法计数器和一个ROM 构成的电路如图8.4(a)所示 1.写出输出F 1、F 2和F 3的表达式;

2.画出CP 作用下F 1、F 2和F 3的波形(计数器的初态为”0“)

·CP

Q 2Q 1Q 0F 1 F F 3F 1F 2F 3

计数器地址

译码

器CP

(a) (b)

图8.4

解:

1. ????

????=??+?+??=?+?+?=0

13012012012201212011Q Q F Q Q Q Q Q Q Q Q Q F Q Q Q Q Q Q Q F

2.

CP F1F2F3

图8.4(b )

【8-5】用ROM 实现全加器。

解:

0m 1m 2m 3m 4m 5m 6m 7m

图8.5

第9章 可编程逻辑器件及Verilog 语言

【9-1】简述CPLD 与FPGA 的结构特点? 解:

CPLD 采用了与或逻辑阵列加上输出逻辑单元的结构形式;而FPGA 的电路结构由若干独立的可编程逻辑模块组成,用户可以通过编程将这些模块连接成所需要的数字系统。CPLD 属于粗粒结构,FPGA 属于细粒结构。CPLD 是基于乘积项的可编程结构,而在FPGA 中,其基本逻辑单元LE 是由可编程的查找表(LUT ,Look-Up Table )构成的, LUT 本质上就是一个RAM 。

【9-2】简述手工设计与PLD 设计的流程? 解:

答:手工设计:第一步,设计电路,画出逻辑图;第二步,选择逻辑元器件。第三步,进行正确的连线。

PLD的设计流程:首先根据设计要求写出相应的逻辑表达式,画出设计草图,接着在计算机上利用PLD软件通过原理图输入方式或硬件描述语言(HDL)输入方式输入逻辑设计描述,经计算机仿真验证后,下载到PLD器件中,最后再通过外部实际输入输出对设计进行验证。

【9-3】用PLD器件实现的电路仿真结果如图9.4所示,请指出电路的功能。

(a)

(b)

(c)

图9.4

解:

图P9.4 (a)为二选一数据选择器,图P9.4 (b) 边沿型D触发器,图P9.4 (c)为电平触发D触发器。

【9-4】Verilog语言程序清单如下,写出电路的逻辑功能,并通过QuartusII进行仿真。module count(out,data,load,reset,clk);

output[7:0] out;

input[7:0] data;

input load,clk,reset;

reg[7:0] out;

always @(posedge clk)

begin

if (!reset) out = 8'h00;

else if (load) out = data;

else out = out - 1;

end

endmodule

解:

Verilog语言程序清单如下,写出电路的逻辑功能,并通过QuartusII进行仿真。

module count(out,data,load,reset,clk);

output[7:0] out;

input[7:0] data;

input load,clk,reset;

reg[7:0] out;

always @(posedge clk)

begin

if (!reset) out = 8'h00;

else if (load) out = data;

else out = out - 1;

end

endmodule

【9-5】Verilog语言程序清单如下,写出电路的逻辑功能表,并通过QuartusII进行仿真。module yima(A,EN,Y);

output [7:0] Y;

input [2:0] A;

input EN;

reg[7:0] Y;

wire [3:0] temp={A,EN};

always

case (temp)

4'b0001 : Y=8'b00000001;

4'b1001 : Y=8'b00000010;

4'b0101 : Y=8'b00000100;

4'b1101 : Y=8'b00001000;

4'b0011 : Y=8'b00010000;

4'b1011 : Y=8'b00100000;

4'b0111 : Y=8'b01000000;

4'b1111 : Y=8'b10000000;

default : Y=8'b11111111;

endcase

endmodule

解:

3输入8输出译码器。仿真波形图见P9.5(a),仿真电路图见P9.5(b)。

(a)仿真波形图

(b) 仿真电路图

图9.5

【9-6】Verilog语言程序清单如下,写出电路的逻辑功能表,并通过QuartusII进行仿真。module bianma(Y,A);

output [2:0] A;

input [7:0] Y;

reg [2:0] A;

wire [7:0] temp=Y;

always

case (temp)

8'b00000001: A=3'b000;

8'b00000010: A=3'b100;

8'b00000100: A=3'b010;

8'b00001000: A=3'b110;

8'b00010000: A=3'b001;

8'b00100000: A=3'b101;

8'b01000000: A=3'b011;

8'b10000000: A=3'b111;

default A=3'b000;

endcase

endmodule

解:

8输入3输出编码器。仿真波形图见P9.6(a),仿真电路图见P9.6(b)。

(a)仿真波形图

(b) 仿真电路图

图P9.6

【9-7】用V erilog 写出60进制计数器的程序,并进行仿真

第10章 脉冲产生及变换电路

【10-1】试计算图10.1中单稳态触发器74LS122的暂稳态时间,R ext =10k Ω、C ext =100nF 。

图10.1

解:

根据图中所给参数,暂稳态时间t w

t w =0.32R ext C ext =0.7′10′103′100′10-9=0.32ms

【10-2】图10.2(a )是由555定时器构成的单稳态触发电路。 1.简要说明其工作原理; 2.计算暂稳态维持时间t w

3.

画出在图10.2(b

)所示输入u i 作用下的u C 和u O 的波形。

4.若u i 的低电平维持时间为15ms ,要求暂稳态维持时间t w 不变,应采取什么措施?

+5V

F

μo

(a) (b )

u t (ms)

(ms)(ms)

u u

图10.2

解:

1、工作原理(略);

2、暂稳态维持时间t w =1.1RC=10ms ;

3、u c 和u o 的波形如下图:

u o

u c

t t t

u i (ms)

(ms)(ms)5 10 25 30 45 50

3.33V

4若u i 的低电平维持时间为15m s ,要求暂稳态维持时间t w 不变,可加入微分电路

【10-3】图10.3(a )为由555定时器和D 触发器构成的电路,请问:

1.555定时器构成的是那种脉冲电路?

2.在图10.3(b )中画出u c 、u 01、u 02的波形; 3.计算u 01和u 02的频率。

0.1 F t

u c

u u u μ

(a ) (b )

图10.3

解:

1、555定时器构成多谐振荡器

2、u c, u o 1, u o 2的波形

u c u o 1u o 2

t t t 1.67V

3.33V

3、u o 1的频率f 1=

1

074501316..

H z ′′≈ u o 2的频率f 2=158H z

【10-4】由555定时器构成的电路如图10.4 (a)所示,其中CC 5V V =、S 4V U =。回答下列问题:

1. 说明由555定时器构成的电路名称。

2. 如果输入信号u i 如图10.4 (b)所示,画出电路输出u o 的波形。

V CC

u o

1

2

34

5678555

u i

-

+S

u u o

(a)

(b)

图10.4

解:

1. 该电路为555定时器构成的施密特触发器。………………………..................…(3分)

2. 由电路图可知,电路的阈值电压为

TH1s 4V U U ==

TH 2s 1

2V 2

U U ==

在给定输入u i 信号条件下,电路输出u o 的波形如图10.4(b)所示。…………......…(3分)

u u o

图10.4(b)

【10-5】由555定时器构成的施密特触发器如图10.5(a )所示。

1.在图(b )中画出该电路的电压传输特性曲线;

2.如果输入u i 为图(c )的波形;所示信号,对应画出输出u O 的波形; 3.为使电路能识别出u i 中的第二个尖峰,应采取什么措施?

4.在555定时器的哪个管脚能得到与3脚一样的信号,如何接法?

+6V

o

5

(a )

i (V)

u o

(V)

t

u u

(b ) (c )

图10.5

数字电子技术基础期末考试试卷 1.时序逻辑电路一般由和两分组成。 2.十进制数(56)10转换为二进制数为和十六进制数为。 3.串行进位加法器的缺点是,想速度高时应采用加法器。 4.多谐振荡器是一种波形电路,它没有稳态,只有两个。 5.用6个D 触发器设计一个计数器,则该计数器的最大模值M=。 123(1(24.T ,图1 5 时,6.D 触发器 的Q 和Q1的表达式,并画出其波形。 图 D=Q n+1=Q 1= 7.已知电路如图4所示,试写出: ①驱动方程; ②状态方程; ③输出方程; ④状态表;

⑤电路功能。图4 1.设计一个三变量偶检验逻辑电路。当三变量A 、B 、C 输入组合中的“1”的个数为偶数时F=1,否则F=0。选用8选1数选器或门电路实现该逻辑电路。 要求: (1)列出该电路F(A,B,C)的真值表和表达式; (2ABCF 2求: (1(21.3.4.产生5.32 10分,共 70分) 1.解: 2.证明:左边 3.解: (1)化简该 函数为最简与或式: 解: F 3()43A B C D E A B C D E AB AC A D E =++++--------------=?+++--------------=++-------------分 分 分 ()()33()(1)22BC D B C AD B BC D BAD CAD BC BC BC D BA CA =++++--------------=++++--------------=++++-----------------------分 分分分

填对卡诺图圈对卡诺图-----------2分 由卡诺图可得: F A B A C D A C D B C B D =++++------------------------------2分 (2)画出用两级与非门实现的最简与或式电路图: 则可得电路图如下:------------------------------------------------2分 4.T 1=0.7T=0.7f= T 1=q= 1T T 5.6. 方程: n n n Q Q K Q 0 0000=+ 1111110(n n n n Q J Q K Q Q X +=+=⊕(2分) ③输出方程:n n Q Q Y 01=-----------------------------------------(1分) ④状态表:--------------------------------------------------------------------(3分) ⑤从状态表可得:为受X 控制的可逆4进制值计数器。-----------------------------(2分) 1.解:(1)依题意得真值表如下:--------------------------3分 0102J J Q ⊕(分)

74LS191功能表 LD CT D U / CP D 0 D 1 D 2 D 3 Q 0 Q 1 Q 2 Q 3 0 × × × d 0d 1 d 2 d 3 1 0 0 ↑ ×××× 1 0 1 ↑ ×d 0 d 1 d 2 d 3 加法计数 减法计数 命 题 人 : 审 题 人 : 命 题 时 间 : 系名 专业 年级、班 学号 姓名 数字电子技术 课程试题( 卷) 题号 一 二 三 四 五 六 七 八 九 十 总分 得分 (请将答案写在答题纸上,答在试卷上不给分) 一. 选择题(16分) 1.已知A B A B B A Y +++=,下列结果正确的是( ) a . Y =A b .Y=B c .A B Y += d .Y=1 2.已知A=(10.44)10(下标表示进制),下列结果正确的是( ) a . A=(1010.1)2 b .A=(0A .8)16 c . A=(12.4)8 d .A=(20.21)5 3.下列说法不正确的是( ) a .当高电平表示逻辑0、低电平表示逻辑1时称为正逻辑 b .三态门输出端有可能出现三种状态(高阻态、高电平、低电平) c .OC 门输出端直接连接可以实现正逻辑的线与运算 d .集电极开路的门称为OC 门 4.以下错误的是( ) a .数字比较器可以比较数字大小 b . 半加器可实现两个一位二进制数相加 c .编码器可分为普通全加器和优先编码器 d .上面描述至少有一个不正确 5.下列描述不正确的是( ) a .触发器具有两种状态,当Q=1时触发器处于1态 b .时序电路必然存在状态循环 c .异步时序电路的响应速度要比同步时序电路的响应速度慢 d .主从JK 触发器具有一次变化现象 6.电路如下图(图中为上升沿Jk 触发器),触发器当前状态Q 3 Q 2 Q 1为“100”,请问在时钟作用下,触发器下一状态(Q 3 Q 2 Q 1)为( ) a .“101” b .“100” c .“011” d .“000” 7.电路如下图,已知电路的当前状态Q 3 Q 2 Q 1 Q 0为“1100”,74LS191具有异步置数的逻辑功能,请问在时钟作用下,电路的下一状态(Q 3 Q 2 Q 1 Q 0)为( ) a .“1100” b .“1011” c .“1101” d .“0000” 8.下列描述不正确的是( ) a .EEPROM 具有数据长期保存的功能且比EPROM 在数据改写上更方便 b .DAC 的含义是数-模转换、ADC 的含义是模数转换 c .积分型单稳触发器电路只有一个状态 d .上面描述至少有一个不正确 二.判断题(9分) 1.TTL 输出端为低电平时带拉电流的能力为5mA ( ) 2.TTL 、CMOS 门中未使用的输入端均可悬空( ) 3.当决定事件发生的所有条件中任一个(或几个)条件成立时,这件事件就会发生,这种因果关系称为与运算。() 4.将代码状态的特点含义“翻译”出来的过程称为译码。实现译码操作的电路称为译码器。() 5.设计一个3进制计数器可用2个触发器实现( ) 6.移位寄存器除了可以用来存入数码外,还可以利用它的移存规律在一定的范围内构成任意模值n 的计数器。所以又称为移存型计数器( ) 7. 判断时序逻辑电路能否自启动可通过判断该电路是否存在有效循环来实现( ) 8. 施密特触发器电路具有两个稳态,而多谐振荡器电路没有稳态( ) 9. DRAM 需要定期刷新,因此,在微型计算机中不如SRAM 应用广泛( ) 三.计算题(8分) 1、在如图所示电路中,U cc =5V ,U BB =9V ,R 1=5.1kΩ, R 2=15kΩ,R c =1kΩ,β=40,请计算U I 分别为5V ,0.3V 时输出U O 的大小?。 密 线 封 A B

Q 1 CP Q 1 Q 0 &&D 1D 0第一组: 计算题 一、(本题20分) 试写出图示逻辑电路的逻辑表达式,并化为最简与或式。 解:C B A B A F ++=C B A B A F ++= 二、(本题25分) 时序逻辑电路如图所示,已知初始状态Q 1Q 0=00。 (1)试写出各触发器的驱动方程; (2)列出状态转换顺序表; (3)说明电路的功能; 解:(1)100Q Q D =,101Q Q D =; (2)00→10→01 (3)三进制移位计数器 三、(本题30分)

由集成定时器555组成的电路如图所示,已知:R 1=R 2=10 k Ω,C =5μF 。 (1)说明电路的功能; (2)计算电路的周期和频率。 解:(1)多谐振荡器电路 (2)T 1=7s , T 2=3.5s 四、(本题25分) 用二进制计算器74LS161和8选1数据选择器连接的电路如图所示, (1)试列出74LS161的状态表; (2)指出是几进制计数器; (3)写出输出Z 的序列。 "1" 解: (1)状态表如图所示 (2)十进制计数器 (3)输出Z 的序列是0010001100 C R R CC u o

第二组: 计算题 一、(本题20分) 逻辑电路如图所示,试答: 1、写出逻辑式并转换为最简与或表达式,2、画出用“与”门及“或”门实现的逻辑图。 B 二、(本题25分) 试用与非门设计一个三人表决组合逻辑电路(输入为A、B、C,输出为F),要求在A有一票决定权的前提下遵照少数服从多数原则,即满足:1、A=1时,F一定等于1,2、A、B、C中有两2个以上等于1,则输出F=1。 试:(1)写出表决电路的真值表; (2)写出表决电路的逻辑表达式并化简; (3)画出用与非门设计的逻辑电路图。 解: (1)真值表

1.导致欧洲中世纪黑暗时期出现的主要原因是什么? 因为中世纪时期是欧洲最为混乱的时期,也是其经济、政治、文化、军事等全面停滞发展的时期,当时的欧洲居民生活在水深火热之中,所以被称为黑暗时期. 1、政治的黑暗、政权的分散:自罗马帝国衰亡后,中欧、西欧被来自东欧的日耳曼民族统治,日耳曼民族又有很多种族,因此相互征伐不断,如法兰克帝国、神圣罗马帝国、英格兰王国、教皇国等等,这些国家相互征伐、动乱不已,而且中世纪时期虽然是欧洲的封建时期,但却不集权、不统一,类似分封制的封建制度导致封建国家缺乏强有力的基础,例如神圣罗马帝国、皇帝仅仅是一个称号而已.而封建地主又对百姓盘剥,加之战乱不断、瘟疫横行,民不聊生. 2、宗教的干涉:这一时期的基督教对各国的干扰极强,甚至对政权的建立、稳定都十分重要.宗教严格的控制文化教育、人们的生活:一方面他们严格要求中下层教士及普通百姓,另一方面,上层教士又和封建势力相勾结,腐败没落,压榨百姓和人民,中世纪的宗教裁判所又有极大的权力,可以处死他们所认为的异端分子,由于思想、科学被严格控制,这一时期的欧洲思想、文化、科学鲜有成就. 3、经济的没落,由于盘剥严重、科技落后,这一时期的经济几乎没有发展,没有进步就代表了落后; 4、瘟疫盛行:宗教的干涉,科技的落后,医学的不发达,导致瘟疫的盛行,540年~590年查士丁尼瘟疫导致东地中海约2500万人死亡;1346

年到1350的鼠疫导致欧洲约2500万人死亡,灾难极大地打击的了欧洲的经济、政治甚至人口的发展. 简而言之,这一时期的欧洲百姓生活在一种暗无天日,毫无希望的生活里,所以被称为黑暗时期. 2、在欧洲中世纪黑暗时期曾经出现过那些知名的数学家,他们在当时那样的背景下各自做了哪些数学工作? 答:罗马人博伊西斯(罗马贵族),曾不顾禁令用拉丁文从古希腊著作的片段中编译了一些算术、几何、音乐、天文的初级读物,他把这些内容称为“四大科”,其中的数学著作还被教会学校作为标准课本使用了近千年之久,但博伊西斯本人还是遭受政治迫害被捕入狱并死在狱中。 7世纪,在英格兰的北部出现了一位博学多才的神学家,这就是被称为“英格兰文化之父”的比德。在数学方面,比德曾写过一些算术著作,研究过历法及指头计算方法。当时,对耶稣复活期的推算是教会讨论最热烈的课题之一,据说,这位比德大师就是最先求得复活节的人。 培根是英格兰人(贵族),曾在牛津大学和巴黎大学任教,会多种语言,对当时几乎所有的知识感兴趣,号称“万能博士”。他提倡科学,重视现实,反抗权威(应为不惧权威)。他认为,数学的思想方法是与生俱来的,并且是与自然规律相一致的。在他看来,数学是一切科学的基础,科学真理之所以是珍贵的,是因为它们是在数学的形成中被反映出来,即用数量和尺规刻画的。培根认为:“寻找和发

; 数字电子技术基础试题 一、填空题 : (每空1分,共10分) 1. 10 = ( ) 2 = ( ) 16 。 2 . 逻辑函数L = + A+ B+ C +D = 。 3 . 三态门输出的三种状态分别为:、和。 4 . 主从型JK触发器的特性方程= 。 5 . 用4个触发器可以存储位二进制数。 6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。【 二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 ) 1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。 图 1

2.下列几种TTL电路中,输出端可实现线与功能的电路是()。 A、或非门 B、与非门 ( C、异或门 D、OC门 3.对CMOS与非门电路,其多余输入端正确的处理方法是()。 A、通过大电阻接地(>Ω) B、悬空 C、通过小电阻接地(<1KΩ) D、通过电阻接V CC 4.图2所示电路为由555定时器构成的()。 A、施密特触发器 B、多谐振荡器 C、单稳态触发器 D、T触发器 " 5.请判断以下哪个电路不是时序逻辑电路()。图2 A、计数器 B、寄存器 C、译码器 D、触发器 6.下列几种A/D转换器中,转换速度最快的是()。图2 A、并行A/D转换器 B、计数型A/D转换器 C、逐次渐进型A/D转换器 D、双积分A/D转换器 7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

图3 . A、施密特触发器 B、反相器 C、单稳态触发器 D、JK触发器 8.要将方波脉冲的周期扩展10倍,可采用()。 A、10级施密特触发器 B、10位二进制计数器 C、十进制计数器 D、10位D/A转换器 9、已知逻辑函数与其相等的函数为()。 A、B、C、D、 10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。 \ A、4 B、6 C、8 D、16 三、逻辑函数化简(每题5分,共10分) 1、用代数法化简为最简与或式 Y= A + 2、用卡诺图法化简为最简或与式

《数学史论约》复习题参考及答案本科 一、填空(22分) 1、数学史的研究对象是(数学这门学科产生、发展的历史),既要研究其历史进程,还要研究其(一般规律); 2、数学史分期的依据主要有两大类,其一是根据(数学学科自身的研究对象、内容结构、知识领域的演进)来分期,其一是根据(数学学科所处的社会、政治、经济、文化环境的变迁)来分期; 3、17世纪产生了影响深远的数学分支学科,它们分别是(解析几何)、(微积分)、(射影几何)、(概率论)、(数论); 4、18世纪数学的发展以(微积分的深入发展)为主线; 5、整数458 用古埃及记数法可以表示为()。 6、研究巴比伦数学的主要历史资料是(契形文字泥板),而莱因特纸草书和莫斯科纸草 书是研究古代(埃及数学)的主要历史资料; 7、古希腊数学发展历经1200多年,可以分为(古典)时期和(亚历山大里亚)时期; 8、17世纪创立的几门影响深远的数学分支学科,分别是笛卡儿和(费马)创立了解析 几何,牛顿和(莱布尼茨)创立了微积分,(笛沙格)和帕斯卡创立了射影几何, (帕斯卡)和费马创立了概率论,费马创立了数论; 9、19世纪数学发展的特征是(创造)精神和(严格)精神都高度发扬; 10、整数458 用巴比伦的记数法可以表示为()。 11、数学史的研究内容,从宏观上可以分为两部分,其一是内史,即(数学内在学科因素促使其发展), 其一是外史,即(数学外在的似乎因素影响其发展); 12、19世纪数学发展的特征,可以用以下三方面的典型成就加以说明: (1)分析基础严密化和(复变函数论创立), (2)(非欧几里得几何学问世)和射影几何的完善, (3)群论和(非交换代数诞生); 13、20世纪数学发展“日新月异,突飞猛进”,其显著趋势是:数学基础公理化, 数学发展整体化,(电子计算机)的挑战,应用数学异军突起,数学传播与(研究)的 社会化协作,(新理论)的导向; 14、《九章算术》的内容分九章,全书共(246)问,魏晋时期的数学家(刘徽)曾为它作注; 15、整数458 用玛雅记数法可以表示为()。 16、数学史的研究对象是数学这门学科产生、发展的历史,既要研究其(历史进程),还要研究其(一般规律); 17、古希腊数学学派有泰勒斯学派、(毕达哥拉斯学派)、(厄利亚学派)、巧辩学派、柏拉图学派、欧多克索学派和(亚里士多德学派); 18、阿拉伯数学家(阿尔-花拉子模)在他的著作(《代数学》)中,系统地研究了当时对一元一次和一元二次方程的求解方法; 19、19世纪数学发展的特点,可以用以下三方面的典型成就加以说明:(1)(分析基础严密化)和复变函数论的创立;(2)非欧几里得几何学问世和(射影几何的完善);(3)在代数学领域(群论)与非交换代数的诞生。 20、整数458 用古印度记数法可以表示为()。 二、选择题 1、数学史的研究对象是(C);

. 数字电子技术基础期末考试试卷 一、填空题 1. 时序逻辑电路一般由 和 两分组成。 2. 十进制数(56)10转换为二进制数为 和十六进制数为 。 3. 串行进位加法器的缺点是 ,想速度高时应采用 加法器。 4. 多谐振荡器是一种波形 电路,它没有稳态,只有两个 。 5. 用6个D 触发器设计一个计数器,则该计数器的最大模值M= 。 二、化简、证明、分析综合题: 1.写出函数F (A,B,C,D) =A B C D E ++++的反函数。 2.证明逻辑函数式相等:()()BC D D B C AD B B D ++++=+ 3.已知逻辑函数F= ∑(3,5,8,9,10,12)+∑d(0,1,2) (1)化简该函数为最简与或式: (2)画出用两级与非门实现的最简与或式电路图: 4.555定时器构成的多谐振动器图1所示,已知R 1=1K Ω,R 2=8.2K Ω,C=0.1μF 。试求脉冲宽度 T ,振荡频率f 和占空比q 。 ………………………密……………………封…………………………装…………………订………………………线……………………… 系别 专业(班级) 姓名 学号

图1 5.某地址译码电路如图2所示,当输入地址变量A7-A0的状态分别为什么状态 时,1Y 、6Y 分别才为低电平(被译中)。 图2 6.触发器电路就输入信号的波形如图3所示,试分别写出D 触发器的Q 和Q1的表达式,并画出其波形。 图3 ………………封…………………………装…………………订………………………线………………………

D= Q n+1= Q1= 7. 已知电路如图4所示,试写出: ①驱动方程; ②状态方程; ③输出方程; ④状态表; ⑤电路功能。图4 三、设计题:(每10分,共20分) 1.设计一个三变量偶检验逻辑电路。当三变量A、B、C输入组合中的“1”的个数为偶数时F=1,否则F=0。选用8选1数选器或门电路实现该逻辑电路。要求: (1)列出该电路F(A,B,C)的真值表和表达式; (2)画出逻辑电路图。 2.试用74161、3-8译码器和少量门电路,实现图5所示波形VO1、VO2,其中CP为输入波形。要求: (1)列出计数器状态与V01、V02的真值表;

数学史复习题 一、1.对于数学史的分期,1820’—现在属于 1.A.数学的起源与早期发展 B.初等数学时期 C.近代数学时期 D.现代数学时期 是希腊演绎几何的最高成就。 A.《原本》 B.《方法》 C.《圆锥曲线论》 D.《大成》 2.______的《数学汇编》被认为是古希腊数学的安魂曲。 3.A.海伦 B.托勒玫 C.丢番图 D.帕波斯 4.“百鸡问题”是“算经十书”中的______卷下的最后一题。 A.《孙子算经》 B.《张邱建算经》 C.《缉古算经》 D.《海岛算经》 5.关于一次同余组求解的剩余定理被称为“______”。 A.中国剩余定理 B.孙子定理 C.秦九韶定理 D.杨辉定理 6.“我思故我在”是______的名言。 A.柏拉图 B.毕达哥拉斯 C.笛卡儿 D.莱布尼茨 7.______是历史上第一篇系统的微积分文献。 8.A.《流数简论》 B.《运用无限多项方程的分析》 C.《流数法与无穷级数》 D.《曲线求积术》 8.“每个偶数是两个素数和;每个奇数是三个素数之和。”这就是着名的 9.A.费马小定理 B.费马大定理 C.哥德巴赫猜想 D.华林问题 世纪数学家们在对几何学作统一处理的观点下进行探索,在所有这些努力中,______ 在《几何基础》中使用的公理化方法最为成功。 A.希尔伯特 B.庞加莱 C.罗巴切夫斯基 D.黎曼 10.英国生物学家和统计学家______在现代数理统计的建立上起了重要作用。他在19世纪末、20世纪初发展了他老师高尔顿首先提出的“相关”与“回归”的理论,成功地创立了生物统计学。 A.贝叶斯 B.皮尔逊 C.费希尔 D.克拉默 11.电子计算机的发明与发展再一次表明,人类计算机工具的改进是离不开数学与数学家的贡献的。电子计算机都是以______的设计思想为基础的。 A.帕斯卡 B.巴贝奇 C.冯·诺依曼 D.图灵 12.费马大定理是1994年由英国数学家______完成的。 A.库默尔 B.谷山丰 C.弗雷 D.维尔斯 13.古典数学名着《圆锥曲线论》的作者是阿波罗尼奥斯。 2.“宋元数学四大家”是秦九韶、李冶、杨辉和朱世杰。

数字电子技术基础考题 一、填空题:(每空3分,共15分) 1.逻辑函数有四种表示方法,它们分别是(真值表)、(逻辑图)、(逻辑表达式)和(卡诺图)。 2.将2004个“1”异或起来得到的结果是(0 )。 3.由555定时器构成的三种电路中,()和()是脉冲的整形电路。4.TTL器件输入脚悬空相当于输入(高)电平。 5.基本逻辑运算有: (and )、(not )和(or )运算。 6.采用四位比较器对两个四位数比较时,先比较(最高)位。 7.触发器按动作特点可分为基本型、(同步型)、(主从型)和边沿型;8.如果要把一宽脉冲变换为窄脉冲应采用(积分型单稳态)触发器 9.目前我们所学的双极型集成电路和单极型集成电路的典型电路分别是(TTL )电路和(CMOS )电路。 10.施密特触发器有(2)个稳定状态.,多谐振荡器有(0 )个稳定状态。 11.数字系统按组成方式可分为功能扩展电路、功能综合电路两种;12.两二进制数相加时,不考虑低位的进位信号是(半)加器。 13.不仅考虑两个_______本位_____相加,而且还考虑来自___低位进位____相加的运算电路,称为全加器。 14.时序逻辑电路的输出不仅和___该时刻输入变量的取值______有关,而且还与_电路原来的状态_______有关。 15.计数器按CP脉冲的输入方式可分为__同步计数器和____异步计数器_。 16.触发器根据逻辑功能的不同,可分为_____rs______、______jk_____、___t________、___d________、___________等。 17.根据不同需要,在集成计数器芯片的基础上,通过采用__反馈归零法_________、__预置数法_________、__进位输出置最小数法__等方法可以实现任意进制的技术器。 18.4. 一个JK 触发器有 2 个稳态,它可存储 1 位二进制数。 19.若将一个正弦波电压信号转换成同一频率的矩形波,应采用多谐振荡器电路。20.把JK触发器改成T触发器的方法是 j=k=t 。 21.N个触发器组成的计数器最多可以组成2n 进制的计数器。 22.基本RS触发器的约束条件是rs=0 。

数字电子技术试卷(1) 一.填空(16) 1.十进制数123的二进制数是 1111011 ;十六进制数是 7B 。 2.1是8421BCD 码,其十进制为 861 。 3.逻辑代数的三种基本运算是 与 , 或 和 非 。 4.三态门的工作状态是 0 , 1 , 高阻 。 5.描述触发器逻辑功能的方法有 真值表,逻辑图,逻辑表达式,卡诺图,波形图 。 6.施密特触发器的主要应用是 波形的整形 。 7.设4位D/A 转换器的满度输出电压位30伏,则输入数字量为1010时的输出模拟电压为 。 8.实现A/D 转换的主要方法有 , , 。 三.化简逻辑函数(14) 1.用公式法化简- -+++=A D DCE BD B A Y ,化为最简与或表达式。 解;D B A Y +=- 2.用卡诺图化简∑∑=m d D C B A Y ),,,,()+,,,,(84210107653),,,(,化为最简与或表达式。 四.电路如图1所示,要求写出输出函数表达式,并说出其逻辑功能。(15) 解;C B A Y ⊕⊕=, C B A AB C )(1++=,全加器,Y 为和,1C 为进位。 五.触发器电路如图2(a ),(b )所示,⑴写出触发器的次态方程; ⑵对应给定波形画 出Q 端波形(设初态Q =0)(15) 解;(1)AQ Q Q n +=- +1,(2)、A Q n =+1 六.试用触发器和门电路设计一个同步的五进制计数器。(15) 七.用集成电路定时器555所构成的自激多谐振荡器电路如图3所示,试画出V O ,V C 的工作 波形,并求出振荡频率。(15)

选择题(每题2分) 1.对古代埃及数学成就的了解主要来源于( A ) A.纸草书 B.羊皮书 C.泥版 D.金字塔内的石刻 2.对古代巴比伦数学成就的了解主要来源于( C ) A.纸草书 B.羊皮书 C.泥版 D.金字塔内的石刻 3.《九章算术》中的“阳马”是指一种特殊的( B ) A.棱柱 B.棱锥 C.棱台 D.楔形体 4.《九章算术》中的“壍堵”是指一种特殊的( A ) A.三棱柱 B.三棱锥 C.四棱台 D.楔形体 5.射影几何产生于文艺复兴时期的( C ) A.音乐演奏 B.服装设计 C.绘画艺术 D.雕刻艺术 6.欧洲中世纪漫长的黑暗时期过后,第一位有影响的数学家是( A )。 A.斐波那契 B.卡尔丹 C.塔塔利亚 D.费罗 7.被称作“第一位数学家和论证几何学的鼻祖”的数学家是( B ) A.欧几里得 B.泰勒斯 C.毕达哥拉斯 D.阿波罗尼奥斯 8.被称作“非欧几何之父”的数学家是( D ) A.波利亚 B.高斯 C.魏尔斯特拉斯 D.罗巴切夫斯基 9.对微积分的诞生具有重要意义的“行星运行三大定律”,其发现者是( C ) A.伽利略 B.哥白尼 C.开普勒 D.牛顿 10.公元前4世纪,数学家梅内赫莫斯在研究下面的哪个问题时发现了圆锥曲线?( C ) A.不可公度数 B.化圆为方 C.倍立方体 D.三等分角 11.印度古代数学著作《计算方法纲要》的作者是( C ) A.阿耶波多 B.婆罗摩笈多 C.马哈维拉 D.婆什迦罗 12.最早证明了有理数集是可数集的数学家是( A ) A.康托尔 B.欧拉 C.魏尔斯特拉斯 D.柯西 13.下列哪一位数学家不属于“悉檀多”时期的印度数学家?( C ) A.阿耶波多 B.马哈维拉 C.奥马.海亚姆 D.婆罗摩笈多 14.在1900年巴黎国际数学家大会上提出了23个著名的数学问题的数学家是( A ) - 1 - / 9

数字电子技术基础1 一.1.(15分) 试根据图示输入信号波形分别画出各电路相应的输出信号波形L1、L2、L3、L4、和L5。设各触发器初态为“0”。 二.(15分) 已知由八选一数据选择器组成的逻辑电路如下所示。试按步骤分析该电路在M1、M2取不同值时(M1、M2取值情况如下表所示)输出F的逻辑表达式。 八选一数据选择器输出端逻辑表达式为:Y=Σm i D i,其中m i是S2S1S0最小项。 三.(8分) 试按步骤设计一个组合逻辑电路,实现语句“A>B”,A、B均为两位二进制数,即A (A1、A0),B(B1、B0)。要求用三个3输入端与门和一个或门实现。 四.(12分) 试按步骤用74LS138和门电路产生如下多输出逻辑函数。 74LS138逻辑表达式和逻辑符号如下所示。 五.(15分) 已知同步计数器的时序波形如下图所示。试用维持-阻塞型D触发器实现该计数器。要求按步骤设计。 六.(18分) 按步骤完成下列两题 1.分析图5-1所示电路的逻辑功能:写出驱动方程,列出状态转换表,画出完全状态转换图和时序波形,说明电路能否自启动。 2.分析图5-2所示的计数器在M=0和M=1时各为几进制计数器,并画出状态转换图。 图5-1

图5-2 七. 八.(10分) 电路下如图所示,按要求完成下列问题。 1.指出虚线框T1中所示电路名称. 2.对应画出V C 、V 01、A 、B 、C 的波形。并计算出V 01波形的周期T=?。 数字电子技术基础2 一.(20分)电路如图所示,晶体管的β=100,Vbe=0.7v 。 (1)求电路的静态工作点; (2) 画出微变等效电路图, 求Au 、r i 和r o ; (3)若电容Ce 开路,则将引起电路的哪些动态参数发生变化?并定性说明变化趋势. 二.(15分)求图示电路中a U 、b U 、b U 、c U 及L I 。 三.(8分)逻辑单元电路符号和具有“0”、“1”逻辑电平输入信号X 1如下图所示,试分别画出各单元电路相应的电压输出信号波形Y 1、Y 2、Y 3。设各触发器初始状态为“0”态。 四.(8分)判断下面电路中的极间交流反馈的极性(要求在图上标出瞬时极性符号)。如为负反馈,则进一步指明反馈的组态。 (a ) (b )

数字电子技术基础试题(一) 一、填空题 : (每空1分,共10分) 1. (30.25) 10 = ( ) 2 = ( ) 16 。 2 . 逻辑函数L = + A+ B+ C +D = 。 3 . 三态门输出的三种状态分别为:、和。 4 . 主从型JK触发器的特性方程= 。 5 . 用4个触发器可以存储位二进制数。 6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。 二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 ) 1.设下图中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。 2.下列几种TTL电路中,输出端可实现线与功能的电路是()。 A、或非门 B、与非门 C、异或门 D、OC门 3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ) B、悬空 C、通过小电阻接地(<1KΩ) D、通过电阻接V CC 4.图2所示电路为由555定时器构成的()。 A、施密特触发器 B、多谐振荡器 C、单稳态触发器 D、T触发器 5.请判断以下哪个电路不是时序逻辑电路()。 A、计数器 B、寄存器 C、译码器 D、触发器 6.下列几种A/D转换器中,转换速度最快的是()。 A、并行A/D转换器 B、计数型A/D转换器 C、逐次渐进型A/D转换器 B、 D、双积分A/D转换器 7.某电路的输入波形 u I 和输出波形 u O 如下图所示,则该电路为()。 A、施密特触发器 B、反相器 C、单稳态触发器 D、JK触发器 8.要将方波脉冲的周期扩展10倍,可采用()。 A、10级施密特触发器 B、10位二进制计数器 C、十进制计数器 B、D、10位D/A转换器 9、已知逻辑函数与其相等的函数为()。 A、 B、 C、 D、 10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。 A、4 B、6 C、8 D、16 三、逻辑函数化简(每题5分,共10分) 1、用代数法化简为最简与或式

第一章数字逻辑基础 第一节重点与难点 一、重点: 1.数制 2.编码 (1) 二—十进制码(BCD码) 在这种编码中,用四位二进制数表示十进制数中的0~9十个数码。常用的编码有8421BCD码、5421BCD码和余3码。 8421BCD码是由四位二进制数0000到1111十六种组合中前十种组合,即0000~1001来代表十进制数0~9十个数码,每位二进制码具有固定的权值8、4、2、1,称有权码。 余3码是由8421BCD码加3(0011)得来,是一种无权码。 (2)格雷码 格雷码是一种常见的无权码。这种码的特点是相邻的两个码组之间仅有一位不同,因而其可靠性较高,广泛应用于计数和数字系统的输入、输出等场合。 3.逻辑代数基础 (1)逻辑代数的基本公式与基本规则 逻辑代数的基本公式反映了二值逻辑的基本思想,是逻辑运算的重要工具,也是学习数字电路的必备基础。 逻辑代数有三个基本规则,利用代入规则、反演规则和对偶规则使逻辑函数的公式数目倍增。 (2)逻辑问题的描述 逻辑问题的描述可用真值表、函数式、逻辑图、卡诺图和时序图,它们各具特点又相互关联,可按需选用。 (3)图形法化简逻辑函数 图形法比较适合于具有三、四变量的逻辑函数的简化。 二、难点: 1.给定逻辑函数,将逻辑函数化为最简 用代数法化简逻辑函数,要求熟练掌握逻辑代数的基本公式和规则,熟练运用四个基本方法—并项法、消项法、消元法及配项法对逻辑函数进行化简。 用图形法化简逻辑函数时,一定要注意卡诺图的循环邻接的特点,画包围圈时应把每个包围圈尽可能画大。 2.卡诺图的灵活应用 卡诺图除用于简化函数外,还可以用来检验化简结果是否最简、判断函数间的关系、求函数的反函数和逻辑运算等。 3.电路的设计 在工程实际中,往往给出逻辑命题,如何正确分析命题,设计出逻辑电路呢?通常的步骤如下:

D C B A D C A B ++《数字电子技术》试卷 姓名:__ _______ 班级:__________ 考号:___________ 成绩:____________ 1.?有一数码10010011,作为自然二进制数时,它相当于十进制数(147),作为8421BCD 码时,它相当于十进制数(93 )。 2.三态门电路的输出有高电平、低电平和(高阻)3种状态。 3.TTL 与非门多余的输入端应接(高电平或悬空)。 4.TTL 集成JK 触发器正常工作时,其d R 和d S 端应接(高)电平。 5. 已知某函数?? ? ??+??? ??++=D C AB D C A B F ,该函数的反函数F = ( )。 6. 如果对键盘上108个符号进行二进制编码,则至少要( 7)位二进制数码。 7. 典型的TTL 与非门电路使用的电路为电源电压为(5 )V ,其输出高电平为(3.6)V ,输出低电平为(0.35)V , CMOS 电路的电源电压为( 3--18) V 。 8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为( )。 9.将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM 。该ROM 有( 11)根地址线,有(16)根数据读出线。 10. 两片中规模集成电路10进制计数器串联后,最大计数容量为( 100)位。 11. =(AB )。 12. 13 二、分) 1.?函数 A .F(A,B,C)=∑m (0,2,4) B. (A,B,C)=∑m (3,5,6,7) C .F(A,B,C)=∑m (0,2,3,4) D. F(A,B,C)=∑m (2,4,6,7) 2.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ??的值是( C )。 A .111 B. 010 C. 000 D. 101 3.十六路数据选择器的地址输入(选择控制)端有( C )个。 A .16 B.2 C.4 D.8

《数字电子技术》习题 一. 单项选择题: 1.十进制数128的8421BCD码是()。 A.10000000 B. 000100101000 C.100000000 D.100101000 2.已知函数F的卡诺图如图1-1, 试求其最简与或表达式 3. 已知函数的反演式为 ,其原函数为()。 A. B. C. D. 4.对于TTL数字集成电路来说,下列说法那个是错误的:(A)电源电压极性不得接反,其额定值为5V; (B)不使用的输入端接1; (C)输入端可串接电阻,但电阻值不应太大; (D)OC门输出端可以并接。 5.欲将正弦信号转换成与之频率相同的脉冲信号,应用 A.T,触发器 B.施密特触发器 C.A/D转换器 D.移位寄存器 6.下列A/D转换器中转换速度最快的是()。 A.并联比较型 B.双积分型 C.计数型 D.逐次渐近型 7. 一个含有32768个存储单元的ROM,有8个数据输出端,其地址输入端有()个。 A. 10 B. 11 C. 12 D. 8

8.如图1-2,在TTL门组成的电路中,与非门的输入电流为I iL≤–1mA?I iH≤20μA。G1输出低电平时输出电流的最大值为 I OL(max)=10mA,输出高电平时最大输出电流为 I OH(max)=–0.4mA 。门G1的扇出系数是()。 A. 1 B. 4 C. 5 D. 10 9.十数制数2006.375转换为二进制数是: A. 11111010110.011 B. 1101011111.11 C. 11111010110.11 D. 1101011111.011 10. TTL或非门多余输入端的处理是: A. 悬空 B. 接高电平 C. 接低电平 D.接”1” 二.填空题(每小题2分,共20分) 1.CMOS传输门的静态功耗非常小,当输入信号的频率增加时,其功耗将______________。 2. 写出四种逻辑函数的表示方法: __________________________________________________________ _____; 3.逻辑电路中,高电平用1表示,低电平用0表示,则称为___逻辑; 4. 把JK触发器改成T触发器的方法是_____________。 5. 组合逻辑电路是指电路的输出仅由当前的_____________决定。 6. 5个地址输入端译码器,其译码输出信号最多应有 _____________个。 7. 输入信号的同时跳变引起输出端产生尖峰脉冲的现象叫做 _____________。 8.一片ROM有10根地址线,8根数据输出线,ROM共有________个存储单元。 9.N个触发器组成的计数器最多可以组成_____________进制的计数器。 8. 基本RS触发器的约束条件是_____________。 三.电路分析题(36分)

数字电子技术基础期末考试试卷 1. 时序逻辑电路一般由 和 两分组成。 2. 十进制数(56)10转换为二进制数为 和十六进制数为 。 3. 串行进位加法器的缺点是 ,想速度高时应采用 加法器。 4. 多谐振荡器是一种波形 电路,它没有稳态,只有两个 。 5. 用6个D 触发器设计一个计数器,则该计数器的最大模值M= 。 1.写出函数F (A,B,C,D) =A B C D E ++++的反函数。 =F 2.证明逻辑函数式相等:()()BC D D B C AD B B D ++++=+ 3.已知逻辑函数F= ∑(3,5,8,9,10,12)+∑d(0,1,2) (1)化简该函数为最简与或式: (2)画出用两级与非门实现的最简与或式电路图: 4.555定时器构成的多谐振动器图1所示,已知R 1=1K Ω,R 2=8.2K Ω,C=0.1μF 。试求脉冲宽度T ,振荡频率f 和占空比q 。 图1 5.某地址译码电路如图2所示,当输入地址变量A7-A0的状态分别为什么状态 时,1Y 、6Y 分别才为低电平(被译中)。 …… …… … … …… …密 … … …… … … … … 封 …… … … … … … … … … 装 … … … … … … … 订 … … … … … … … … … 线 … … … … … … … … … 学院 专业 (班级) 姓名 学号 …… … … … … 线 …

6.触发器电路就输入信号的波形如图3所示,试分别写出D触发器的Q和Q1的表达式,并画出其波形。 图 D= Q n+1= Q1= 7. 已知电路如图4所示,试写出: ①驱动方程; ②状态方程; ③输出方程; ④状态表; ⑤电路功能。图4 1.设计一个三变量偶检验逻辑电路。当三变量A、B、C输入组合中的“1”的个数为偶数时F=1,否则F=0。选用8选1数选器或门电路实现该逻辑电路。 要求: (1)列出该电路F(A,B,C)的真值表和表达式; (2)画出逻辑电路图。 A B C F

数字电子技术基础答案 第1章 自测题 1.1填空题 1. 100011.11 00110101.01110101 11110.01 1E.4 2. 4 3. n 2 4. 逻辑代数 卡诺图 5.)(D C B A F += )(D C B A F +=' 6.))((C B D C B A F +++= 7. 代数法 卡诺图 8. 1 1.2判断题 1. √ 2.√ 3. × 1.3选择题 1.B 2.C 3.C 1.4 A F =1⊙B AB F =2 B A F +=3 1.5 1.6 C L = 1.7 AB C B A BC Y ++= 习题 1.1 当000012=A A A ,7A 到3A 有1个不为0时,就可以被十进制8整除 1.2 (a)AC BC AB L ++=(b )B A AB L += (c)C B A S ⊕⊕= AC BC AB C ++=0 1.3略 1.4 (1) )(B A D C F ++=)(1 ))((1B A D C F ++=' (2) )(B A B A F ++=)(2 ))((2B A B A F ++=' (3) E D C B A F =3 DE C AB F =' 3

(4) )()(4D A B A C E A F +++=)( ))()((4D A C AB E A F +++=' 1.5 C B A F ⊕⊕= 1.6 (1) B A C B C A L ++= (2) D B C B D C A L +++= (3) AD L = (4) E ABCD L = (5) 0=L 1.7 C B A BC A C AB ABC C B A L +++=),,( 1.8(1) ABD D A C F ++=1 (2) BC AB AC F ++=2 (3) C A B A B A F ++=3 (有多个答案) (4) C B A D C AB C A CD F +++=4 (5) C B A ABD C B A D B A F +++=5 (6) 16=F 1.9 (1) AD D C B B A F ++=1 (2) B A AC F +=2 (3) D A D B C B F ++=3 (4) B C F +=4 1.10 (1) C A B F +=1 (2) B C F +=2 (3) D A B C F ++=3 (4) C B A D B D C F ++=4 1.11 C A B A D F ++= 1.12 (1) D B A D C A D C B F ++=1(多种答案) (2) C B BCD D C D B F +++=2 (3) C B C A D C F ++=3 (4) A B F +=4 (5) BD D B F +=5 (6) C B D A D C A F ++=6(多种答案) (7) C A D B F +=7(多种答案) (8) BC D B F +=8(多种答案) (9) B D C F +=9 1.13 略 第2章 自测题 2.1 判断题 1. √ 2. √ 3. × 4. √ 5. √ 6. √ 7. × 8. √ 9. × 10√ 2.2 选择题 1.A B 2.C D 3.A 4.B 5.B 6.A B D 7.C 8.A C D 9.A C D 10.B 习题 2.1解:ABC Y =1