差分线对在高速PCB设计中的应用

时间:2007-04-28 来源: 作者:王延辉谢锘点击:3269 字体大小:【大中小】

摘要:在高速数字电路设计过程中,工程师采取了各种措施来解决信号完整性问题,利用差分线传输高速数字信号的方法就是其中之一。在PCB中的差分线是耦合带状线或耦合微带线,信号在上面传输时是奇模传输方式,因此差分信号具有抗干扰性强,易匹配等优点。随着人们对数字电路的信息传输速率要求的提高,信号的差分传输方式必将得到越来越广泛的应用。

1 用差分线传输数字信号

如何在高速系统设计中考虑信号完整性的因素,并采取有效的控制措施,已成为当今国内外系统设计工程师和PCB设计业界的一个热门课题。利用差分线传输数字信号就是高速数字电路中控制破坏信号完整性因素的一项有效措施。

在印刷电路板上的差分线,等效于工作在准TEM模的差分的微波集成传输线对,其中,位于PCB顶层或底层的差分线等效于耦合微带线;位于多层PCB的内层的差分线,正负两路信号在同一层的,等效于侧边耦合带状线,正负两路在相邻层的,等效于宽边耦合带状线。数字信号在差分线上传输时是奇模传输方式,即正负两路信号的相位相差180°,而噪声以共模的方式在一对差分线上耦合出现,在接受器中正负两路的电压(或电流)相减,从而可以获得信号,消除共模噪声。而差分线对的低压幅或电流驱动输出实现了高速集成功耗的要求。

2 差分线的阻抗匹配

差分线是分布参数系统,因此在设计PCB时必须进行阻抗匹配,否则信号将会在阻抗不连续的地方发生反射,信号反射在数字波形上主要表现为上冲、下冲和振铃现象。式(1)是一个信号的上升沿(幅度为E G)从驱动端经过差分传输线到接收端的频率响应:

其中信号源的电动势为E G,内阻抗为:Z G,负载阻抗为Z L;Hl(ω)为传输线的系统函数;ΓL和ΓG分别是信号接收端和信号驱动端的反射系数,由以下两式表示:

由式(1)可以看出,传输线上的电压是由从信号源向负载传输的入射波和从负载向信号源传输的反射波的叠加。只要我们通过阻抗匹配使ΓL和ΓG等于0,就可以消除信号反射现象。在实际工程应用中,一般只要求ΓL=0,这是因为只要接收端不发生信号反射,就不会有信号反射回源端并发生源端反射。

由式(3)可知,如果ΓL =0,则必须Z L=Z0,即传输线的特性阻抗等于终端负载的电阻值。传输线的特性阻抗可以由有关软件计算出来,它和差分线的线宽、线距及相邻介质的介电常数有关,一般把差分线的特性阻抗控制在100Ω左右。值得注意的是,一个差分信号在多层PCB的不同层传输时(特别是内外层都走线时),要及时调整线宽线距来补偿因为介质的介电常数变化带来的特性阻抗变化。终端负载电阻的控制要根据不同的逻辑电平接口,来选择适当的电阻网络和负载并联,以达到阻抗匹配的目的。

3 差分线的端接

差分线的端接要满足2方面的要求:逻辑电平的工艺要求和传输线阻抗匹配的要求。因此,不同的逻辑电平工艺要采用不同的端接。本文主要介绍2种常见的适于高速数传的电平的端接方法:

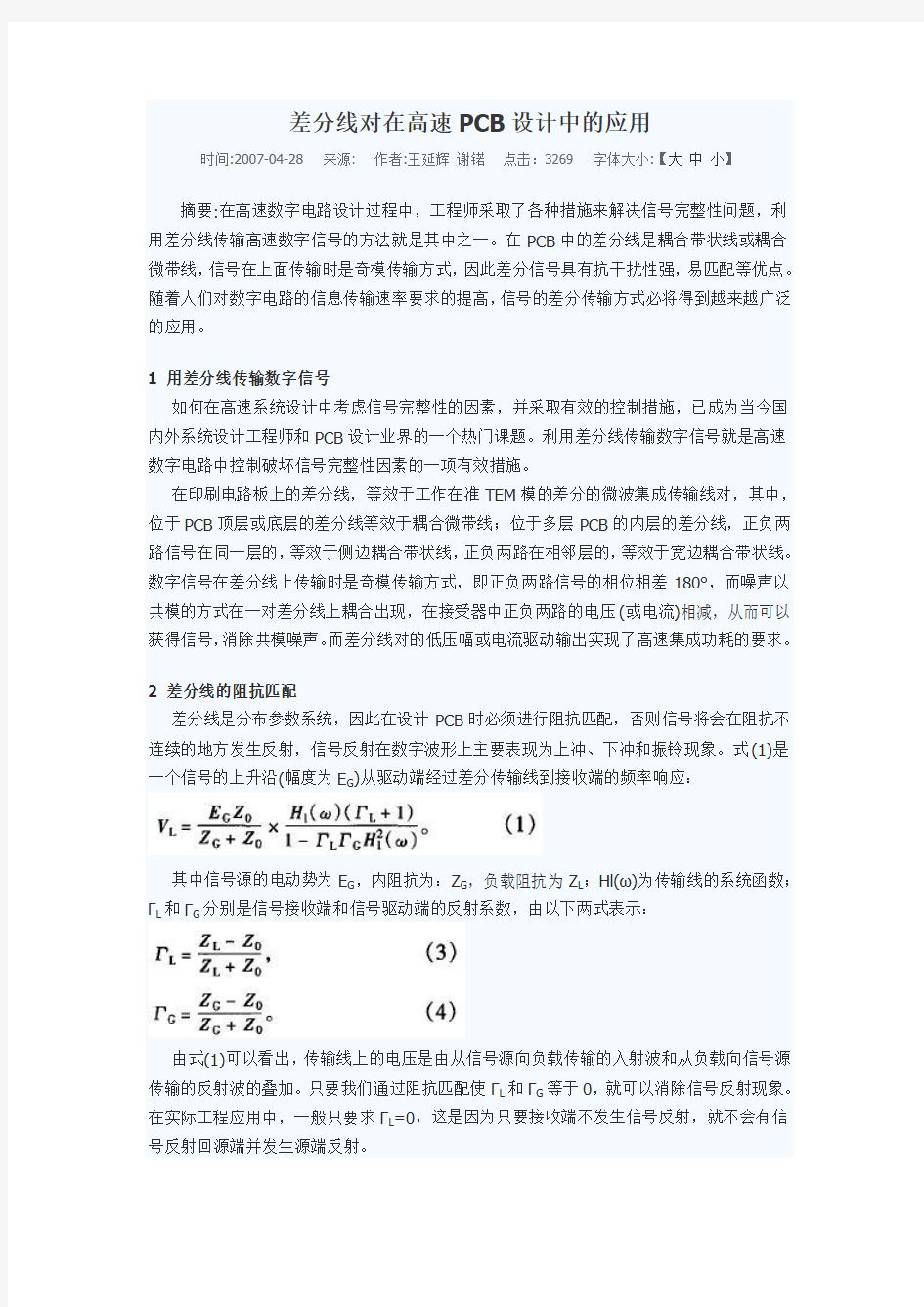

①LVDS电平信号的端接。

LVDS是一种低摆幅的差分信号技术,它上面的信号可以以几百Mbps的速率传输。LVDS 信号的驱动器由1个驱动差分线的电流源组成,通常电流为3.5 mA。它的端接电阻一般只要跨接在正负两路信号的中间就可以了,如图1所示。

LVDS信号的接受器一般具有很高的输入阻抗,因此驱动器输出的电流大部分都流过了100Ω的匹配电阻,并产生了350 mV的电压。有时为了增加抗噪声性能,差分线的正负两路信号之间用2个5OΩ的电阻串联,并在电阻中间加1个滤波电容到地,这样可以减少高频噪声。随着微电子技术的发展,很多器件生产商已经可以把LVDS电平信号的终端电阻做到器件内部,以减少PCB设计者的工作。

②LVPECL电平信号的端接。

LVPECL电平信号也是适合高速传输的差分信号电平之一,最快可以让信号以1 GBaud 波特的速率传输。它的每一单路信号都有一个比信号驱动电压小2 V的直流电位,因此应用终端匹配时不能在正负两条差分线之间跨接电阻(如果在差分线之间跨接电阻,电阻中间相当于虚地,直流电位将变成零),而只能将每一路进行单端匹配。

对LEPECL信号进行单端匹配,要符合2个条件,即信号的直流电位要为1.3 v(设驱动电压为3.3 V,减2后,为1.3 V)和信号的负载要等于信号线的特性阻抗(50Ω)。因此可以应用以下理想的端接方式:

在实际的工程设计中,增加一个电源就意味着增加了新的干扰源,也会增加布线空间(电源的滤波网络要使用大量的布线空间),改变电源分割层的布局。因此在设计系统时,可以利用交直流等效的方法,对图2中的端接方式进行了等效改变。

在图3中,对交流信号而言,相当于120Ω电阻和82Ω电阻并联,经计算为48.7Ω;对于直流信号,两个电阻分压,信号的直流电位为:3.3×82/(120+82)= 1.34 V。因此等效结果在工程应用的误差允许范围内。

4 差分线的一些设计规则

在做PCB板的实际工作中,应用差分线可以很大程度上提高信号线的抗干扰性,要想设计出满足信号完整性要求的差分线,除了要使负载和信号线的阻抗相匹配外,还要在设计中尽量避免阻抗不匹配的环节出现。现根据实际工作经验,总结出以下规则:

1.差分线离开器件引脚后,要尽量相互靠近,以确保耦合到信号线的噪声为共模噪声。

一般使用FR4介质时,50 Ω布线规则(差分线阻抗为100Ω)时,差分线之间的距离

要小于0.2 mm;

2.信号线的长度应匹配,不然会引起信号扭曲,引起电磁辐射;

3.不要仅仅依赖软件的自动布线功能,要仔细修改以实现差分线的阻抗匹配和隔离;

4.尽量减少使用过孔和其他一些引起阻抗不连续的因素;

5.不要使用90°走线,可用圆弧或45°折线代替;

6.信号线在不同的信号层时,要注意调整差分线的线宽和线距,避免因介质条件改变

引起的阻抗不连续。

5 结束语

在高速数字PCB设计中,运用差分线传输高速信号,一方面在对PCB系统的信号完整性和低功耗等方面大有裨益,另一方面也给的PCB设计水平提出了更高要求。作为设计者应该深刻理解传输线理论的有关概念,仔细分析出各种畸变现象的原因,找出合理有效的解决办法;还要不断把工作中积累的一些经验加以总结,并上升为理性认识,才能够取得满意的设计效果。

标签:无标签

高速PCB设计中差分线对走线策略

差分线对的工作原理是使接收到的信号等于两个互补并且彼此互为参考的信号之间的差值,因此可以极大地降低信号的电气噪声效应。而单端信号的工作原理是接收信号等于信号与电源或地之间的差值,因此信号或电源系统上的噪声不能被有效抵消。这就是差分信号对高速信号如此有效的原因,也是它用于快速串行总线和双倍数据率存储器的原因。

在差分线对中,正负两边都必须始终在相同的环境下沿着传输路径传送。正负两边必须紧靠在一起,以使正负信号经由这些信号上相应点的电磁场而彼此耦合。差分线对是对称的,因此它们的环境也必须对称。当然,完美的对称是不可能实现的,因为至少存在着尺寸公差。但设计师如果遵循一些基本规则还是可以获得接近理想的最佳差分信号结果。

建议

确保信号同一时间出现在每条线路的同一点上。要使走线的各段等长,如图中相同的字母表示的那样。如果差分线对带有串联端接电阻或共模滤波器,那么这些器件到差分驱动器正负两端引脚的连接距离应该是相等的。

最好按点到点布线,在任何情况下都要让分支线或支路(图中的C)保持在0.6Tr 英寸以内,这里Tr指驱动器输出上升时间。图中的A和E要尽可能使用相同的长度限制规则。

采用现场解决工具(field solver)设计走线间隔,这样可以方便地获得偶模和奇模阻抗值。50欧姆的电路板并不意味着偶模、奇模或差分特征阻抗也是50欧姆。

如果为了终止某个差分信号而将它端接到地或参考电压,就应考虑应害噪声着杂环境的影响被奇模阻抗。

还应考虑端接偶模或共模(偶模值的一半)以终止有害噪声。

如果在两条线间端接,应考虑差模阻抗(奇模阻抗的两倍)。

记住,只有在差分线对紧密耦合时,来自同一个源的辐射噪声才能被有效抑制,因为只有当走线彼此靠得非常近时,周围的电磁场才可能接近相同。

延长走线长度以便补偿互补输出信号之间的任何偏移都要在靠近驱动器处进行。

尽可能只以差分方式延长走线长度,记住左右弯曲的数量和风格应该保持平衡。

图:在差分线对中,正负两边都必须始终在相同的环境下沿着传输路径传送。避免

用单端特征阻抗代替奇模和偶模阻抗作为终端阻抗:紧密耦合的差分线对是专门针对互补信号设计的。

只是保证走线总长度相等,而不是确保走线的每一段都相等。

差分线对的布线跨越电源或地平面的间隙。

在使用自动布线工具时忘记定义差分线对,这样只能得到单端布线。

让测试工程师在差分线对每一边的不同位置增加测试焊盘。测试焊盘相当于高阻抗器件的输入,因此很容易使差分线对失去平衡。

其它信号的布线过于平行地接近差分线对,或正好在下面或上面的另一层上,它们产生的串扰可能让差分信号失去平衡。

?在不相关的电源或地平面(例如单独的模拟电源平面) 的上面或下面布线差分

线对。

忘了考虑板外连接去向。在利用仿真检查目标电路时,系统中其它板上的连接器、电缆和差分拓扑都应被建模。

被探针或测试设备的寄生电感和电容所蒙蔽。如果在差分线对的一边放置一个探针,很可能会致使差分线对失去平衡,这时的测量很容易被误导,设备也很可能在这种测试情况下出现假故障。

pcb设计心得体会范文 一些基本操作,对更深层的有些就不是很了解了。但是时间有限,只有一个星期实训pcb电路板,老师能教给我们的也只有这么多了,剩下的只有靠我们自己回去自己学习了,作为电子工程系的一名学生,深知掌握这些装也软件的重要性,因为以后我们从事的技术工作需要这些软件工具。 第一天搭接电路,还比较简单,只是有点麻烦,电路搭接好后就要开始封装各个元器件的封装,这就需要很大的耐心,一个一个元器件的进行封装,还不能弄错,不然后面就生成不了报表,生成不了报表,后面进行电路板设计的时候就会导入错误,以致不能进行电路板设计。后面用pcbediter 进行设计电路板设计要导入报表,然后才能开始布局和布线,由于导入的库文件里面没有sop8和sop28两个焊盘的封装,因此在进行设计电路板之前,要先设计那两个器件的焊盘的封装,然后导入库函数,才能导入报表的时候不会报错。不过导入的时候也遇到了一些问题,会提示二极管的管脚不匹配,譬如多一个2脚,少一个3角,然后就觉得很神奇,二极管就只有两个管脚怎么会有3脚了。后面通过老师的讲解,

才明白,原来设计电路板的时候只认封装,不认元器件,是根据封装导入元器件,因此在设计封装的时候,管脚是怎么设计,在原理图里面就要把元器件的管脚改成和封装一样,后面把原理图的管脚改成和导入库函数里面的封装一样,提示就没有了,不过后面又遇到一些小问题,譬如说,下划线写成横线了,然后就有报错,找不到元器件的封装。这给我警示,在原理图的时候,要仔细认真的把管脚封装写对,最然会很麻烦。后面导入报表,开始设计电路板,先开始是布局,大致步好后,然后就开始用软件自带的自动布线,结果发现有很多蝴蝶结,为什么要自动布线,因为最开始我认为如果自动布线可以的话,那手动布线肯定也可以,结果后面一直自动布线不成功。后面老师讲解,才知道,不一定要自动布线成功才能手动布线,浪费了好多时间,以至于后面都要重新排,因为最开始没有把原理图的元器件分块布局,完全是凭感觉乱布局的,后面就是一大片密密麻麻的线,而且很多元器件接点的线都有点长。后面按块先布局,然后再整体布局,然后再微小变动,这样,线明显变少了,而且元器件的接点的线都很少很长了,这样就方便后面的布线了。所以说,布局那是相当的重要啊,先考虑局部,然后再考虑整体。布局步好后,布线就很快了,也没有花多少时间布局,步好后,看了下,还是感觉蛮好的,再没有布电源和地线的情况下,总共打了21个孔,总之,布线的图看起还是蛮自

[讨论]今天终于弄懂了PCB高速电路板设计的方法和技巧受益匪浅啊 电容, 最大功率, 技巧 高速电路设计技术阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,并且得到最大功率输出的一种工作状态。高速PCB布线时,为了防止信号的反射,要求线路的阻抗为50Ω。这是个大约的数字,一般规定同轴电缆基带50Ω,频带75Ω,对绞线则为100Ω,只是取整数而已,为了匹配方便。根据具体的电路分析采用并行AC端接,使用电阻和电容网络作为端接阻抗,端接电阻R要小于等于传输线阻抗Z0,电容C必须大于100pF,推荐使用0.1UF的多层陶瓷电容。电容有阻低频、通高频的作用,因此电阻R不是驱动源的直流负载,故这种端接方式无任何直流功耗。 串扰是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生不期望的电压噪声干扰。耦合分为容性耦合和感性耦合,过大的串扰可能引起电路的误触发,导致系统无法正常工作。根据串扰的一些特性,可以归纳出几种减小串扰的方法: 1、加大线间距,减小平行长度,必要时采用jog 方式布线。 2、高速信号线在满足条件的情况下,加入端接匹配可以减小或消除反射,从而减小串扰。 3、对于微带传输线和带状传输线,将走线高度限制在高于地线平面范围要求以内,可以显著减小串扰。 4、在布线空间允许的条件下,在串扰较严重的两条线之间插入一条地线,可以起到隔离的作用,从而减小串扰。传统的PCB设计由于缺乏高速分析和仿真指导,信号的质量无法得到保证,而且大部分问题必须等到制版测试后才能发现。这大大降低了设计的效率,提高了成本,在激烈的市场竞争下显然是不利的。于是针对高速PCB设计,业界人士提出了一种新的设计思路,成为“自上而下”的设计方法,经过多方面的方针分析和优化,避免了绝大部分可能产生的问题,节省了大量的时间,确保满足工程预算,产生高质量的印制板,避免繁琐而高耗的测试检错等。利用差分线传输数字信号就是高速数字电路中控制破坏信号完整性因素的一项有效措施。在印制电路板(PCB抄板)上的差分线,等效于工作在准TEM模的差分的微波集成传输线对。其中,位于PCB顶层或底层的差分线等效于耦合微带线,位于多层PCB内层的差分线,等效于宽边耦合带状线。数字信号在差分线上传输时是奇模传输方式,即正负两路信号的相位差是180,而噪声以共模的方式在一对差分线上耦合出现,在接受器中正负两路的电压或电流相减,从而可以获得信号消除共模噪声。而差分线对的低压幅或电流驱动输出实现了高速集成低功耗的要求。

本文主要使用时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计。 1 概述 当今计算机系统DDR3存储器技术已得到广泛应用,数据传输率一再被提升,现已高达1866Mbps。在这种高速总线条件下,要保证数据传输质量的可靠性和满足并行总线的时序要求,对设计实现提出了极大的挑战。 本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性和安全性大大提高。 2 DDR3介绍 DDR3内存与DDR2内存相似包含控制器和存储器2个部分,都采用源同步时序,即选通信号(时钟)不是独立的时钟源发送,而是由驱动芯片发送。它比DR2有更高的数据传输率,最高可达1866Mbps;DDR3还采用8位预取技术,明显提高了存储带宽;其工作电压为1.5V,保证相同频率下功耗更低。 DDR3接口设计实现比较困难,它采取了特有的Fly-by拓扑结构,用“Write leveling”技术来控制器件内部偏移时序等有效措施。虽然在保证设计实现和信号的完整性起到一定作用,但要实现高频率高带宽的存储系统还不全面,需要进行仿真分析才能保证设计实现和信号质量的完整性。 3 仿真分析 对DDR3进行仿真分析是以结合项目进行具体说明:选用PowerPC 64位双核CPU 模块,该模块采用Micron公司的MT41J256M16HA—125IT为存储器。Freescale 公司P5020为处理器进行分析,模块配置内存总线数据传输率为1333MT/s,仿真频率为666MHz。 3.1仿真前准备 在分析前需根据DDR3的阻抗与印制板厂商沟通确认其PCB的叠层结构。在高速传输中确保传输线性能良好的关键是特性阻抗连续,确定高速PCB信号线的阻抗控制在一定的范围内,使印制板成为“可控阻抗板”,这是仿真分析的基础。DDR3总线单线阻抗为50Ω,差分线阻抗为100Ω。 设置分析网络终端的电压值;对分析的器件包括无源器件分配模型;确定器件类属性;确保器件引脚属性(输入\输出、电源\地等)……

pcb设计心得体会范文 篇一:PCB电路板设计总结 经过五天的PCB电路板训练,通过对软件的使用,以及实际电路板的设计,对电路板有了更深的认识,知道了电路板的相关知识和实际工作原理。同时也感受到了电路板的强大能力,怪不得现在的电路都是采用集成的电路板电路,因为它实在是有太多的好处,节约空间,方便接线,能大大缩小电路的体积。方便人类小型电器的发明。但是电路板也有一定缺陷,就是太小了,散热不是特别好,这就使得器件的性能不能像想象中那么好。 通过使用,不得不说cadence软件确实很好用,功能太强大,而且也很方便使用,接线,布线,绘制电路板等,很方便使用,不过有一点就是,器件接线的时候不能直接把器件接到导线上,这点不够人性化。虽然说,软件学了五天时间,不过对软件使用还不是能完全掌握,只能掌握一些基本操作,对更深层的有些就不是很了解了。但是时间有限,只有一个星期实训PCB电路板,老师能教给我们的也只有这么多了,剩下的只有靠我们自己回去自己学习了,作为电子工程系的一名学生,深知掌握这些装也软件的重要性,因为以后我们从事的技术工作需要这些软件工具。 第一天搭接电路,还比较简单,只是有点麻烦,电路搭接好后就要开始封装各个元器件的封装,这就需要很大的耐心,一个一个元器件的进行封装,还不能弄错,不然后面就生成不了报表,生成不了报

表,后面进行电路板设计的时候就会导入错误,以致不能进行电路板设计。后面用PCB Editer 进行设计电路板设计要导入报表,然后才能开始布局和布线,由于导入的库文件里面没有sop8和sop28两个焊盘的封装,因此在进行设计电路板之前,要先设计那两个器件的焊盘的封装,然后导入库函数,才能导入报表的时候不会报错。不过导入的时候也遇到了一些问题,会提示二极管的管脚不匹配,譬如多一个2脚,少一个3角,然后就觉得很神奇,二极管就只有两个管脚怎么会有3脚了。后面通过老师的讲解,才明白,原来设计电路板的时候只认封装,不认元器件,是根据封装导入元器件,因此在设计封装的时候,管脚是怎么设计,在原理图里面就要把元器件的管脚改成和封装一样,后面把原理图的管脚改成和导入库函数里面的封装一样,提示就没有了,不过后面又遇到一些小问题,譬如说,下划线写成横线了,然后就有报错,找不到元器件的封装。这给我警示,在原理图的时候,要仔细认真的把管脚封装写对,最然会很麻烦。后面导入报表,开始设计电路板,先开始是布局,大致步好后,然后就开始用软件自带的自动布线,结果发现有很多蝴蝶结,为什么要自动布线,因为最开始我认为如果自动布线可以的话,那手动布线肯定也可以,结果后面一直自动布线不成功。后面老师讲解,才知道,不一定要自动布线成功才能手动布线,浪费了好多时间,以至于后面都要重新排,因为最开始没有把原理图的元器件分块布局,完全是凭感觉乱布局的,后面就是一大片密密麻麻的线,而且很多元器件接点的线都有点长。后面按块先布局,然后再整体布局,然后再微小变动,这样,线明显变

高速PCB设计指南 第一篇 PCB布线 在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的,在整个PCB中,以布线的设计过程限定最高,技巧最细、工作量最大。PCB布线有单面布线、双面布线及多层布线。布线的方式也有两种:自动布线及交互式布线,在自动布线之前,可以用交互式预先对要求比较严格的线进行布线,输入端与输出端的边线应避免相邻平行,以免产生反射干扰。必要时应加地线隔离,两相邻层的布线要互相垂直,平行容易产生寄生耦合。 自动布线的布通率,依赖于良好的布局,布线规则可以预先设定,包括走线的弯曲次数、导通孔的数目、步进的数目等。一般先进行探索式布经线,快速地把短线连通,然后进行迷宫式布线,先把要布的连线进行全局的布线路径优化,它可以根据需要断开已布的线。并试着重新再布线,以改进总体效果。 对目前高密度的PCB设计已感觉到贯通孔不太适应了,它浪费了许多宝贵的布线通道,为解决这一矛盾,出现了盲孔和埋孔技术,它不仅完成了导通孔的作用,还省出许多布线通道使布线过程完成得更加方便,更加流畅,更为完善,PCB 板的设计过程是一个复杂而又简单的过程,要想很好地掌握它,还需广大电子工程设计人员去自已体会,才能得到其中的真谛。 1 电源、地线的处理

既使在整个PCB板中的布线完成得都很好,但由于电源、地线的考虑不周到而引起的干扰,会使产品的性能下降,有时甚至影响到产品的成功率。所以对电、地线的布线要认真对待,把电、地线所产生的噪音干扰降到最低限度,以保证产品的质量。 对每个从事电子产品设计的工程人员来说都明白地线与电源线之间噪音所产生的原因,现只对降低式抑制噪音作以表述: (1)、众所周知的是在电源、地线之间加上去耦电容。 (2)、尽量加宽电源、地线宽度,最好是地线比电源线宽,它们的关系是:地线>电源线>信号线,通常信号线宽为:0.2~0.3mm,最经细宽度可达0.05~0.07mm,电源线为1.2~2.5 mm 对数字电路的PCB可用宽的地导线组成一个回路, 即构成一个地网来使用(模拟电路的地不能这样使用) (3)、用大面积铜层作地线用,在印制板上把没被用上的地方都与地相连接作为地线用。或是做成多层板,电源,地线各占用一层。 2 数字电路与模拟电路的共地处理 现在有许多PCB不再是单一功能电路(数字或模拟电路),而是由数字电路和模拟电路混合构成的。因此在布线时就需要考虑它们之间互相干扰问题,特别是地线上的噪音干扰。 数字电路的频率高,模拟电路的敏感度强,对信号线来说,高频的信号线尽可能远离敏感的模拟电路器件,对地线来说,整人PCB对外界只有一个

《高速电路板设计与仿真》课程教学大纲 课程代码:030442003 课程英文名称:High Speed Printed Circuit Board Design and Emulation 课程类别:专业基础课 课程性质:选修 适用专业:电子科学与技术 课程总学时:40 讲课:40 实验:0 上机:0 大纲编写(修订)时间:2011.7 一、大纲使用说明 (一)课程的地位及教学目标 本课程是电子科学与技术专业的专业任选课, 属于专业技术基础课,是一门重要的实践课程。通过本课程的学习,学生能够利用先进的高端软件设计高速电路板,绘制出具有实际意义的原理图和印刷电路板图,具有对设计中的信号完整性、电磁兼容性、电源完整性等问题的分析能力,熟悉一定的电子工艺和印刷电路板的布局布线知识,为今后从事高端设计工作打下一定的基础。 (二)知识、能力及技能方面的基本要求 在知识方面,要求学生具有初步的半导体工艺、印制电路、芯片封装等方面的知识,还要了解信号完整性、电磁兼容性、电源完整性等方面的基本概念,如此才能设计出高质量的高速PCB。在能力方面,要求学生具备一些计算机方面的操作技能。 (三)实施说明 1.教学内容:包括原理图设计、PCB设计、高速信号仿真三部分,其中PCB设计为重点内容。应突出高速和高质量PCB的讲解,以适应高端设计要求。讲课要理论联系实际,设计具有实际意义的原理图和印刷电路板图,而不只是空讲理论知识。 2.教学方法:采用启发式教学,提高学生分析问题和解决问题的能力。鼓励学生通过实践和自学获取知识,培养学生的自学能力,调动学生自行设计的学习积极性和创新能力。 3.教学手段:本课程属于技术基础课,在教学中可采用电子教案、CAI课件及多媒体教学系统等先进教学手段,以确保在有限的学时内,全面、高质量地完成课程教学任务。 4.大纲实施时应贯彻学院工程训练与工程教育相结合的特点,注重学生的能力培养和专业素质的提高,尤其是培养学生的实际动手设计和操作的能力。 (四)对先修课的要求 本课程的先修课为电路、模拟电子电路、数字电子电路、计算机基础知识。 (五)对习题课、实践环节的要求 每次课后留有一定量的操作练习,要求学生课后在自己的电脑上学习操作。本课程无实验。 (六)课程考核方式 1.考核方式:考查 2.考核目标:考核学生是否掌握了软件的基本操作方法,重点考核学生的原理图绘制和印刷电路板的设计能力,所设计的项目是否具有实际意义。 3.成绩构成:本课程的总成绩由两部分组成:平时成绩(包括平时自行练习、出勤等)占20%,期末验收成绩(以综合作业完成情况给出成绩)占80%。按优、良、中、及格、不及格五级给出最后成绩。 (七)参考书目 《Cadence SPB 15.7工程实例入门》于争著,电子工业出版社, 2010.5.

高速PCB设计中终端匹配电阻的放置 胡为东1 (西安电子科技大学电子工程学院西安 710071) 摘要:本文简要的总结了在高速数字设计中串联终端匹配和并联终端匹配的优缺点,并对这两种匹配方式的终端匹配电阻处于不同位置时的匹配效果做了相应的仿真和深入的分析,得出了串联终端匹配电阻对位置的要求没有终端匹配电阻严格这一结论,给出了一些关于终端匹配电阻摆放位置的建议。为在PCB设计中如何放置终端匹配电阻提供了理论和实践上的指导。 关键词:并联终端匹配串联终端匹配放置 Termination Placement in High-Speed PCB Design HU Wei-dong (Electronic Engineering of Xidian University . Xi’an 710071) Abstract: This paper gives the advantages and disadvantages of the parallel and series termination in high-speed digital design. Proper simulation and deep analysis are done as terminations are located in different points. A conclusion is got that series terminated circuits are much less affected by placement compromises than parallel terminated circuits , and some suggestions are made on where termination should be located. A theoretic and practical direction is given on how to place the termination in high-speed PCB design. key words: Parallel Termination Series Termination Placement 1胡为东,男,1979年11月出生,西安电子科技大学硕士研究生。主要研究方向:高速板卡和高速PCB设计及仿真、信号完整性及电源完整性分析。

随着信息宽带化和高速化的发展,以前的低速PCB已完全不能满足日益增长信息化发展的需要,人们对通信需求的不断提高,要求信号的传输和处理的速度越来越快,相应的高速PCB的应用也越来越广,设计也越来越复杂。高速电路有两个方面的含义,一是频率高,通常认为数字电路的频率达到或是超过45MHZ 至50MHZ,而且工作在这个频率之上的电路已经占到了整个系统的三分之一,就称为高速电路;二是从信号的上升与下降时间考虑,当信号的上升时小于6倍信号传输延时时即认为信号是高速信号,此时考虑的与信号的具体频率无关。高速PCB的出现将对硬件人员提出更高的要求,仅仅依靠自己的经验去布线,会顾此失彼,造成研发周期过长,浪费财力物力,生产出来的产品不稳定。 高速电路设计在现代电路设计中所占的比例越来越大,设计难度也越来越高,它的解决不仅需要高速器件,更需要设计者的智慧和仔细的工作,必须认真研究分析具体情况,解决存在的高速电路问题。一般说来主要包括三方面的设计:信号完整性设计、电磁兼容设计、电源完整性设计。 在电子系统与电路全面进入1GHz以上的高速高频设计领域的今天,在实现VLSI芯片、PCB和系统设计功能的前提下具有性能属性的信号完整性问题已经成为电子设计的一个瓶颈。从广义上讲,信号完整性指的是在高速产品中有互连线引起的所有问题,它主要研究互连线与数字信号的电压电流波形相互作用时其电气特性参数如何影响产品的性能。 传统的设计方法在制作的过程中没有仿真软件来考虑信号完整性问题,产品首次成功是很难的,降低了生产效率。只有在设计过程中融入信号完整性分析,才能做到产品在上市时间和性能方面占优势。对于高速PCB设计者来说,熟悉信号完整性问题机理理论知识、熟练掌握信号完整性分析方法、灵活设计信号完整性问题的解决方案是很重要的,因为只有这样才能成为21世纪信息高速化的成功硬件工程师。 信号完整性的研究还是一个不成熟的领域,很多问题只能做定性分析,为此,在设计过程中首先要尽量应用已经成熟的工程经验;其次是要对产品的性能做出预测和评估以及仿真。在设计过程中可以不断积累分析能力,不断创新解决信号完整性的方法,利用仿真工具可以得到检验。 第二章:Candence Allegro PCB简介

干货-PCB设计经验总结 随着新能源汽车的发展,汽车电气化越来越严重,相关的EMC问题也越来越突出,因此为了从根本上降低EMC的风险,需要从设计阶段尤其是PCB layout 入手,来防患于未然。下面是一位从业十余年的硬件工程师的经验笔记! 如觉得有帮助欢迎支持转发分享给更多需要的人! 叠层: 1.电源和地的平面尽可能近(利于电源噪声高频滤波) 2.信号层:避免两信号层相邻(如果必须相邻,加大两层间距); 3.电源层:避免两电源层相邻; 4.外层:铺地; 布线: 5.关键信号线:避免跨分割(参考平面); 6.关键信号线:“换层不换面(参考平面)”; 7.关键信号线:长度尽可能短; 8.关键信号线:位置远离PCB板边缘及接口; 9.信号线:不能跨越分割间隙布线(否则电磁辐射及信号串扰剧增);

10.信号线:换层(返回路径)必须跨分割时,须使用过孔或滤波电容(10nf); 11.总线:相同功能的并行布置,中间勿参杂其他信号; 12.接收发送信号:分开布线,勿交叉; 13.高速信号线:走线宽度勿突变; 14.电源:电源线不要形成环路(近似包裹的环路) 15.地:地线不要形成环路(近似包裹的环路); 16.地:干扰源的地勿与信号地就近共用(晶振等干扰源的地不干净); 17.地:多芯片并排共电源与地时,电源与地的主线路宜在芯片同侧(回流面积小); 18.分割:模拟地与数字地分割布线,建立“地连接桥”,如有必要进行磁珠滤波; 19.分割:电源/地平面分割需合理(否则高速信号存在EMI、EMC风险); 20.拐角走线:优选45度(降低拐角对走线阻抗影响) 21.拐角走线:长度越长越好(降低拐角对走线阻抗影响) 22.拐角走线:过孔处上下走线拐角要求同上; 23.高频干扰源:下方禁止布线(晶振、开关电源等干扰源); 24.高频干扰源:附近尽量避免布电源主路线(晶振、开关电源等干扰源); 25.接插件:下方禁止布线; 电源滤波: 26.滤波区域为原理信号区域(降低耦合); 27.高频滤波电容需靠近电源PIN脚(容值越小越近);

电源完整性与地弹噪声的高速PCB仿真 作者:Martin Vogel 和Brad Cole,Ansoft 公司使用基于电磁场分析的设计软件来选择退耦电容的大小及其放置位置可将电源平面与地平面的开关噪声减至最小。 随着信号的沿变化速度越来越快,今天的高速数字电路板设计者所遇到的问题在几年前看来是不可想象的。对于小于1纳秒的信号沿变化,PCB板上电源层与地层间的电压在电路板的各处都不尽相同,从而影响到IC芯片的供电,导致芯片的逻辑错误。为了保证高速器件的正确动作,设计者应该消除这种电压的波动,保持低阻抗的电源分配路径。 为此,你需要在电路板上增加退耦电容来将高速信号在电源层和地层上产生的噪声降至最低。你必须知道要用多少个电容,每一个电容的容值应该是多大,并且它们放在电路板上什么位置最为合适。一方面你可能需要很多电容,而另一方面电路板上的空间是有限而宝贵的,这些细节上的考虑可能决定设计的成败。 反复试验的设计方法既耗时又昂贵,结果往往导致过约束的设计从而增加不必要的制造成本。使用软件工具来仿真、优化电路板设计和电路板资源的使用情况,对于要反复测试各种电路板配置方案的设计来说是一种更为实际的方法。本文以一个xDSM(密集副载波多路复用)电路板的设计为例说明此过程,该设计用于光纤/宽带无线网络。软件仿真工具使用Ansoft的SIwave,SIwave基于混合全波有限元技术,可以直接从layout工具Cadence Allegro, Mentor Graphics BoardStation, Synopsys Encore和Zuken CR-5000 Board Designer导入电路板设计。图1是SIwave中该设计的PCB版图。由于PCB的结构是平面的,SIwave可以有效的进行全面的分析,其分析输出包括电路板的谐振、阻抗、选定网络的S参数和电路的等效Spice模型。 图1, SIwave中xDSM电路板的PCB版图,左边是两个高速总线,右边是三个Xilinx的FPGA。 xDSM电路板的尺寸,也就是电源层和地层的尺寸是11×7.2 英寸(28×18.3 厘米)。电源层和地层都是1.4mil厚的铜箔,中间被23.98mil厚的衬底隔开。 为了理解对电路板的设计,首先考虑xDSM电路板的裸板(未安装器件)特性。根据电路板上高速信号的上升时间,你需要了解电路板在频域直到2GHz范围内的特性。图2所示为一个正弦信号激励电路板谐振于0.54GHz时的电压分布情况。同样,电路板也会谐振于0.81GHz和0.97GHz以及更高的频率。为了更好地理解,你也可以在这些频率的谐振模式下仿真电源层与地层间电压的分布情况。 图2所示在0.54GHz的谐振模式下,电路板的中心处电源层和地层的电压差变化为零。对于一些更高频率的谐振模式,情况也是如此。但并非在所有的谐振模式下都是如此,例如在1.07GHz、1.64GHz和1.96 GHz的高阶谐振模式下,电路板中心处的电压差变化是不为零的。

PCB设计总结 、概述 PCB是一个连接电子元器件的载体。PCB设计是一个把原理设计上的电气连接变成实实在 在的,可用的线路连接。简单的PCB设计就是将器件的管脚按照一定的需要连通,但对于 高速,高密度的PCB设计,涉及到很多的方面,包括结构方面,信号完整性,EMC,EMI, 电源设计,加工工艺方面等等。 、布局 1材料 PCB材料很多,我们目前使用的基本都是FR4的,TG参数(高耐热性)是一个很重要的指 标,一般结构工程师会在他们提供的cutout里面给出TG参数的要求。 2合理的层数安排 一块板PCB层数多少合适,要基于生产成本和信号质量需求两方面考虑。对于速度低,密度小的板块,可以考虑层数少些,对于高速,高密度板,要尽可能多的安排完整的电地层,以保证较好的信号质量。 3电源层和地层 3.1、电源层和地层的作用和区别 电源层和地层都可以作为参考平面,在一定程度上来说他们是一样的。但是,相对来说,电源平面的特性阻抗较高,与参考平面存在较大的电位势差。而地平面作为地基准,地平面的屏蔽作用要远远好于电源屏幕,对于重要信号,最好选择地平面作为参考屏幕。 3.2、电源层,信号层,地层位置 A、第二层为地层,用于屏蔽器件(如果有更重要的信号需要地,可以进行调整) B、所有信号层都有参考平面。 C、最好不要相邻信号层,有的话,要安排信号走向为垂直方向。 D、关键信号参考平面为完整的地平面不跨分割区。

3.3、几种常用的板子的叠层方案 四层版 BOT 在该方案中表层具有较好的信号质量,对器件也有较好的屏蔽,使电源层和地层距离适当拉近,可以降低电源地的分布阻抗,保证电源地的去耦效果。 其它一些方案参考 paul wang发的一份emc规范。

mp3的设计原理及制作 高速PCB设计指南之一 第一篇PCB布线 在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的,在整个PCB中,以布线的设计过程 限定最高,技巧最细、工作量最大。PCB布线有单面布线、双面布线及多层布线。布线的方式也有两种:自动布线及交互式布 线,在自动布线之前,可以用交互式预先对要求比较严格的线进行布线,输入端与输出端的边线应避免相邻平行,以免产生 反射干扰。必要时应加地线隔离,两相邻层的布线要互相垂直,平行容易产生寄生耦合。 自动布线的布通率,依赖于良好的布局,布线规则可以预先设定,包括走线的弯曲次数、导通孔的数目、步进的数目等。一般 先进行探索式布经线,快速地把短线连通,然后进行迷宫式布线,先把要布的连线进行全局的布线路径优化,它可以根据需要 断开已布的线。并试着重新再布线,以改进总体效果。 对目前高密度的PCB设计已感觉到贯通孔不太适应了,它浪费了许多宝贵的布线通道,为解决这一矛盾,出现了盲孔和埋孔技 术,它不仅完成了导通孔的作用,还省出许多布线通道使布线过程完成得更加方便,更加流畅,更为完善,PCB 板的设计过 程是一个复杂而又简单的过程,要想很好地掌握它,还需广大电子工程设计人员去自已体会,才能得到其中的真谛。 1 电源、地线的处理 既使在整个PCB板中的布线完成得都很好,但由于电源、地线的考虑不周到而引起的干扰,会使产品的性能下降,有时甚至影 响到产品的成功率。所以对电、地线的布线要认真对待,把电、地线所产生的噪音干扰降到最低限度,以保证产品的质量。 对每个从事电子产品设计的工程人员来说都明白地线与电源线之间噪音所产生的原因,现只对降低式抑制噪音作以表述: (1)、众所周知的是在电源、地线之间加上去耦电容。 (2)、尽量加宽电源、地线宽度,最好是地线比电源线宽,它们的关系是:地线>电源线>信号线,通常信号线宽为:0.2~ 0.3mm,最经细宽度可达0.05~0.07mm,电源线为1.2~2.5 mm。对数字电路的PCB可用宽的地导线组成一个回路, 即构成一个 地网来使用(模拟电路的地不能这样使用) (3)、用大面积铜层作地线用,在印制板上把没被用上的地方都与地相连接作为地线用。或是做成多层板,电源,地线各占用 一层。 2 数字电路与模拟电路的共地处理 现在有许多PCB不再是单一功能电路(数字或模拟电路),而是由数字电路和模拟电路混合构成的。因此在布线时就需要考虑 它们之间互相干扰问题,特别是地线上的噪音干扰。 数字电路的频率高,模拟电路的敏感度强,对信号线来说,高频的信号线尽可能远离敏感的模拟电路器件,对地线来说,整人 PCB对外界只有一个结点,所以必须在PCB内部进行处理数、模共地的问题,而在板内部数字地和模拟地实际上是分开的它们 之间互不相连,只是在PCB与外界连接的接口处(如插头等)。数字地与模拟地有一点短接,请注意,只有一个连接点。也有 在PCB上不共地的,这由系统设计来决定。 3 信号线布在电(地)层上 在多层印制板布线时,由于在信号线层没有布完的线剩下已经不多,再多加层数就会造成浪费也会给生产增加一定的工作量, 成本也相应增加了,为解决这个矛盾,可以考虑在电(地)层上进行布线。首先应考虑用电源层,其次才是地层。因为最好是 保留地层的完整性。 4 大面积导体中连接腿的处理 在大面积的接地(电)中,常用元器件的腿与其连接,对连接腿的处理需要进行综合的考虑,就电气性能而言,元件腿的焊盘 与铜面满接为好,但对元件的焊接装配就存在一些不良隐患如:①焊接需要大功率加热器。②容易造成虚焊点。所以兼顾电气 性能与工艺需要,做成十字花焊盘,称之为热隔离(heat shield)俗称热焊盘(Thermal),这样,可使在焊接时因截面过分散 热而产生虚焊点的可能性大大减少。多层板的接电(地)层腿的处理相同。 5 布线中网络系统的作用 在许多CAD系统中,布线是依据网络系统决定的。网格过密,通路虽然有所增加,但步进太小,图场的数据量过大,这必然对 设备的存贮空间有更高的要求,同时也对象计算机类电子产品的运算速度有极大的影响。而有些通路是无效的,如被元件腿的 焊盘占用的或被安装孔、定们孔所占用的等。网格过疏,通路太少对布通率的影响极大。所以要有一个疏密合理的网格系统来 支持布线的进行。 标准元器件两腿之间的距离为0.1英寸(2.54mm),所以网格系统的基础一般就定为0.1英寸(2.54 mm)或小于0.1英寸的整倍数, 如:0.05英寸、0.025英寸、0.02英寸等。 6 设计规则检查(DRC) 布线设计完成后,需认真检查布线设计是否符合设计者所制定的规则,同时也需确认所制定的规则是否符合印制板生产工艺的 需求,一般检查有如下几个方面: (1)、线与线,线与元件焊盘,线与贯通孔,元件焊盘与贯通孔,贯通孔与贯通孔之间的距离是否合理,是否满足生产要 求。 (2)、电源线和地线的宽度是否合适,电源与地线之间是否紧耦合(低的波阻抗)?在PCB中是否还有能让地线加宽的地 方。 (3)、对于关键的信号线是否采取了最佳措施,如长度最短,加保护线,输入线及输出线被明显地分开。 (4)、模拟电路和数字电路部分,是否有各自独立的地线。 (5)后加在PCB中的图形(如图标、注标)是否会造成信号短路。 (6)对一些不理想的线形进行修改。 (7)、在PCB上是否加有工艺线?阻焊是否符合生产工艺的要求,阻焊尺寸是否合适,字符标志是否压在器件焊盘上,以免影 响电装质量。 (8)、多层板中的电源地层的外框边缘是否缩小,如电源地层的铜箔露出板外容易造成短路。 Copyright by BroadTechs Electronics Co.,Ltd 2001-2002

高速高密度PCB设计的现状 随着电子产品功能的日益复杂和性能的提高,印刷电路板的密度和其相关器件的频率都不断攀升,工程师面临的高速高密度PCB设计所带来的各种挑战也不断增加。下面为大家准备了关于高速高密度PCB设计的现状,欢迎阅读。 随着竞争的日益加剧,厂商面临的产品面世时间的压力也越来越大,如何利用先进的EDA工具以及最优化的方法和流程,高质量、高效率的完成设计,已经成为系统厂商和设计工程师不得不面对的问题。 热点:从信号完整性向电源完整性转移 谈到高速设计,人们首先想到的就是信号完整性问题。信号完整性主要是指信号在信号线上传输的质量,当电路中信号能以要求的时序、持续时间和电压幅度到达接收芯片管脚时,该电路就有很好的信号完整性。当信号不能正常响应或者信号质量不能使系统长期稳定工作时,就出现了信号完整性问题,信号完整性主要表现在延迟、反射、串扰、时序、振荡等几个方面。一般认为,当系统工作在50MHz 时,就会产生信号完整性问题,而随着系统和器件频率的不断攀升,信号完整性的问题也就愈发突出。元器件和PCB板的参数、元器件在PCB板上的布局、高速信号的布线等这些问题都会引起信号完整性问题,导致系统工作不稳定,甚至完全不能正常工作。 信号完整性技术经过几十年的发展,其理论和分析方法都已经较为成熟。对于信号完整性问题,陈兰兵认为,信号完整性不是某个

人的问题,它涉及到设计链的每一个环节,不但系统设计工程师、硬件工程师、PCB工程师要考虑,甚至在制造时也不能忽视。解决信号完整性问题,必须借助先进的仿真工具,如Cadence的SPECCTRAQuest 就是不错的仿真工具,利用它可以在设计前期进行建模、仿真,从而形成约束规则指导后期的布局布线,提高设计效率。随着Cadence 在今年6月推出的专门针对千兆赫信号的仿真器MGH——它是业界首个可以在几秒之内完成数万BIT千兆赫信号的仿真器——信号完整性 技术更臻完善。 相对于信号完整性,电源完整性是一种较新的技术,它被认为是高速高密度PCB设计目前最大的挑战之一。电源完整性是指在高速系统中,电源传输系统(PDS power deliver system)在不同频率上,阻抗特性不同,使PCB板上电源层与地层间的电压在电路板的各处不尽相同,从而造成供电不连续,产生电源噪声,使芯片不能正常工作;同时由于高频辐射,电源完整性问题还会带来EMC/EMI问题。如果不能很好地解决电源完整性问题,会严重影响系统的正常工作。 通常,电源完整性问题主要通过两个途径来解决:优化电路板的叠层设计及布局布线,以及增加退耦电容。退耦电容在系统频率小于300 ~ 400MHz时,可以起到抑止频率、滤波和阻抗控制的作用,在恰当的位置放置合适的退耦电容有助于减小系统电源完整性的问题。但是当系统频率更高时,退耦电容的作用很小。在这种情况下,只有通过优化电路板的层间距设计以及布局布线或者其他的降低电

随着微电子技术和计算机技术的不断发展,信号完整性分析的应用已经成为解决高速系统设计的唯一有效途径。借助功能强大的Cadence公司SpecctraQuest 仿真软件,利用IBIS模型,对高速信号线进行布局布线前信号完整性仿真分析是一种简单可行行的分析方法,可以发现信号完整性问题,根据仿真结果在信号完整性相关问题上做出优化的设计,从而缩短设计周期。 本文概要地介绍了信号完整性(SI)的相关问题,基于信号完整性分析的PCB 设计方法,传输线基本理论,详尽的阐述了影响信号完整性的两大重要因素—反射和串扰的相关理论并提出了减小反射和串扰得有效办法。讨论了基于SpecctraQucst的仿真模型的建立并对仿真结果进行了分析。研究结果表明在高速电路设计中采用基于信号完整性的仿真设计是可行的, 也是必要的。 【关键字】 高速PCB、信号完整性、传输线、反射、串扰、仿真 Abstract With the development of micro-electronics technology and computer technology,application of signal integrity analysis is the only way to solve high-speed system design. By dint of SpecctraQuest which is a powerful simulation software, it’s a simple and doable analytical method to make use of IBIS model to analyze signal integrity on high-speed signal lines before component placement and routing. This method can find out signal integrity problem and make optimization design on interrelated problem of signal integrity. Then the design period is shortened. In this paper,interrelated problem of signal integrity, PCB design based on signal integrity, transmission lines basal principle are introduced summarily.The interrelated problem of reflection and crosstalk which are the two important factors that influence signal integrity is expounded. It gives effective methods to reduce reflection and crosstalk. The establishment of emulational model based on SpecctraQucst is discussed and the result of simulation is analysed. The researchful fruit indicates it’s doable and necessary to adopt emulational design based on signal integrity in high-speed electrocircuit design.

一:前言 随着PCB系统的向着高密度和高速度的趋势不断的发展,电源的完整性问题,信号的完整性问题(SI),以及EMI,EMC的问题越来越突出,严重的影响了系统的性能甚至功能的实现。所谓高速并没有确切的定义,当然并不单单指时钟的速度,还包括数字系统上升沿及下降沿的跳变的速度,跳变的速度越快,上升和下降的时间越短,信号的高次谐波分量越丰富,当然就越容易引起SI,EMC,EMI的问题。本文根据以往的一些经验在以下几个方面对高速PCB的设计提出一些看法,希望对各位同事能有所帮助。 ●电源在系统设计中的重要性 ●不同传输线路的设计规则 ●电磁干扰的产生以及避免措施 二:电源的完整性 1.供电电压的压降问题。 随着芯片工艺的提高,芯片的内核电压及IO电压越来越小,但功耗还是很大,所以电流有上升的趋势。在内核及电压比较高,功耗不是很大的系统中,电压压降问题也许不是很突出,但如果内核电压比较小,功耗又比较大的情况下,电源路径上的哪怕是0.1V 的压降都是不允许的,比如说ADI公司的TS201内核电压只有 1.2V,内核供电电流要 2.68A,如果路径上有0.1欧姆的电阻,电 压将会有0.268V的压降,这么大的压降会使芯片工作不正常。如何尽量减小路径上的压降呢?主要通过以下几种方法。

a:尽量保证电源路径的畅通,减小路径上的阻抗,包括热焊盘的连接方式,应该尽量的保持电流的畅通,如下图1和图2的比较,很明显图2中选择的热焊盘要强于图1。 b:尽量增加大电流层的铜厚,最好能铺设两层同一网络的电源,以保证大电流能顺利的流过,避免产生过大的压降,关于电流大小和所流经铜厚的关系如表1所示。 (表1) 1 oz.铜即35微M厚, 2 oz.70微M, 类推 举例说,线宽0.025英寸,采用2 oz.盎斯的铜,而允许温升30度,

关于制作pcb心得体会 制作PCB的心得体会 学习了一学期的PCB制版,我有很多的心得体会,在整个制版过程中,可以在Altium 之下进行,也可以在DXP XX 下进行,但两者之间要关联的文件,可在打工软件后,在菜单栏DXP---属性preferences---system—file type将文件类型与该软件进行关联,以后就可双击文件而利用这个Altium Designer 打开那个文件。常用的要关联的文件有工程文件project, 原理图文件sch,当然还有PCB文件。 先新建原理图,再新建PCB图。还要建个和。用来画库里找不到的元件,用来为该元件创建封装,再将这个封装给了里新建的元件,这样就可以了。若要新建第二个元件,则TOOL-New Component,然后画矩形,放管脚。放管脚Pin 时,Display name 要在矩形框内部,风络标识Designator 要在矩形框外部。还有在里画元件封装时一定要注意,将封装画在坐标的点,否则将原理图导入PCB后,拖动元件时,会产生鼠标指针跑到别的地方去的现象。原理图上的连线,可以用线直接连,也可以用net网络标识。在建好原理图之后,要先导出所需元件的清单,里面的模板Template要空着,file format先.xls,然后点Export就可以保存了。建好原理图后,要进行编译,Project---compile schdoc.,若没弹出message窗口,则需手动去右

下角system,,打开messages对话框,查看文件中的错误,对警告warnings 要进行检查,然后再导入PCB中。Design---updata PCB Document(第一个),就可将原理图导入到PCB中。 一次性修改多个元件的某项属性,可以按shift一个一个的选,也可以选中一个后右键,find similar objects ,然后在PCB Inspector中进行统一修改即可。如果要改变放置的过孔的大小,则步骤为:Tool—属性Preference—PCB Editor—Default—选择过孔Via,再点Edit Value更改后OK即可。 PCB图是实际要制作的电路板。Q键是PCB中mm和mil 之间的转换。Ctrl+m是测量距离,P+V是放置过孔,Z+A是观看整图等常用操作。过孔是上下两层之间连接改线使用的,焊盘是用来焊接元件的。过孔大小Hole size==22mil , 直径Diameter==40mil较为好看且实用。 将所有器件布局好后。进行连线前,先要设置好线的粗细。比如12V电源线最好用30mil,信号线用12mil,需要线宽大约是到2mm等。线宽与电流是有对应关系的。 布线前,要先设置好要布的各种线的宽度,如VCC和GND 的线宽和信号NET的线宽。 —规则—Design Rout,选电气规则,将其线间距在右边窗口中设置为12mil,放入右边的窗口中,然后点应用;