PCB阻抗匹配总结

网名:chinawei97qq: 1219658831

做硬件工程师好几年,有最初的不做阻抗,到后面认为做阻抗是PCB厂家的事情,导致设计的pcb交给pcb厂家后重新修改修改布线,影响项目进度,下面把总结写在后面,以面再犯同样的错误。

做4层板,正片工艺,这样就对做半孔工艺带来加工不方便,半孔工艺会带来价格的增加,单价增加0.05元/cm2

1.6mm厚度的4层PCB板加工,建议做阻抗设计的时候按照1.5mm厚度进行设计,剩下0.1mm厚度留给工厂作为其他工艺要求用(后制诚厚度,绿油、丝印等)。

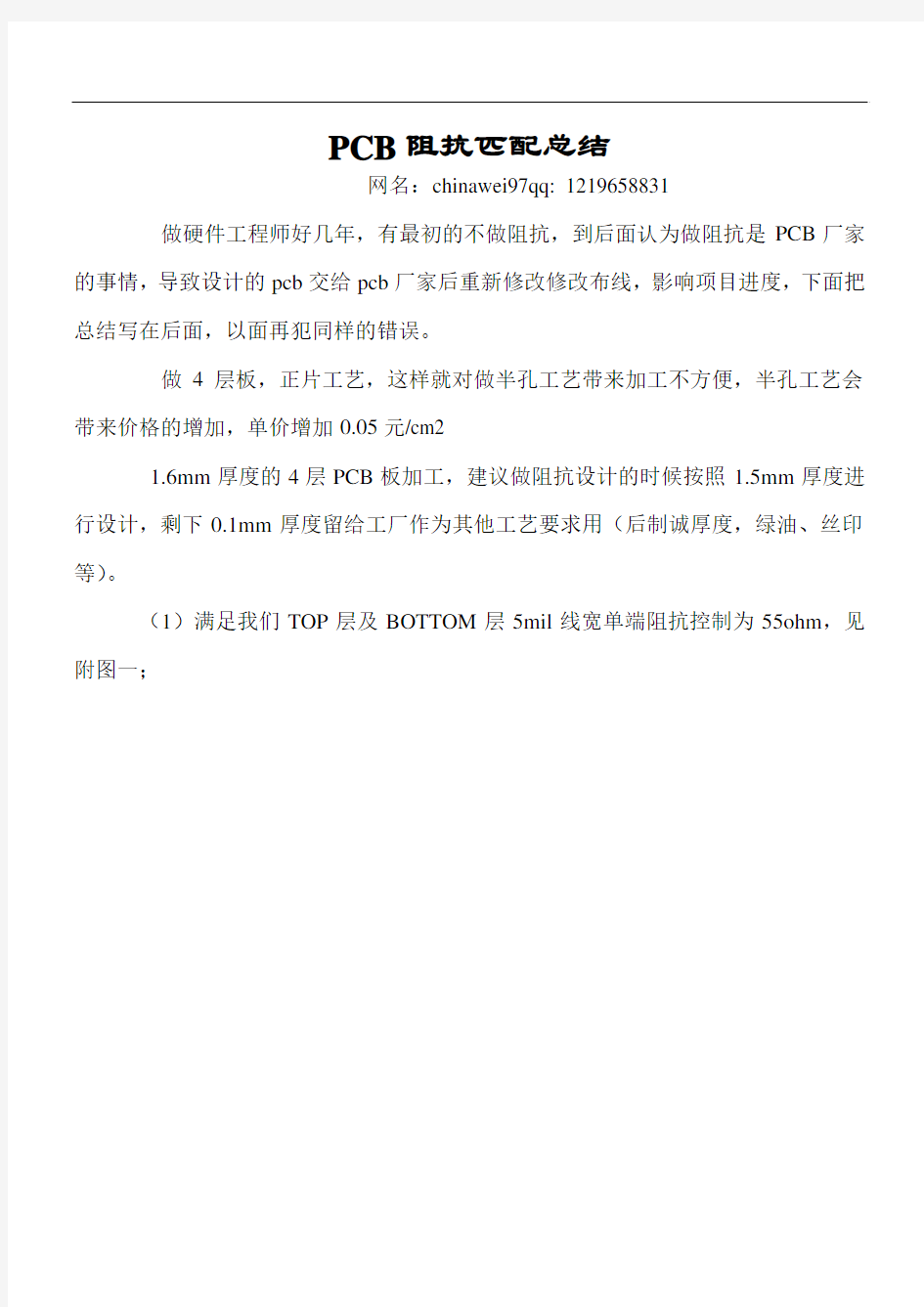

(1)满足我们TOP层及BOTTOM层5mil线宽单端阻抗控制为55ohm,见附图一;

(2)满足差分线阻抗为100ohm,见附图二

附图二

一般是通过调整层与层之间的填充(如FR-4)的厚度来满足整个板厚及阻抗控制(单端阻抗与填充厚度及导线宽度有关)的要求。

0.5OZ的铜相当于1.2mil ,1OZ的铜相当于1.9mil 。4层板来说,第一、第二层的厚度和第三、第四层的厚度相同,这样平衡对称有利用PCB板加工和使用,放置翘板。采用了外层1.7mil 内层1.4mil 的填充工艺。采用外层1OZ,内存0.5OZ 的工艺。

附图一中H1为第一层、第二层的间距为3MIL 这样第三层、第四层也为3MIL; 整板厚度为1.6mm,取1.5mm 等于 60mil 。叠层设计的厚度为:1.7+1.7+1.4+1.4+3+3+47.8,大致设计以后可以参考candece下面的计算,见附图三。具体阻抗要求

还是以工厂为准。

附图三

差分阻抗比单端阻抗还要多一个影响参数间距,和要设置Coupling Type 对线的类型,参考附图二的trace separation 中S1 参数为 6.5mil ,allegro 计算如附图四。

附图四

总结:

线径越窄、电源/地越远、隔离层的阶电常数越低,特征阻抗就越大。

(1) 在相条件下,在同一个层面,阻抗值(单端、差分)和线宽成反比;(2) 在相条件下,在同一个层面,差分阻抗值和间距成正比;

(3) 在相条件下,阻抗和板厚成反比;

(4) allergro 计算阻抗相对于Polar Si8000 这样的专业软件还是误差比

较大,由于PCB的各个厂家工艺水平的不一样,计算出来的阻抗值有一定误差。这样就要求我们设计PCB布线是要和PCB厂家的技术人员进行沟通,以免我们设计的板子制造出来不能满足我们设计的要求。

双面板阻抗差分100,板厚1.2mm,差分阻抗100欧

(5) trace宽度和电路板的叠层决定Trace特性;

(6) Trace和参考平面间的距离对阻抗和窜扰的影响:阻抗,随距离增加而增加;窜扰,随距离增加而增加

(7) Trace的阻抗依据下面的因素:

绝缘材料的介电常数:在布线层之间是否有平面层,在平面层的存在对于布线层间的窜扰起了重要作用;

绝缘材料的厚度;

Trace的宽度和厚度;

(8) Thanks

高频布线基本知识 内容目录 1. 引言 2. 信号完整性问题 3. 电磁兼容性问题 4. 电源完整性问题 5. 高频电路设计一般规范 6. 数模混合电路设计一般规范 一:高频电路的定义 *在数字电路中,是否是高频电路取决于信号的上升沿和下降沿,而不是信号的频率。 公式:F2 =1/(Tr×π),Tr为信号的上升/下降延时间。 *F2 > 100MHz,就应该按照高频电路进行考虑,下列情况必须按高频规则进行设计 –系统时钟频率超过50MHz –采用了上升/下降时间少于5ns的器件 –数字/模拟混合电路 *逻辑器件的上升/下降时间和布线长度限制上升/下主要谐波频谱分布最大传输线最大传输 降时间Tr分量F2=1/Fmax=10*距离(微带)线距离(微带线)πTr F2 74HC 13-15ns24MHz 240 MHz 117cm 91cm 74LS 9.5ns 34 MHz 340MHz 85.5cm 66.5cm 74H 4-6ns 80 MHz 800MHz 35 28 74S 3-4ns 106 MHz 1.1GHz 27 21 74HCT 5-15ns 64 MHz 640MHz 45 34 74ALS 2-10ns 160 MHz 1.6GHz 18 13 74FCT 2-5ns 160 MHz 1.6GHz 18 13 74F 1.5ns 212 MHz 2.1GHz 12.5 10.5 ECL12K 1.5ns 212 MHz 2.1GHz 12.5 10.5 ECL100K 0.75ns 424 MHz 4.2GHz 6 5 传统的PCB设计方法效率低: 原理图,传统的设计方法设计和输入布局、布线没有任何质量控制点,制作PCB每一步设计都是凭经验,发现问题就必须从头开始,功能、性能测试问题的查找非常困难 信号完整性问题: 1.反射问题 2.串扰问题 3.过冲和振荡 4.时延 反射问题:传输线上的回波。信号功率(电压和电流)的一部分传输到线上并达到负载处,但是有一部分被反射了。 多点反射

PCB的阻抗设计 1、阻抗的定义: 在某一频率下,电子器件传输信号线中,相对某一参考层,其高频信号或电磁波在传播过程中所受的阻力称之为特性阻抗,它是电阻抗,电感抗,电容抗……的一个矢量总和。 当信号在PCB导线中传输时,若导线的长度接近信号波长的1/7,此时的导线便成为信号传输线,一般信号传输线均需做阻抗控制。PCB制作时,依客户要求决定是否需管控阻抗,若客户要求某一线宽需做阻抗控制,生产时则需管控该线宽的阻抗。 当信号在PCB上传输时,PCB板的特性阻抗必须与头尾元件的电子阻抗相匹配,一但阻抗值超出公差,所传出的信号能量将出现反射、散射、衰减或延误等现象,从而导致信号不完整、信号失真。 2、计算阻抗的工具: 目前大部分人都用Polar软件:Polar Si8000、Si9000等。 常用的软件阻抗模型主要有三种: (1)特性阻抗,也叫单端阻抗;(2)差分阻抗,也叫差动阻抗;(3)共面阻抗,也叫共面波导阻抗,主要应用于双面板阻抗设计当中。

选择共面阻抗设计的原因是:双面板板厚决定了阻抗线距离,下面的参考面比较远,信号非常弱,必须选择距离较近的参考面,于是就产生了共面阻抗的设计。 3、安装软件Polar Si9000,然后打开Polar Si9000软件。熟悉一下常用的几个阻抗模型: (1)下图是外层特性阻抗模型(也叫单端阻抗模型):

(2)下图是外层差分阻抗模型: (3)内层差分阻抗模型常用以下三种:

下面是共面的常用模型: (4)下图是外层共面单端阻抗模型: (5)下图是外层共面差分阻抗模型:

4、怎样来计算阻抗? 各种PP及其组合的厚度,介电常数详见PP规格表,铜厚规则按下图的要求。

浅谈PCB的阻抗控制 随着电路设计日趋复杂和高速,如何保证各种信号(特别是高速信号)完整性,也就是保证信号质量,成为难题。此时,需要借助传输线理论进行分析,控制信号线的特征阻抗匹配成为关键,不严格的阻抗控制,将引发相当大的信号反射和信号失真,导致设计失败。常见的信号,如PCI总线、PCI-E总线、USB、以太网、DDR内存、LVDS信号等,均需要进行阻抗控制。阻抗控制最终需要通过PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,我对这个问题有了一些粗浅的认识,愿和大家分享。 多层板的结构: 为了很好地对PCB进行阻抗控制,首先要了解PCB的结构: 通常我们所说的多层板是由芯板和半固化片互相层叠压合而成的,芯板是一种硬质的、有特定厚度的、两面包铜的板材,是构成印制板的基础材料。而半固化片构成所谓的浸润层,起到粘合芯板的作用,虽然也有一定的初始厚度,但是在压制过程中其厚度会发生一些变化。 通常多层板最外面的两个介质层都是浸润层,在这两层的外面使用单独的铜箔层作为外层铜箔。外层铜箔和内层铜箔的原始厚度规格,一般有0.5OZ、1OZ、2OZ(1OZ约为35um 或1.4mil)三种,但经过一系列表面处理后,外层铜箔的最终厚度一般会增加将近1OZ左右。内层铜箔即为芯板两面的包铜,其最终厚度与原始厚度相差很小,但由于蚀刻的原因,一般会减少几个um。 多层板的最外层是阻焊层,就是我们常说的“绿油”,当然它也可以是黄色或者其它颜色。阻焊层的厚度一般不太容易准确确定,在表面无铜箔的区域比有铜箔的区域要稍厚一些,但因为缺少了铜箔的厚度,所以铜箔还是显得更突出,当我们用手指触摸印制板表面时就能感觉到。 当制作某一特定厚度的印制板时,一方面要求合理地选择各种材料的参数,另一方面,半固化片最终成型厚度也会比初始厚度小一些。下面是一个典型的6层板叠层结构: PCB的参数: 不同的印制板厂,PCB的参数会有细微的差异,通过与上海嘉捷通电路板厂技术支持的沟通,得到该厂的一些参数数据: 表层铜箔:

高频布线工艺和PCB板选材 -----需要探讨工艺和加工细节,可以联系QQ:748985601 摘要:本文通过对微带传输特性、常用板材性能参数进行比较分析,给出用于无线通信模拟前端、高速数字信号等应用中PCB板材选取方案,进一步从线宽、过孔、线间串扰、屏蔽等方面总结高频板PCB设计要点。 关键字:PCB板材、PCB设计、无线通信、高频信号 近年来在无线通信、光纤通信、高速数据网络产品不断推出,信息处理高速化、无线模拟前端模块化,这些对数字信号处理技术、IC工艺、微波PCB设计提出新的要求,另外对PCB板材和PCB工艺提出了更高要求。 如商用无线通信要求使用低成本的板材、稳定的介电常数(εr变化误差在±1-2%间)、低的介电损耗(0.005以下)。具体到手机的PCB板材,还需要有多层层压、PCB加工工艺简易、成品板可靠性高、体积小、集成度高、成本低等特点。为了挑战日益激烈的市场竞争,电子工程师必须在材料性能、成本、加工工艺难易及成品板的可靠性间采取折衷。 目前可供选用的板材很多,有代表性的常用板材有:环氧树脂玻璃布层压板FR4、多脂氟乙烯PTFE、聚四氟乙烯玻璃布F4、改性环氧树脂FR4等。特殊板材如:卫星微波收发电路用到蓝宝石基材和陶瓷基材;微波电路基材GX系列、RO3000系列、RO4000系列、TL系列、TP-1/2系列、F4B-1/2系列。它们使用的场合不同,如FR4用于1GHz以下混合信号电路、多脂氟乙烯PTFE多用于多层高频电路板、聚四氟乙烯玻璃布纤维F4用于微波电路双面板、改性环氧树脂FR4用于家用电器高频头(500MHz以下)。由于FR4板材易加工、成本低、便于层压,所以得到广泛应用。 下面我们从微带传输线特性、多层板层压工艺、板材参数性能比较等多个方面分析,给出了对于特殊应用的PCB板材选取方案,总结了高频信号PCB设计要点,供广大电子工程师参考。 1微带传输线传输特性 板材的性能指标包括有介电常数εr、损耗因子(介质损耗角正切)tgδ、表面光洁度、表面导体导电率、抗剥强度、热涨系数、抗弯强度等。其中介电常数εr、损耗因子是主要参数。 高速数据信号或高频信号传输常用到微带线(Microstrip Line),由附着在介质基片两边的导带和导体Array接地板构成,且导带一部分 暴露在空气中,信号在介质 基片和空气这两种介质中 传播引起传输相速不等会 产生辐射分量、如果合理选 用微带尺寸这种分量很小。 图一基片结构示意

阻抗匹配概念 阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态。对于不同特性的电路,匹配条件是不一样的。 在纯电阻电路中,当负载电阻等于激励源内阻时,则输出功率为最大,这种工作状态称为匹配,否则称为失配。 当激励源内阻抗和负载阻抗含有电抗成份时,为使负载得到最大功率,负载阻抗与内阻必须满足共扼关系,即电阻成份相等,电抗成份只数值相等而符号相反。这种匹配条件称为共扼匹配。 阻抗匹配(Impedance matching)是微波电子学里的一部分,主要用于传输线上,来达至所有高频的微波信号皆能传至负载点的目的,不会有信号反射回来源点,从而提升能源效益。 大体上,阻抗匹配有两种,一种是透过改变阻抗力(lumped-circuit matching),另一种则是调整传输线的波长(transmission line matching)。 要匹配一组线路,首先把负载点的阻抗值,除以传输线的特性阻抗值来归一化,然后把数值划在史密夫图表上。 改变阻抗力 把电容或电感与负载串联起来,即可增加或减少负载的阻抗值,在图表上的点会沿著代表实数电阻的圆圈走动。如果把电容或电感接地,首先图表上的点会以图中心旋转180度,然后才沿电阻圈走动,再沿中心旋转180度。重覆以上方法直至电阻值变成1,即可直接把阻抗力变为零完成匹配。 调整传输线

由负载点至来源点加长传输线,在图表上的圆点会沿著图中心以逆时针方向走动,直至走到电阻值为1的圆圈上,即可加电容或电感把阻抗力调整为零,完成匹配 阻抗匹配则传输功率大,对于一个电源来讲,单它的内阻等于负载时,输出功率最大,此时阻抗匹配。最大功率传输定理,如果是高频的话,就是无反射波。对于普通的宽频放大器,输出阻抗50Ω,功率传输电路中需要考虑阻抗匹配,可是如果信号波长远远大于电缆长度,即缆长可以忽略的话,就无须考虑阻抗匹配了。阻抗匹配是指在能量传输时,要求负载阻抗要和传输线的特征阻抗相等,此时的传输不会产生反射,这表明所有能量都被负载吸收了.反之则在传输中有能量损失。高速PCB布线时,为了防止信号的反射,要求是线路的阻抗为50欧姆。这是个大约的数字,一般规定同轴电缆基带50欧姆,频带75欧姆,对绞线则为100欧姆,只是取个整而已,为了匹配方便. 阻抗从字面上看就与电阻不一样,其中只有一个阻字是相同的,而另一个抗字呢?简单地说,阻抗就是电阻加电抗,所以才叫阻抗;周延一点地说,阻抗就是电阻、电容抗及电感抗在向量上的和。在直流电的世界中,物体对电流阻碍的作用叫做电阻,世界上所有的物质都有电阻,只是电阻值的大小差异而已。电阻小的物质称作良导体,电阻很大的物质称作非导体,而最近在高科技领域中称的超导体,则是一种电阻值几近于零的东西。但是在交流电的领域中则除了电阻会阻碍电流以外,电容及电感也会阻碍电流的流动,这种作用就称之为电抗,意即抵抗电流的作用。电容及电感的电抗分别称作电容抗及电感抗,简称容抗及感抗。它们的计量单位与电阻一样是奥姆,而其值的大小则和交流电的频率有关系,频率愈高则容抗愈小感抗愈大,频率愈低则容抗愈大而感抗愈小。此外电容抗和电

PCB板基础知识、布局原则、布线技巧、设计规则 PCB 板基础知识 一、PCB 板的元素 1、工作层面对于印制电路板来说,工作层面可以分为 6 大类,信号层(signal layer))内部电源/接地层内部电源接地层(internal plane layer))机械层(主要用来放置物理边界和放置尺寸标注等信息,起到相应机械层(mechanical layer))的提示作用。EDA 软件可以提供 16 层的机械层。防护层(包括锡膏层和阻焊层两大类。锡膏层主要用于将表面贴防护层(mask layer))元器件粘贴在 PCB 上,阻焊层用于防止焊锡镀在不应该焊接的地方。印层(在 PCB 板的 TOP 和 BOTTOM 层表面绘制元器件的外观丝印层(silkscreen layer))轮廓和放置字符串等。例如元器件的标识、标称值等以及放置厂家标志,生产日期等。同时也是印制电路板上用来焊接元器件位置的依据,作用是使 PCB 板具有可读性,便于电路的安装和维修。其他工作层(禁止布线层 Keep Out Layer 其他工作层(other layer))钻孔导引层 drill guide layer 钻孔图层 drill drawing layer 复合层multi-layer 2、元器件封装是实际元器件焊接到 PCB 板时的焊接位置与焊接形状,包括了实际元器件的外形尺寸,所占空间位置,各管脚之间的间距等。元器件封装是一个空间的功能,对于不同的元器件可以有相同的封装,同样相同功能的元器件可以有不同的封装。因此在制作 PCB 板时必须同时知道元器件的名称和封装形式。(1)元器件封装分类通孔式元器件封装(THT,through hole technology)表面贴元件封装(SMT Surface mounted technology )另一种常用的分类方法是从封装外形分类: SIP 单列直插封装 DIP 双列直插封装 PLCC 塑料引线芯片载体封装 PQFP 塑料四方扁平封装 SOP 小尺寸封装 TSOP 薄型小尺寸封装 PPGA 塑料针状栅格阵列封装 PBGA 塑料球栅阵列封装 CSP 芯片级封装 (2) 元器件封装编号编号原则:元器件类型+引脚距离(或引脚数)+元器件外形尺寸 例如 AXIAL-0.3 DIP14 (3)常见元器件封装 RAD0.1 RB7.6-15 等。 电阻类普通电阻 AXIAL- ×× ,其中××表示元件引脚间的距离;可变电阻类元件封装的编号为 VR × , 其中×表示元件的类别。电容类非极性电容编号 RAD ×× ,其中××表示元件引脚间的距离。极性电容编号 RB xx - yy ,xx 表示元件引脚间的距离,yy 表示元件的直径。二极管类编号 DIODE- ×× ,其中××表示元件引脚间的距离。晶体管类器件封装的形式多种多样。集成电路类 SIP 单列直插封装 DIP 双列直插封装 PLCC 塑料引线芯片载体封装 PQFP 塑料四方扁平封装 SOP 小尺寸封装 TSOP 薄型小尺寸封装 PPGA 塑料针状栅格阵列封装 PBGA 塑料球栅阵列封装 CSP 芯片级封装 3、铜膜导线是指 PCB 上各个元器件上起电气导通作用的连线,它是 PCB 设计中最重要的部分。对于印制电路板的铜膜导线来说,导线宽度和导线间距是衡量铜膜导线的重要指标,这两个方面的尺寸是否合理将直接影响元器件之间能否实现电路的正确连接关系。印制电路板走线的原则:◆走线长度:尽量走短线,特别对小信号电路来讲,线越短电阻越小,干扰越小。◆走线形状:同一层上的信号线改变方向时应该走 135°的斜线或弧形,避免 90°的拐角。◆走线宽度和走线间距:在 PCB 设计中,网络性质相同的印制板线条的宽度要求尽量一致,这样有利于阻抗匹配。走线宽度通常信号线宽为: 0.2~

PCB阻抗设计及计算简介

特性阻抗的定义 ?何谓特性阻抗(Characteristic Impedance ,Z0) ?电子设备传输信号线中,其高频信号在传输线中传播时所遇到的阻力称之为特性阻抗;包括阻抗、容抗、感抗等,已不再只是简单直流电的“欧姆电阻”。 ?阻抗在显示电子电路,元件和元件材料的特色上是最重要的参数.阻抗(Z)一般定义为:一装置或电路在提供某特定频率的交流电(AC)时所遭遇的总阻力. ?简单的说,在具有电阻、电感和电容的电路里,对交流电所起的阻碍作用叫做阻抗。

设计阻抗的目的 ?随着信号传送速度迅猛的提高和高频电路的广泛应用,对印刷电路板也提出了更高的要求。印刷电路板提供的电路性能必须能够使信号在传输过程中不发生反射现象,信号保持完整,降低传输损耗,起到匹配阻抗的作用,这样才能得到完整、可靠、精确、无干扰、噪音的传输信号。?阻抗匹配在高频设计中是很重要的,阻抗匹配与否关系到信号的质量优劣。而阻抗匹配的目的主要在于传输线上所有高频的微波信号皆能到达负载点,不会有信号反射回源点。

?因此,在有高频信号传输的PCB板中,特性阻抗的控制是尤为重要的。 ?当选定板材类型和完成高频线路或高速数字线路的PCB 设计之后,则特性阻抗值已确定,但是真正要做到预计的特性阻抗或实际控制在预计的特性阻抗值的围,只有通过PCB生产加工过程的管理与控制才能达到。

?从PCB制造的角度来讲,影响阻抗和关键因素主要有: –线宽(w) –线距(s)、 –线厚(t)、 –介质厚度(h) –介质常数(Dk) εr相对电容率(原俗称Dk介质常数),白容生对此有研究和专门诠释。 注:其实阻焊也对阻抗有影响,只是由于阻焊层贴在介质上,导致介电常数增大,将此归于介电常数的影响,阻抗值会相 应减少4%

1、高频信号布线时要注意哪些问题? 答:信号线的阻抗匹配;与其他信号线的空间隔离;对于数字高频信号,差分线效果会更好; 2、在布板时,如果线密,过孔就可能要多,当然就会影响板子的电气性能,请问怎样提高板子的电气性能? 答:对于低频信号,过孔不要紧,高频信号尽量减少过孔。如果线多可以考虑多层板; 3、是不是板子上加的去耦电容越多越好? 答:去耦电容需要在合适的位置加合适的值。例如,在你的模拟器件的供电端口就进加,并且需要用不同的电容值去滤除不同频率的杂散信号; 4、一个好的板子它的标准是什么? 答:布局合理、功率线功率冗余度足够、高频阻抗阻抗、低频走线简洁. 5、通孔和盲孔对信号的差异影响有多大?应用的原则是什么? 答:采用盲孔或埋孔是提高多层板密度、减少层数和板面尺寸的有效方法,并大大减少了镀覆通孔的数量。但相比较而言,通孔在工艺上好实现,成本较低,所以一般设计中都使用通孔。 6、在涉及模拟数字混合系统的时候,有人建议电层分割,地平面采取整片敷铜,也有人建议电地层都分割,不同的地在电源源端点接,但是这样对信号的回流路径就远了,具体应用时应如何选择合适的方法? 答:如果你有高频>20MHz信号线,并且长度和数量都比较多,那么需要至少两层给这个模拟高频信号。一层信号线、一层大面积地,并且信号线层需要打足够的过孔到地。这样的目的是:1)对于模拟信号,这提供了一个完整的传输介质和阻抗匹配;2)地平面把模拟信号和其他数字信号进行隔离;3)地回路足够小,因为你打了很多过孔,地有是一个大平面。 7、在电路板中,信号输入插件在PCB最左边沿,MCU在靠右边,那么在布局时是把稳压电源芯片放置在靠近接插件(电源IC输出5V经过一段比较长的路径才到达MCU),还是把电源IC放置到中间偏右(电源IC的输出5V的线到达MCU就比较短,但输入电源线就经过比较长一段PCB板)?或是有更好的布局? 答:首先你的所谓信号输入插件是否是模拟器件?如果是是模拟器件,建议你的电源布局应尽量不影响到模拟部分的信号完整性.因此有几点需要考虑:1)首先你的稳压电源芯片是否是比较干净,纹波小的电源.对模拟部分的供电,对电源的要求比较高;2)模拟部分和你的MCU是否是一个电源,在高精度电路的设计中,建议把模拟部分和数字部分的电源分开;3)对数字部分的供电需要考虑到尽量减小对模拟电路部分的影响. 8、在高速信号链的应用中,对于多ASIC都存在模拟地和数字地,究竟是采用地分割,还是不分割地?既有准则是什么?哪种效果更好? 答:迄今为止,没有定论。一般情况下你可以查阅芯片的手册。ADI所有混合芯片的手册中都是推荐你一种接地的方案,有些是推荐公地、有些是建议隔离地。这取决于芯片设计。 9、何时要考虑线的等长?如果要考虑使用等长线的话,两根信号线之间的长度之差最大不能超过多少?如何计算? 答:差分线计算思路:如果你传一个正弦信号,你的长度差等于它传输波长的一半是,相位差就是180度,这时两个信号就完全抵消了。所以这时的长度差是最大值。以此类推,信号线差值一定要小于这个值。 10、高速中的蛇形走线,适合在那种情况?有什么缺点没,比如对于差分走线,又要求两组信号是正交的。 答蛇形走线,因为应用场合不同而具不同的作用: 1)如果蛇形走线在计算机板中出现,其主要起到一个滤波电感和阻抗匹配的作用,提高电路的抗干扰能力。计算机主机板中的蛇形走线,主要用在一些时钟信号中,如PCI-Clk,AGPCIK,IDE,DIMM等信号线;2)若在一般普通PCB板中,除了具有滤波电感的作用外,还可作为收音机天线的电感线圈等等。如2.4G的对讲机中就用作电感;3)对一些信号布线长度要求必须严格等长,高速数字PCB板的等线长是为了使各信号的延迟差保持在一个范围内,保证系统在同一周期内读取的数据的有效性(延迟差超过一个时钟周期时会错读下一周期的数据)。如INTELHUB架构中的HUBLink,一共13根,使用233MHz的频率,要求必须严格等长,以消除时滞造成的隐患,绕线是惟一的解决办法。一般要求延迟差不超过1/4时钟周期,单位长度的线延迟差也是固定的,延迟跟线宽、线长、铜厚、板层结构有关,但线过长会增大分布电容和分布电感,使信号质量有所下降。所以时钟IC引脚一般都接;" 端接,但蛇形走线并非起电感的作用。相反地,电感会使信号中的上升沿中的高次谐波相移,造成信号质量恶化,所以要求蛇形线间距最少是线宽的两倍。信号的上升时间越小,就越易受分布电容和分布电感的影响。4)蛇形走线在某些特殊的电路中起到一个分布参数的LC滤波器的作用。 11、在设计PCB时,如何考虑电磁兼容性EMC/EMI,具体需要考虑哪些方面?采取哪些措施?

阻抗计算说明 Rev0.0 heroedit@https://www.doczj.com/doc/477448729.html, z给初学者的 一直有很多人问我阻抗怎么计算的. 人家问多了,我想给大家整理个材料,于己于人都是个方便.如果大家还有什么问题或者文档有什么错误,欢迎讨论与指教! 在计算阻抗之前,我想很有必要理解这儿阻抗的意义 z传输线阻抗的由来以及意义 传输线阻抗是从电报方程推导出来(具体可以查询微波理论) 如下图,其为平行双导线的分布参数等效电路: 从此图可以推导出电报方程 取传输线上的电压电流的正弦形式 得 推出通解

定义出特性阻抗 无耗线下r=0, g=0得 注意,此特性阻抗和波阻抗的概念上的差异(具体查看平面波的波阻抗定义) ε μ=EH Z 特性阻抗与波阻抗之间关系可从 此关系式推出. Ok,理解特性阻抗理论上是怎么回事情,看看实际上的意义,当电压电流在传输线传播的时候,如果特性阻抗不一致所求出的电报方程的解不一致,就造成所谓的反射现象等等.在信号完整性领域里,比如反射,串扰,电源平面切割等问题都可以归类为阻抗不连续问题,因此匹配的重要性在此展现出来. z 叠层(stackup)的定义 我们来看如下一种stackup,主板常用的8层板(4层power/ground 以及4层走线层,sggssggs,分别定义为L1, L2…L8)因此要计算的阻抗为 L1,L4,L5,L8 下面熟悉下在叠层里面的一些基本概念,和厂家打交道经常会使用的 Oz 的概念 Oz 本来是重量的单位Oz(盎司 )=28.3 g(克) 在叠层里面是这么定义的,在一平方英尺的面积上铺一盎司的铜的厚度为1Oz, 对

我来大概概括一下ADC输入阻抗的问题: 1:SAR型ADC这种ADC内阻都很大,一般500K以上。即使阻抗小的ADC,阻抗也是固定的。所以即使只要被测源内阻稳定,只是相当于电阻分压,可以被校正。 2:开关电容型,如TLC2543之类。他要求很低的输入阻抗用于对内部采样电容快速充电。这时最好有低阻源,否则会引起误差。实在不行,可以外部并联一很大的电容,每次被取样后,大电容的电压下降不多。因此并联外部大电容后,开关电容输入可以等效为一个纯阻性阻抗,可以被校正。 3:FLASH.html">FLASH型(直接比较型)。大多高速ADC都是直接比较型,也称闪速型(FLASH),一般都是低阻抗的。要求低阻源。对外表现纯阻性,可以和运放直接连接 4:双积分型大多输入阻抗极高,几乎不用考虑阻抗问题 5:Sigma-Delta型。这是目前精度最高的ADC类型,也是最难伺候的一种ADC。重点讲一下要注意的问题: a.内部缓冲器的使用。SigmaDelta型ADC属于开关电容型输入,必须有低阻源。所以为了简化外部设计,内部大多集成有缓冲器。缓冲器打开,则对外呈现高阻,使用方便。但要注意了,缓冲器实际是个运放。那么必然有上下轨的限制。大多数缓冲器都是下轨50mV,上轨AVCC-1.5V。在这种应用中,共莫输入范围大大的缩小,而且不能到测0V。一定要特别小心!一般用在电桥测量中,因为共模范围都在1/2VCC附近。不必过分担心缓冲器的零票,通过内部校零寄存器

很容易校正的。 b.输入阻抗问题。SigmaDelta型ADC属于开关电容型输入,在低阻源上工作良好。但有时候为了抑制共模或抑制乃奎斯特频率外的信号,需要在输入端加RC滤波器,一般DATASHEET上会给一张最大允许输入阻抗和C和Gain的关系表。这时很奇怪的一个特性是,C越大,则最大输入阻抗必须随之减小!刚开始可能很多人不解,其实只要想一下电容充电特性久很容易明白的。还有一个折衷的办法是,把C取很大,远大于几百万倍的采样电容Cs(一般4~20PF),则输入等效纯电阻,分压误差可以用GainOffset寄存器校正。 c.运放千万不能和SigmaDelta型ADC直连!前面说过,开关电容输入电路电路周期用采样电容从输入端采样,每次和运放并联的时候,会呈现低阻,和运放输出阻抗分压,造成电压下降,负反馈立刻开始校正,但运放压摆率(SlewRate)有限,不能立刻响应。于是造成瞬间电压跌落,取样接近完毕时,相当于高阻,运放输出电压上升,但压摆率使运放来不及校正,结果是过冲。而这时正是最关键的采样结束时刻。 所以,运放和SD型ADC连接,必须通过一个电阻和电容连接(接成低通)。而RC的关系又必须服从5.c里面所述规则。 d.差分输入和双极性的问题。SD型ADC都可以差分输入,都支持双极性输入。但这里的双极性并不是指可以测负压,而是Vi+Vi-两脚之间的电压。假设Vi-接AGND,那么负压测量范围不会超过-0.3V。正确的接法是Vi+Vi-共模都在-0.3~VCC之间差分输入。一个典型的

阻抗线计算 一.传输线类型 1 最通用的传输线类型为微带线(microstrip)和带状线(stripline) 微带线(microstrip):指在PCB外层的线和只有一个参考平面的线,有非嵌入/嵌入两种如图所示:(图1) 非嵌入(我们目前常用) (图2) 嵌入(我们目前几乎没有用过) 带状线:在绝缘层的中间,有两个参考平面。如下图: (图3) 2 阻抗线 2.1差动阻抗(图4)

差动阻抗,如上所示,阻抗值一般为90,100,110,120 2.2特性阻抗(图5) 特性阻抗: 如上如所示,.阻抗值一般为50 ohm,60ohm 二.PCB叠层结构 1板层、PCB材质选择 PCB是一种层叠结构。主要是由铜箔与绝缘材料叠压而成。附图为我们常用的1+6+1结构的,8层PCB叠层结构。(图6) 首先第一层为阻焊层(俗称绿油)。它的主要作用是在PCB表面形成一层保护膜,防止导体上不该上锡的区域沾锡。同时还能起到防止导体之间因潮气、化学品等引起的短路、生产

和装配中不良操作造成的断路、防止线路与其他金属部件短路、绝缘及抵抗各种恶劣环境,保证PCB工作稳定可靠。 防焊的种类有传统环氧树脂IR烘烤型,UV硬化型, 液态感光型(LPISM-Liquid Photo Imagable Solder Mask)等型油墨, 以及干膜防焊型(Dry Film, Solder Mask),其中液态感光型为目前制程大宗,常用的有Normal LPI, Lead-free LPI,Prob 77. 防焊对阻抗的影响是使得阻抗变小2~3ohm左右 阻焊层下面为第一层铜箔。它主要起到电路连通及焊接器件的作用。硬板中使用的铜箔一般以电解铜为主(FPC中主要使用压延铜)。常用厚度为0.5OZ及1OZ.(OZ为重量单位在PCB行业中做为一种铜箔厚度的计量方式。1OZ表示将重量为1OZ的铜碾压成1平方英尺后铜箔的厚度。1OZ=0.035mm). 铜箔下面为绝缘层..我们常用的为FR4半固化片.半固化片是以无碱玻璃布为增强材料,浸以环氧树脂.通过120-170℃的温度下,将半固化片树脂中的溶剂及低分子挥发物烘除.同时,树脂也进行一定程度的反应,呈半固化状态(B阶段).在PCB制作过程中通过层压机的高温压合.半固化中的树脂完全反应,冷却后完全固化形成我们所需的绝缘层. 半固化片中所用树脂主要为热塑性树脂, 树脂有三种阶段: A阶段:在室温下能够完全流动的液态树脂,这是玻钎布浸胶时状态 B阶段:环氧树脂部分交联处于半固化状态,在加热条件下,又能恢复到液体状态 C阶段:树脂全部交联为C阶段,在加热加压下会软化,但不能再成为液态,这是多层板压制后半固化片转成的最终状态. 由于半固化片在板层压合过程中,厚度会变小,因而半固化片的原始材料厚度和压合后的厚度不一样,因而必须分清厚度是原始材料厚度还是完成厚度。另外,半固化片的厚度不是固定不变的,根据板厚、板层和板厂不同,而有所不同。上述只是一例。 同时该叠层中用了两块芯板,即core(FR-4).芯板是厂家已压合好的带有双面铜的基材,在压合过程中厚度是不变的。常见芯板见下:(表二)

1、[问]高频信号布线时要注意哪些问题? [答] 1.信号线的阻抗匹配; 2.与其他信号线的空间隔离; 3.对于数字高频信号,差分线效果会更好; 2、[问] 在布板时,如果线密,过孔就可能要多,当然就会影响板子的电气性能,请问怎样提高板子的电气性能? [答] 对于低频信号,过孔不要紧,高频信号尽量减少过孔。如果线多可以考虑多层板; 3、[问]是不是板子上加的去耦电容越多越好? [答] 去耦电容需要在合适的位置加合适的值。例如,在你的模拟器件的供电端口就进加,并且需要用不同的电容值去滤除不同频率的杂散信号; 4、[问]一个好的板子它的标准是什么? [答] 布局合理、功率线功率冗余度足够、高频阻抗阻抗、低频走线简洁. 5、[问]通孔和盲孔对信号的差异影响有多大?应用的原则是什么? [答] 采用盲孔或埋孔是提高多层板密度、减少层数和板面尺寸的有效方法,并大大减少了镀覆通孔的数量。但相比较而言,通孔在工艺上好实现,成本较低,所以一般设计中都使用通孔。 6、[问]在涉及模拟数字混合系统的时候,有人建议电层分割,地平面采取整片敷铜,也有人建议电地层都分割,不同的地在电源源端点接,但是这样对信号的回流路径就远了,具体应用时应如何选择合适的方法? [答] 如果你有高频>20MHz信号线,并且长度和数量都比较多,那么需要至少两层给这个模拟高频信号。一层信号线、一层大面积地,并且信号线层需要打足够的过孔到地。这样的目的是: 1、对于模拟信号,这提供了一个完整的传输介质和阻抗匹配; 2、地平面把模拟信号和其他数字信号进行隔离; 3、地回路足够小,因为你打了很多过孔,地有是一个大平面。 7、[问]在电路板中,信号输入插件在 PCB最左边沿,MCU在靠右边,那么在布局时是把稳压电源芯片放置在靠近接插件(电源IC输出5V经过一段比较长的路径才到达 MCU),还是把电源 IC放置到中间偏右(电源 IC的输出 5V的线到达MCU就比较短,但输入电源 线就经过比较长一段 PCB板)?或是有更好的布局? [答] 首先你的所谓信号输入插件是否是模拟器件?如果是是模拟器件,建议你的电源布局应尽量不影响到模拟部分的信号完整性.因此有几点需要考虑(1)首先你的稳压电源芯片是否是比较干净,纹波小的电源.对模拟部分的供电,对电源的要求比较高. (2)模拟部分和你的MCU是否是一个电源,在高精度电路的设计中,建议把模拟部分和数字部分的电源分开. (3)对数字部分的供电需要考虑到尽量减小对模拟电路部分的影响.

PCB线路板阻抗计算公式 现在关于PCB线路板的阻抗计算方式有很多种,相关的软件也能够直接帮您计算阻抗值,今天通过polar si9000来和大家说明下阻抗是怎么计算的。 在阻抗计算说明之前让我们先了解一下阻抗的由来和意义: 传输线阻抗是从电报方程推导出来(具体可以查询微波理论) 如下图,其为平行双导线的分布参数等效电路: 从此图可以推导出电报方程 取传输线上的电压电流的正弦形式 得

推出通解 定义出特性阻抗 无耗线下r=0, g=0 得 注意,此特性阻抗和波阻抗的概念上的差异(具体查看平面波的波阻抗定义) 特性阻抗与波阻抗之间关系可从此关系式推出. Ok,理解特性阻抗理论上是怎么回事情,看看实际上的意义,当电压电流在传输线传播的时候,如果特性阻抗不一致所求出的电报方程的解不一致,就造成所谓的反射现象等等.在信号完整性领域里,比如反射,串扰,电源平面切割等问题都可以归类为阻抗不连续问题,因此匹配的重要性在此展现出来. 叠层(stackup)的定义

我们来看如下一种stackup,主板常用的8 层板(4 层power/ground 以及4 层走线层,sggssggs,分别定义为L1, L2…L8)因此要计算的阻抗为L1,L4,L5,L8 下面熟悉下在叠层里面的一些基本概念,和厂家打交道经常会使用的 Oz 的概念 Oz 本来是重量的单位Oz(盎司)=28.3 g(克) 在叠层里面是这么定义的,在一平方英尺的面积上铺一盎司的铜的厚度为1Oz,对应的单位如下 介电常数(DK)的概念 电容器极板间有电介质存在时的电容量Cx 与同样形状和尺寸的真空电容量Co之比为介电常数:ε = Cx/Co = ε'-ε" Prepreg/Core 的概念 pp 是种介质材料,由玻璃纤维和环氧树脂组成,core 其实也是pp 类型介质,只不过他两面都覆有铜箔,而pp 没有.

高頻佈線工藝和PCB板選材 國家數位交換系統工程技術研究中心 張建慧饒龍記[鄭州1001信箱787號] 摘要:本文通過對微帶傳輸特性、常用板材性能參數進行比較分析,給出用於無線通信類比前端、高速數位信號等應用中PCB板材選取方案,進一步從線寬、過孔、線間串擾、遮罩等方面總結高頻板PCB設計要點。 關鍵字:PCB板材、PCB設計、無線通信、高頻信號 近年來在無線通信、光纖通信、高速資料網路產品不斷推出,資訊處理高速化、無線模擬前端模組化,這些對數位信號處理技術、IC工藝、微波PCB設計提出新的要求,另外對PCB板材和PCB工藝提出了更高要求。 變化誤差在如商用無線通信要求使用低成本的板材、穩定的介電常數(ε r ±1-2%間)、低的介電損耗(0.005以下)。具體到手機的PCB板材,還需要有多層層壓、PCB加工工藝簡易、成品板可靠性高、體積小、集成度高、成本低等特點。為了挑戰日益激烈的市場競爭,電子工程師必須在材料性能、成本、加工工藝難易及成品板的可靠性間採取折衷。 目前可供選用的板材很多,有代表性的常用板材有:環氧樹脂玻璃布層壓板FR4、多脂氟乙烯PTFE、聚四氟乙烯玻璃布F4、改性環氧樹脂FR4等。特殊板材如:衛星微波收發電路用到藍寶石基材和陶瓷基材;微波電路基材GX系列、 B-1/2系列。它們使用的RO3000系列、RO4000系列、TL系列、TP-1/2系列、F 4 場合不同,如FR4用於1GHz以下混合信號電路、多脂氟乙烯PTFE多用於多層高頻電路板、聚四氟乙烯玻璃布纖維F4用於微波電路雙面板、改性環氧樹脂FR4用於家用電器高頻頭(500MHz以下)。由於FR4板材易加工、成本低、便於層壓,所以得到廣泛應用。 下面我們從微帶傳輸線特性、多層板層壓工藝、板材參數性能比較等多個方面分析,給出了對於特殊應用的PCB板材選取方案,總結了高頻信號PCB設計要點,供廣大電子工程師參考。 1微帶傳輸線傳輸特性 板材的性能指標包括有介電常數ε 、損耗因數(介質損耗角正切)tgδ、表 r 面光潔度、表面導體導電率、抗剝強度、熱漲係數、抗彎強度等。其中介電常數、損耗因數是主要參數。 ε r 高速資料信號或高頻信號傳輸常用到微帶線(Microstrip Line),由附著在介質基片兩邊的導帶和導 體接地板構成,且導帶一部 分暴露在空氣中,信號在介 質基片和空氣這兩種介質 中傳播引起傳輸相速不等Array會產生輻射分量、如果合理 選用微帶尺寸這種分量很 小。

谈谈嵌入式系统PCB设计中的阻抗匹配与0欧电阻 1、阻抗匹配 阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式。根据接入方式阻抗匹配有串行和并行两种方式;根据信号源频率阻抗匹配可分为低频和高频两种。 (1)高频信号一般使用串行阻抗匹配。串行电阻的阻值为20~75Ω,阻值大小与信号频率成正比,与 PCB走线宽度和长度成反比。在嵌入式系统中,一般频率大于20M的信号PCB走线长度大于5cm时都要加串行匹配电阻,例如系统中的时钟信号、数据和地址总线信号等。串行匹配电阻的作用有两个: ◆减少高频噪声以及边沿过冲。如果一个信号的边沿非常陡峭,则含有大量的高频成分,将会辐射干扰,另外,也容易产生过冲。串联电阻与信号线的分布电容以及负载输入电容等形成一个RC电路,这样就会降低信号边沿的陡峭程度。 ◆减少高频反射以及自激振荡。当信号的频率很高时,则信号的波长就很短,当波长短得跟传输线长度可以比拟时,反射信号叠加在原信号上将会改变原信号的形状。如果传输线的特征阻抗跟负载阻抗不相等(即不匹配)时,在负载端就会产生反射,造成自激振荡。PCB板内走线的低频信号直接连通即可,一般不需要加串行匹配电阻。 (2)并行阻抗匹配又叫“终端阻抗匹配”,一般用在输入/输出接口端,主要指与传输电缆的阻抗匹配。例如,LVDS与RS422/485 使用5类双绞线的输入端匹配电阻为100~120Ω;视频信号使用同轴电缆的匹配电阻为75Ω或50Ω、使用篇平电缆为300Ω。并行匹配电阻的阻值与传输电缆的介质有关,与长度无关,其主要作用也是防止信号反射、减少自激振荡。值得一提的是,阻抗匹配可以提高系统的EMI性能。此外,解决阻抗匹配除了使用串/并联电阻外,还可使用变压器来做阻抗变换,典型的例子如以太网接口、CAN总线等。 2、0欧电阻的作用 (1)最简单的是做跳线用,如果某段线路不用,直接不焊接该电阻即可(不影响外观)。 (2)在匹配电路参数不确定的时候,以0欧姆代替,实际调试的时候,确定参数,再以具体数值的元件

阻抗计算: 1.介电常数E r E r(介电常数)就目前而言通常情况下选用的材料为 F R-4,该种材料的E r 特性为随着加载频率的不同而变化,一般情况下E r的分水岭默认为1 G H Z(高频)。目前材料厂商能够承诺的指标<5.4(1M H z),根据我们实际加工的经验,在使用频率为1G H Z以下的其E r认为4.2左右。1.5—2.0G H Z的使用频率其仍有下降的空间。故设计时如有阻抗的要求则须考虑该产品的当时的使用频率。 我们在长期的加工和研发的过程中针对不同的厂商已经摸索出一定的规律和计算公式。 ●7628----4.5(全部为1G H z状态下) ●2116----4.2 ●1080----3.6 2. 介质层厚度H H(介质层厚度)该因素对阻抗控制的影响最大故设计中如对阻抗的宽容度很小的话,则该部分的设计应力求准确,FR-4的H的组成是由各种半固化片组合而成的(包括内层芯板),一般情况下常用的半固化片为: ●1080 厚度0.075MM、 ●7628 厚度0.175MM、 ●2116厚度 0.105MM。 3.线宽W 对于W1、W2的说明:

5.铜箔厚度 外层铜箔和内层铜箔的原始厚度规格,一般有0.5OZ、1OZ、2OZ(1OZ约为35um或1.4mil)三种,但经过一系列表面处理后,外层铜箔的最终厚度一般会增加将近1 OZ左右。内层铜箔即为芯板两面的包铜,其最终厚度与原始厚度相差很小,但由于蚀刻的原因,一般会减少几个um。

表层铜箔: 可以使用的表层铜箔材料厚度有三种:12um、18um和35um。加工完成后的最终厚度大约是44um、50um和67um,大致相当于铜厚1 OZ、1.5 OZ、2 OZ。注意:在用阻抗计算软件进行阻抗控制时,外层的铜厚没有0.5 OZ的值。 走线厚度T与该层的铜厚有对应关系,具体如下: 铜箔厚度单位转换: Oz 本来是重量的单位Oz(盎司ang si )=28.3 g(克) 在叠层里面是这么定义的,在一平方英尺的面积上铺一盎司的铜的厚度为1Oz,对应的单位如下

一文读懂高频pcb线路板制作相关知识 众所周知高频PCB线路板涉及才高频材料,对工艺的要求也比较高。今天小编来分享一下高频电路板的制作工艺和注意事项。 首先我们从构造上去了解高频PCB板的制作 高频PCB主要由焊盘、过孔、安装孔、导线、元器件、接插件、填充、电气边界等组成,各组成部分的主要功能如下: 焊盘:用于焊接元器件引脚的金属孔。 过孔:有金属过孔和非金属过孔,其中金属过孔用于连接各层之间元器件引脚。 安装孔:用于固定电路板。

导线:用于连接元器件引脚的电气网络铜膜。 接插件:用于电路板之间连接的元器件。 填充:用于地线网络的敷铜,可以有效的减小阻抗。 电气边界:用于确定电路板的尺寸,所有电路板上的元器件都不能超过该边界。 其次了解高频电路板制作原理是必须: 在高频电路设计中,电源以层的形式设计,在大多数情况下都比以总线的形式设计要好得多,这样回路总可以沿着阻抗最小的路径走。此外电源板还得为PCB上所有产生和接受的信号提供一个信号回路,这样可以最小化信号回路,从而减小噪声,这点常常为低频电路设计人员所忽视。 在高频PCB设计中,我们应该遵循下面的原则: 电源与地的统一,稳定。 仔细考虑的布线和合适的端接可以消除反射。 仔细考虑的布线和合适的端接可以减小容性和感性串扰。 需要抑制噪声来满足EMC要求。 了解了高频电路板构成和制作原理我们就不难理解高频电路板加工注意点 1、阻抗控制要求比较严格,相对线宽控制的很严格,一般公差百分之二左右。 2、由于板材特殊,所以PTH沉铜时的附着力不高,通常需要借助等离子处理设备等先对过孔及表面进行粗化处理,以增加PTH孔铜和阻焊油墨的附着力。 3、做阻焊之前不能磨板,不然附着力会很差,只能用微蚀药水等粗化。

PCB阻抗匹配总结 网名:chinawei97qq: 1219658831 做硬件工程师好几年,有最初的不做阻抗,到后面认为做阻抗是PCB厂家的事情,导致设计的pcb交给pcb厂家后重新修改修改布线,影响项目进度,下面把总结写在后面,以面再犯同样的错误。 做4层板,正片工艺,这样就对做半孔工艺带来加工不方便,半孔工艺会带来价格的增加,单价增加0.05元/cm2 1.6mm厚度的4层PCB板加工,建议做阻抗设计的时候按照1.5mm厚度进行设计,剩下0.1mm厚度留给工厂作为其他工艺要求用(后制诚厚度,绿油、丝印等)。 (1)满足我们TOP层及BOTTOM层5mil线宽单端阻抗控制为55ohm,见附图一;

(2)满足差分线阻抗为100ohm,见附图二

附图二 一般是通过调整层与层之间的填充(如FR-4)的厚度来满足整个板厚及阻抗控制(单端阻抗与填充厚度及导线宽度有关)的要求。 0.5OZ的铜相当于1.2mil ,1OZ的铜相当于1.9mil 。4层板来说,第一、第二层的厚度和第三、第四层的厚度相同,这样平衡对称有利用PCB板加工和使用,放置翘板。采用了外层1.7mil 内层1.4mil 的填充工艺。采用外层1OZ,内存0.5OZ 的工艺。 附图一中H1为第一层、第二层的间距为3MIL 这样第三层、第四层也为3MIL; 整板厚度为1.6mm,取1.5mm 等于 60mil 。叠层设计的厚度为:1.7+1.7+1.4+1.4+3+3+47.8,大致设计以后可以参考candece下面的计算,见附图三。具体阻抗要求 还是以工厂为准。

附图三 差分阻抗比单端阻抗还要多一个影响参数间距,和要设置Coupling Type 对线的类型,参考附图二的trace separation 中S1 参数为 6.5mil ,allegro 计算如附图四。 附图四