试议3D封装到来时的机遇与挑战

苏州德天光学技术有限公司

1111摘要:本文揭示了在摩尔定律即将失效的大背景下,电子信息产业的开发思维、生产方式将发生一系列变革;较详尽地阐述了3D封装将是电子产业发展的必然趋势;反映了检测手段的提高是3D封装目前面临的主要难题。分析了我国信息电子产业在此环境下所面临的机遇和挑战。

关键词:摩尔定律3D封装微焊点自动光学显微检测(MMI)机遇与挑战Discussion on the opportunities and challenges of the 3D pac kage’s coming

Liu Bin, Yan Shixin

Suzhou Detian Optical Technology Co., Ltd.

Abstract: Against the background of Moore’s law will lose effectiveness,a variety of reformation will appear in the development and production mode of electronics and information industry; 3D-TSV will be the inexorable trend of the electronic industry, and the improvement of detection level is the main problem of 3D package. The opportunities and challenges electronics and information industry will be faced with under the circumstances were analyzed.

Key Words: Moore’s Law, 3D Package, Micro-joint Automatic Optical Micro-Inspection (MMI), Opportunities and Challenges

目前,国际电子信息行业正在经历一场新的变革,摩尔定律即将失效,3D封装蓬勃兴起,如果我们能抓住这个机会,对国内相关行业及其发展环境进行大力改革整顿,顺应世界发展潮流,将大大缩小我们同国际先进水平的差距。

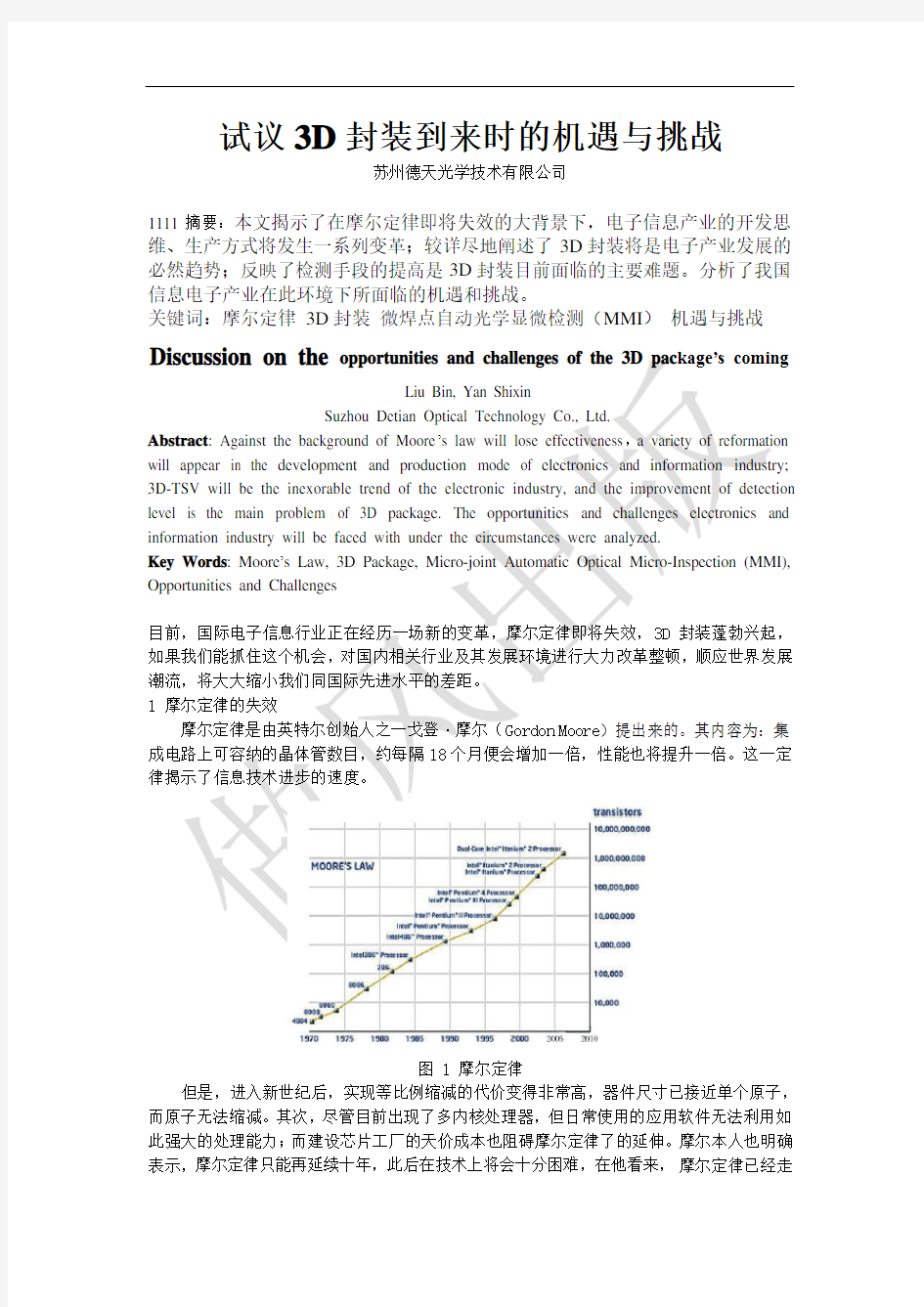

1 摩尔定律的失效

摩尔定律是由英特尔创始人之一戈登·摩尔(Gordon Moore)提出来的。其内容为:集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。这一定律揭示了信息技术进步的速度。

图 1 摩尔定律

但是,进入新世纪后,实现等比例缩减的代价变得非常高,器件尺寸已接近单个原子,而原子无法缩减。其次,尽管目前出现了多内核处理器,但日常使用的应用软件无法利用如此强大的处理能力;而建设芯片工厂的天价成本也阻碍摩尔定律了的延伸。摩尔本人也明确表示,摩尔定律只能再延续十年,此后在技术上将会十分困难,在他看来,摩尔定律已经走

到尽头。由此将引起产业内的一系列的变革。

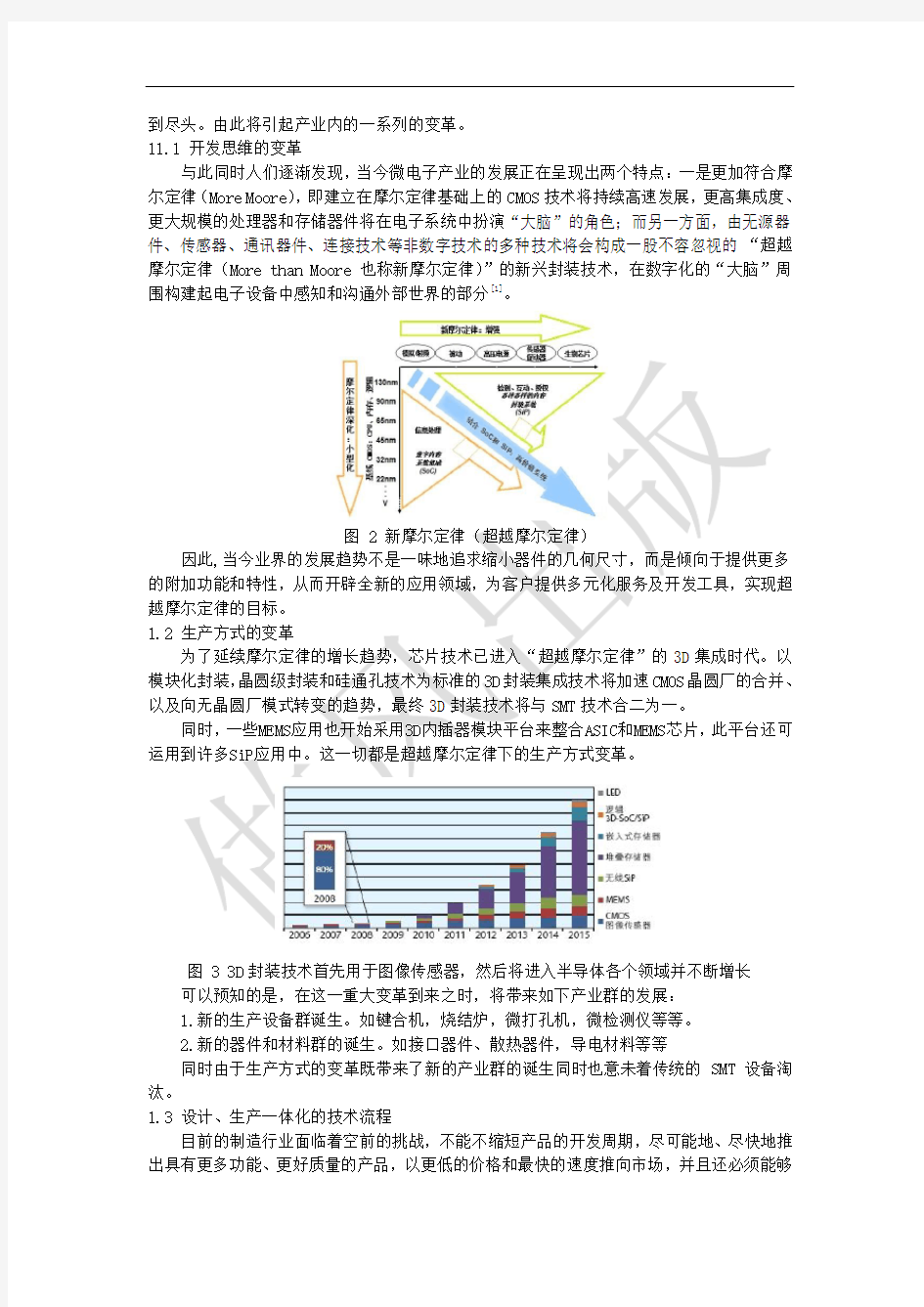

11.1 开发思维的变革

与此同时人们逐渐发现,当今微电子产业的发展正在呈现出两个特点:一是更加符合摩尔定律(More Moore),即建立在摩尔定律基础上的CMOS技术将持续高速发展,更高集成度、更大规模的处理器和存储器件将在电子系统中扮演“大脑”的角色;而另一方面,由无源器件、传感器、通讯器件、连接技术等非数字技术的多种技术将会构成一股不容忽视的“超越摩尔定律(More than Moore也称新摩尔定律)”的新兴封装技术,在数字化的“大脑”周围构建起电子设备中感知和沟通外部世界的部分[1]。

图 2 新摩尔定律(超越摩尔定律)

因此,当今业界的发展趋势不是一味地追求缩小器件的几何尺寸,而是倾向于提供更多的附加功能和特性,从而开辟全新的应用领域,为客户提供多元化服务及开发工具,实现超越摩尔定律的目标。

1.2 生产方式的变革

为了延续摩尔定律的增长趋势,芯片技术已进入“超越摩尔定律”的3D集成时代。以模块化封装,晶圆级封装和硅通孔技术为标准的3D封装集成技术将加速CMOS晶圆厂的合并、以及向无晶圆厂模式转变的趋势,最终3D封装技术将与SMT技术合二为一。

同时,一些MEMS应用也开始采用3D内插器模块平台来整合ASIC和MEMS芯片,此平台还可运用到许多SiP应用中。这一切都是超越摩尔定律下的生产方式变革。

图 3 3D封装技术首先用于图像传感器,然后将进入半导体各个领域并不断增长

可以预知的是,在这一重大变革到来之时,将带来如下产业群的发展:

1.新的生产设备群诞生。如键合机,烧结炉,微打孔机,微检测仪等等。

2.新的器件和材料群的诞生。如接口器件、散热器件,导电材料等等

同时由于生产方式的变革既带来了新的产业群的诞生同时也意未着传统的SMT设备淘汰。

1.3 设计、生产一体化的技术流程

目前的制造行业面临着空前的挑战,不能不缩短产品的开发周期,尽可能地、尽快地推出具有更多功能、更好质量的产品,以更低的价格和最快的速度推向市场,并且还必须能够

不断地去满足日益增多的客户的个性化的需求,快速地组成生产和销售。而电子制造产业受摩尔定律影响,其产品更新换代的速率比其他行业更为迅速,这就对行业的各个方面,尤其是研发和设计的环节带来了非常严峻的挑战。同时也对设计、管理、产业规划提出了更高要求:

设计人员要有一体化概念

在产品的开发过程中,设计人员通常因为信息来源的问题,很难能够清楚地去掌握现在的原材料的价格、供货周期甚至是产品的生产加工方式以及影响使用性能的重要因素。因此,开发人员就很难在设计的过程里就去准确地估算产品的成本,可加工性甚至使用性能,使得开发周期增长,产品总成本大为增加。

我国的产品开发人员往往只注重局部功能的实现而忽略了产品的整体性能的提高,并且在这一思维的指导下,开发人员根本不考虑产品的可制造性,根本不会考虑生产设备共用性的问题,这样很难及时地将开发出来的产品,迅速地转化为商品,从而以最快的速度进入市场。

管理人员要有一体化意识

但在摩尔定律濒临失效的背景下,电子制造业正迅速向系统化、模块化、多功能化方向,这就对研发人员提出了更高的要求:不仅整个系统开发人员与生产人员之间,而且各个模块开发人员之间也要相互交流合作,才能在最短时间内开发出功能最完善,系统整体性能更好的产品,从而在竞争中立于不败之地。

产业规划人员要有一体化思维

电子制造业的发展必须有一个良好的产业链发展的环境。而在一个国家或地区的发展规划中,产业链上的各部分往往分属于不同的部门,这就要求各部门产业规划人员之间能够充分沟通,对电子制造业产业链进行战略性整合,促进其飞速发展。

2 三维封装的兴起

三维封装是将多个芯片垂直连接的一系列方法的统称,到目前为止,三维封装只在引线键合、倒装芯片、模块化封装等特定应用中取得成功。然而,硅通孔封装技术(TSV)作为备选方案得到了迅猛发展。

硅通孔技术(TSV)是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直导通,实现芯片之间互连的最新技术。以TSV为代表的3D集成技术优势有:

降低延迟:IBM半导体研发中心副总裁Lisa Su指出:TSV可把芯片上数据需要传输的距离缩短1000倍,并使每个器件的互连性增加100倍。英特尔计划在未来的万亿赫兹研究型处理器中采用TSV技术。

降低功耗:据报道,IBM在90 nm节点的微处理器50%以上的有源开关功耗都用于驱动互连线,并且90%以上的功率实际上是由10%的长互连线消耗的。据称,TSV可将硅锗芯片的功耗降低大约40%。

手机和其他一些应用需要更加创新的芯片级封装(CSP)解决方案。现在系统设计师为了手机和其他很多紧凑型消费品,不得不选择用3D封装来开发z方向上的潜力。

因此,业内人士将TSV 称为继引线键合(Wire Bonding)、TAB 和倒装芯片(FC)之后的第四代封装技术。

据市场研究公司Yole Developpement统计,到2015年,3D-TSV晶圆的出货量将达数百万,并可能对25%的存储器业务产生影响。2015年,除了存储器,3D-TSV晶圆在整个半导体产业的份额也将超过6%[2]。

图 4 3D技术平台市场细分

2.1 3D封装目前所遇到问题

对于3D-TSV阵列堆叠,关键要素有通孔形成/填充、晶圆减薄、质量评价与检测技术、凸点形成和芯片与芯片/衬底的键合等。这些问题的解决将依赖于大量新型设备与工艺的开发。

图 5在设计方案提出之后,设备和材料就成为制造3D-TSV IC的关键因素减薄技术与设备

减薄技术面临的首要挑战就是超薄化工艺所要求的<50μm的减薄能力。在这个厚度上,硅片很难容忍减薄工程中的磨削对硅片的损伤及内在应力,其刚性也难以使硅片保持原有的平整状态。

目前业界的主流解决方案是采用东京精密公司所率先倡导的一体机思路,将硅片的磨削、抛光、保护膜去除、划片膜粘贴等工序集合在一台设备内,硅片从磨片一直到粘贴划片膜为止始终被吸在真空吸盘上,始终保持平整状态,从而解决了搬送的难题。

刻蚀技术与设备

TSV制程都面临一个共同的难题:通孔的刻蚀。目前通常有两种方法:激光钻孔以及深反应离子刻蚀(DRIE)。激光加工系统供应商Xsil公司为TSV带来了最新解决方案,Xsil称激光钻孔工艺将首先应用到低密度闪存及CMOS传感器中,随着工艺及生产能力的提高,将会应用到DRAM中。

在TSV刻蚀设备领域,Lam Research推出了第一台300mm TSV刻蚀设备2300Syndion,并已发货至客户。而Aviza针对TSV先进封装也推出了Omegai2L刻蚀系统,日月光(ASE)已宣布将采用此系统研发先进制程技术。

晶圆键合技术与设备

EVG公司(奥地利)自2002年起,便致力于针对3D集成开发300mm晶圆键合设备,其首款

300mm多反应腔3D键合系统已在2008年完成。CEA-Leti (法国)及SET(法国)成功开发出新一代高精度(0.5μm)高键合力(4000N)的300mm晶圆器件键合设备FC300[4]。

质量评价与检测技术相关设备

可以预见,TSV的特殊性还会给3D IC制造的检测和量测带来前所未有的困难,控制TSV 通孔工艺需要几何尺寸的量测,以及对刻蚀间距和工艺带来的各种缺陷进行检测。通常TSV 的直径在1μm到50μm,深度在10μm到150μm,深宽比在3到5甚至更高,一颗芯片上的通孔大约在几百甚至上千。减薄和键合工艺对检测和量测的需求更多。厚度和厚度均匀度需要测量,工艺中必须监控研磨浆残留、微粒污染、铜微粒、应力引起的开裂、边缘碎片等。

对于键合,无论是芯片至晶圆、还是晶圆之间,在精准的对位的同时,还需要控制表面粗糙程度、表面洁净度和平坦度。另外,一些新的工艺步骤也需要考虑监控,比如尺寸在几十个微米的凸点阵列等。

目前3D封装技术的发展面临的最大难题是制造过程中的实时工艺过程的实时检测问题,因为这一问题如果解决不了,那么就会出现高损耗,只有控制了每一道生产工艺,就能有效地保证产品的质量,从而达到有效地降低废品率。苏州德天光学技术有限公司开发的微焊点自动光学显微检测仪(MMI)的出现刚好解决了这一技术难题,它可满足所有3D封装的每一个检测点的实时工艺过程控制的要求,微焊点自动光学显微检测仪(MMI)的出现将大大促进3D封装的发展。

2.2 3D封装兴起对电子产业的影响

由于表面贴装技术(Surface Mount Technology,SMT)受到加工精度、可生产性、成本和组装工艺的制约,大大限制了高密度组装的发展。为此,元器件由QFP向BGA、CSP、晶圆级封装(Wafer–Scale Package,WS–CSP)方向发展,封装器件的外形尺寸越来越小。

图 6 封装尺寸变化

但即便这样,仍不能满足对微型化日益增加的需求,为此开始引入了封装器件三维(3D)堆叠组装的理念[3]。

图 7 POP和PiP

3D封装的出现,改变了以往先封装后组装的模式,使封装工艺与前道工艺紧密地结合在一起,作为传统后道工艺的SMT技术除了在某些特别领域仍有少量应用外,将大幅度退出封装市场,为新兴的3D封装技术所取代。在此过程中,大量SMT相关的设备将不得不被淘汰,如贴片机,印刷机,回流炉等。

为了将3D-TSV阵列堆叠从概念转变为生产,需要在制造设备和重大研发工作方面投资。现阶段研发工作的焦点在于如何让整合生产链(如减薄、固定和芯片内工艺)。从而通过总体成本优化和降低终端用户风险来使主流厂商接受TSV工艺。

应用材料公司正在努力加快TSV的广泛应用。为了加快主流应用,该公司正在和其他设备厂商加强合作,包括Semitool公司和一些硅片引线厂商,全面定义工艺流程中相互制约的因素,降低总体成本。

美国半导体制造技术战略联盟(Sematech)3D互联总监Sitaram Arkalgud认为:“以TSV为代表的三维技术在LSI的高性能化及多功能化、低耗电化以及减少占用空间等方面更有优势”。但是,“这种技术上的潜力与实际的大量生产还有距离”,因此“不应将三维连

接视为单一的要素技术”。第一,由导入三维技术来提高生产效率,应由各层供货商齐心协力来实现,而不是诸如只需特定的制造装置业界努力就能实现的问题。需要前端工序、封装、设计、测试等电子产业整体的合作。第二,成本优势不是单从芯片,而应是从整个系统出发来评估。在推动TSV技术向前发展的过程中,大量新的产业链将在电子产业整体合作中产生。

3 机遇与挑战

面对世界蓬勃发展的电子产业形势,分析我国目前的产业现状,一些问题值得我们深思。我国自从新中国成立后由于内乱已失去了多次发展的良机,在电子信息产业面临全面洗牌之际,应该如何谋划我国的原生态产业发展目,是时不我待的头等大事。只有先进的生产设备体系的建立,才能达到成为制造强国的目的,国力的增强才实而不虚。为了达到这一目标,我们必需:

3.1 战略层面的考虑

电子产业必须与时俱进才能发展。国际电子产业发展的历史证明了这一点。我国电子产业如何与时俱进?当务之急是研究我国电子产业的发展战略,制订发展规划。从战略方面考虑,需要做到以下三点:一是积极推进先进新兴产业的发展;二是高度重视不同领域和技术的交叉和融合,优化我国电子产业的科研生产体系。三是重视电子产业人才的培养,积极倡导和大力发展属于我国自主知识产权的原创技术。否则,我们将越跟踪越落后。在这一点,我们可以很好地借鉴韩国和我国台湾的经验。

3.2 具体政策的形成和落实

积极推进先进产业的发展

产业规划人员需要研究国内外产业形势,把握产业发展趋势,才能准确判断各种技术的发展前景,从而制定相应的发展规划。对于先进发展方向的技术,应该大力支持,特别是关系到新兴产业发展的关键技术,应该重点扶持,并以此为切入点,推动整个产业链的发展。为此我们必需做好经下几点:

1.统计现有生产设备的实际库存量,做好即将淘汰设备的淘汰前的准备工作,制订新

发展规划。

2.研究新的生产线的设备的分布情况,制定出不同的发展方向,先可抓大放小,从易

到难。

3.制定切实可行的扶持机制,最简单的行之有效的方法,就是用产品说话和市场说话。

高度重视不同领域和技术的交叉和融合

不同材料的交叉和融合产生新的材料;不同技术交叉和融合产生新的技术;不同领域的交叉和融合产生新的领域。我们国家在相关协会已经有不少分会和机构,技术领域已涉及电子电路、电子封装、表面安装、电子装联、电子材料、电子专用设备、电子焊接和电子电镀等。过去,同行业交流较多,但不同行业交流不够,今后应积极组织这种技术交流。

重视电子产业人才的培养

国家应把握目前电子产业发展的大好机遇,统筹计划、统一布局、集中投资和人才,尽快建设若干个关于信息电子产业的研究开发中心或重点实验室,使之成为我国信息电子创新技术的发源地和优秀人才的培养基地。

3.3 标准的制定及知识产权的维护

在新产业链形成的过程当中,新的产业标准(设计、制造等)和将被制定,大量专利必将申报。只有在现阶段对相关技术大量投入,抢占先机,才能在制定产业标准时获得一定话语权,以形成对我国电子制造业有利的产业标准;在专利成果方面打破国外垄断,核心技术不受国外制约。

对已申请的专利要做好知识产权的维护,这样不仅使原创者利益不受到损害,也能维护整个产业内一个公平的发展环境,进而鼓励、推动更多企业自主创新,形成技术创新的良性

循环,推动整个产业的迅猛发展。

3.4 战术的谋划和扶持

先进产业的推动

在摩尔定律即将失效,3D封装正在兴起的背景下,继续推动企业成为技术创新的主体,鼓励企业加大研究开发投入。建立市场主导型的技术创新机制,实施企业技术创新工程。按照政府引导、市场化运作的方式,大力推进企业联合重组,培育若干大型企业集团,使其具有技术创新和自主开发能力,规模化生产能力,系统集成和综合服务能力。

对即将淘汰的SMT技术、设备要限制引进,转而大力支持本土3D产业,对从事3D封装技术的高新企业给予政策、资金上的优惠,鼓励其进行3D封装核心技术和设备的研发,争取在新一轮的产业链分工竞争中占有一席之地。

科研方面的扶持

对高校、科研院所的科研项目申请,应引导其向3D和系统集成方向发展,以顺应国际发展趋势,鼓励其与企业共同申报,以形成优势互补,互惠互利的局面。大力促进产学研联合,组建以资产为纽带的产学研紧密联合体。加大技术改造,注重对引进技术的消化与吸收,实现引进、消化、吸收、创新与自主开发的良性循环。不仅能加快研发成果向实际生产的转化,同时也能培养一批熟悉研发、生产流程的专业人才。

3.5 配套措施的完善

要使整个产业获得良好发展,还必须完善相关的配套措施。

硬件方面

建立良好投资环境,集中打造具有产业优势的工业园区;在3D封装发展过程中,新型材料,设备必然大量出现,要重视对这些新材料、新设备的前期研发,为新兴产业链的兴起做好技术准备。

软件方面

建立和完善多渠道融投资体制,多渠道筹措电子信息产业建设资金;建立风险投资机制;积极争取国家和省市资金支持,建立电子信息产业建设资金,集中投向。引进和完善风险投资模式和机制,制定鼓励电子信息产业发展的优惠政策,加大资金扶持力度,创建信息产业风险投资基金和专项发展资金。发展民营高科技企业,积极扶持民营企业成长,成为电子信息产业又一支生力军。

4 结论

在摩尔定律即将失效的大背景下,电子信息产业的开发思维、生产方式将发生一系列变革,现有技术流程将被先进的设计、生产一体化所取代;以硅通孔技术(TSV)为代表的3D 封装将是电子产业发展的必然趋势,现有大多数设备必将淘汰,新设备、新工艺大量出现,多条新兴产业链迅速形成。在此情况下,我们要从战略层面上对整个产业进行改革调整,顺应国际发展趋势,鼓励产业创新,才能在未来新兴产业竞争中达到国际先进水平。

参考文献

[1]童志义. 后摩尔时代的封装技术[J]. 电子工业专用设备.2010年6月总第185

期:1-8.

[2]童志义. 3D IC 集成与硅通孔(TSV)互连[J].电子工业专用设备. 2009年3月总

第170期:27-34.

[3]胡志勇. 满足高密度组装的SMT三维封装堆叠技术[J].表面安装技术. 2009 第10

期,58-69

[4]郎鹏,高志方,牛艳红,3D封装与硅通孔工艺技术[J].电子工艺技术. 2009年11

月第30卷第6期:323-326

3D IC-TSV技术与可靠性研究 摘要:对三维(3 Dimension,3D)堆叠集成电路的硅通孔(Through Silicon Via,TSV)互连技术进行了详细的介绍,阐述了TSV的关键技术与工艺,比如对准、键合、晶圆减薄、通孔刻蚀、铜大马士革工艺等。着重对TSV可靠性分析的重要性、研究现状和热应力分析方面进行了介绍。以传热分析为例,实现简单TSV模型的热仿真分析和理论计算。最后介绍了TSV技术市场化动态和未来展望。 关键词: 3D-TSV;通孔;晶圆减薄;键合;热可靠性 0 引言 随着半导体制作工艺尺寸缩小到深亚微米量级,摩尔定律受到越来越多的挑战。首先,互连线(尤其是全局互连线)延迟已经远超过门延迟,,这标志着半导体产业已经从“晶体管时代”进入到“互连线时代”。为此,国际半导体技术路线图组织(ITRS)在 2005 年的技术路线图中提出了“后摩尔定律”的概念。“后摩尔定律”将发展转向综合创新,而不是耗费巨资追求技术节点的推进。尤其是基于TSV(Through Silicon Via)互连的三维集成技术,引发了集成电路发展的根本性改变。三维集成电路(Three-Dimensional Integrated Circuit,3D IC)可以将微机电系统(MEMS)、射频模块(RF module)、内存(Memory)及处理器(Processor)等模块集成在一个系统内[1],,大大提高了系统的集成度,减小了功耗,提高了性能,因此被业界公认为延续摩尔定律最有效的途径之一,成为近年来研究的热点。 目前3D集成技术主要有如下三种:焊线连接(Wire-Bonding)、单片集成(Monolithic Integration)和TSV技术[2]。焊线连接是一种直接而经济的集成技术,但仅限于不需要太多层间互连的低功率、低频的集成电路。单片集成是在同一个衬底上制作多层器件的新技术,它的应用受到工艺温度要求很高和晶体管质量较差等约束。基于TSV的3D集成可以实现短且密的层间互连,有效缩短了互连线长度,大大提高了系统集成度,降低了互连延时,提高了系统性能,缩小了封装尺寸,高频特性出色,芯片功耗降低(可将硅锗芯片的功耗降低大约40%),热膨胀可靠性高,同时还实现了异构集成,成为业界公认使摩尔定律持续有效的有力保证,所以备受研究者的青睐。 1 TSV技术与相关工艺 1.1 TSV技术介绍 TSV技术将在先进的三维集成电路(3D IC)设计中提供多层芯片之间的互连功能[3]。图2给出了最早的TSV结构示意图,这是1958年诺贝尔奖得主WilliamShockley提出的[4]。它是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直导通,一般用导体材料钨、铝、铜、多晶硅或碳纳米管构成的互连线垂直穿过硅衬底以实现上下层芯片的信号互连[5],需要穿透组成叠层电路的各种材料以及很厚的硅衬底。TSV作为目前芯片互连的最新技术,使芯片在三维方向堆叠密度最大、芯片间的互连线最短、外形尺寸最小,大大改善芯片速度,产生低功耗性能。 使用硅基板和TSV的三维堆叠的结构。在 3D 芯片堆叠结构中,为了充分利用三维集成电路的优势[6],硅通孔能缩短堆叠芯片之间的垂直互连,硅中介层是在相同衬底上途经任何组件的硅衬底。TSV对通孔进行金属化处理,然后在孔上形成低熔点的凸点,使之成为导电通孔,再利用孔内的金属焊点以及金属层进行垂直方向的互连[7]。与目前应用于多层互连的通孔不同,TSV技术尺寸的一般要求如表1 所示。

晶圆级三维系统集成技术 三维集成系统正在快速增长,它涉及众多不同技术新兴领域,目前已出现诸多大有希望应用于三维集成的新技术。本文将对其中的一项技术进行系统介绍。为了实现三维结构的体积最小化和具有优良电性能的高密度互连,我们将采用穿硅通孔(TSV)用于晶圆级堆叠器件的互连。 该技术基本工艺为高密度钨填充穿硅通孔,通孔尺寸从1μm到3μm。用金属有机化学汽相淀积(MOCVD)淀积一层TiN薄膜作为籽晶层,随后同样也采用CVD工艺淀积而成的钨膜的扩散势垒层即可实现具有大纵宽比(HAR)ICV的金属填充。堆叠器件的未来应用还需要铜填充TSV以优化电学性能。所谓的ICV-SLID技术可用于制作三维器件的堆叠。这项工艺非常适合应用于产品的低成本高效率生产,包括高性能应用,如三维微处理器和高度小型化的多功能系统,传感器之间的节点、存储器数据处理与传输(eGrains TM, eCubes TM)等。 推动三维系统集成技术发展的关键因素 从总体上看,加速三维集成技术应用于微电子系统生产的重要因素包括以下几个方面:?系统的外形体积:缩小系统体积、降低系统重量并减少引脚数量的需求, ?性能:提高集成密度,缩短互连长度,从而提高传输速度并降低功耗, ?大批量低成本生产:降低工艺成本,如混合技术等, ?新应用:如超小无线传感器系统等。 与系统芯片(SoC)相比,这种新方法是一种能将不同优化生产技术高效融合在一起的三维系统集成技术。此外,三维集成方法还可能用于解决由信号传播延迟导致的“布线危机”,不管是板级的还是芯片级的,其原因是这种方法可以实现最短的互连长度,而且还省去了受速度限制的芯片之间及芯片内部互连。 低成本制作潜力也是影响三维集成技术未来应用的主要因素。当前,系统芯片的制作主要依靠单片集成来嵌入多种工艺。但这种方法有很多缺陷,如复杂性达到最高程度时会使分片工艺非常困难,从而导致总系统“制作成本爆炸性”提高。与之相比,采用适当的三维集成技术可以将MEMS和CMOS等不同的最佳基础工艺有机结合起来,通过提高产品合格率和小型化程度,发挥该技术低成本制作的潜力。与单片集成SoC相比,采用最佳三维集成技术制作的器件堆叠(如控制器层和存储器层等)会使生产成本显著降低。此外,采用该技术还有望实现新型多功能微电子系统,如分布式无线传感器网络应用的超小型传感器节点等(图1)。

第38卷第3期2017年3月 焊 接 学 报 TRANSACTIONSOFTHECHINAWELDINGINSTITUTION Vol.38 No.3March 2017 收稿日期:2015-03-18 基金项目:黑龙江省自然科学基金资助项目(E201449) 三维封装铜柱应力及结构优化分析 江 伟, 王丽凤 (哈尔滨理工大学材料科学与工程学院,哈尔滨 150080) 摘 要:文中利用有限元模拟软件ANSYS对三维立体封装芯片发热过程中整体应力及局部铜柱的应力情况进行了分析,并对三维封装的结构进行了优化设计.结果表明,最大应力分布在铜柱层,铜柱的应力最大点出现在铜柱外侧拐角与底部接触位置.以铜柱处最大应力作为响应,进行了结构参数优化,采用三因素三水平正交试验方法,分别使用铜柱直径、铜柱高度、铜柱间距三个影响因素作为变化的结构参数.结果表明,铜柱直径的变化对等效应力影响最大,铜柱间距次之,铜柱高度影响最小.且发现随着铜柱高度、铜柱间距、铜柱直径的不断增大其铜柱外侧拐角与底部接触位置的最大等效应力不断减小.关键词:有限元模拟;铜柱应力;正交试验;参数优化 中图分类号:TG404 文献标识码:A 文章编号:0253-360X(2017)03-0112-05 0 序 言 随着电子工业的不断发展,对微系统的功能、密度和性能要求不断提高,为顺应摩尔定律的增长趋势,芯片技术越来越向着小型化和高性能方向发展,并且越来越需要三维集成方案,在此推动下,穿透硅通孔技术(throughsiliconvias,TSV)应运而生 [1] ,成 为三维集成、芯片级和晶圆级封装的关键技术之一.TSV技术是通过在芯片与芯片之间、晶圆与晶圆之间作垂直互连,是实现芯片之间互连的最新技术.三维封装与传统封装相比有特殊的优势,TSV能够使三维方向堆叠密度最大,因此使得电性能大大提高,互连长度大大减小 [2] .3D堆叠芯片极薄,可以 小到50~100μm,非常容易产生裂纹[3] ,例如在热 循环和高压键合下极易产生裂纹,很多研究指出,通过调整铜柱高度,铜柱间距及铜柱直径可以避免裂纹的产生 [4,5] . 由于三维封装结构的复杂性和尺寸的微化,使得TSV技术变得更加复杂,许多有关TSV技术的研究也只是在初期,因此使用ANSYS软件利用有限元分析方法对三维堆叠封装进行模拟研究显得尤为重要.在小规模三维堆叠封装中,芯片产热是极大的,特别是芯片极薄的情况下会产生很大的温差,中间温度极高,对芯片造成损害,另外随着芯片封装尺寸 的减小和芯片的垂直堆叠,大量不同热膨胀系数的材料将围绕TSV,由于铜热膨胀系数相对较大,造成材料间热膨胀系数差很大,这样在热的作用下将产生大量的热应力,因此由于芯片发热问题而引起的热应力不得不被引起高度重视. Chukwudi等人 [6] 对3D-SIC封装中铜通孔Cu- Cu键合压力进行了研究,认为铜(16.7ppm/℃)与硅之间(2.3ppm/℃)热膨胀系数的不匹配,铜的自 由膨胀被大块的硅所限制将会在硅片内部产生应力而影响结构的整体性能,最终导致硅片的失效.文中虽然指出失效机制,但并未对此进行深入研究.因此研究铜与硅之间的结构力学性能具有重要的意义.Hsieh等人 [7] 对四层芯片堆叠封装体的热力学 性能进行了模拟计算研究.为了获得在堆叠IC封装的热应力分布,设计了4层堆叠IC封装(芯片对芯片)与TSV技术的结构.指出在芯片发热过程中,TSV受热应力的影响,封装体最大应力出现在芯片界面和TSV结构连接处.文中指出了最大应力的分布位置,但并未对影响应力分布的结构参数进行研究,因此研究铜结构参数对应力分布的影响具有重要意义.文中首先通过一组合适的参数研究了在芯片发热过程中三维封装结构整体应力情况及局部TSV通孔中铜柱的应力情况,然后把铜柱直径、高度和间距作为优化参数,通过使用正交试验方法对不同参数下铜柱最大应力数据进行分析,从而找到铜柱直径、铜柱高度和铜柱间距三者对铜柱应力影响的大小. 万方数据

系统级封装(SiP)的发展前景(上) ——市场驱动因素,要求达到的指标,需要克腰的困难 集成电路技术的进步、以及其它元件的微小型化的发展为电子产品性能的提高、功能的丰富与完善、成本的降低创造了条件。现在不仅仅军用产品,航天器材需要小型化,工业产品,甚至消费类产品,尤其是便携式也同样要求微小型化。这一趋势反过来又进一步促进微电子技术的微小型化。这就是近年来系统级封装(SiP,System in Package)之所以取得了迅速发展的背景。SiP已经不再是一种比较专门化的技术;它正在从应用范围比较狭窄的市场,向更广大的市场空间发展;它正在成长为生产规模巨大的重要支持技术。它的发展对整个电子产品市场产生了广泛的影响。它已经成为电子制造产业链条中的一个重要环节。它已经成为影响,种类繁多的电子产品提高性能、增加功能、扩大生产规模、降低成本的重要制约因素之一。它已经不是到了产品上市前的最后阶段才去考虑的问题,而是必须在产品开发的开始阶段就加以重视,纳入整体产品研究开发规划;和产品的开发协同进行。再有,它的发展还牵涉到原材料,专用设备的发展。是一个涉及面相当广泛的环节。因此整个电子产业界,不论是整机系统产业,还是零部件产业,甚至电子材料产业部门,专用设备产业部门,都很有必要更多地了解,并能够更好地促进这一技术的发展。经过这几年的发展,国际有关部门比较倾向于将SiP定义为:一个或多个半导体器件(或无源元件)集成在一个工业界标准的半导体封装内。按照这个涵义比较广泛的定义,SiP又可以进一步按照技术类型划分为四种工艺技术明显不同的种类;芯片层叠型;模组型;MCM型和三维(3D)封装型。现在,SiP应用最广泛的领域是将存储器和逻辑器件芯片堆叠在一个封装内的芯片层叠封装类型,和应用于移动电话方面的集成有混合信号器件以及无源元件的小型模组封装类型。这两种类型SiP的市场需求在过去4年里十分旺盛,在这种市场需求的推动下,建立了具有广泛基础的供应链;这两个市场在成本方面的竞争也十分激烈。 而MCM(多芯片模组)类型的SiP则是一贯应用于大型计算机主机和军用电子产

三维集成封装的电热特性研究及优化设计在技术发展、社会需要以及经济增长的驱动下,“延续摩尔”和“超越摩尔”成为了目前集成电路发展的两大趋势,在这种情况下,三维集成封装技术受到了广泛的认可。目前,三维集成封装技术在多方面都取得了突破性的进展,然而仍然存在由于内部复杂电磁环境导致的电可靠性问题,以及由于堆叠芯片增大了功率密度导致的热可靠性问题,针对这些问题,本文着重于三维集成封装的电热特性以及优化设计方面的创新研究,并取得了如下成果:1)研究了三维集成封装多端口互连的电特性与优化设计。我们首先提出了新型共面波导串扰屏蔽结构,分析其电特性并据此进行了优化设计,然后对结果进行了实验验证;接下来针对基于“地缺陷结构”的共模噪声滤波器,分析了各尺寸参数对于其电特性的影响并提出了应用机器学习进行优化的方法。2)显著的提高了应用去嵌入方法测量三维集成封装多端口硅通孔(TSV)高频电特性的测量精度。 我们首先分析了传统去嵌入测量结构与算法,得到将其应用于多端口高频电特性测量的两个补充条件,并通过修正测量结构与加入屏蔽TSV满足了这两个条件,进而提高了测量精度,其中插入损耗的最大相对误差从33.52%降低至4.67%,最后通过实验进行了验证。3)使用解析法研究了三维集封装TSV的横向热特性,包括TSV作为热源的稳态热特性以及TSV作为导热材料的瞬态热特性,并分别通过数值仿真对推导结果进行了验证。4)提出了基于流体制冷和机器学习的三维集成封装动态热管理方案。我们首先讨论了集成流体热槽的三维集成封装的建模仿真方法,然后提出了基于机器学习的优化控制方法并讨论了算法的计算复杂度,最后通过仿真模拟热管理系统工作,验证了该动态热管理方案的有效性。

LANCASTER

UNIVERSITY

Centre for Microsystems Engineering Faculty of Applied Sciences

System-in-Package Research within the IeMRC

Prof. Andrew Richardson Lancaster University

Project Statistics

? Design for Manufacture Methodology for SiP

– – – – Academic partners : Lancaster University & Greenwich Industrial partners : NXP, Flowmerics, Coventor & Selex £206K – Nov 2005 – Nov 2007 Focus : Reliability Engineering of SiP assemblies

? Integrated Health Monitoring of MNT Enabled Integrated Systems “I-Health”

– Academic partners : Lancaster University & Heriot Watt University – Industrial partners : NXP, QinetiQ, Coventor, MCE – Focus : Embedded Test & Health Monitoring of SiP based systems

国家标准《集成电路硅通孔(TSV)三维封装可靠性试验方法》(征求意见稿)编制说明 1工作简况 1.1任务来源 本项目是2018年国家标准委下达的军民通用化工程标准项目中的一项,本国家标准的制定任务已列入2018年国家标准制修订项目,项目名称为《集成电路硅通孔(TSV)三维封装可靠性试验方法》,项目编号为:20182284-T-339。本标准由中国电子技术标准化研究院负责组织制定,标准归口单位为全国半导体器件标准化技术委员会集成电路分技术委员会(TC78/SC2)。 1.2起草单位简介 中国电子技术标准化研究院是工业和信息化部直属事业单位,专业从事工业和电子信息技术领域标准化科研工作。中国电子技术标准化研究院紧紧围绕部中心工作,立足标准化工作核心,研究工业和电子信息技术领域标准化发展战略,提出相关规划和政策建议;组织建立和完善电子信息、软件服务等领域技术标准体系,开展共性、基础性标准的研究制定和应用推广;承担电子产品的试验检测、质量控制和技术评价、质量监督检查和质量争议鉴定等工作;负责电子工业最高计量标准的建立、维护和量值传递工作;开展管理体系认证、产品认证、评估服务等相关活动;建立和维护标准信息资源,开展标准信息服务、技术咨询评估和培训活动。 1.3主要工作过程 接到编制任务,项目牵头单位中国电子技术标准化研究院成立了标准编制组,中科院微电子研究所、华进半导体封装先导技术研发中心有限公司、中国电子科技集团公司第十三研究所等相关单位参与标准编制工作。编制组落实了各单位职责,并制定编制计划。 编制组查找了国际、国内三维集成电路封装相关标准,认真研究了现行集成电路标准体系和相关标准技术内容,在此基础上形成了标准草案。 2标准编制原则和确定主要内容的论据及解决的主要问题 2.1本标准制定原则 本标准遵循“科学性、实用性、统一性、规范性”的原则进行编制,依据GB/T 1.1-2009规则起草,确立了本标准的范围、规范性引用文件、术语和定义。 2.2标准的主要内容与依据 2.2.1本标准的定位 本标准是三维(3D)集成电路(IC)封装系列标准中的一项,规定了采用硅通孔(TSV)

试议3D封装到来时的机遇与挑战 苏州德天光学技术有限公司 1111摘要:本文揭示了在摩尔定律即将失效的大背景下,电子信息产业的开发思维、生产方式将发生一系列变革;较详尽地阐述了3D封装将是电子产业发展的必然趋势;反映了检测手段的提高是3D封装目前面临的主要难题。分析了我国信息电子产业在此环境下所面临的机遇和挑战。 关键词:摩尔定律3D封装微焊点自动光学显微检测(MMI)机遇与挑战Discussion on the opportunities and challenges of the 3D pac kage’s coming Liu Bin, Yan Shixin Suzhou Detian Optical Technology Co., Ltd. Abstract: Against the background of Moore’s law will lose effectiveness,a variety of reformation will appear in the development and production mode of electronics and information industry; 3D-TSV will be the inexorable trend of the electronic industry, and the improvement of detection level is the main problem of 3D package. The opportunities and challenges electronics and information industry will be faced with under the circumstances were analyzed. Key Words: Moore’s Law, 3D Package, Micro-joint Automatic Optical Micro-Inspection (MMI), Opportunities and Challenges 目前,国际电子信息行业正在经历一场新的变革,摩尔定律即将失效,3D封装蓬勃兴起,如果我们能抓住这个机会,对国内相关行业及其发展环境进行大力改革整顿,顺应世界发展潮流,将大大缩小我们同国际先进水平的差距。 1 摩尔定律的失效 摩尔定律是由英特尔创始人之一戈登·摩尔(Gordon Moore)提出来的。其内容为:集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。这一定律揭示了信息技术进步的速度。 图 1 摩尔定律 但是,进入新世纪后,实现等比例缩减的代价变得非常高,器件尺寸已接近单个原子,而原子无法缩减。其次,尽管目前出现了多内核处理器,但日常使用的应用软件无法利用如此强大的处理能力;而建设芯片工厂的天价成本也阻碍摩尔定律了的延伸。摩尔本人也明确表示,摩尔定律只能再延续十年,此后在技术上将会十分困难,在他看来,摩尔定律已经走

(一) 硅通孔(TSV,Through -Silicon-Via)技术 3D 封装的发展趋势已经被清楚地确认,穿透硅通孔(TSV)的晶圆封装技术已不断地向 高量产发展。然而,许多问题的研究仍然在进行中,比如:对于通孔联结需要怎样的深宽比及哪些填充材料和技术能够满足它们。 穿透硅通孔(TSV) 将在先进的三维集成电路(3D IC)设计中提供多层芯片之间的互连功能。TSV 与目前应用于多层互连的通孔有所不同,一方面是尺寸的差异(直径1~100 μm,深度10~400 μm),另一方面,它们不仅需要穿透组成叠层电路的各种材料,还需要穿透很厚的硅衬底。目前制造商们正在考虑的多种三维集成方案,也需要多种尺寸的TSV 与之配合。 等离子刻蚀技术已经广泛应用于存储器和MEMS 生产的深硅刻蚀工艺,同样也非常适合于 制造TSV。 TSV 作为新一代封装技术,是通过在芯片和芯片之间,晶圆和晶圆之间制造垂直导通,实现芯片之间互连的最新技术,能够在三维方向使得堆叠密度最大,芯片之间的互连线最短、且外形尺寸最小,大大改善了芯片速度和低功耗性能。 (定义)硅通孔技术(TSV)是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直导通,实现芯片之间互连的新技术(见图4 所示)。 TSV 技术被看做是一个必然的互连解决方案,是目前倒装芯片和引线键合型叠层芯片 解决方案的很好补充。许多封装专家认为TSV 是互连技术的下一阶段。实际上,TSV 可以很好取代引线键合。 硅通孔技术(TSV)是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直导通,实现芯片 之间互连的最新技术。它将集成电路垂直堆叠,在更小的面积上大幅提升芯片性能并增加芯片功能。与以往的IC 封装键合和使用凸点的叠加技术不同,TSV 能够使芯片在三维方向堆叠的密度最大,外形尺寸最小,并且大大改善芯片速度和低功耗的性能。因此,业内人士将TSV 称为继引线键合(Wire Bonding)、TAB 和倒装芯片(FC)之后的第四代封装技术。 由于TSV 工艺的内连接长度可能是最短的,因此可以减小信号传输过程中的寄生损失 和缩短时间延迟。TSV 的发展将受到很多便携式消费类电子产品的有力推动,这些产品需 要更长的电池寿命和更小的波形系数。芯片堆叠是各种不同类型的电路互相混合的最佳手段,例如将存储器直接堆叠在逻辑器件上方。 TSV的优势:

微电子封装技术发展趋势 电子产品正朝着便携式、小型化、网络化和多媒体化方向发展,这种市场需求对电路组装技术提出了相应的要求,单位体积信息的提高(高密度)和单位时间处理速度的提高(高速化)成为促进微电子封装技术发展的重要因素。 片式元件:小型化、高性能 片式元件是应用最早、产量最大的表面组装元件。它主要有以厚薄膜工艺制造的片式电阻器和以多层厚膜共烧工艺制造的片式独石电容器,这是开发和应用最早和最广泛的片式元件。 随着工业和消费类电子产品市场对电子设备小型化、高性能、高可靠性、安全性和电磁兼容性的需求,对电子电路性能不断地提出新的要求,片式元件进一步向小型化、多层化、大容量化、耐高压、集成化和高性能化方向发展。在铝电解电容和钽电解电容片式化后,现在高Q 值、耐高温、低失真的高性能MLCC已投放市场;介质厚度为10um的电容器已商品化,层数高达100层之多;出现了片式多层压敏和热敏电阻,片式多层电感器,片式多层扼流线圈,片式多层变压器和各种片式多层复合元件;在小型化方面,规格尺寸从3216→2125→1608→1005发展,目前最新出现的是0603(长0.6mm,宽0.3mm),体积缩小为原来的0.88%。 集成化是片式元件未来的另一个发展趋势,它能减少组装焊点数目和提高组装密度,集成化的元件可使Si效率(芯片面积/基板面积)达到80%以上,并能有效地提高电路性能。由于不在电路板上安装大量的分立元件,从而可极大地解决焊点失效引起的问题。 芯片封装技术:追随IC的发展而发展 数十年来,芯片封装技术一直追随着IC的发展而发展,一代IC就有相应一代的封装技术相配合,而SMT的发展,更加促进芯片封装技术不断达到新的水平。 六七十年代的中、小规模IC,曾大量使用TO型封装,后来又开发出DIP、PDIP,并成为这个时期的主导产品形式。八十年代出现了SMT,相应的IC封装形式开发出适于表面贴装短引线或无引线的LCCC、PLCC、SOP等结构。在此基础上,经十多年研制开发的QFP 不但解决了LSI的封装问题,而且适于使用SMT在PCB或其他基板上表面贴装,使QFP终于成为SMT主导电子产品并延续至今。为了适应电路组装密度的进一步提高,QFP的引脚间距目前已从1.27mm发展到了0.3mm 。由于引脚间距不断缩小,I/O数不断增加,封装体积也不断加

TSV三维封装内部典型缺陷的特征识别方法研究随着微电子技术的飞速发展,为了应对现代微电子器件高集成,小型化和高可靠性的封装要求,TSV(硅通孔,Through-Silicon Via,简称TSV)三维封装技术凭借其集成度高,低时延和低功耗等优良特点而受到广泛关注。与此同时,由于小孔径、高密度及高深宽比正逐渐成为TSV三维封装的主流发展趋势,极易造成其缺陷的频繁发生,而缺陷大多集中于晶圆和芯片内部,如果能掌握其缺陷的外在表现特征并加以识别,进而可以达到TSV三维封装内部缺陷检测的目的。本文主要以TSV内部缺陷响应机理研究为基础,采用理论分析,有限元仿真和试验结果验证相结合的方式,得到其缺陷下温度和应力的分布规律,识别和定位出相应的缺陷,通过掌握TSV内部缺陷的外在表现形式,从而可解决三维封装中内部缺陷难检测的问题。 具体工作内容如下:首先,综合阐述了目前关于TSV缺陷检测的常见方法,结合TSV三维封装基本结构和工作方式,着重分析了TSV三维封装内部的热传导过程,建立了TSV三维封装内部热传导微分方程和热阻网络模型,并在此基础上做了应力应变分析,为后续的仿真和试验提供理论支撑。然后,针对填充缺失、含有缝隙和底部空洞三种典型的TSV内部缺陷,分别建立了有限元模型,并进行了热-电和热-结构耦合条件下的有限元分析。两种耦合场下的仿真结果表明:从整体上来看所有含缺陷的TSV均显示出了与正常结构明显不同的温度和应力分布。 相比而言,在三种缺陷中,含有填充缺失的TSV显示出最明显的温度和应力分布及路径变化差异;其次为底部有空洞的TSV;而具有缝隙的TSV差异最小,并且还探究了TSV层指定路径上温度分布变化的规律。最后,设计并制备出了所需的TSV试验样品,并对样品进行了测量和试验系统的搭建。试验结果表明:(1)温

三维封装技术创新发展(2020年版) 先进封测环节将扮演越来越重要的角色。如何把环环相扣的芯片技术链系统整合到一起,才是未来发展的重心。有了先进封装技术,与芯片设计和制造紧密配合,半导体世界将会开创一片新天地。 从半导体发展趋势和微电子产品系统层面来看,先进封测环节将扮演越来越重要的角色。如何把环环相扣的芯片技术链系统整合到一起,才是未来发展的重心。有了先进封装技术,与芯片设计和制造紧密配合,半导体世界将会开创一片新天地。现在需要让跑龙套三十年的封装技术走到舞台中央。

日前,厦门大学特聘教授、云天半导体创始人于大全博士在直播节目中指出,随着摩尔定律发展趋缓,通过先进封装技术来满足系统微型化、多功能化成为集成电路产业发展的新的引擎。在人工智能、自动驾驶、5G网络、物联网等新兴产业的加持下,使得三维(3D)集成先进封装的需求越来越强烈,发展迅猛。 一、先进封装发展背景 封装技术伴随集成电路发明应运而生,主要功能是完成电源分配、信号分配、散热和保护。伴随着芯片技术的发展,封装技术不断革新。封装互连密度不断提高,封装厚度不断减小,三维封装、系统封装手段不断演进。随着集成电路应用多元化,智能手机、物联网、汽车电子、高性能计算、5G、人工智能等新兴领域对先进封装提出更高要求,封装技术发展迅速,创新技术不断出现。 于大全博士在分享中也指出,之前由于集成电路技术按照摩尔定律飞速发展,封装技术跟随发展。高性能芯片需要高性能封装技术。进入2010年后,中道封装技术出现,例如晶圆级封装(WLP,Wafer Level Package)、硅通孔技术(TSV,Through Silicon Via)、2.5D Interposer、3DIC、Fan-Out 等技术的产业化,极大地提升了先进封装技术水平。 当前,随着摩尔定律趋缓,封装技术重要性凸显,成为电子产品小型化、多功能化、降低功耗,提高带宽的重要手段。先进封装向着系统集成、高速、高频、三维方向发展。

系统级封装(Sip)问题的研究 1优势 1.1较短的开发时间 系统级封装产品研制开发的周期比较短,市场响应时间比较快。 全新的SoC需要耗费大量的时间和金钱,许多产品(特别是消费类产品)不堪重负。例如,某些SoC的上市时间长达18个月,而SiP可以将该时间削减50%或更短。 1.2满足小型化需求,缩短互联距离 将原本各自独立的封装元件改成以SiP技术整合,便能缩小封装体积以节省空间,并缩短元件间的连接线路而使电阻降低,提升电性效果,最终呈现微小封装体取代大片电路载板的优势,又仍可维持各别晶片原有功能。 系统级封装可以使多个封装合而为一, 从而显着减小封装体积、重量,减少I/O引脚数,缩短元件之间的连线,有效传输信号。SiP可以将微处理器、存储器(如EPROM和DRAM)、FPGA、电阻器、电容和电感器合并在一个容纳多达四或五个芯片的封装中。与传统的IC封装相比,通常最多可节约80%的资源,并将重量降低90%。 通过垂直集成,SiP也可以缩短互连距离。这样可以缩短信号延迟时间、降低噪音并减少电容效应,使信号速度更快。功率消耗也较低。 1.3节约成本 系统级封装减少了产品封装层次和工序,因此相应地降低了生产制造成本,提高了产品可靠性。虽然就单一产品而言封装制造成本相对较高。但从产业链整合、运营及产品销售的角度来看,SiP产品开发时间大幅缩短,而且通过封装产品的高度整合可减少印刷电路板尺寸及层数,降低整体材料成本,有效减少终端产品的制造和运行成本,提高了生产效率 1.4能实现多功能集成 系统级封装可以集成不同工艺类型的芯片,如模拟、数字和RF等功能芯片,很容易地在单一封装结构内实现混合信号的集成化。 1.5满足产品需求 第一,要求产品在精致的封装中具有更高的性能、更长的电池寿命和不断提高的存储器密度;第二要求降低成本并简化产品 因SiP是将相关电路以封装体完整包覆,因此可增加电路载板的抗化学腐蚀与抗应力(Anti-stress)能力,可提高产品整体可靠性,对产品寿命亦能提升。 SiP设计具有良好的电磁干扰抑制效果,对系统整合客户而言可减少抗电磁干扰方面的工作 2劣势 2.1晶片薄化

三维封装的现在和未来 微电子学一班随着便携式电子系统复杂性的增加, 对VLSI集成电路用的低功率、轻型及小型封装的生产技术提出了越来越高的要求。同样, 许多航空和军事应用也正在朝该方向发展。为满足这些要求, 现在产生了许多新的3- D 封装技术, 或是将裸芯片, 或是将MCM 沿z 轴叠层在一起, 这样, 在小型化方面就取得了极大的改进同时, 由于z 平面技术总互连长度更短, 会产生寄生电容, 因而系统功耗可降低约30%。 三维(3D)封装技术的分类 三维封装的结构类型有3种: 一是埋置型3D封装,即在多层基板底层埋置IC 芯片,顶层组装IC芯片,其间高密度互连; 二是有源基板型3D封装,即在Si或GaAs 衬底上制造多层布线和多种集成电路,顶层组装模拟IC芯片和其它元器件; 三是叠层型3D封装,即把多个裸芯片或封装好芯片或多芯片模块( MCM)沿Z轴叠装、互连,组装成3D封装结构。由于叠层型3D封装适用范围广,并且工艺相对简单,成本相对较低,已引起国外多家公司的注意,如Actel , IBM, Harris, Mo to rola 等著名公司都在积极开展叠层型3D封装的研究工作。下面将重点介绍叠层型3D封装。 1.埋置型3D 结构 这是一种实施最早( 八十年代) , 也是最为灵活方便的3D, 同时又可作为后布线的芯片互连技术, 能大大减少焊点, 提高电子产品可靠性的电子封装技术。埋置型3D 结构又可分为基板开槽埋置型和多层布线介质埋置型, 如图1所

示。在混合集成电路( H IC) 多层布线中埋置R、C 元件已经普遍, 而埋置IC芯片和R、C 后的布线顶层仍可贴装各类IC 芯片, 就可构成更高组装密度的3D-MCM 结构。由于布线密度及功率密度都很高, 所以这种3D-MCM 所使用的基板多为高导热的Si 基板、AIN 基板或金属基板。 上图是AIN 基板多层布线介质埋置IC 的3D-MCM 结构, 制作方法与常规多层布线技术相同。 2.有源基板型3D 结构 自从IC 出现以来, 人们就试图将一个复杂的电子整机甚至电子系统都集成在一大片Si 圆片内, 成为圆片规模IC( WSI) 。今天的VLSI、ASIC( 专用集成电路) 已部分地实现了WSI, 如CPU、DSP、摄录一体机等, 就是一个个小系统。有些芯片的尺寸达到近30mm 见方, 能集成数千万个器件。这种有源Si基板再多层布线, 上面再安装多芯片, 就可形成有源基板型的3D-MCM, 从而以立体封装形式达到了WSI 所能实现的功能。无论是一个大尺寸的复杂IC 作为Si 基板还是

西安电子科技大学 硕士研究生课程考试试卷 科目集成电路封装与测试 题目硅通孔(TSV)工艺技术 学号 1511122657 班级 111504 姓名马会会 任课教师包军林 分 数 评卷人 签名 注意事项 1.考试舞弊者做勒令退学或开除学籍 2.用铅笔答题一律无效(作图除外) 3.试题随试卷一起交回 硅通孔TSV工艺技术

1511122657 马会会 摘要:本文主要介绍近几年封装技术的快速发展及发展趋势。简单介绍了TSV技术的发展前景及其优势。详细介绍了硅通孔工艺以及其关键技术。并针对TSV 中通孔的形成,综述了国内外研究进展,提出了干法刻蚀、湿法刻蚀、激光钻孔和光辅助电化学刻蚀法(PAECE)等四种TSV通孔的加工方法、并对各种方法进行了比较,提出了各种方法的适用范围。 关键词:后摩尔时代;封装技术;TSV;硅通孔 Abstract:This paper mainly introduces the rapid development and development trend of packaging technology in recent years.In the brief introduction of several vertical packaging technology, the paper focuses on the development of TSV technology and its advantages. The technology of Si - through hole and its key technologies are introduced in detail. In this paper, the research progress of TSV was summarized, and the method of dry etching, wet etching, laser drilling and photo assisted electrochemical etching (PAECE) was proposed, and four kinds of TSV through hole were compared. Keywords:Post Moore era; packaging technology; TSV; silicon through hole 引言 集成电路技术在过去的几十年里的到了迅速的发展。集成电路的速度和集成度得到了很大的提高并且一直遵循摩尔定律不断发展,即单位集成电路面积上可容纳的晶体管数目大约每隔18个月可以增加一倍。然而,当晶体管尺寸减小到几十纳米级后,想再通过减小晶体管尺寸来提升集成电路的性能已经变得非常困难,要想推动集成电路行业继续遵循摩尔定律发展就不得不寻求新的方法。 自从集成电路发明以来,芯片已无可辩驳地成为电子电路集成的最终形式。从那以后,集成度增加的速度就按照摩尔定律的预测稳步前进。摩尔定律的预测在未来若干年依然有效的观点目前仍然被普遍接受,然而,一个同样被广泛认同的观点是,物理定律将使摩尔定律最初描述的发展趋势停止。在这种情况下,电子电路技术和点路设计的概念将进入一个新的发展阶段,互连线将在重要性和价值方面得到提升。在被称作“超越摩尔定律”的新兴范式下,无论是物理上还是使用上,在z轴方向组装都变得越来越重要。目前在电子封装业中第三维正在被广泛关注,成为封装技术的主导。 图1 封装的技术演变与长期发展图

课题:三维高密度组装技术的发展 及新成果 院(系) 专业: 学生姓名: 学号:

三维高密度组装技术的发展及新成果 XXX (桂林电子科技大学机电工程学院,广西桂林 541004) 摘要:三维高密度封装技术是一种可实现电子产品小尺寸、轻重量、低功耗、高性能和低成本的先进封装技术,该技术已广泛用于手机、数码相机、MP4及其他的便携式无线产品, 是微电子学领域的一项重大变革技术,对现代化的计算机、自动化、通讯业等领域将产生重大影响。随着人们对手持式电子设备不断提出的微型化、多功能化和集成化的需求,转化为采用三维(3D)方式装配印制电路板(PCB)强大推动力。为满足电子产品轻、薄、小以及系统集成的需求,各种新的封装结构正在不断推出. 三维封装(3D packages)愈来愈受到重视。本文概述了三维高密度组装思想在芯片封装领域的应用。 关键词:三维组装技术;3D-MCM;PIP;PoP;TSV;高密度封装;芯片堆叠 Three-dimensional high-density assembly technology development and new achievements XXX (School of Mechanical and Electrical Engineering of the Guilin University of Electronic Technology , Guilin, Guangxi 541004,China) Abstract: Three-dimensional high-density packaging technology is an enabling electronic products small size, light weight, low power consumption, high performance and low cost advanced packaging technology, which has been widely used in mobile phones, digital cameras, MP4 and other portable wireless products, is a major field of microelectronics revolution technology, the modern computer, automation, communications and other areas will have a significant impact. As people continue to raise handheld electronic device miniaturization, multi-functional and integration requirements, into a three-dimensional (3D) mode assembled printed circuit board (PCB) a strong force. Electronic products to meet the light, thin, small, and system integration requirements, a variety of new packaging structure is being constantly introduced. Dimensional package (3D packages) more and more attention. This article outlines the three-dimensional high-density chip package assembly of thought in the field of application. Key words: three-dimensional assembly technology, 3D-MCM, PIP, PoP, TSV;high-density packaging, chip stacking 1.三维高密度电子组装发展概述 在某种意义上,电子学近几十年的历史可以看作是逐渐小型化的历史,推动电子产品朝小型化过渡的主要动力是元器件和集成电路IC的微型化。所谓封装是指将半导体集成电路芯片可靠地安装到一定的外壳上,封装用的外壳不仅起着安放、固定、密封、保护芯片和增强电热性能的作用,而且还是沟通芯片内部世界与外部电路的桥梁,即芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印制板上的导线与其他器件建立连接。因此,封装对集成电路和整个电路系统都起着重要的作用。 随着手机、PDA 、数码相机、MP4等移动消费型电子产品对于功能集成、大存储空间、高可靠性及小型化等封装的要求程度越来越高,及宇航、卫星、计算机及通信等军事和民用领域对提高组装密度、减轻重量、减小体积、高性能和高可靠性等方面的迫切需求,加之3D-MCM在满足上述要求方面具有的独特优点,因此在MCM(多芯片组件)X 、Y平面内的二维封装的基础上,沿Z方向堆叠的更高密度的三维封装技术近年来得到了迅速发展。新的三维封装技术形式,或是将裸芯片,或是将封装体(如MCM)沿z 轴叠层

微波毫米波系统级封装中键合线建模 孙一超胡静钱学军 摘要:在系统级封装中,存在微波及高速电路,如果没有考虑互连线对电路性能的影响,可能会导致最终的电路不能满足设计要求。本文利用3维电磁场仿真软件HFSS分析单根键合线的电磁特性,建立单根键合线的电路模型,并研究不同参数下键合线在电磁特性方面的区别。 关键词:键合线HFSS 等效电路 Bond-Wire Modeling in Microwave Millimeter Wave System-Level Package Abstract: Without considering the influence of the interconnection line on the electric circuit performance in system-level package, the final electric circuit may not to be able to satisfy the design requirements for the existence of microwave and high-speed circuit. In this paper,the 3D electromagnetic analysis software HFSS was used to analyse the simple and the circuit model was build for the microwave Characteristics of the bond-wire in with different parameters. Keyword: Bond-Wire HFSS Equivalent Circuit 1.引言 随着科技水平的不断提高,无论是军用还是民用通信系统的功能都变得日益强大,随之电路结构也变得日益复杂,电路的规模、体积也不断增大。通常,电路的体积庞大会限制其应用,为此,自上世纪90年代以来,能将微处理器、存