2-4分频及任意分频(N)电路

分频系数较大的2N分频电路需要采用标准计数器来实现,此处的方法是直接将计数器的相应位赋给分频电路的输出信号即可实现分频功能。采用这个方法的好处是:一是不需要定义中间信号,设计简单,节约资源;二是可以避免毛刺现象的发生,从而避免了逻辑错误产生的可能性。

对JK触发器,J,K都为1时,输出在CP的下降沿翻转。对D触发器,D为1时,输出在CP的上升沿置1;D为0时,输出在CP的上升沿清0。

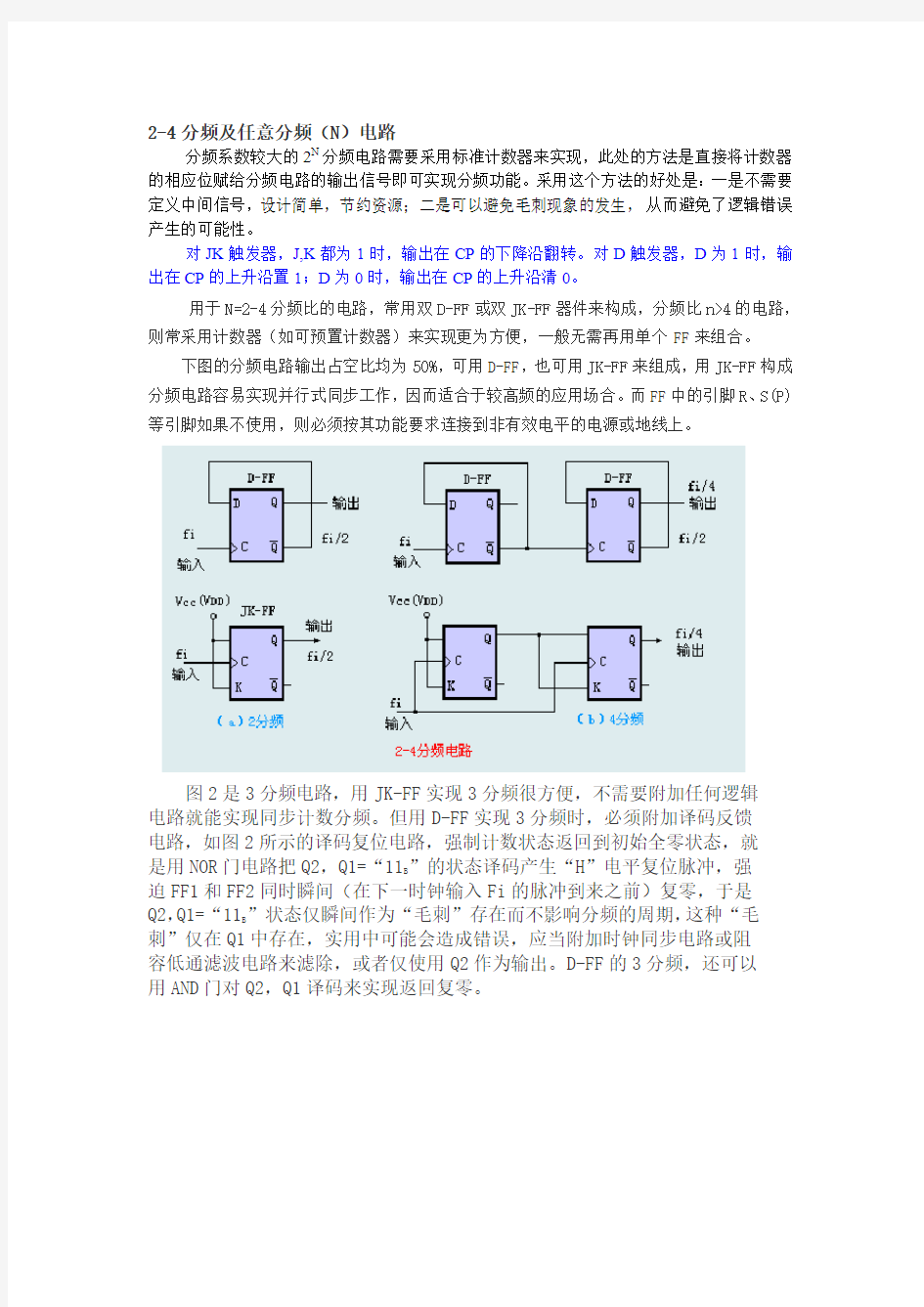

用于N=2-4分频比的电路,常用双D-FF或双JK-FF器件来构成,分频比n>4的电路,则常采用计数器(如可预置计数器)来实现更为方便,一般无需再用单个FF来组合。

下图的分频电路输出占空比均为50%,可用D-FF,也可用JK-FF来组成,用JK-FF构成分频电路容易实现并行式同步工作,因而适合于较高频的应用场合。而FF中的引脚R、S(P)等引脚如果不使用,则必须按其功能要求连接到非有效电平的电源或地线上。

图2是3分频电路,用JK-FF实现3分频很方便,不需要附加任何逻辑

电路就能实现同步计数分频。但用D-FF实现3分频时,必须附加译码反馈

电路,如图2所示的译码复位电路,强制计数状态返回到初始全零状态,就

是用NOR门电路把Q2,Q1=“11

”的状态译码产生“H”电平复位脉冲,强

B

迫FF1和FF2同时瞬间(在下一时钟输入Fi的脉冲到来之前)复零,于是

Q2,Q1=“11

”状态仅瞬间作为“毛刺”存在而不影响分频的周期,这种“毛

B

刺”仅在Q1中存在,实用中可能会造成错误,应当附加时钟同步电路或阻

容低通滤波电路来滤除,或者仅使用Q2作为输出。D-FF的3分频,还可以

用AND门对Q2,Q1译码来实现返回复零。

图3是可逆、可预置计数器CD4029构成的任意N分频减法计数电路,U/D接“L”电平进行减法计数,B/D接“L”电平按BCD输出码进行计数,

输入进行进位计数,按BCD计数连接可实现0-299低位的Co进位到高位的C

T

分频,按二进制连接(B/D)端连到V

上)可实现0-8192分频,分频比N

DD

值是由并行预置输入端P3-P0所加的数字电平来决定的,可在上述范围内任意设置。

该电路每当各级CD4029均计数到全零状态时,各级的Co=“L”电平,通过3输入NOR门译码就在PE端出现正脉冲(tw宽),将各级预置设定数字(图示123)并行置入内部,再开始新的计数循环,PE端出现的瞬变脉冲就是分频后的输出信号,其周期是计数时钟CLK(即fin)周期的N倍,脉宽tw是由计数器延迟时间和NOR门延时之和来决定的,用CD4029和CD4025(三NOR)情况大约tw=0.9us(V

=5V时),如果需要更宽的脉冲分频输出,

DD

可以使用单稳延时电路如CD4528/4538来作定时展宽。

六分频加法电路的设计 1相关原理分析 1.1计数器 计数器是实现分频电路的基础,计数器包括普通计数器和约翰逊计数器两种,这两种电路均可用于分频电路中。 最普通的计数器莫过于加法(减法)计数器。以3位二进制计数器为例,计数脉冲CP 通过计数器时,每输入一个计数脉冲,计数器的最低位(记为Q0,后面的依次记为Q1、Q2、)翻转一次,Q1、Q2、都以前一级的输出信号作为触发信号。分析这个过程,不难得出输出波形。 图1-1 3位二进制计数器时序图 由上很容易看出Q0 的频率是CP的1/2,即实现了2分频,Q1则实现了4分频,同理Q2实现了8分频。这就是加法计数器实现分频的基本原理。 约翰逊计数器是一种移位寄存器,采用的是把输出的最高位取非,然后反馈送到最低位触发器的输入端。约翰逊计数器在每一个时钟下只有一个输出发生变化。同样以3为二进制为例。假设最初值或复位状态是000,则依次是000、001、011、111、110、100、000这样循环。由各位的输出可以看出,约翰逊计数器最起码能实现2分频。 1.2两种计数器的比较 从以上分析可以看出约翰逊计数器没有充分有效地利用寄存器的所有状态,而且如果

由于噪声引入一个无效状态,如010,则无法恢复到有效循环中去,需要加入错误恢复处理。但其较之加法计数器也有它的好处。同一时刻,加法计数器的输出可能有多位发生变化,因此当使用组合逻辑对输出进行译码时,会导致尖峰脉冲信号。而约翰逊计数器可以避免这个问题。 1.3 计数器的选择 本次训练要求设计的是加法分频电路,选择的是加法计数器。加法计数器实现分频较之约翰逊计数器简单,编程也容易理解一些,对于初学者也较容易上手。在前面已经讲过加法计数器实现2n的分频的方法,现在就不在赘述。 1.4 偶数分频器 如前所述,分频器的基础是计数器,设计分频器的关键在于输出电平翻转的时机。偶数分频最易于实现,要实现占空比为50%的偶数N分频,一般来说有两种方案:一是当计数器计数到N/2-1时,将输出电平进行一次翻转,同时给计数器一个复位信号,如此循环下去;二是当计数器输出为0到N/2-1时,时钟输出为0或1,计数器输出为N/2到N-1时,时钟输出为1或0,当计数器计数到N-1时,复位计数器,如此循环下去。可以根据以上两种方案设计电路和程序。 2 六分频加法电路 2.1 电路的结构设计 前面已经讲到过关于2n分频可以直接通过计数器获得。而对于一些非2的整数次幂的分频,如本次课设的6分频,还需要在基本计数器电路描述中加上复位控制电路。 图2-1 加法分频电路的RTL视图

always@( negedge resetn or posedge clk or negedge clk) begin if (resetn==1'b0) begin counter[2:0]<=3'd0; out_clk<=1'b0; end else begin if (counter[2:0]==3'd5) begin counter[2:0]<=3'd0; end else beign counter[2:0]<= counter[2:0]+1; end

//////////////////////////////////////////////////// if (counter[2:0]==3'd5 || counter[2:0]==3'd2) begin out_clk<=~out_clk; end end end 其仿真结果是正确的 这个逻辑无法综合。存在半导体工艺问题。 2.下面给出一个逻辑图。

逻辑是用器件画出来的,保证不存在物理上的实现问题。 仿真图如下: 也许有人要问,既然仿真都是对的,那么为什么要说实际中是80%工作呢? 看到波形图上的clk1(黄色)上的那些毛刺了么,毛刺并不可怕,但是这个电路工作的基础却是那些毛刺,准确地说,那些毛刺是必须有的,是工作过程的比不可少的部份。这样的电路是否能正常工作就很让人匪夷所思了。 我们能不能让电路的正常功能不依赖于毛刺呢? 小结一下: 以上的思路都是试图在输入的clk上做改造,试图在恰当的地 方取正沿,恰当的地方取反沿。但是要知道,这一定会导致竞争和冒险。虽然逻辑上是可性的,但是实践中却没有那么简单。这个时候,我们需要调整一下思路了:

9.(09贵阳)请在图中用笔画线代替导线,按要求连接电路。要求:⑴开关同时控制两盏电灯;⑵电灯L1、L2并联;⑶电流表测通过两灯的总电流;⑷所画导线不能交叉。 10.根据电路图,以笔线代替导线,把元件对应地连接起来,组成电路。要求做到导线不交 叉、不破线。 11、在图52中添两根导线,使两灯并联,电流表测干路电流 12、在图53电路中补画两根导线,使电键控制两盏灯,且电键闭合后电流表只测量灯L2的 电流。 图52 图53

13. 在图56中补上两根导线,使两灯并联,电键控制两盏灯,电流表只测L 1的电流强度(导线不要交叉) 14. 在图58中将两根未连接的导线接到滑动变阻器上,使得滑片向右移动时,灯变亮。 15.在如图60所示的电路中,有两根导线未连接,请用笔线代替导线补上,补上后要求: 电键闭合后,当滑动变阻器的滑片向右移动时,电流表的读数变小,灯的亮度不变。 16、如图61所示中的电路连线中缺两根导线,请用笔线代替导线补上,且满足当滑动变阻器的滑片向右移动时电流表的读数变大,电压表的读数变小。 17.请根据图中磁感线的方向标出通电螺线管的N 、S 极及电源的正,负极 18. 请依照如图所示的电路图把图的实物图连接成相应的电路 19.用笔画线,将图4中的器材连成电路。(要求:两灯并联,开关控制两盏灯) 图 56

20.如图11所示是小明同学设计的测电阻只的电路图.请根据这个电路图用笔画线代替导线,将图12中的元件连成电路.要求:滑动变阻器的滑片P 向左移动时,电流表的示数变大.(电压表选用0~3V 量程,电流表选用0~0.6A 量程,导线不能交叉 ) 图11 图12 21.小明要研究小灯泡的亮度与流过小灯泡电流的关系,他已连接的部分电路如下图所示,请你用画线代表导线,将电路连接完整,并在方框内画出对应的电路图. 22.按照图7所示的电路图,将图8中各元件连接起来。(用笔画线表示导线,导线不许交叉) 23.请依照如图9所示的电路图把图10的实物图连接成相应的电路。 图 7 图8

电路原理图的绘制方法与步骤 一.电路原理图绘制前的准备工作 1.设计电路原理图的草图 例如要画出图1所示的稳压电源的电路图,首先要画出电路图的草图。 2.电路图有关资料的整理、列表 为了方便快捷地画出电路原理图,首先必须将电路图中所有零件的名称、拟采用的编号、零件的类型以及元件封装进行整理,列出表格,如表1所示。 二、Protel 99 SE 的启动 在Windows 桌面上,将鼠标的指示箭头对准图2所示的Protel 99 SE 图标, 双击鼠标左键,启动Protel 99 SE 。 启动Protel 99 SE 后,屏幕会出现图3所示的界面。 图2 Protel 99 SE 图标 图1 稳压电源电路图

几秒钟后,Protel 99 SE 的启动界面消失,留下了Protel 99 SE 的初始操作界面,如图4所示: 三、进入电路原理图设计环境 1.启动电路原理图编辑器 (1)创建工程设计数据库FirstDesign.ddb : 启动Protel 99 SE 后,打开File 菜单,选择New 命令,则弹出的题目为New Design Database 的对话框,在Design Storage Type 栏内,选择设计数据库的格式为MS Access Database ;在Databass Location 框中指定设计数据库存放的位置为:C :\Design Explorer 99se\\Examples ;在Databass File Name 文本框中输入数据库的名称FirstDesign.ddb 。单击OK 按钮,完成设计数据库的创建。 标题栏 菜单栏 工具条 设计管理面板 设计工作区 图4 Protel 99 SE 的操作界面 图6 图2 Protel 99 SE 的启动界面

分频电路的设计 在数字电路的设计中,我们会经常遇到分频电路,而且分频电路输出信号频率的稳定性、精确度与整个电路的稳定性有着很大的关系。本文就一些常用分频电路作一总结。 一、n2分频 众所周知,2分频是最简单的分频,通常用D触发器用作反相器即可以实现2分频,要 想实现n2分频,最简单的方法就是将2分频电路级联,n级联在一起就构成了n2分频。 我们以n=5为例,用MAX+plus II进行仿真,电路如图1所示,我们得到的波形如图2所示: 图1 图2 由波形我们可以看出,该电路能实现32分频,但由于它采用的是行波时钟,Q4的输出t。n越大,延时就越大。 与CLK之间延时为5 co 改进图1的电路,我们可以采用同步计数来实现32分频,如图2所示,其中5BITcounter 是在MAX+plus II中用生成的5位二进制加法计数器。Q4输出就是32分频的信号,波形如图4所示。

图3 图4 t。保证了系统的同由于图3是采用同步计数器,所以每个输出的延时都一样,都为 co 步运行。 同样的道理,若n增大时,我们只要改变计数器的位数即可。 二、2n分频 在数字电路的设计中,2n分频也是经常遇到的。对于2n分频,我们常采用两级分频的方法,第一级用来n分频,第二级用作2分频,这样做的目的就是保证输出信号有50%的占空比,若对占空比无要求则可任意实现n分频。 以n=25为例,在MAX+plus II中,利用构造一个5bit模为25的加法计数器,电路如图5所示,out即为50分频后的输出,波形如图6所示。 图5

图6 从图6可以看出,out 与输入时钟CLK 之间的延时是2co t =6ns 。 三、M N 2分频 在一些特殊的数字电路中,可能会用到M N 2分频,由于分频是小数,我们不可能对输入 信号精确地分频,只能保证输出信号的平均频率与理想的分频频率相等。我们这里以26/3分频为例来介绍这种分频方法。 分析:26/3分频的实质就是在26个CLK 周期内产生3个周期的输出信号。我们还是采用采用两级分频方法,目的是为了保证占空比为50%,第一级分频倍数为13/3,即13个CLK 周期内产生3个周期的输出信号。这样我们构造一个模13的4bit 加法计数器,利用门电路输出三个周期信号,计数器从0计到3时A 输出1,计到7时B 输出1,计到12时C 输出1,将A 、B 、C 三路信号相或就得到我们想要的波形,电路如图7所示,波形如图8所示。 图7

三分频器的设计 时钟输入端(clkin)首先反向和不反向分别接到两个D触发器的时钟输入端,两个D触发器的输出接到一个二输入或非门的输入端,或非门的输出反馈到前面两个D触发器的D输入端,并且或非门的输出后面接一二分频器,得到占空比为50%的三分频波形。 图1:图形设计 VHDL程序: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity fen3 is port (clkin : in std_logic; --时钟输入 qout1 : buffer std_logic; qout2 : buffer std_logic; qout3 : buffer std_logic; clkout : out std_logic --占空比为1/2的三分频输出 ); end fen3; architecture behave of fen3 is begin qout3<=qout1 nor qout2; process(clkin) begin if clkin'event and clkin='1' then --在上升沿触发 qout1<=qout3; end if;

end process; process(clkin) begin if clkin'event and clkin='0' then --在下降沿触发 qout2<=qout3; end if; end process; process(qout3) variable tem:std_logic; begin if qout3'event and qout3='1' then --二分频tem:=not tem; end if; clkout<=tem; end process; end behave; 图3:仿真结果

装饰材料购销合同 简单电路设计设计大全 1.保密室有两道门,只有当两道门都关上时(关上一道门相当于闭合一个开关),值班室内的指示灯才会发光,表明门都关上了.下图中符合要求的电路是 2.小轿车上大都装有一个指示灯,用它来提醒司机或乘客车门是否关好。四个车门中只要有一个车门没关好(相当于一个开关断开),该指示灯就会发光。下图为小明同学设计的模拟电路图,你认为最符合要求的是 3.中考试卷库大门控制电路的两把钥匙分别有两名工作人员保管,单把钥匙无法打开,如图所示电路中符合要求的是 ”表示)击中乙方的导电服时,电路导通,4.击剑比赛中,当甲方运动员的剑(图中用“S 甲 乙方指示灯亮。下面能反映这种原理的电路是 5.家用电吹风由电动机和电热丝等组成,为了保证电吹风的安全使用,要求:电动机不工作时,电热丝不能发热;电热丝发热和不发热时,电动机都能正常工作。如图所示电路中符合要求的是( )

6.一辆卡车驾驶室内的灯泡,由左右两道门上的开关S l、S2和车内司机右上方的开关S3共同控制。S1和S2分别由左右两道门的开、关来控制:门打开后,S1和S2闭合,门关上后,S l和S2断开。S3是一个单刀三掷开关,根据需要可将其置于三个不同位置。在一个电路中,要求在三个开关的共同控制下,分别具有如下三个功能:(1)无论门开还是关,灯都不亮; (2)打开两道门中的任意一道或两道都打开时,灯就亮,两道门都关上时,灯不亮;(3)无论门开还是关,灯都亮。如图所示的四幅图中,符合上述要求的电路是 A.图甲 B.图乙 C.图丙 D.图丁 7.教室里投影仪的光源是强光灯泡,发光时必须用风扇给予降温。为了保证灯泡不被烧坏,要求:带动风扇的电动机启动后,灯泡才能发光;风扇不转,灯泡不能发光。则在如图3所示的四个电路图中符合要求的是 ( ) 8.一般家用电吹风机都有冷热两挡,带扇叶的电动机产生风,电阻R产生热。冷热风能方便转换,下面图3中能正确反应电吹风机特点的电路图是 ( ) 9.飞机黑匣子的电路等效为两部分。一部分为信号发射电路,可用等效电阻R1表示,用开关S1控制,30天后自动断开,R1停止工作。另一部分为信息存储电路,可用等效电阻R2表示,用开关S2控制,

实验六 Verilog设计分频器/计数器电路 一、实验目的 1、进一步掌握最基本时序电路的实现方法; 2、学习分频器/计数器时序电路程序的编写方法; 3、进一步学习同步和异步时序电路程序的编写方法。 二、实验内容 1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为4个clock周期的低电平,4个clock周期的高电平),文件命名为fenpinqi10.v。 2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK(上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为couter10.v。 3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为couter8.v。 4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk上升沿有效,文件命名为mcout5.v。 5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效,异步清零;Q[3..0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端。 三、实验步骤 实验一:分频器 1、建立工程

单位:嵌入式系统实验室 姓名:汤晓东 内容:简单分频时序电路的设计(三分频) 时间:2010-7-7 3.练习三 模块源代码: //-------------------文件名div3.v---------------------------------- module div3(clk_in,clk_out,reset ); input clk_in,reset; output clk_out; wire clk_out; integer n1,n2; reg clk1,clk2; always @(posedge clk_in or negedge reset) //检测clk_in的上升沿 begin if (!reset) begin n1=0; clk1<=1'b0; //clk1是对clk_in的三分频 end // 但是占空比为1/3 else if (n1==2) begin n1=0; clk1<=1'b1; end else begin n1=n1+1; clk1<=1'b0; end end always @(negedge clk_in or negedge reset) //检测clk_in的下降沿 begin if (!reset) begin n2=0; clk2<=1'b0; //clk2也是对clk_in的三分频 end else if (n2==2) //占空比为1/3,但是与clk1相差begin //半个时钟周期 n2=0; clk2<=1'b1; end else begin n2=n2+1; clk2<=1'b0; end

家庭照明电路设计 姓名:杨光辉 学号:2011173124 班级:2011级机电一体化 呼伦贝尔学院工程技术学院

一、设计目的 二、家庭照明电路组成部分的功能和安装要求三、设计的总体思路 四、电路布线施工图及及电路原理图 1. 阳台灯的自动控制系统 2.电机控制电路系统 3. 客厅灯电路系统 4.自来水开关控制系统 五、安装用电路元器件以及预算六、施工要求 七、设计总结

家庭照明电路设计 一、设计目的 1、理解家庭电路的基本原理,巩固和加深在电路课程中所学的理论知识和实践技能。 2、学会查阅相关手册和资料,了解照明电灯的相关知识,培养独立分析与解决问题的能力。 3、掌握常用电子电路的一般设计方法,学会使用常用电子元器件,正确开绘制电路图。 4、掌握平面图的正规设计与应用。 5、认真写好总结报告,培养严谨的作风与科学态度,提高我们从实践中提高的能力。 二、家庭照明电路组成部分的功能和安装要求 家庭照明电路组成部分主要包括电能表、闸刀、空气开关、导1、电能表线(包括火线和零线)、熔断器、电灯开关、电灯和插座这几部分。电能表的作用是测量电路消耗了多少电能,计量每单位消耗的电能值,也就是度或者千瓦时,电能表常见的有感应式机械电度表和电子式电能表。 感应式机械电度表其工作原理为:根据电磁感应原理,电表通电时,在电流线圈和电压线圈产生电磁场,在铝盘上形成转动力矩,通过传动齿轮带动计度器

计数,电流电压越大,转矩越大,计数越快,用电越多。铝盘的转动力矩与负载的有功功率成正比。 电子式电度表是利用电子电路/芯片来测量电能;用分压电阻或电压互感器将电压信号变成可用于电子测量的小信号,用分流器或电流互感器将电流信号变成可用于电子测量的小信号,利用专用的电能测量芯片将变换好的电压、电流信号进行模拟或数字乘法,并对电能进行累计,然后输出频率与电能成正比的脉冲信号;脉冲信号驱动步进马达带动机械计度器显示,或送微计算机处理后进行数码显示。在安装电能表时,进户电源线在允许的范围内线径越大越好,有条件建议使用单相电缆。必须安装在户外。进户电源线必须套绝缘管。下列场合不允许安装电能表,在易燃易爆的危险场所;有腐蚀性气体或高温的危险场所;有磁场影响及多灰尘的地方。 2、闸刀 闸刀开关是一种手动配电电器。主要用来隔离电源或手动接通与断开交直流电路,也可用于不频繁的接通与分断额定电流以下的负载,如小型电动机、电炉等。闸刀刀开关是最经济但技术指标偏低的一种刀开关。闸刀开关也称开启式负荷开关。使用闸刀开关时应注意要将它垂直的安装在控制屏或开关扳上,不可随意搁置;进线座应在上方,接线时不能把它与出线座搞反,否则在更换熔丝时将会发生触电事故;更换熔丝必须先拉开闸刀,并换上与原用熔丝规格相同的新熔丝,同时还要防止新熔丝受到机械损伤;若胶盖和瓷底座损坏或胶盖失落,闸刀开关就不可再使用,以防止安全事故。 3、漏电开关 漏电保护主要作用是解决漏电问题(相线流出多少电流,中性线就要回来多少电流,一旦有电流缺失,比如人体触电,电流通过人体流到地上的时候,一般超过30毫安,漏电保护器就会工作,切断电源,从而杜绝了电流对人体伤害),但是一般专用的漏电保护开关是不起过载保护用的(现在大多带过载保护)。当电流超过一定的电流的时候自身会发热,(利用双金属片受热弯曲的道理)导致

武汉理工大学《微机原理与接口技术》课程设计报告书

学

号:

0121105830129

课 程 设 计

题 学 专 班 姓

目 院 业 级 名

分频信号发生器的分析与设计 自动化学院 电气工程及自动化 电气 1107 班 成涛 陈静 教授

指导教师

2014 年

01 月

09 日

武汉理工大学《微机原理与接口技术》课程设计报告书

课程设计任务书

学生姓名: 指导教师: 题 目: 成涛 专业班级: 电气 1107 班 陈静 教授 工作单位: 自动化学院 分频信号发生器的分析与设计

要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰 写等具体要求) 1. 设:有一输入方波信号 f0(<1MHz) 。要求输出信号:f1=f0/N,N 通过键盘 输入。 2. 画出简要的硬件原理图,编写程序。 3. 撰写课程设计说明书。 内容包括:摘要、 目录、 正文、 参考文献、 附录 (程 序清单) 。正文部分包括:设计任务及要求、方案比较及论证、软件设计说明(软 件思想,流程,源程序设计及说明等) 、程序调试说明和结果分析、课程设计收 获及心得体会。

时间安排: 12 月 26 日----- 12 月 28 日 查阅资料及方案设计 12 月 29 日----- 01 月 0 2 日 编程 01 月 03 日-----0 1 月 07 日 调试程序 01 月 08 日----- 01 月 09 日 撰写课程设计报告

指导教师签名: 系主任(或责任教师)签名:

年 年

月 月

日 日

模拟电子技术课程设计报告 题目名称:直流稳压电源电路设计姓名: 学号: 班级: 指导教师: 成绩:

目录 1课程设计任务和要求 2 2方案设计 2 3单元电路设计与参数计算 4 4总原理图及元器件清单9 5安装与调试 11 6性能测试与分析12 7结论与心得14 8参考文献 14

课程设计题目: 直流稳压电源电路设计 一、课程设计任务和要求: 1)用桥式整流电容滤波集成稳压块电路设计固定的正负直流电源(±12V)。 2)输出可调直流电压,范围:1.5∽15V; 3)输出电流:IOm≥1500mA;(要有电流扩展功能) 4)稳压系数Sr≤0.05;具有过流保护功能。 二、方案设计: 稳压电源由电源变压器、整流电路、滤波电路和稳压电路四部分组成,如下图1所示,其整流与稳压过程的电压输出波形如图2所示。 图1稳压电源的组成框图 图二整流与稳压过程波形图 电网供电电压交流220V(有效值)50Hz,要获得低压直流输出,首先必须采用电源变压器将电网电压降低获得所需要交流电压。降压后的交流电压,通过整流电路变成单向直流电,但其幅度变化大(即脉动大)。脉动大的直流电压须经过滤波电路变成平滑,脉动小的直流电,即将交流成份滤掉,保留其直流成份。滤波后的直流电压,再通过稳压电路稳压,便可得到基本不受外界影响的稳定直流电压输出,供给负载RL。

方案一、单相半波整流电路 半波单相整流电路简单,电路及其电压输出波形分别如图3、图4所示,使用元件少,它只对交流电的一半波形整流,其输出波形只利用了交流电的一半波形则整流效率不高,且输出波形脉动大,其值为:S= =≈1.57,直流成分小,= ≈0.45,变压器利用率低。 图3 单相半波整流电路 图 4 单相半波整流电路电压输出波形图 方案二、单相全波整流电路 使用的整流器件是半波电路的两倍,整流电压脉动较小,是半波的一半,无滤波电路时的输出电压=0.9,变压器的利用率比半波电路的高,整流器件所承受的反向电压要求较高。 方案三、单相桥式整流电路 单相桥式整流电路使用的整流器件较多,但其实现了全波整流电路,它将的负半周也利用起来,所以在变压器副边电压有效值相同的情况下,输出电压的平均值是半波整流电路的两倍,且如果负载也相同的情况下,输出电流的平均值也是半波整流电路的两倍,且其与半波整流电路相比,在相同的变压器副边电压下,对二极管的参数要求一样,还具有输出电压高、变压器利用率高、脉动小等优点。所以综合三种方案的优缺点决定用方案三。

实验六V e r i l o g设计分频器/计数器电路 一、实验目的 1、进一步掌握最基本时序电路的实现方法; 2、学习分频器/计数器时序电路程序的编写方法; 3、进一步学习同步和异步时序电路程序的编写方法。 二、实验内容 1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为4个clock周期的低电平,4个clock 周期的高电平),文件命名为。 2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK (上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为。 3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN 为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为。 4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk 上升沿有效,文件命名为。 5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是

时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR 是复位输入端,高电平有效,异步清零;Q[3..0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端。 三、实验步骤 实验一:分频器 1、建立工程 2、创建Verilog HDL文件 3、输入10分频器程序代码并保存 4、进行综合编译 5、新建波形文件 6、导入引脚 7、设置信号源并保存 8、生成网表 9、功能仿真 10、仿真结果分析 由仿真结果可以看出clockout输出5个clock周期的低电平和5个clock 的高电平达到10分频的效果,设计正确。 实验二:十进制加法计数器(异步清零) 1、建立工程 2、创建Verilog HDL文件 3、输入加法计数器代码并保存 4、进行综合编译 5、新建波形文件 6、导入引脚 7、设置信号源并保存 8、生成网表 9、功能仿真 10、仿真结果分析

初中物理电学电路图 大全

初中物理电学电路图大全2013.10.14

9.请在图中用笔画线代替导线,按要求连接电路。要求:⑴开关同时控制两盏电灯;⑵电灯L1、L2并联;⑶电流表测通过两灯的总电流;⑷所画导线不能交叉。 10.根据电路图,以笔线代替导线,把元件对应地连接起来,组成电路。要求做到导线不交叉、不破线。 11、在图11中添两根导线,使两灯并联,电流表测干路电流 12、在图12电路中补画两根导线,使电键控制两盏灯,且电键闭合后电流表只测量灯L2的电流。

图11 图12 13.在图13中补上两根导线,使两灯并联,电键控制两盏灯,电流表只测L1的电流强度(导线不要交叉) 14.在图14中将两根未连接的导线接到滑动变阻器上,使得滑片向右移动时,灯变亮。 13 15.在如图15所示的电路中,有两根导线未连接,请用笔线代替导线补上,补上后要求: 电键闭合后,当滑动变阻器的滑片向右移动时,电流表的读数变小,灯的亮度不变。 16、如图16所示中的电路连线中缺两根导线,请用笔线代替导线补上,且满足当滑动变阻器的滑片向右移动时电流表的读数变大,电压表的读数变小。 15 16

17. 请根据图中磁感线的方向标出通电螺线管的N 、S极及电源的正,负极 18. 请依照如图所示的电路图把图的实物图连接成相应的电路 19.用笔画线,将图4中的器材连成电路。(要求:两灯并联,开关控制两盏灯) 20.如图11所示是小明同学设计的测电阻只的电路图.请根据这个电路图用 笔画线代替导线,将图12中的元件连成电路.要求:滑动变阻器的滑片P 向左移动时,电流表的示数变大.(电压表选用0~3V量程,电流表选用0~0.6A量程,导线不能交叉)

三分频扬声器系统分频器电感的精确设计 1 引言 扬声器系统的分频器分为前级分频和功率分频2类。前级分频是前级电路中由电子元件产生的分频,再由各自的功放分别驱动高﹑中﹑低音扬声器系统,如图(1a)所示,属于小信号有源分频。而功率分频则是由电感、电容、电阻元件构成的位于功放与扬声器之间的无源分频电路,如图(1b)所示。 采用功率分频的扬声器系统结构简单、成本低,而且又能获得很高的放音质量,因而在现代高保真放音系统中应用最为普遍。其性能的好坏与扬声器的各项指标以及分频电路、电感元件的性能、精度有密不可分的关系,精确计算电感参数便是成功的关键。 2 对分频器电路、元件的要求 (1)电路中电感元件直流电阻、电感值误差越小越好。而且为使频响曲线平坦最好使用空心电感。(2)电路中电容元件损耗尽可能小。最好使用音频专用金属化聚丙烯电容。 (3)使各扬声器单元分配到较平坦的信号功率,且起到保护高频扬声器的作用。 (4)各频道分频组合传输功率特性应满足图2所示特性曲线的要求(P0为最大值,P1为对应分频点f1、f2的值)。分频点处的功率与功率最大值之间幅度应满足P1(=0.3~0.5)P0的范围。 (5)整个频段内损耗平坦,基本不出现“高峰”和“深谷”。 3 分频电感电容参数值的计算

下面以三分频分频器为例说明其参数的计算,如图3所示。

1)计算分频电感L1,L2,L3,L4和分频电容C1,C2,C3,C4。 为了得到理想的频谱特性曲线,理论计算时可取:C1=C4,C3=C2,L1=L3,L4=L2,分频点频率为f1,(f2见图2),则分频点ω1=2πf0,ω2=2πf2。并设想高、中、低扬声器阻抗均相同为RL。每倍频程衰减12 dB。 2)实验修正C1,C2,C3,C4,L1,L2,L3,L4的值 为精确起见,可用实验方法稍微调整C1,C2,C3,C4,L1,L2,L3,L4的值,以满足设计曲线﹙见图2﹚的要求。即通过实验描绘频响曲线,从而得到C1,C2,C3,C4,L1,L2,L3,L4的最佳值。如果没有实验条件,这一步也可不做。求出电容电感的值后就可计算电感值了。 4 最佳结构电感的作用 4.1最佳结构电感的提出 空心分频电感(简称电感)的基本参数是电感量和直流电阻。一般来说,电感量不准会导致分频点偏离设计要求并可能影响扬声器系统的频响,大家都比较重视。然而其直流电阻不宜过大,否则会对音质产生影响。通常人们对此电阻在电路中的影响及其定量要求不甚了解,因此未引起足够重视,对此特作以下简要分析。 以图3的分频网络为例,由于低音单元的分频电感L2与负载R(L低音单元额定阻抗)相串联,因此若L2的阻抗过大,功放输出功率在其上的损耗将增大。同时,功放内阻对低音单元的阻尼作用也将大大减弱。前者影响功放的有效输出功率,后者对音质的影响却无可挽回。由于分频网络中L2的电感量最大,且随分频点的降低而增大,所以L2的直流电阻的影响相当突出。 至于高音单元的分频电感L1,因它未与负载串联,就不存在L2那样的功耗和阻尼问题。但是仍希望其阻抗尽可能小些。因为它与负载并联,起着旁路来自C1的残余低音频成分的作用。若阻值过大,就会影响高音分频网络对低音频的衰减陡度。

集成电路版图设计笔试面试大全 1. calibre语句 2. 对电路是否了解。似乎这个非常关心。 3. 使用的工具。 , 熟练应用UNIX操作系统和L_edit,Calibre, Cadence, Virtuoso, Dracula 拽可乐(DIVA),等软件进行IC版图 绘制和DRC,LVS,ERC等后端验证 4. 做过哪些模块 其中主要负责的有Amplifier,Comparator,CPM,Bandgap,Accurate reference,Oscillator,Integrated Power MOS,LDO blocks 和Pad,ESD cells以及top的整体布局连接 5. 是否用过双阱工艺。 工艺流程见版图资料 在高阻衬底上同时形成较高的杂质浓度的P阱和N阱,NMOS、PMOS分别做在这两个阱中,这样可以独立调节两种沟道MOS管的参数,使CMOS电路达到最优特性,且两种器件间距离也因采用独立的阱而减小,以适合于高密度集成,但是工艺较复杂。 制作MOS管时,若采用离子注入,需要淀积Si3N4,SiO2不能阻挡离子注入,进行调沟或调节开启电压时,都可以用SiO2层进行注入。 双阱CMOS采用原始材料是在P+衬底(低电阻率)上外延一层轻掺杂的外延层P-(高电阻率)防止latch-up效应(因为低电阻率的衬底可以收集衬底电流)。 N阱、P阱之间无space。

6. 你认为如何能做好一个版图,或者做一个好版图需要注意些什么需要很仔细的回答~答:一,对于任何成功的模拟版图设计来说,都必须仔细地注意版图设计的floorplan,一般floorplan 由设计和应用工程师给出,但也应该考虑到版图工程师的布线问题,加以讨论调整。总体原则是 模拟电路应该以模拟信号对噪声的敏感度来分类。例如,低电平信号节点或高阻抗节点,它们与输入信号典型相关,因此认为它们对噪声的敏感度很高。这些敏感信号应被紧密地屏蔽保护起来,尤其是与数字输出缓冲器隔离。高摆幅的模拟电路,例如比较器和输出缓冲放大器应放置在敏感模拟电路和数字电路之间。数字电路应以速度和功能来分类。显而易见,因为数字输出缓冲器通常在高速时驱动电容负载,所以应使它离敏感模拟信号最远。其次,速度较低的逻辑电路位于敏感模拟电路和缓冲输出之间。注意到敏感模拟电路是尽可能远离数字缓冲输出,并且最不敏感的模拟电路与噪声最小的数字电路邻近。 芯片布局时具体需考虑的问题,如在进行系统整体版图布局时,要充分考虑模块之间的走线,避免时钟信号线对单元以及内部信号的干扰。模块间摆放时要配合压焊点的分布,另外对时钟布线要充分考虑时延,不同的时钟信号布线应尽量一致,以保证时钟之间的同步性问题。而信号的走线要完全对称以克服外界干扰。 二(电源线和地线的布局问题

50%占空比三分频器的设计方法(原创) 浏览次数:1037 添加时间:2006-04-17 20:47:01 本文主要介绍了50%占空比三分频器的三种设计方法,并给出了图形设计、VHDL设计、编译结果和仿真结果。设计中采用EPM7064AETC44-7 CPLD,在QUARTUSⅡ4.2软件平台上进行。 方法一: 时钟输入端(clkin)首先反向和不反向分别接到两个D触发器的时钟输入端,两个D触发器的输出接到一个二输入或非门的输入端,或非门的输出反馈到前面两个D触发器的D输入端,并且或非门的输出后面接一二分频器,得到占空比为50%的三分频波形。 图1:图形设计 VHDL程序: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity fen3 is

port (clkin : in std_logic; --时钟输入 qout1 : buffer std_logic; qout2 : buffer std_logic; qout3 : buffer std_logic; clkout : out std_logic --占空比为1/2的三分频输出); end fen3; architecture behave of fen3 is begin qout3<=qout1 nor qout2; process(clkin) begin if clkin'event and clkin='1' then --在上升沿触发qout1<=qout3; end if; end process; process(clkin) begin if clkin'event and clkin='0' then --在下降沿触发

●实验名称:利用VerilogHDL设计一个模10加法计数器和一个时钟20分频电路 ●实验目的: 1.熟悉用可编程器件实现基本时序逻辑电路的方法。 2.了解计数器的Verilog描述方法,以及偶数分频的思路与原理。 ●预习要求: 1.回顾数字电路中加法计数器的相关知识。 ●实验说明: 1.用MAX+plus II软件开发PLD器件有两种设计输入方式:原理图输入和HDL语言 输入方式,或者将两者结合起来,一部分电路采用原理图,另一部分采用HDL语 言。 2.加法计数器表示随着时钟脉冲的输入,计数器从0开始正向计数,直到计满规定的 模值后归零,然后依次循环计数。模10计数器表示,计数器从0000~1001循环计 数。 3.时钟分频电路的功能是,对输入的时钟频率进行偶数倍的降频(倍增其周期),20 分频意味着分频后产生的新时钟周期是输入时钟的20倍(频率降为原频率1/20)。 ●实验内容与步骤: 1.新建一个属于自己的工程目录。 2.用VerilogHDL语言方式编写一个模10加法计数器cnt_10。 3.对此计数器模块进行编译和仿真。 4.用VerilogHDL语言方式编写一个20分频模块fenpin_20,对输入时钟进行20分频 处理。 5.对此分频电路进行仿真。 ●实验报告要求: 1.将自己绘制的电路图或者编写的VerilogHDL代码,截图或者复制到实验报告中。 2.将代码关键位置写上相应注释(可用中文)。 3.对仿真波形截图,贴到实验报告中。 ●实验图表与数据: 1. 模10加法计数器cnt_10的V erilog代码:

2. 模10加法计数器cnt_10的仿真波形: 3. 10分频模块fenpin_10的Verilog代码: 4. 10分频模块fenpin_10的仿真波形:

上海电力学院VLSI原理和设计报告 题目:三分频器 院系:计算机与信息工程学院 专业:电子科学与技术 年级:2008141班 姓名:王沁学号:20082617 指导老师:赵倩

三分频器 一、实验目的: 1、完成三分频器功能块的行为和结构描述,以及测试程序的编写。 2、熟练掌握VI编辑器,并用VCS调试验证设计程序的正确性。 二、实验要求: 用VI编辑器完成三分频器电路的源程序、测试程序的编写,并用VCS 仿真验证设计的正确性。 三、实验内容和步骤 程序: module div3(clk,clk_3); input clk; output clk_3; reg [1:0] countp; reg [1:0] countn; reg clk_3p; reg clk_3n; always@(posedge clk) begin if(countp<=2'd1) begin clk_3p<=1'b1; countp<=countp+2'd1; end else if(countp==2'd2) begin clk_3p<=1'b0; countp<=2'd0; end end

always@(negedge clk) begin if(countn<=2'd1) begin clk_3n<=1'b1; countn<=countn+2'd1; end else if(countn==2'd2) begin clk_3n<=1'b0; countn<=2'd0; end end assign clk_3=(clk_3p&&clk_3n)?1'b1:1'b0; endmodule 验证结果正确。 四、实验总结 经过这次实验,我了解了源代码以及测试代码的识别,并且通过VCS仿真可以测试出结果出来,检验其准确性,对三分频器也有了更深的了解。实验过程中遇到了一些问题,但经过老师的知道还是完成了。

电路图形大全一、图形

电位器 表示符号:VR,RP,W 可调电阻 表示符号:VR,RP,W 电位器 表示符号:VR,RP,W 三脚消磁电阻表示符号:RT 二脚消磁电阻 表示符号:RT 压敏电阻 表示符号:RZ,VAR 光敏电阻CDS 电容(有极性电容) 表示符号: 电容(有极性电容) 表示符号:C 电容(无极性电容)表示符号:C 四端光电光电耦合器 表示符号:IC,N 六端光电光电耦合器 表示符号:IC,N 场效应管增强型N-MOS 电阻电阻器或固定电阻表 示符号:R 可调电阻 表示符号:VR,RP,W 热敏电阻 表示符号:RT 可调电容 表示符号:C 单向可控硅(晶闸 管) 双向可控硅(晶闸管) 双向可控硅(晶闸管) 晶振石英晶体振荡器 表示符号:X 石英晶体滤波器 表示符号:X 双列集成电路 表示符号:IC或U 运算放大器倒相放大器 AND gate 非门 NAND gate与非门NOR gate 或非门 保险管 表示符号:F 变压器永久磁铁电感

二、电工电路图符号大全 电流表PA 电压表PV 有功电度表PJ 无功电度表PJR 频率表PF 相位表PPA 最大需量表(负荷监控仪) PM 功率因数表PPF 有功功率表PW 无功功率表PR 无功电流表PAR

声信号HA 光信号HS 指示灯HL 红色灯HR 绿色灯HG 黄色灯HY 蓝色灯HB 白色灯HW 连接片XB 插头XP 插座XS 端子板XT 电线,电缆,母线W 直流母线WB 插接式(馈电)母线WIB 电力分支线WP 照明分支线WL 应急照明分支线WE 电力干线WPM 照明干线WLM 应急照明干线WEM 滑触线WT 合闸小母线WCL 控制小母线WC 信号小母线WS 闪光小母线WF 事故音响小母线WFS 预告音响小母线WPS 电压小母线WV 事故照明小母线WELM 避雷器F 熔断器FU 快速熔断器FTF 跌落式熔断器FF 限压保护器件FV 电容器C