NE555时基集成电路实验

2012年04月01日11:41 来源:本站整理作者:灰色天空我要评论(0)

1.常用电子元器件简介

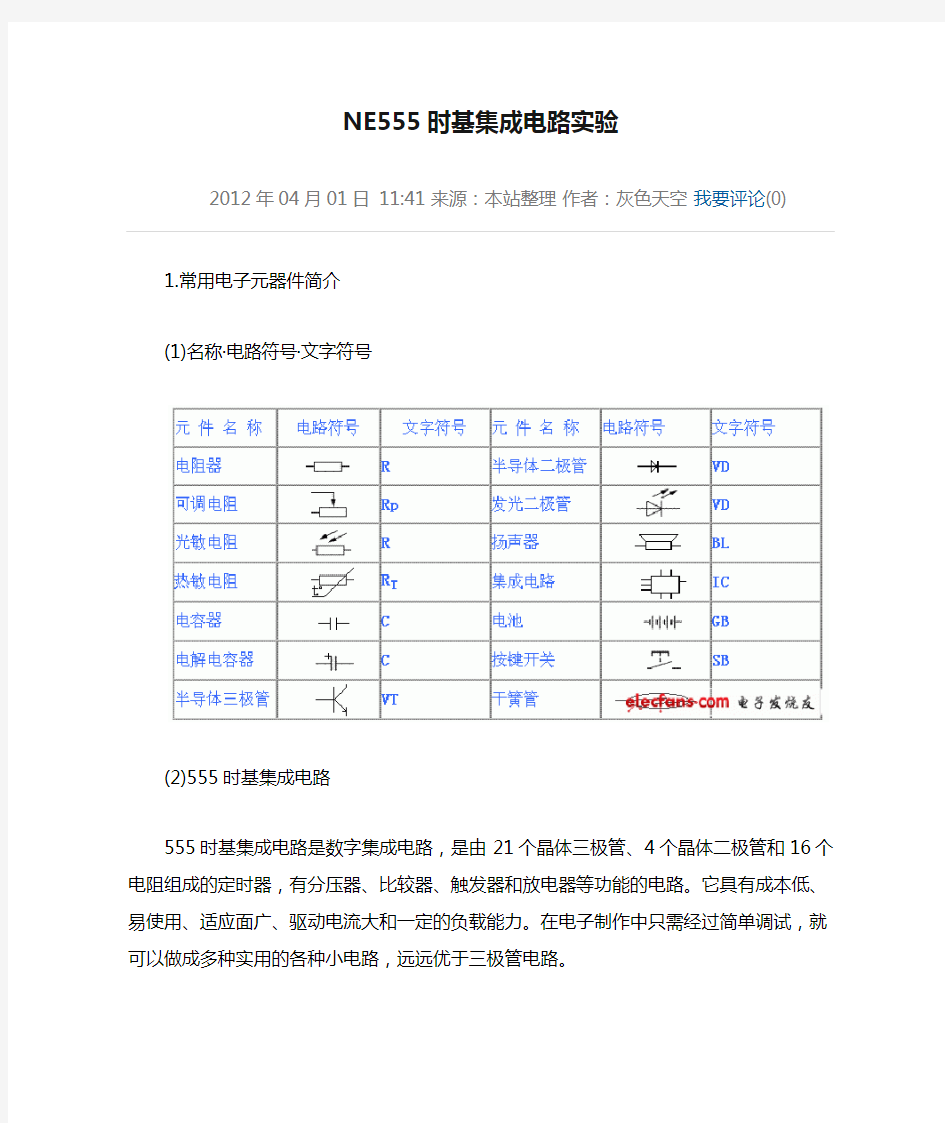

(1)名称·电路符号·文字符号

(2)555时基集成电路

555时基集成电路是数字集成电路,是由21个晶体三极管、4个晶体二极管和16个电阻组成的定时器,有分压器、比较器、触发器和放电器等功能的电路。它具有成本低、易使用、适应面广、驱动电流大和一定的负载能力。在电子制作中只需经过简单调试,就可以做成多种实用的各种小电路,远远优于三极管电路。

555时基电路国内外的型号很多,如国外产品有:NE555、LM555、A555和CA555等;国内型号有5GI555、SL555和FX555等。它们的内部结构和管脚序号都相同,因此,可以直接互相代换。但要注意,并不是所有的带555数字的集成块都是时基集成电路,如MMV555、AD555和AHD555等都不是时基集成电路。

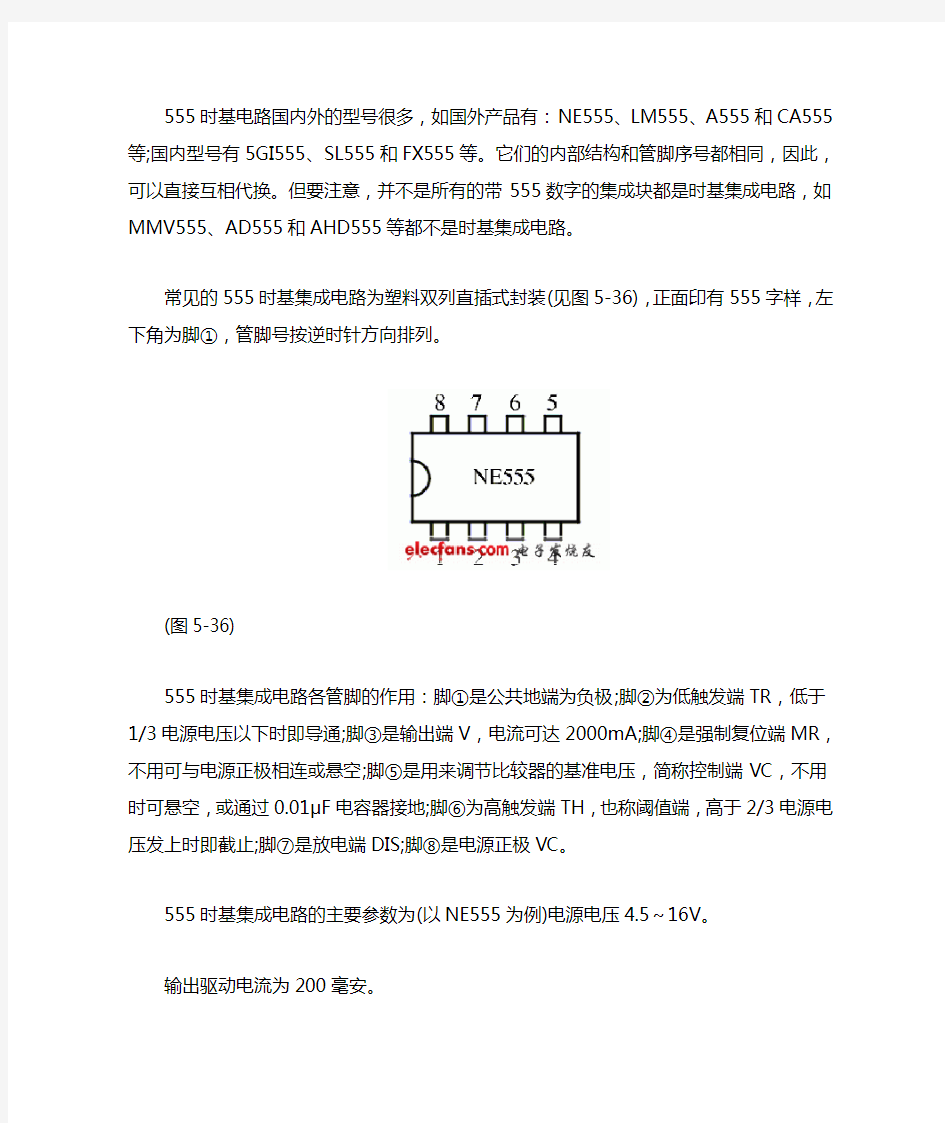

常见的555时基集成电路为塑料双列直插式封装(见图5-36),正面印有555字样,左下角为脚①,管脚号按逆时针方向排列。

(图5-36)

555时基集成电路各管脚的作用:脚①是公共地端为负极;脚②为低触发端TR,低于1/3电源电压以下时即导通;脚③是输出端V,电流可达2000mA;脚④是强制复位端MR,不用可与电源正极相连或悬空;脚⑤是用来调节比较器的基准电压,简称控制端VC,不用时可悬空,或通过0.01μF电容器接地;脚⑥为高触发端TH,也称阈值端,高于2/3电源电压发上时即截止;脚⑦是放电端DIS;脚⑧是电源正极VC。

555时基集成电路的主要参数为(以NE555为例)电源电压4.5~16V。

输出驱动电流为200毫安。

作定时器使用时,定时精度为1%。

作振荡使用时,输出的脉冲的最高频率可达500千赫。

使用时,驱动电流若大于上述电流时,在脚③输出端加装扩展电流的电路,如加一三极管放大。

(3)音乐片集成电路

它同模仿动物叫声和人语言集成电路都是模拟集成电路,采用软包装,即将硅芯片用黑的环氧树脂封装在一块小的印刷电路板上。

由于集成电路内不宜制作电感、电容及可调电阻等元器件,为了发挥它的作用,必须外接一些元器件。

注意:集成电路片在焊接时不能带电操作,只有焊接后,检查无误,才能接通电源。

2.555时基集成电路基础电路实验

为了便于利用较少的元器件,而达到基本学会555时基集成电路的制作和应用能力,我们筛选了以下元器件供大家实验参考(以下电路图5-37中不再标出数值)。

R1是光敏电阻、R2=10K、R3=2K、R4=200Ω、R5=200Ω、Rp是150K、RT是热敏电阻、IC1是NE555、IC2是焊有三极管和电阻的音乐片、红绿发光管VD1和VD2各一个、SB是按键开关、C1=0.01μF、C2=0.04μF、C3=10μF、C4=47μF、C5=100μF(C3、C4和C5为电解电容器,耐压应当大于6V)、GB=6V、喇叭为8Ω。

(1)触摸电路

这是555时基集成电路的一个特长,具有电路翻转功能,称为双稳工作方式。图5-38是最典型的双稳电路。图中“开”和“关”是两个金属片(铁片或铜片),当手触摸“开”金属片时,人体感应到的脉冲信号就输入到②脚,此时③脚输出高电位,发光二极管发亮。当手摸一下“关”金属片,电路进行翻转,此时③脚输出低电位,发光二极管灭。

图5-37

应注意:发光二极管的两个管脚有正负极之分,焊接(连接)时不能搞错。当电路没有接金属片实验时,手应沾一点水或用手拿钥匙去接触管脚增大电感量。

NE555时基集成电路实验(2)

2012年04月01日11:41 来源:本站整理作者:灰色天空我要评论(0)

(2)延时电路

延时电路有两种,一种是延时关电路,如楼道灯就是这种电路;另一种是延时开电路,这种电路也叫定时电路。

图5-38是555时基集成电路构成的延时关电路。当按动按键开关SB时(按下后手即离开),使C4放电,触发脚③输出高电位,发光二极管亮,定时开始。当C放电结束通过R 充电,电压从零上升到555电源电压的2/3时,脚③输出低电位,发光二极管自动熄灭,定时结束。

图5-38

实验中先将可调电阻的动片接触点拧到中间位置(约75K左右),实验时增大或减少电阻值可以发现发光二极管亮的时间随之增长或减少。拆下C4,换C3和C5会发现电容量越大发光二极管亮的时间也越长。这就是说延时的长短由RP和C数值决定,电阻值越大、电容值越大,延时时间越长。在科技制作中可根据需要更换电阻和电容,以达到延时目的。

(3)闪光电路

图5-39中555时基集成电路由输入端R3、RP和C4组成一个振荡电路,脚③输出的电平不断高低翻转,当脚③输出低电位时,VD1导通发光,VD2灭;当脚③输出低电位时,VD1灭,VD2导通发光。这样红绿发光二极管交替发光闪烁。

图5-39

实验时先将可调电阻动片的接触点拧到中间位置,然后再将电阻值增大或者减少,这时发光二极管交替发光的时间也随之增大或者减少,但并不十分明显。如果分别用C5和C3去替换C4,交替发光时间的长短就十分明显了。其振荡频率(即每秒发光二极管的闪烁次数)只要改变RP的阻值和C的电容量,就能实现。

(4)音响电路

只要把闪光电路中输出端接扬声器(喇叭),如图5-40所示,就成为一个音响器。

图5-40

实验时先将可调电阻拧到中间位置,然后慢慢将电阻值增大减少,音调也随之改变。如果用C2替换C1会发现音调变低。在电子制作中调整电阻阻值或更换电容量达到自己需要的音调。

(5)光控电路

图5-41中光敏电阻和电阻组成一个简单的分压器,脚②和脚⑥接在分压点上。当光照较大时,光敏电阻呈低电阻,因此,分压点的电位较高,当脚⑥电位在2/3电源电压以上时,555时基集成电路内部的上比较器处于复位状态,输出端脚③为低电平,无电流通过。当无光或光弱时,光敏电阻呈高电阻,分压点为低电位,当脚②电位在1/3电源以下时,555时基集成电路内部的下比较器处于置位状态(导通),脚③输出高电平,使发光二极管VD1发光。

图5-41

实验时先将可调电阻的动片接触点拧到中间位置,电路连接好后,用黑色塑料笔帽(不能用金属笔帽)或其他不透光的物品套在光敏电阻上,这时发光二极管亮(如果不亮调整可调

阻值,使发光二极管亮)。如果要在某一特定暗度(不是全黑)下使发光二极管亮,应在所需的暗度下慢慢减少可调电阻阻值,使发光二极管发光,而遇到比这个暗度稍亮的情况后,发光二极管不发光即可,这往往需要反复调整几次才行。

NE555时基集成电路实验(3)

2012年04月01日11:41 来源:本站整理作者:灰色天空我要评论(0)

(6)温度控制电路

图5-42电路中使用热敏电阻器作为头,插入所要控制的物体中去,当温度升高时,热敏电阻阻值减少,利用这个特点通过电路控制所需的温度。

图5-42

电路连接好后,实验时先将热敏电阻器放入热水中,可调电阻值由大向小慢慢调整,使发光二极管刚好发光,当热敏电阻从热水取出,发光二极管立即灭,表示水温超过这个温度时,发光二极管发光提示,不到这个温度不发光。

《集成电路应用》课程实验实验一 4053门电路综合实验 学院:物理与信息工程学院 专业: 电子信息工程 年级: 2015级 姓名:张桢 学号: 指导老师:许志猛

实验一 4053门电路综合实验 一、实验目的: 1.掌握当前广泛使用的74/HC/HCT系列CMOS集成电路、包括门电路、反相 器、施密特触发器与非门等电路在振荡、整形、逻辑等方向的应用。 2.掌握4053的逻辑功能,并学会如何用4053设计门电路。 3.掌握多谐振荡器的设计原理,设计和实现一个多谐振荡器,学会选取和 计算元件参数。 二、元件和仪器: 1.CD4053三2通道数字控制模拟开关 2.万用表 3.示波器 4.电阻、电容 三、实验原理: 1.CD4053三2通道数字控制模拟开关 CD4053是三2通道数字控制模拟开关,有三个独立的数字控制输入端A、B、C和INH输入,具有低导通阻抗和低的截止漏电流。幅值为4.5~20V的数字信号可控制峰-峰值至20V的数字信号。CD4053的管脚图和功能表如下所示 4053引脚图

4053的8种逻辑功能 CD4053真值表 根据CD4053的逻辑功能,可以由CD4053由4053电路构成如下图所示8种逻辑门(反相器与非门或非门、反相器、三态门、RS 触发器、——RS 触发器、异或门等)。 输入状态 接通通道

]) 2)(()(ln[ T DD T DD T DD T V V V V V V V RC T -+--=2.多谐振荡器的设计 非门作为一个开关倒相器件,可用以构成各种脉冲波形的产生电路。电路的基本工作原理是利用电容器的充放电,当输入电压达到与非门的阈值电压VT 时,门的输出状态即发生变化。因此,电路输出的脉冲波形参数直接取决于电路中阻容元件的数值。 可以利用反相器设计出如下图所示的多谐振荡器 这样的多谐振荡器输出的信号周期计算公式为: 当R S ≈2R 时,若:VT=0.5VDD ,对于HC 和HCU 型器件,有 T ≈2.2RC 对于HCT 型器件,有 T ≈2.4RC 四、实验内容: 1. 验证CD4053的逻辑功能,用4053设计门电路,并验证其逻辑功能: (1)根据实验原理设计如下的反相器电路图: CD4053构成反相器电路

福州大学集成电路应用实验一

————————————————————————————————作者:————————————————————————————————日期:

《集成电路应用》课程实验实验一 4053门电路综合实验 学院:物理与信息工程学院 专业: 电子信息工程 年级: 2015级 姓名:张桢 学号: 指导老师:许志猛

实验一 4053门电路综合实验 一、实验目的: 1.掌握当前广泛使用的74/HC/HCT系列CMOS集成电路、包括门电路、反相 器、施密特触发器与非门等电路在振荡、整形、逻辑等方向的应用。 2.掌握4053的逻辑功能,并学会如何用4053设计门电路。 3.掌握多谐振荡器的设计原理,设计和实现一个多谐振荡器,学会选取和 计算元件参数。 二、元件和仪器: 1.CD4053三2通道数字控制模拟开关 2.万用表 3.示波器 4.电阻、电容 三、实验原理: 1.CD4053三2通道数字控制模拟开关 CD4053是三2通道数字控制模拟开关,有三个独立的数字控制输入端A、B、C和INH输入,具有低导通阻抗和低的截止漏电流。幅值为4.5~20V的数字信号可控制峰-峰值至20V的数字信号。CD4053的管脚图和功能表如下所示 4053引脚

4053的8种逻辑功能 CD4053真值表 根据CD4053的逻辑功能,可以由CD4053由4053电路构成如下图所示8种逻辑门(反相器与非门或非门、反相器、三态门、RS 触发器、——RS 触发器、异或门等)。 输入状态 接通通道

]) 2)(()(ln[ T DD T DD T DD T V V V V V V V RC T -+--=2.多谐振荡器的设计 非门作为一个开关倒相器件,可用以构成各种脉冲波形的产生电路。电路的基本工作原理是利用电容器的充放电,当输入电压达到与非门的阈值电压VT 时,门的输出状态即发生变化。因此,电路输出的脉冲波形参数直接取决于电路中阻容元件的数值。 可以利用反相器设计出如下图所示的多谐振荡器 这样的多谐振荡器输出的信号周期计算公式为: 当R S ≈2R 时,若:VT=0.5VDD ,对于HC 和HCU 型器件,有 T ≈2.2RC 对于HCT 型器件,有 T ≈2.4RC 四、实验内容: 1. 验证CD4053的逻辑功能,用4053设计门电路,并验证其逻辑功能: (1)根据实验原理设计如下的反相器电路图: CD4053构成反相器电路

《集成电路应用》课程实验实验二锁相环综合实验 学院:物理与信息工程学院 专业: 电子信息工程 年级: 2015级 姓名:张桢 学号: 指导老师:许志猛

实验二锁相环综合实验 一、实验目的: 1.掌握锁相环的基本原理。 2.掌握锁相环外部元件的选择方法。 3.应用CD4046锁相环进行基本应用设计。 二、元件和仪器: 1.CD4046 2.函数信号发生器 3.示波器 4.电阻、电容若干 5.面包板 三、实验原理: 1.锁相环的基本原理。 锁相环最基本的结构如图所示。它由三个基本的部件组成:鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)。 锁相环工作原理图 鉴相器是个相位比较装置。它把输入信号Si(t)和压控振荡器的输出信号So(t)的相位进行比较,产生对应于两个信号相位差的误差电压Se(t)。 环路滤波器的作用是滤除误差电压Se(t)中的高频成分和噪声,以保证环路所要求的性能,增加系统的稳定性。

压控振荡器受控制电压Sd(t)的控制,使压控振荡器的频率向输入信号的频率靠拢,直至消除频差而锁定。 锁相环是个相位误差控制系统。它比较输入信号和压控振荡器输出信号之间的相位差,从而产生误差控制电压来调整压控振荡器的频率,以达到与输入信号同频。在环路开始工作时,如果输入信号频率与压控振荡器频率不同,则由于两信号之间存在固有的频率差,它们之间的相位差势必一直在变化,结果鉴相器输出的误差电压就在一定范围内变化。在这种误差电压的控制下,压控振荡器的频率也在变化。若压控振荡器的频率能够变化到与输入信号频率相等,在满足稳定性条件下就在这个频率上稳定下来。达到稳定后,输入信号和压控振荡器输出信号之间的频差为零,相差不再随时间变化,误差电压为一固定值,这时环路就进入“锁定”状态。这就是锁相环工作的大致过程。 2.CD4046芯片的工作原理。 CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V -18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。 CD4046锁相的意义是相位同步的自动控制,功能是完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。锁相环主要由相位比较器(PC)、压控振荡器(VCO)、低通滤波器三部分组成,如下所示。 4046组成框图

电子科技大学 实验报告 二、实验项目名称:CMOS模拟集成电路设计与仿真 三、实验地点:211大楼606房间 四、实验学时:4 五、实验目的: (1)综合运用课程所学知识自主完成相应的模拟集成电路版图设计,掌握基本的IC版图布局布线技巧。 (2)学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行版图的的设计与验证 六、实验原理: IC设计一般规则: ①根据用途要求,确定系统总体方案 ②根据电路的指标和工作条件,确定电路结构与类型,然后通过模拟计算, 决定电路中各器件的参数(包括电参数、几何参数等),EDA软件进行模拟仿真。 ③根据电路特点选择适当的工艺,再按电路中各器件的参数要求,确定满足 这些参数的工艺参数、工艺流程和工艺条件。 ④按电路设计和确定的工艺流程,把电路中有源器件、阻容元件及互连以一 定的规则布置在硅片上,绘制出相互套合的版图,以供制作各次光刻掩模版用。 ⑤生成PG带制作掩模版 ⑥工艺流片 ⑦测试,划片封装

实验模拟基于Cadence 平台的电路设计与仿真 七、实验内容: 1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。 2、设计一个运算放大器电路,要求其增益大于60dB, 相位裕度大于45o, 功耗小于10mW。 3、根据设计指标要求,选取、确定适合的电路结构,并进行计算分析。 4、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans 分析、建立时间小信号特性和压摆率大信号分析,能熟练掌握各种分析的参数设置方法。 5、电路性能的优化与器件参数调试,要求达到预定的技术指标。 6、整理仿真数据与曲线图表,撰写并提交实验报告。 八、实验仪器与器材 (1)工作站或微机终端一台 (2)EDA仿真软件 1套 九、实验结果: 1、根据实验指导书熟悉UNIX操作系统常用命令的使用,掌握Cadence EDA仿真环境的调用。 2、根据设计指标要求,设计出如下图所示的电路结构。并进行计算分析,确定其中各器件的参数。 4、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans分析,能熟练掌握各种分 ①增益与频率之间的关系、相位裕度与频率之间关系图如下所示: ②输入、输出关系曲线 十、实验结果计算与分析: 从幅频特性曲线图像中可以读出,电路的增益A V=59dB略小于设计所要求的60dB;找出增益接近于0时候的截止频率为102.4MHz,对应到下方相频特性曲线图像中为-130o,则相位裕度为180o-130o=50o,

实验一集成电路系统EDA软件使用简介 (基础性实验) 一实验目的 1、了解利用Quartus II 8.0 软件开发数字电路的基本流程以及掌握Quartus II软件 的详细操作。 2、了解使用VHDL原理图设计进行集成电路系统设计的实现方法。 3、掌握Quartus II 8.0 软件开发数字电路的基本设计思路,软件环境参数配置,时 序仿真,管脚分配,并且利用JTAG接口进行下载的常规设计流程。 二实验前的准备 1、将红色的MODUL_SEL拨码开关组合的1、 2、8拨上, 3、 4、 5、 6、7拨下,使数码 管显示当前模式为:C1. 2、检查JTAG TO USB转换接口和USB连接线的连接,并且将JTAG线连接到核心板上的 JTAG接口(核心板的第二个十针的插口)处。 三实验要求 学习使用Quartus II 8.0软件,掌握VHDL文本描述和原理图描述的RTL级描述方法。 四实验内容 (一)了解门电路元件库 1、新建原理图设计文件,并在原理图设计文件的基础上插入各种基本门电路元件,包 括与门、或门、非门、异或门等。 2、利用原理图图形编辑窗,将基本门电路元件进行连接,形成布线。 3、为连接好的门电路组合电路添加输入和输出端口。 (二)了解逻辑电路的仿真 1、保存原理图设计文件,新建时序仿真文件。 2、将各端口的信号标出,并对其实施功能仿真或时序仿真。并将仿真波形写入实验报 告。 (三)了解原理图文件的综合和下载 1、对原理图文件进行综合和引脚连结。 2、将对应FPGA端口连接至原理图电路端口中,并将原理图文件综合后的网表文件下载 到FPGA中,进行功能验证。 3、将硬件功能情况描述记录于实验报告中。

555/556时基电路的特点和封装 常见的数字或模拟集成电路型号的阿拉伯数字,仅表示其编号,而555时基集成电路的3个“5”,却有具体的内涵,故各生产厂家无一例外地在型号中加以保留。这是因为在该集成电路基片上的基准电压电路是由三个误差极小的5KΩ电阻组成,分压精度高。 555电路大量应用于电子控、电子检测、仪器仪表、家用电器、音响报警、电子玩具等诸多方面。可用作振荡器、脉冲发生器、延时发生器、定时器、方波发生器、单稳态触发振荡器、双稳态多谐振荡器、自由多谐振荡器、锯齿波产生器、脉宽调制器、脉位调制器等等。 555时基电路之所以得到这样的广泛应用,在于它具有如下几个特点: 1、555在电路结构上是由模拟电路数字电路组合而成,它将模拟功能与逻辑功能兼容为一体,能够产生精确的时间延迟和振荡。它拓宽了模拟集成电路的应用范围。 2、该电路采用单电源。双极型555的电压范围为1.5V~15V;而CMOS型的电源适应范围更宽,为2V~18V。这样,它就可以和模拟运算放大器和TTL或CMOS数字电路共用一个电源。 3、555可独立构成一个定时电路,且定时精度高。 4、555的最大输出电流达200mA,带负载能力强,可直接驱动小电机、喇叭、继电器等负载。

图1 555时基集成电路的封装外形一般有两种,一种是做成8脚圆形TO-99型,如图1中(a)所示;另一种是8脚双列直插式封装,如图1中(b)所示。556双时基集成电路内含两个相同的时基电路,双列直插14脚封装,如图2所示。 图2 CMOS型555/556时基集成电路与双极型的555/556管脚排列完全相同,国产型号的555/556与国外产品的管脚排列也一致,易于互换。 同时应指出,CMOS型555/556在绝大多数场合都可以直接替代双极型555/556,但CMOS型的驱动电流较双极型的要小,且多数电参数都有所改善,如静态电流300μA,阈值端、触发端、复位端等的输入阻抗高达1010欧姆,电源电压的适应范围也加宽,为2~18V。

实验报告 课程名称:集成电路原理 实验名称:模拟集成电路版图设计与验证小组成员: 实验地点:科技实验大楼606 实验时间:2017年6月19日 2017年6月19日 微电子与固体电子学院

一、实验名称:模拟集成电路版图设计与验证 二、实验学时:4 三、实验原理 1、电路设计与仿真 实验2内容,根据电路的指标和工作条件,然后通过模拟计算,决定电路中各器件的参数(包括电参数、几何参数等),EDA软件进行模拟仿真。 2、工艺设计 根据电路特点结合所给的工艺,再按电路中各器件的参数要求,确定满足这些参数的工艺参数、工艺流程和工艺条件。 3、版图设计 按电路设计和确定的工艺流程,把电路中有源器件、阻容元件及互连以一定的规则布置在Candence下的版图编辑器内。并优化版图结构。 四、实验目的 本实验是基于微电子技术应用背景和《集成电路原理》课程设置及其特点而设置,为IC设计性实验。其目的在于: 1、根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路版图设计,掌握基本的IC版图布局布线技巧。 2、学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行版图的的设计与验证。 通过该实验,使学生掌握CMOS模拟IC版图设计的流程,加深对课程知识的感性认识,增强学生的设计与综合分析能力。 五、实验内容 1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。

2、根据实验2所得参数,自主完成版图设计,并掌握布局布线的基本技巧。 3、整理版图生成文件,总结、撰写并提交实验报告。 六、实验仪器设备 (1)工作站或微机终端一台 (2)EDA仿真软件1套 七、实验步骤 1、根据实验指导书掌握Cadence EDA仿真环境的调用。熟悉版图编辑器Layout Editor的使用。了解基本的布局布线方法及元器件的画法。 2、根据实验2所计算验证的两级共源CMOS运放的元器件参数如表1所示,在版图设计器里画出相应的元器件,对V+、V-、V out、V DD、GND的压焊点位置合理化放置,通过金属画线将各个元器件按实验2的电路图合理连接,避免跳线。 表 1运放各器件版图参数

实验2 导线特性 1 实验目的 了解导线的RC特性和建模方法。 2 实验内容 设某层金属阻值为0.086欧姆/方。金属层导线长度为1300um,宽度为0.13um;其集总电容为0.1pf。设信号源为1.2V,内阻1K欧姆。利用Elmore延时公式计算、并使用下列模型仿真此导线的延时(50%至50%)以及上升和下降时间(10%至90%)。 (1)一个电阻、一个电容的集总模型; (2) 3型RC模型; (3)T3型RC模型。 下面是当时编写的,自己都记不清了,问号是保存为记事本txt有问题。 (a) INVa .options list node post .model m1 pmos level=2 .model m2 nmos level=2 m1 out in vdd vdd?m1 L=0.250u?W=1.125u m2 out in 0? 0? m1 L=0.250u?W=0.375u cl out 0 1pf vdd vdd 0 dc 2.5 vin in 0 dc 2.5 .op .dc vin 0 2.5 0.5 .print dc v(in) v(out) .probe dc v(in) v(out) .END (b) INVb .options list node post

.model m1 pmos level=2 .model m2 nmos level=2 m1 out in vdd vdd?m1 L=0.250u?W=2.750u m2 out in 0? 0? m1 L=0.250u?W=0.375u cl out 0 1pf vdd vdd 0 dc 2.5 vin in 0 dc 2.5 .op .dc vin 0 2.5 0.5 .print dc v(in) v(out) .probe dc v(in) v(out) .END (c) INVc .options list node post .model m1 pmos level=2 .model m2 nmos level=2 m1 out in vdd vdd?m1 L=0.250u?W=1.125u m2 out in 0? 0? m1 L=0.250u?W=0.375u cl out 0 1pf vdd vdd 0 dc 2.5 vin in 0 dc vd .data vd_table 1 1.5 2.5 .enddata .op .tran 100p 100n .print tran v(in) v(out) .probe tran v(in) v(out) .END (d) INVc .options list node post .model m1 pmos level=2 .model m2 nmos level=2 m1 out in vdd vdd?m1 L=0.250u?W=0.750u m2 out in 0? 0? m1 L=0.250u?W=0.375u cl out 0 1pf vdd vdd 0 dc 2.5 vin in 0 dc 2.5

集成电路设计综合实验 题目:集成电路设计综合实验 班级:微电子学1201 姓名: 学号:

集成电路设计综合实验报告 一、实验目的 1、培养从版图提取电路的能力 2、学习版图设计的方法和技巧 3、复习和巩固基本的数字单元电路设计 4、学习并掌握集成电路设计流程 二、实验内容 1. 反向提取给定电路模块(如下图1所示),要求画出电路原理图,分析出其所完成的逻辑功能,并进行仿真验证;再画出该电路的版图,完成DRC验证。 图1 1.1 查阅相关资料,反向提取给定电路模块,并且将其整理、合理布局。 1.2 建立自己的library和Schematic View(电路图如下图2所示)。 图2 1.3 进行仿真验证,并分析其所完成的逻辑功能(仿真波形如下图3所示)。

图3 由仿真波形分析其功能为D锁存器。 锁存器:对脉冲电平敏感,在时钟脉冲的电平作用下改变状态。锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,当锁存器处于使能状态时,输出才会随着数据输入发生变化。简单地说,它有两个输入,分别是一个有效信号EN,一个输入数据信号DATA_IN,它有一个输出Q,它的功能就是在EN有效的时候把DATA_IN的值传给Q,也就是锁存的过程。 只有在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号。其中使能端A 加入CP信号,C为数据信号。输出控制信号为0时,锁存器的数据通过三态门进行输出。所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号到来时才改变。锁存,就是把信号暂存以维持某种电平状态。 1.4 生成Symbol测试电路如下(图4所示) 图4

第一章 集成电路的测试 1.集成电路测试的定义 集成电路测试是对集成电路或模块进行检测,通过测量对于集成电路的输出回应和预期输出比较,以确定或评估集成电路元器件功能和性能的过程,是验证设计、监控生产、保证质量、分析失效以及指导应用的重要手段。 .2.集成电路测试的基本原理 输入Y 被测电路DUT(Device Under Test)可作为一个已知功能的实体,测试依据原始输入x 和网络功能集F(x),确定原始输出回应y,并分析y是否表达了电路网络的实际输出。因此,测试的基本任务是生成测试输入,而测试系统的基本任务则是将测试输人应用于被测器件,并分析其输出的正确性。测试过程中,测试系统首先生成输入定时波形信号施加到被测器件的原始输入管脚,第二步是从被测器件的原始输出管脚采样输出回应,最后经过分析处理得到测试结果。 3.集成电路故障与测试 集成电路的不正常状态有缺陷(defect)、故障(fault)和失效(failure)等。由于设计考虑不周全或制造过程中的一些物理、化学因素,使集成电路不符合技术条件而不能正常工作,称为集成电路存在缺陷。集成电路的缺陷导致它的功能发生变化,称为故障。故障可能使集成电路失效,也可能不失效,集成电路丧失了实施其特定规范要求的功能,称为集成电路失效。故障和缺陷等效,但两者有一定区别,缺陷会引发故障,故障是表象,相对稳定,并且易于测试;缺陷相对隐蔽和微观,缺陷的查找与定位较难。 4.集成电路测试的过程 1.测试设备 测试仪:通常被叫做自动测试设备,是用来向被测试器件施加输入,并观察输出。测试是要考虑DUT的技术指标和规范,包括:器件最高时钟频率、定时精度要求、输入\输出引脚的数目等。要考虑的因素:费用、可靠性、服务能力、软件编程难易程度等。 1.测试界面 测试界面主要根据DUT的封装形式、最高时钟频率、ATE的资源配置和界面板卡形等合理地选择测试插座和设计制作测试负载板。

555时基电路的四种常用电路 555时基电路是一种双极型的时基集成电路,工作电源为4.5v~18v,输出电平可与TTL、CMOS 和HLT逻辑电路兼容,输出电流为200mA,工作可靠,使用简便而且成本低,可直接推动扬声器、电感等低阻抗负载,还可以在仪器仪表、自动化装置及各种电器中作定时及时间延迟等控制,可构成单稳态触发器、无稳态多谐振荡器、脉冲发生器、防盗报警器、电压监视器等电路,应用及其广泛 1 555时基电路的内部结构 国产双极型定时器CB555的电路结构如图l所示。它由分压器、电压比较器C1和C2、SR锁存器、缓冲输出器和集电极开路的放电三极管TD组成。 1.1 电压比较器 电压比较器C1和C2是两个相同的线性电路,每个电压比较器有两个信号输入端和一个信号输出端。C1的同向输入端接基准比较电压VR1,反向输入端(也称阈值端TH)外接输入触发信号电压,C2的反向输入端接基准比较电压VR2,同向输入端(也称触发端TR')外接输入触发信号电压。 1.2 分压器 分压器由三个等值电阻串联构成,将电源电压Vcc分压后分别为两个电压比较器提供基准比较电压。在控制电压输入端Vco悬空时,C1、C2的基准比较电压分别为 通常应将Vco端接一个高频干扰旁路电容。如果Vco外接固定电 压,则 1.3 SR锁存器 SR锁存器是由两个TTL与非门构成,它的逻辑状态由两个电压比较器的输出电位控制,并有一个外引出的直接复位控制端R'D。只要在R'D端加上低电平,输出端vo便立即被置成低电平,不受其它输入端状态的影响。正常工作时必须使R'D处于高电平。SR锁存器有置0(复位)、置1(置位)和保持三种逻辑功能。电压比较器C1的输出信号作为SR锁存器的复位控制信号,电压比较器C2的输出信号作为SR锁存器的置位控制信号。 1.4 集电极开路的放电三极管

NE555时基集成电路的创新应用研究 王若麟,邱宗毓,符俊虎,李麒,王艺凯,郑培远,刘世源 (平顶山一中) 摘要:NE555是555计时芯片中应用较广的一个型号,具有双稳态、单稳态、无稳态三种电路组织形式,工作电压范围达4.5~16V,输出电流最大可达225mA,工作频率范围宽,具有较好的兼容性。其双稳态电路可用于电子开关等,单稳态电路可用于定时器、延时器、分频器等,无稳态电路可用于逆变器、音频振荡器、PWM调压输出等。关键词:NE555集成电路;R-S触发器;单稳态定时器;PWM调压输出;多谐振荡器 1 绪论 1.1 NE555简介 NE555是属于555系列的计时芯片中的一个型号,输入电压范围4.5~16V,输出电流最大225mA,只需简单的电容器、电阻与其配合,便可构成双稳态、单稳态、无稳态三大类电路,完成特定的振荡、锁存或延时作用,且定时范围极广,可由数微秒至数小时。它的操作电源范围大,可与TTL,CMOS 等逻辑芯片配合,并且输出电流大,可直接推动多种负载。DIP封装的NE555的芯片引脚图和内部结构图如下所示 图1.1-1 DIP封装NE555引脚图1 图1.1-2 NE555内部结构示意图1 555定时器典型应用有单稳态电路、双稳态电路、无稳态电路三种。单稳态电路只有一个稳定状态,触发翻转一段时间后会回到原来的稳定状态,一般用作定时、分频或固定宽度脉冲整形,分为人工启动型、脉冲启动型、压控振荡器三种类型。双稳态电路有两个稳定状态,具有记忆和锁存的功能,有R-S触发器和施密特触发器两种形式,R-S型可用于电子开关等,施密特触发器可用于波形变换、电压鉴别。无稳态电路主要是多谐振荡器,可分为直接反馈型、间接反馈型和压控振荡型,

电子科技大学成都学院 课程结题报告 课程名称:集成电路应用设计实验报告姓名:乱弹的枇杷 学号:1240830XXX 院系:电子工程系 专业:电气工程及其自动化教师:XXX 2014年6月

数据选择器及其应用 一、实验器材(设备、元器件): 1,数字、模拟实验装置(1台); 2,数字电路实验板(1块); 3,74LS00和74LS153芯片(各1片)。 二、实验内容及目的: 1,熟悉中规模集成电路数据选择器的逻辑功能; 2,了解数据选择器的应用; 3,熟悉了解用中规模集成电路设计逻辑电路的技巧。 三、实验步骤: 1、测试74LS153集成电路的逻辑功能 74LS153又名双四选一数据选择器,即其在一块集成芯片上有两个四选一数据选择器。其外引脚图与功能表如下图所示: 输入 输出 1A 0A S Y X X 1 0 0 0 0 0D 0 1 0 1D 1 0 0 2D 1 1 3D

将74LS153按下图所示电路图连接,将地址端1A 、0A ,使能端S 接逻辑电平开关,确定数据输入端0D ——3D 的状态,输出端Q 接逻辑电平显示;再改变地址端1A 、0A 的状态组合,观察Q 的输出变化,记录测试结果。 2,用74LS153设计一位全加器 ①根据全加器真值表,可写出和i S ,高位进位i C 的逻辑函数; ②1A 、2A 作为两输入变量,即加数和被加数A ,B ,0D ——3D 为第三个输入变量,即低位进位i C ;1Y 为全加器的和i S ,2Y 为全加器的高位进位i C ,则可令数据选 择器的输入为:1A =i A ,0A =i B ,01D =31D =i C ,11D =21D =1-i C ,02D =0,32D =1,12D =22D =1-i C ,1Y=i S ,2Y=i C ; ③以此连接再验证。 3,将74LS153扩展成一个八选一数据选择器 将74LS153的1A 、0A 作为地址端,将S 1和2S 作为连接作为选通端,将1Y 和2Y (1Y+2Y=Y )利用74LS00(或门)作为输出端,这样就构成了一个八选一数据选择器,其输出端的状态与数据输入端31D 、21D 、11D 、01D 、32D 、22D 、12D 、02D 有关。

CMOS放大器设计实验报告 一、实验目的 1.培养学生分析、解决问题的综合能力; 2.熟悉计算机进行集成电路辅助设计的流程; 3.学会适应cadence设计工具; 4.掌握模拟电路仿真方法 6.掌握电子电路、电子芯片底层版图设计原则和方法; 7.掌握使用计算机对电路、电子器件进行参数提取及功能模拟的过程; 8.熟悉设计验证流程和方法。 二、实验原理 单级差分放大器结构如下图所示: 在电路结构中,M2和M3组成了NMOS差分输入对,差分输入与

单端输入相比可以有效抑制共模信号干扰;M0和M1电流镜为有源负载,可将差分输入转化为单端输出;M5管提供恒定的偏置电流。三、实验要求 设计电路使得其达到以下指标: 1.供电电压: 2.输入信号:正弦差分信号 3.共模电压范围为 4.差分模值范围 5.输出信号:正弦信号 6.摆率大于 7.带宽大于 8.幅值增益: 9.相位裕度: 10.功耗: 11.工作温度: 四、差分放大器分析

1、直流分析 为了使电路正常工作,电路中的MOS管都应处于饱和状态。 1.1 M2管的饱和条件: 1.2 M4管的饱和条件: 2.小信号分析 小信号模型如下:

由图可得: 2.1 增益分析 其中 2.2 频率响应分析由小信号模型易知: 其中 3.电路参数计算3.1确定电流 根据摆率指标:

根据功耗指标易知: 根据带宽指标: 综上,取: 3.2宽长比的确定 M4与M5:电流源提供的电流为,参数设为,根据电流镜原理,可以算出 M2与M3: 带入数据可得 取值为20,则取 M0与M1:这两个PMOS管对交流性能影响不大,只要使其下方的

《集成电路应用》课程实验实验一4053门电路综合实验 学院:物理与信息工程学院 专业: 电子信息工程 年级:2015级 姓名:张桢 学号: 指导老师:许志猛

实验一4053门电路综合实验 一、实验目的: 1.掌握当前广泛使用的74/HC/HCT系列CMOS集成电路、包括门电路、 反相器、施密特触发器与非门等电路在振荡、整形、逻辑等方向的应用。 2.掌握4053的逻辑功能,并学会如何用4053设计门电路。 3.掌握多谐振荡器的设计原理,设计和实现一个多谐振荡器,学会选取和 计算元件参数。 二、元件和仪器: 1.CD4053三2通道数字控制模拟开关 2.万用表 3.示波器 4.电阻、电容 三、实验原理: 1.CD4053三2通道数字控制模拟开关 CD4053是三2通道数字控制模拟开关,有三个独立的数字控制输入端A、B、C和INH输入,具有低导通阻抗和低的截止漏电流。幅值为4.5~20V的数字信号可控制峰-峰值至20V的数字信号。CD4053的管脚图和功能表如下所示

CD4053真值表 根据CD4053的逻辑功能,可以由CD4053由4053电路构成如下图所示 8种逻辑门(反相器与非门或非门、反相器、三态门、RS 触发器、——RS 触发器、异或门等)。 输入状态 接通通道

]) 2)(()(ln[T DD T DD T DD T V V V V V V V RC T -+--=2.多谐振荡器的设计 非门作为一个开关倒相器件,可用以构成各种脉冲波形的产生电路。电路的 基本工作原理是利用电容器的充放电,当输入电压达到与非门的阈值电压VT 时,门的输出状态即发生变化。因此,电路输出的脉冲波形参数直接取决于电路中阻容元件的数值。 可以利用反相器设计出如下图所示的多谐振荡器 这样的多谐振荡器输出的信号周期计算公式为: 当R S ≈2R 时,若:VT=0.5VDD ,对于HC 和HCU 型器件,有 T ≈2.2RC 对于HCT 型器件,有 T ≈2.4RC 四、实验内容: 1. 验证CD4053的逻辑功能,用4053设计门电路,并验证其逻辑功能: (1)根据实验原理设计如下的反相器电路图:

哈尔滨理工大学数字集成电路设计实验报告 学院:应用科学学院 专业班级:电科12 - 1班 学号:32 姓名:周龙 指导教师:刘倩 2015年5月20日

实验一、反相器版图设计 1.实验目的 1)、熟悉mos晶体管版图结构及绘制步骤; 2)、熟悉反相器版图结构及版图仿真; 2. 实验内容 1)绘制PMOS布局图; 2)绘制NMOS布局图; 3)绘制反相器布局图并仿真; 3. 实验步骤 1、绘制PMOS布局图: (1) 绘制N Well图层;(2) 绘制Active图层; (3) 绘制P Select图层; (4) 绘制Poly图层; (5) 绘制Active Contact图层;(6) 绘制Metal1图层; (7) 设计规则检查;(8) 检查错误; (9) 修改错误; (10)截面观察; 2、绘制NMOS布局图: (1) 新增NMOS组件;(2) 编辑NMOS组件;(3) 设计导览; 3、绘制反相器布局图: (1) 取代设定;(2) 编辑组件;(3) 坐标设定;(4) 复制组件;(5) 引用nmos组件;(6) 引用pmos组件;(7) 设计规则检查;(8) 新增PMOS基板节点组件;(9) 编辑PMOS基板节点组件;(10) 新增NMOS基板接触点; (11) 编辑NMOS基板节点组件;(12) 引用Basecontactp组件;(13) 引用Basecontactn 组件;(14) 连接闸极Poly;(15) 连接汲极;(16) 绘制电源线;(17) 标出Vdd 与GND节点;(18) 连接电源与接触点;(19) 加入输入端口;(20) 加入输出端口;(21) 更改组件名称;(22) 将布局图转化成T-Spice文件;(23) T-Spice 模拟; 4. 实验结果 nmos版图

集成电路设计 综合实验报告 学院:电气与控制工程学院 班级:微电子1001 姓名:*** 学号:10060801**

1、培养从版图提取电路的能力 2、学习版图设计的方法和技巧 3、复习和巩固基本的数字单元电路设计 4、学习并掌握集成电路设计流程 二、实验内容 1. 反向提取给定电路模块(如下图1所示),要求画出电路原理图,分析出 其所完成的逻辑功能,并进行仿真验证;再画出该电路的版图,完成DRC 验证。 2. 设计一个CMOS结构的二选一选择器。 (1)根据二选一选择器功能,分析其逻辑关系。 (2)根据其逻辑关系,构建CMOS结构的电路图。 (3)利用EDA工具画出其相应版图。 (4)利用几何设计规则文件进行在线DRC验证并修改版图。

通过反复对比版图可以提取出如下电路原理图 再分析可得到门级电路图 进行仿真,波形如下

功能分析 通过如上分析可知,该电路的功能是一个带使能端的D锁存器:A端为CLK输入端,低电平有效,B端为D信号端,C端为使能端,高电平有效,Y端为输出端。 再设计优化版图如下 MUX21设计 1.电路原理图如下

2.版图设计

3.仿真波形 四、心得体会 经过前几次的实习,我已经能很熟练的使用终端命令了,对于cadence的使用也更加熟练,大量快捷键的使用帮了我很大忙。这一次的反向提取还是很麻烦的,摸索了很长时间后,我们给栅加编号,从上到下,从左到右。然后分析两侧的源漏端,最后分析铜线连接,不断对比得到最后的电路原理图。版图的设计还是比较容易的,因为我们是对比原来的版图画的,但是在版图的绘制过程之中还是要细心,注意工艺的最小线宽或者最小的距离的要求。由于刚开始没注意,我们又反复调整了很多次 通过这一次的实验,让我基本掌握了Cadence软件的使用,原理图的绘制及仿真;版图绘制的基本步骤,在绘制过程中应该注意的工艺要求,以及DRC验证的方法。

2.3.1 555时基电路的介绍和内部结构 555集成电路定时器是一种将模拟功能和逻辑功能集成在同一硅片上的单片时基电路。它的型号很多,如FX555,5G555,J55,UA555,NE555,它们的逻辑功能与外部引线排列完全相同,555定时器的电源电压范围宽,双极型555定时器为5~16V,CMOS555 定时器为3~18V,它可提高与TTL,CMOS的数字电路兼容的接口电平。由于555定时 器价格低廉,使用灵活方便,只需外接少量元件就可构成多种模拟和数字电路,因而极广泛地应用在波形产生与变换,测量与控制,家用电器及电子玩具领域,它的外部引脚 555定时器能在较宽电压范围工作,输出交电平不低于90%电源电压,带拉电流负载和电流负载能力可达到200MA。 图2-3 555定时器外部引脚 555时基电路由运算放大电路器A1,A2组成电压比较器,由F1F2组成的

基本R—S触发器以及由F3和NPN型集成电极开路输出的放电三极管TD等组成的输出级和放电开关。其中电压比较器的分压偏置电阻采用三个阻值相同的5K电阻,所以电路因此特征而被命名为“555时基电路”。555时基电路的内部结构图如图2-4。 图2-4 555时基电路图 2.3.2 555时基电路的工作原理及功能电压比较 1)分压器3个5K 电阻组成,为两个A1和A2提供基准电平,如控制端C O,则经分压后,A的基准电平为2/3Ucc,B的基准电平为1/3Ucc,如改变管脚的接法就改变了两个电压比较器的基准电平 2)比较器 比较器A1,B2是两个结构和性能完全相同的高精度电压比较器,其输出直接控制着基本R-S触发器的状态。TH是比较器A1的输入端,TR是比较器A2的输入端。 当TH输入信号使U6》2/3Ucc,则A1输出交电平,否则A输出为低电平,当R输入信号使号使V2》1/3Ucc,A2输出为低电平,否则输出高电平3)基本R—S触发器 基本R——S触发器要求低电平触发,图中F1的输入端接UC1,为置O 输入端(R),F2的输入端接Uc2为置输入端(S)。Uc1=0,Uc2=1,时Q=0。当Uc1=1,Uc2=时,Q=1 4)放电器和输出缓冲器 集电极开路输出的放三极管TD组成放电器当输出U0为‘0“时,Q为1使UTD导通,管脚T和地间构成通路,而输出U0为”1“时,Q为0 使UTD 截止,通路被切断。输出缓冲器由反相器构成,一方面增强了带负载能力,另一方面隔离负载对555定时器的影响。 总上所述可得555时基器电路功能表如下表2-1所示 2-1 表555时基电路功能表

福州大学集成电路应用实验二

《集成电路应用》课程实验 实验二锁相环综合实验 学院:物理与信息工程学院 专业:电子信息工程_________ 年级:2015 级______________ 姓名:_______ 张桢___________ 学号:_______________________ 指导老师:许志猛____________

实验二锁相环综合实验 一、实验目的: 1.掌握锁相环的基本原理。 2.掌握锁相环外部元件的选择方法。 3.应用CD4046锁相环进行基本应用设计。 二、元件和仪器: 1.CD4046 2.函数信号发生器 3.示波器 4.电阻、电容若干 5.面包板 三、实验原理: 1.锁相环的基本原理。 锁相环最基本的结构如图所示。它由三个基本的部件组成:鉴相器(PD、环路滤波器(LPF)和压控振荡器(VCO o 锁相环工作原理图 鉴相器是个相位比较装置。它把输入信号Si(t)和压控振荡器的输出信号So(t)的相位进行比较,产生对应于两个信号相位差的误差电压

Se(t) o

环路滤波器的作用是滤除误差电压Se(t)中的高频成分和噪声,以保证环路所要求的性能,增加系统的稳定性。 压控振荡器受控制电压Sd(t)的控制,使压控振荡器的频率向输入信号的频率靠拢,直至消除频差而锁定。 锁相环是个相位误差控制系统。它比较输入信号和压控振荡器输出信号之间 的相位差,从而产生误差控制电压来调整压控振荡器的频率,以达到与输入信号 同频。在环路开始工作时,如果输入信号频率与压控振荡器频率不同,则由于两信号之间存在固有的频率差,它们之间的相位差势必一直在变化,结果鉴相器输出的误差电压就在一定范围内变化。在这种误差电压的控制下,压控振荡器的频率也在变化。若压控振荡器的频率能够变化到与输入信号频率相等,在满足稳定 性条件下就在这个频率上稳定下来。达到稳定后,输入信号和压控振荡器输出信号之间的频差为零,相差不再随时间变化,误差电压为一固定值,这时环路就进入“锁定”状态。这就是锁相环工作的大致过程。 2.CD4046芯片的工作原理。 CD4046是通用的CMO锁相环集成电路,其特点是电源电压范围宽(为3V— 18V),输入阻抗高(约100M Q),动态功耗小,在中心频率f0为10kHz下功耗仅为600卩W属微功耗器件。 CD4046锁相的意义是相位同步的自动控制,功能是完成两个电信号相位同步 的自动控制闭环系统叫做锁相环,简称PLL,它广泛应用于广播通信、频率合成、 自动控制及时钟同步等技术领域。锁相环主要由相位比较器( PC、压控振荡器 (VCO、低通滤波器三部分组成,如下所示。 4046组成框图 Yn

NE555时基集成电路实验 2012年04月01日11:41 来源:本站整理作者:灰色天空我要评论(0) 1.常用电子元器件简介 (1)名称·电路符号·文字符号 (2)555时基集成电路 555时基集成电路是数字集成电路,是由21个晶体三极管、4个晶体二极管和16个电阻组成的定时器,有分压器、比较器、触发器和放电器等功能的电路。它具有成本低、易使用、适应面广、驱动电流大和一定的负载能力。在电子制作中只需经过简单调试,就可以做成多种实用的各种小电路,远远优于三极管电路。 555时基电路国内外的型号很多,如国外产品有:NE555、LM555、A555和CA555等;国内型号有5GI555、SL555和FX555等。它们的内部结构和管脚序号都相同,因此,可以直接互相代换。但要注意,并不是所有的带555数字的集成块都是时基集成电路,如MMV555、AD555和AHD555等都不是时基集成电路。 常见的555时基集成电路为塑料双列直插式封装(见图5-36),正面印有555字样,左下角为脚①,管脚号按逆时针方向排列。

(图5-36) 555时基集成电路各管脚的作用:脚①是公共地端为负极;脚②为低触发端TR,低于1/3电源电压以下时即导通;脚③是输出端V,电流可达2000mA;脚④是强制复位端MR,不用可与电源正极相连或悬空;脚⑤是用来调节比较器的基准电压,简称控制端VC,不用时可悬空,或通过0.01μF电容器接地;脚⑥为高触发端TH,也称阈值端,高于2/3电源电压发上时即截止;脚⑦是放电端DIS;脚⑧是电源正极VC。 555时基集成电路的主要参数为(以NE555为例)电源电压4.5~16V。 输出驱动电流为200毫安。 作定时器使用时,定时精度为1%。 作振荡使用时,输出的脉冲的最高频率可达500千赫。 使用时,驱动电流若大于上述电流时,在脚③输出端加装扩展电流的电路,如加一三极管放大。 (3)音乐片集成电路 它同模仿动物叫声和人语言集成电路都是模拟集成电路,采用软包装,即将硅芯片用黑的环氧树脂封装在一块小的印刷电路板上。 由于集成电路内不宜制作电感、电容及可调电阻等元器件,为了发挥它的作用,必须外接一些元器件。 注意:集成电路片在焊接时不能带电操作,只有焊接后,检查无误,才能接通电源。 2.555时基集成电路基础电路实验 为了便于利用较少的元器件,而达到基本学会555时基集成电路的制作和应用能力,我们筛选了以下元器件供大家实验参考(以下电路图5-37中不再标出数值)。