DS100 (v1.0) 2009 年 2 月 6 日

产品规范

? 2006–2009 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PowerPC is a trademark of IBM Corp. and is used under license. PCI, PCI Express, PCIe, and PCI-X are trademarks of PCI-SIG. All other trademarks are the property of their respective owners.

Virtex-5 系列概述

概述

Virtex?-5 系列可提供 FPGA 市场中最新最强大的功能。Virtex-5 系列采用第二代高级芯片组合模块 (ASMBLTM) 列式架构,包含 5 个截然不同的平台(子系列),是 FPGA 系列中选择最为丰富的系列。每个平台都拥有独特特性,以满足诸多高级逻辑设计的需求。除最先进的高性能逻辑结构外,Vritex-5 FPGA 还内置大量 IP 硬核系统级模块,其中包括功能强大的 36Kb 模块 RAM/FIFO 、第二代 25x18 DSP Slice 、带内置数控阻抗的 SelectIO TM 技术、ChipSync TM 源同步接口模块、系统监控功能、带集成数字时钟管理器 (DCM) 和锁相环 (PLL) 时钟生成器的增强型时钟管理模块,以及高级的配置选项。平台的其它独立特性包括用于增强串行连接功能的功耗优化型高速串行收发器模块、符合 PCI Express? 规范的集成端点模块、三态以太网媒体访问控制器 (MAC) 以及高性能 PowerPC? 440 微处理器嵌入式模块。这些特性可以让高级逻辑设计人员在基于 FPGA 的系统中构建最高性能和最强大的功能。Virtex-5 FPGA 采用业界一流的 65 nm 铜工艺技术,是定制 ASIC 技术理想的可编程替代产品。大多数高级系统设计都要求强大的 FPGA 可编程功能。Virtex-5 FPGA 以前所未有的逻辑、DSP 、硬/软微处理器和连接功能,为满足高性能逻辑设计人员、高性能 DSP 设计人员和高性能嵌入式系统设计人员的需求,提供了最佳解决方案。Virtex-5 LXT 、SXT 、TXT 及 FXT 平台具有高级高速串行连接功能和链路/事务层功能。

? 5 个平台:LX 、LXT 、SXT 、TXT 及 FXT

- Virtex-5 LX :主要用于高性能通用逻辑应用

- Virtex-5 LXT :主要用于具备高级串行连接功能的高性能逻辑 - Virtex-5 SXT :主要用于具备高级串行连接功能的高性能信号 处理应用

- Virtex-5 TXT :主要用于具备双密度高级串行连接功能的高 性能系统

- Virtex-5 FXT :主要用于具备高级串行连接功能的高性能嵌 入式系统? 跨平台兼容性

- LXT 、SXT 及 FXT 器件使用可调稳压器,可以在相同封装 内实现引脚兼容

? 最先进的最佳利用率高性能 FPGA 结构 - 真正的 6 输入查找表 (LUT) 技术 - 双 5- LUT 选项

- 改进的布线减少了中间连线 - 64 位分布式 RAM 选项 - SRL32/双 SRL16 选项

? 强大的时钟管理模块 (CMT) 时钟功能

- 具有零延迟缓冲、频率综合和时钟相移功能的数字时钟管理模 块 (DCM)

- 具备输入抖动滤波、零延迟缓冲、频率综合以及相位匹配时钟 分频功能的 PLL 模块? 36Kb Block RAM/FIFO - 真双端口 RAM 模块

- 增强的可选可编程 FIFO 逻辑 - 可编程

- 高达 36 位宽度的真正双端口 - 高达 72 位宽度的简单双端口 - 内置可选纠错电路

- 可选择将每个块配置作为两个独立的18Kb 块? 高性能并行 SelectIO 技术

- I/O 工作电压:1.2V 至 3.3V

- 使用 ChipSync TM 技术的源同步接口连接 - 数控阻抗 (DC) 有源终端 - 灵活的精细 I/O 分组 - 支持高速存储器接口

? 高级 DSP48E Slice 技术

- 25x18 补码乘法运算

- 可选加法器、减法器及累加器 - 可选流水线功能 - 可选按位逻辑功能 - 专用的级联连接? 灵活的配置选项

- SPI 和并行 Flash 接口

- 专用的回读重配置逻辑,可支持多比特流 - 自动总线宽度检测功能? 对所有器件都有系统监控功能 - 片上/片外热特性监控 - 片上/片外电源监控

- 通过 JTAG 端口访问所有监控量? PCI Express 集成端点模块

- 支持 LXT 、SXT 、TXT 及 FXT 平台 - 符合 PCI Express 基本规范 1.1

- 每个模块支持 1 倍、4 倍或者 8 倍信道宽度 - 与 RocktetIO TM 收发器配合使用? 三态 10/100/1000 Mb/s 以太网 MAC - 支持 LXT 、SXT 、TXT 及 FXT 平台

- RocketIO 收发器可用作 PHY ,也可选择使用多种软 MII (媒体独立接口)连接到外部 PHY

? 速率从 100Mb/s 到 3.75Gb/s 的 RocketIO GTP 收发器 - 支持 LXT 和 SXT 平台

? 速率从 150Mb/s 到 6.5Gb/s 的 RocketIO GTP 收发器 - 支持 TXT 和 FXT 平台? PowerPC 440 微处理器 - 仅支持 FXT 平台 - RISC 架构 - 7 级流水线

- 包括 32 KB 的指令和数据缓存 - 优化的处理器接口结构(纵横机)? 65 nm 铜 CMOS 工艺技术

? 1.0V 内核电压

? 可选择标准或无铅的具有高度信号完整性的倒装片封装

Virtex-5 FPGA 特性总结

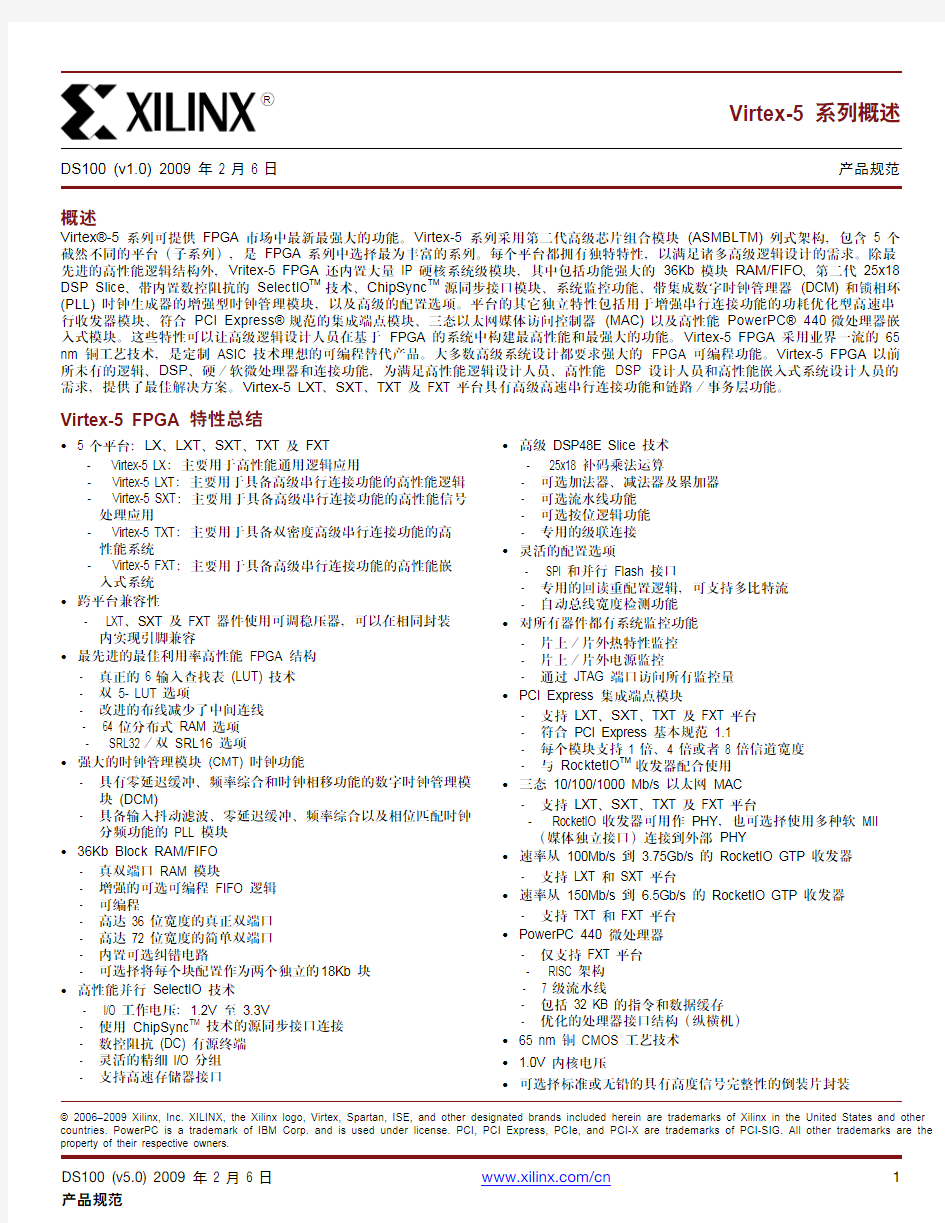

表 1:Virtex-5 FPGA 系列成员

器件

可配置逻辑模块 (CLB)

DSP48E

Slice(2)

Block RAM

CMT(4)

PowerPC

处理器

模块

PCI

Express

端点

模块

以太网

MAC

最大 RocketIO

收发器(6)

总I/O

bank(8)

最大

用户

I/O(7)阵列

(行x列)

Virtex-5

Slice(1)

最大

分布式

RAM(Kb)

18Kb(3)36Kb

最大

(Kb)

GTP GTX

XC5VLX3080 x 304,8003203264321,5222不适用不适用不适用不适用不适用13400 XC5VLX50120 x 307,2004804896481,7286不适用不适用不适用不适用不适用17560 XC5VLX85120 x 5412,96084048192963,4566不适用不适用不适用不适用不适用17560 XC5VLX110160 x 5417,2801,120642561284,6086不适用不适用不适用不适用不适用23800 XC5VLX155160 x 7624,3201,6401283841926,9126不适用不适用不适用不适用不适用23800 XC5VLX220160 x 10834,5602,2801283841926,9126不适用不适用不适用不适用不适用23800 XC5VLX330240 x 10851,8403,42019257628810,3686不适用不适用不适用不适用不适用331,200 XC5VLX20T60 x 263,1202102452269361不适用124不适用7172 XC5VLX30T80 x 304,8003203272361,2962不适用148不适用12360 XC5VLX50T120 x 307,20048048120602,1606不适用1412不适用15480 XC5VLX85T120 x 5412,960840482161083,8886不适用1412不适用15480 XC5VLX110T160 x 5417,2801,120642961485,3286不适用1416不适用20680 XC5VLX 155T160 x 7624,3201,6401284242127,6326不适用1416不适用20680 XC5VLX 220T160 x 10834,5602,2801284242127,6326不适用1416不适用20680 XC5VLX 330T240 x 10851,8403,42019264832411,6646不适用1424不适用27960 XC5VSX 35T80 x 345,440520192168843,0242不适用148不适用12360 XC5VSX 50T120 x 348,1607802882641324,7526不适用1412不适用15480 XC5VSX 95T160 x 4614,7201,5206404882448,7846不适用1416不适用19640 XC5VSX 240T240 x 7837,4404,2001,0561,03251618,5766不适用1424不适用27960 XC5VTX150T200 x 5823,2001,500804562288,2086不适用14不适用4020680 XC5VTX240T240 x 7837,4402,4009664832411,6646不适用14不适用4820680 XC5VFX30T80 x 385,12038064136682,4482114不适用812360 XC5VFX70T T160 x 3811,2008201282961485,3286134不适用1619640 XC5VFX100T160 x 5616,0001,2402564562288,2086234不适用1620680 XC5VFX130T200 x 5620,4801,58032059629810,7286236不适用2024840 XC5VFX200T240 x 6830,7202,28038491245616,4166248不适用2427960

注:

1. Virtex-5 FPGA Slice 的结构与前几代不同。每个 Virtex-5 FPGA Slice 均包含 4 个 LUT 和 4 个触发器(之前为 2 个 LUT 和 2 个触发器。)

2. 每个 DSP48E Slice 内含一个 25x18 乘法器、一个加法器及一个累加器。

3. Block RAM 大小基本为 36 Kb。每个模块还可以作为两个独立的 18 Kb 模块使用。

4. 每个时钟管理模块 (CMT) 内含 2 个 DCM 和一个 PLL。

5. 本表列出了各个器件的以太网 MAC 个数。

6. RocketIO GTP 收发器的运行速率为:100Mb/s 到 3.75Gb/s。RocketIO GTX 收发器的运行速率为:150Mb/s 到 6.5Gb/s。

7. 该数字不包括 RocketIO 收发器。

8. 包含配置 Bank 0。

2 https://www.doczj.com/doc/3c14799129.html,/cn DS100 (v5.0) 2009 年 2 月 6 日

? 高达 16.4Mb 的集成模块存储器? 带有可选双 18Kb 模式的 36Kb 模块? 真双端口 RAM 单元

? 可选独立端口宽度(1 位宽到 72 位宽)

- 对于真双端口运行,每端口总宽度高达 36 位

- 对简单双端口运行,每端口总宽度高达 72 位(一个读取端口 和一个写入端口)

- 支持 9 位、18 位、36 位和 72 位宽度的存储器位数及奇偶校 验/边带存储器

- 从 32Kx1 到 512x72 的配置(从 8Kx4 到 512x72 用于 FIFO 运行)

? 多速率 FIFO 支持逻辑

- 具有完全可编程近满标志和近空标志的满标志和空标志? 支持同步 FIFO ,没有标志不确定的问题

? 用于提高性能的可选流水线级数? 字节写入功能

? 专用级联布线,无需 FPGA 其他连线即可配成 64K x 1 存储器? 满足高可靠性存储要求的集成可选 ECC

? 针对 18 Kb (及以下)运行的特殊降功耗设计? 多达 6 个时钟管理模块 (CMT)

- 每个 CMT 包含 2 个 DCM 和一个 PLL ,时钟发生器总数多达 18 个

- 灵活的 DCM 到 PLL 或 PLL 到 DCM 级联 - 精密时钟去歪斜和相移 - 灵活的频率综合

- 多种运行模式,便于性能权衡决策 - 提高最大输入/输出频率 - 精细相移分辩率 - 输入抖动滤波 - 低功耗运行 - 相移范围大

? 可实现优化低抖动时钟和精确占空比的差分时钟树结构

? 32 个全局时钟网络

? 除了全局时钟外,还提供局部时钟、I/O 时钟和本地时钟。? 多达 1,200 个用户 I/O

? 提供从 1.2V 到 3.3V 的广泛的 I/O 标准选择范围? 极高的性能

- 高达 800Mb/s 的 HSTL 和 SSTL (在所有单端 I/O 上) - 高达 1.25Gb/s 的 LVDS (在所有差分 I/O 对上)? 真正的差分片上终端

? 输入和输出 I/O 同边沿采集? 支持广泛的存储器接口

? 25x18 补码乘法运算

? 用于提高性能的可选流水线级数

? 用于乘法累加 (MACC) 运算的可选 48 位累加器,可选择将累加

器级联为 96 位

? 用于复杂乘法运算或乘加运算的集成加法器

? 可选按位逻辑运行模式

? 每个 Slice 具有独立的 C 寄存器

? 在一个 DSP 列中完全可级联,无需外部布线资源? 与 SelectIO 技术配合使用,简化源同步接口

? 所有 I/O 模块均内置逐比特去歪斜功能(所有输入和输出上的可

变延迟线)

? 专用的 I/O 时钟和区域时钟资源(引脚和时钟树)

? 所有 I/O 均内置数据串行器和解串器逻辑,支持相应的时钟分

频器

? 每个 I/O 提供速率高达 1.25Gb/s 的网络/电信接口

? 与 Virtex-4 器件相比,平均提升 1 至 2 个速度级

? 具备可级联的 32 位可变移位寄存器或 64 位分布式存储器功能? 优异的布线架构,增强了对角布线功能,连接模块与模块之间的

中间连线极少

? 支持多达 330,000 个逻辑单元,包括:

- 多达 207,360 个具有时钟使能的内部架构触发器 (XC5VLX330)

- 多达 207,360 个真 6 输入查找表 (LUT),总 LUT 位数超过 1,300 万

- 双 5-LUT 提供 2 个输出模式提高了利用率 - 逻辑扩展式多路复用器和 I/O 寄存器

Virtex-5 FPGA 逻辑

550MHz 集成模块存储器550MHz 时钟技术SelectIO 技术

550MHz DSP48E Slice

ChipSync 源同步接口逻辑

4 https://www.doczj.com/doc/3c14799129.html,/cn DS100 (v5.0) 2009 年 2 月 6 日

? 可选串行或并行终端? 温度和电压补偿? 显著简化电路板布局

- 减少电阻器

- 在理想的位置设置终端,比如信号源或信号终点

? 片上温度测量(±4℃)? 片上电源测量(±1%)? 简便易用,独立运行

- 基本运行无需设计

- 所有片上传感器自行监测

- 片上传感器的用户可编程报警阈值

? 用户可访问的 10 位 200kSPS ADC

- 偏移和增益误差的自动校准

- DNL=±0.9 LSB 最大? 可支持多达 17 个外部模拟输入通道

- 输入范围 0V 到 1V - 监控外部传感器,如电压、温度

- 通用模拟输入? 可以通过内部结构或 JTAG TAP 全面访问系统监控器? 在 FPGA 配置之前和器件省电模式下完全可运行(仅通过 JTAG TAP 访问)

? 1.0V 内核电压

? 12 层金属提供最强的布线功能,并可容纳硬 IP 植入? 三栅极氧化层技术,确实可降低静态功耗

? 支持 Platform Flash 配置、标准 SPI Flash 配置或标准并行 NOR Flash 配置

? 可支持包含专用的回读重配置逻辑的比特流? 256 位 AES 比特流解密,可保护知识产权并防止复制设计? 增强型比特流检错/纠错功能

? 自动总线宽度检测功能

? 通过 ICAP 端口进行部分重配置

? 确实可实现优异信号完整性的预制封装技术

- 尽量减少信号到回路之间的感应环路 - 最佳信号与 PWR/GND 比? 将 SSO 感应噪声降低 1/7

? 无铅封装和标准封装

? 配合 RocketIO GTP 收发器(LXT 和 SXT )以及 GTX 收发器

(TXT 和 FXT ),在最小程度地占用 FPGA 逻辑的情况下,提供 全面的 PCI Express 端点功能? 符合 PCI Express 基本规范 1.1

? PCI Express 端点模块或传统 PCI Express 端点模块? 8 倍、4 倍或 1 倍信道宽度? 支持电源管理

? 用于缓存的 Block RAM ? 完全缓存传输与接收

? 访问 PCI Express 配置空间和内部配置的管理接口? 全程支持最大有效载荷

? 多达 6x32 位或 3x64 位 BAR (或 32 位与 64 位的组合)

? 符合 IEEE 802.3-2002 规范

? 以 10、100 和 1,000Mb/s 的速率运行? 支持三态自动协商

? 接收地址滤波器(5 条地址记录)

? 使用 RocketIO GTP 收发器的全单片 1000Base-X 解决方案? 通过软逻辑和 SelectIO 资源支持多种外部 PHY 连接(RGMII 、

GMII 等)接口

? 通过使用软逻辑和 RocketIO GTP 收发器的 SGMII ,支持到外部 PHY 器件的连接

? 通过独立接口接收和传输可用统计数据

? 独立的主机和客户端接口? 支持巨型帧? 支持 VLAN

? 灵活的用户可配置主机接口

? 支持 IEEE 802.3ah-2004 单向模式

数控阻抗 (DCI) 有源 I/O 终端系统监控器65nm 铜 CMOS 工艺

配置先进的倒装片封装

LXT 、SXT 、TXT 和 FXT 器件具体的系统模块

符合 PCI Express 规范的集成端点模块三态以太网媒体访问控制器

? 具有 100 Mb/s 到 3.75Gb/s 波特率能力的全双工串行收发器? 8B/10B 用户定义 FPGA 逻辑或无编码选项? 支持通道绑定? CRC 生成和检查

? 发射器可编程预加重或预均衡? 可编程终端和电压摆幅? 接收器可编程均衡

? 接收器信号检测和信号丢失指示器? 可用二级配置总线进行用户动态重配置? 对串行 ATA (SATA) 提供带外支持

? 为电气闲置、信标、接收器检测以及 PCI Express 和 SATA 扩频

时钟支持

? 不足100mW 的典型功耗

? 内置 PRBS 发生器和检验器

? 嵌入式 PowerPC 440 (PPC440) 核

- 运行频率高达 550MHz

- 每内核性能均高于 1000DMIPS - 7 级流水线

- 每周期可执行多条指令 - 无序执行

- 32KB 64 路组关联一级指令高速缓存 - 32KB 64 路组关联一级数据高速缓存 - 符合 Book E 标准

? 可增强系统性能的集成纵横机 - 128 位处理器局部总线 (PLB) - 集成的分散/聚集 DMA 控制器

- 用于连接 DDR2 存储器控制器的专用接口 - 非整数 PLB 到 CPU 时钟比率自动同步? 辅助处理器单元 (APU) 接口和控制器

- PPC440 嵌入式模块与基于 FPGA 架构的协处理器的直接连接 - 128 位宽流水线 APU 加载/存储 - 支持自主指令:无流水线停顿 - 定制指令的可编程解码

? 具有 150Mb/s 到 6.5Gb/s 波特率能力的全双工串行收发器

? 8B/10B 编码和编程变速箱,支持 64B/66B 和 64B/67B 编码、用

户定义 FPGA 逻辑或无编码选项? 支持通道绑定

? CRC 生成和检查

? 发射器可编程预加重或预均衡? 可编程终端和电压摆幅

? 接收器可编程连续时间均衡? 接收器可编程决策反馈均衡

? 接收器信号检测与信号丢失指示器? 可用二级配置总线进行用户动态重配置? 支持 OOB (SATA)

? 电气闲置、信标、接收器检测以及 PCI Express 扩频时钟支持? 在所有线速下都能实现低功耗运行

RocketIO GTP 收发器(仅 LXT/SXT )

PowerPC 440 RISC 核(仅 FXT )RocketIO GTX 收发器(仅 TXT/FXT )

?I/O 模块提供连接封装引脚和内部可配置逻辑的接口。可编程 I/O 模块 (IOB) 支持大多数流行的前沿 I/O 标准。可将 IOB 连接到非常灵活的 ChipSync 逻辑,以增强源同步接口连接。源同步优化包括逐比特去歪斜(对于输入和输出信号)、数据串行器/解串器、时钟分频器以及专用 I/O 和本地时钟资源。

?可配置逻辑块 (CLB) 是赛灵思 FPGA 的基本逻辑元件,提供组合和同步逻辑以及分布式存储器和 SRL32 移位寄存器功能。

Virtex-5 FPGA CLB 以真正 6 输入查找表技术为基础,可提供比前几代可编程逻辑更优异的功能和性能。

?Block RAM 模块提供灵活的 36Kb 真双端口 RAM,这种 RAM 可级联为更大的存储器模块。另外,Virtex-5 FPGA Block RAM 包含的可选可编程 FIFO 逻辑可提高器件利用率。还可将每个

Block RAM 配置为两个独立的 18Kb 真双端口 RAM 模块,以便为需要较小 RAM 模块的设计提供存储器粒度。

?可级联嵌入式 DSP48E Slice 具有 25x18 补码乘法器和 48 位加法器/减法器/累加器,可支持大规模并行 DSP 算法。另外,每个 DSP48E Slice 都可用于执行按位逻辑功能。

?时钟管理模块 (CMT) 为 FPGA 提供最灵活、最高性能的时钟控制。每个 CMT 包含 2 个数字时钟管理器 (DCM) 模块(自校准、全数字)和一个 PLL 模块(自校准、模拟),用于时钟分配延迟补偿、时钟乘法/除法运算、粗/细精度时钟相移和输入时钟抖动滤波。此外,LXT、SXT、TXT 和 FXT 器件还包含:

?用于 PCI Express 设计的集成端点模块,提供 1 倍、4 倍或 8 倍的 PCI Express 端点功能。当与 RocketIO 收发器配合使用时,可以用最少的 FPGA 逻辑实现一个完整的 PCI Express 端点。?10/100/1000 Mb/s 以太网媒体访问控制模块提供以太网功能。LXT 和 SXT 器件包含:

?RocketIO GTP 收发器,运行速度可达 3.75Gb/s。每个 GTP 收发器都支持全双工时钟与数据恢复。

TXT 和 FXT 器件包含:

?GTX 收发器,运行速度可达 6.5Gb/s。每个 GTX 收发器都支持全双工时钟与数据恢复。

FXT 器件包含:

?嵌入式 IBM PowerPC 440 RISC CPU。各 PowerPC 440 CPU 的运行频率可达 550MHz。每个 PowerPC 440 CPU 还包含一个可支持硬件加速的 APU(辅助处理器单元)接口,以及一个可实现高数据流量的集成纵横机。

通用布线矩阵(GRM) 在各内部组件之间提供一个布线开关阵列。每个可编程元件均与一个开关矩阵绑定,以实现对通用布线矩阵的多重连接。总体可编程互连是层级式结构,可支持高速设计。在Virtex-5 器件中,优化的布线连接能够以最少的中继段支持 CLB 互连。减少中继段极大地提高了后期布局布线 (PAR) 设计性能。

包括布线资源在内的所有可编程元件均由静态存储元件中的存储值控制。这些值在配置过程中加载到 FPGA 中,可重新加载以便更改可编程元件的功能。

架构说明

Virtex-5 阵列简介

Virtex-5 器件是用户可编程的门阵列,具有针对高密度和高性能系统设计优化的各种可配置元件和嵌入式内核。Virtex-5 器件可实现以下功能:

6 https://www.doczj.com/doc/3c14799129.html,/cn DS100 (v5.0) 2009 年 2 月 6 日

IOB 可编程,并可分类如下:

? 可编程单端或差分 (LVDS) 运行

? 具有可选单倍数据速率 (SDR) 或双倍数据速率 (DDR) 寄存器的 输入模块

? 具有可选 SDR 或 DDR 寄存器的输出模块? 双向模块

? 逐比特去歪斜电路

? 专用 I/O 和区域时钟资源? 内置数据串行器/解串器

IOB 寄存器为边沿触发 D 型触发器或电平敏感锁存器。IOB 支持以下单端标准:

? LVTTL

? LVCMOS (3.3V 、2.5V 、1.8V 、1.5V 和 1.2V )? PCI (33 和 66MHz )? PCI-X

? GTL 和 GTLP

? HSTL 1.5V 和 1.8V (I 、II 、III 和 IV 级)? HSTL 1.2V (一级)

? SSTL 1.8V 和 2.5V (I 和II 级)

数控阻抗 (DCI) I/O 功能可配置成为每个单端 I/O 标准和某些差分 I/O 标准提供片上终端。

IOB 元件还支持以下差分信令 I/O 标准:

? LVDS 和扩展 LVDS (仅 2.5V )? BLVDS (总线 LVDS )? ULVDS

? Hypertransport TM

? 差分 HSTL 1.5V 和 1.8V (I 和 II 级)? 差分 SSTL 1.8V 和 2.5V (I 和 II 级)? RDSD (2.5V 点对点)

每个差分对使用两个相邻的焊盘。2 个或 4 个 IOB 模块连接到一个接入布线资源的开关矩阵。

逐比特去歪斜电路允许 FPGA 内部的可编程信号延迟。逐比特去歪斜灵活地提供精细延迟增量,以精细地生成一系列信号延迟。这对于在源同步接口中同步信号边沿尤其有用。

对于位置选择得当的通用 I/O (每 Bank 8 个),应该为同一局部区域内的 I/O 添加特殊的硬件连接,从而将其设计成具有“区域 Clock-capable ”的 I/O 。这些区域时钟输入分布于限定的区域内,以尽量减轻各 IOB 之间的时钟歪斜。区域 I/O 时钟是对全局时钟资源的补充。

Virtex-5 FPGA 特性

输入/输出模块 (SelectIO)

可配置逻辑块 (CLB)

Block RAM

本部分简述 Virtex-5 系列 FPGA 的特性。

为每个 I/O 增加了数据串行器/解串器功能,以支持源同步接口。输入通路包含一个附有时钟分频器的串并转换器,而输出通路则包含一个并串转换器。

有关 Virtex-5 FPGA IOB 的深入指导,请参阅《Virtex-5 FPGA 三态以太网 MAC 用户指南》。

一个 Virtex-5 FPGA CLB 资源由 2 个 Slice 组成。每个 Slice 包含并等效于:

? 4 个函数发生器? 4 个存储元件? 算术逻辑门? 大型多路复用器? 高速超前进位链

函数发生器可配置为 6 输入 LUT 或双输出 5 输入 LUT 。某些 CLB 中的 SLICEM 可配置成作为一个 32 位移位寄存器(或 2 个 16 位移位寄存器)或 64 位分布式 RAM 运行。此外,可将 4 个存储元件配置成边沿触发的 D 型触发器或电平敏感型锁存器。每个 CLB 具有内部快速互连,并且连接到一个接入通用布线资源的开关矩阵。《Virtex-5 FPGA 用户指南》中进一步讨论了 Virtex-5 FPGA CLB 。

36Kb 真双端口 RAM 模块资源可以编程为从 32Kx1 到 512x72 的各种深度和宽度配置。此外,每个 36Kb 模块也可配置成作为两个独立的 18Kb 双端口 RAM 模块运行。

每个端口都完全同步且独立,提供三种“边写边读”模式。Block RAM 可以级联,以实现大型嵌入式存储模块。此外,作为选项还提供了后端流水线寄存器、时钟控制电路、内置 FIFO 支持、ECC 和字节写使能功能。

《Virtex-5 FPGA 用户指南》中进一步讨论了 Virtex-5 器件中的 Block RAM 功能。

8 https://www.doczj.com/doc/3c14799129.html,/cn DS100 (v5.0) 2009 年 2 月 6 日

CMT 和全局时钟多路复用缓冲器为设计高速时钟网络提供了完善的解决方案。

每个 CMT 包含 2 个 DCM 和一个 PLL 。DCM 和 PLL 可独立使用,也可广泛级联。最多可使用 6 个 CMT 模块,总共可提供 18 个时钟发生器元件。

每个 DCM 都提供常用的时钟生成功能。为了生成无歪斜的内部或外部时钟,可以把每个 DCM 都用于消除时钟分配延迟。DCM 还提供输出时钟的 90°、180°和 270°相移输出。相移精度以数分之一时钟周期的增量提供更高分辨率的相位调整。灵活的频率综合提供等于输入时钟频率分数或整数倍的时钟输出频率。

为增强 DCM 的功能,Virtex-5 FPGA CMT 还包含一个 PLL 。该模块提供参考时钟抖动滤波和更多频率综合选项。

Virtex-5 器件具有 32 个全局时钟 MUX 缓冲器。时钟树设计为差分式。差分时钟可帮助减少抖动和占空比失真。

DSP48E Slice

DSP48E Slice 资源包含一个 25x18 补码乘法器和一个 48 位加法器/减法器/累加器。每个 DSP48E Slice 还含有广泛的级联功能,可有效实现高速 DSP 算法。

《Virtex-5 FPGA XtremeDSP 设计注意事项》中进一步讨论了 Virtex-5 FPGA DSP48E Slice 的功能。

布线资源

Virtex-5 器件中的所有部件都使用相同的互连方案以及相同的全局布线矩阵接入方式。此外,CLB 到 CLB 的布线设计成以尽可能少的中间连线提供一整套连接功能。时序模型是共享的,可大大提高高速设计性能的可预测性。

边界扫描

边界扫描指令和相关的数据寄存器支持接入和配置 Virtex-5 器件的标准方法,符合 IEEE 标准 1149.1 和 1532。

全局时钟

配置

Virtex-5 器件的配置方法是用下列模式之一将比特流载入内部配置存储器:

? 从串模式? 主串模式

? 从动 SelectMAP 模式? 主动 SelectMAP 模式

? 边界扫描模式(IEEE-1532 和 IEEE-1149)? SPI 模式(串行外设接口标准 Flash )

? BPI 上/BPI 下模式(字节宽度外设接口标准 x8 或 x16 NOR

Flash )

此外,Virtex-5 器件还支持下列配置选项:

? 用于 IP 保护的 256 位 AES 比特流解密? 支持冷/热启动的多比特流管理 (MBM)? 并行配置总线宽度自动检测? 并行菊花链

? 配置 CRC 和 ECC 支持,以实现最强大、最灵活的器件完整性

校验

《Virtex-5 FPGA 配置指南》中进一步讨论了 Virtex-5 器件配置。

系统监控器

FPGA 是高可用性/可靠性基础架构的重要构建模块。因此,有必要

更好地监测 FPGA 的片上物理环境及其在系统内紧邻的周边环境。Virtex-5 系列系统监控器首次为 FPGA 及其外部环境提供了更简单的监控。Virtex-5 系列的每个成员都包含一个系统监控器模块。系统监控器是围绕一个 10 位 200kSPS ADC (模数转换器)构建的。这个 ADC 用于对若干片上传感器进行数字化,以提供有关 FPGA 内部物理环境的信息。片上传感器包括一个温度传感器和几个电源传感器。对外部环境的访问是通过若干外部模拟输入通道提供的。这些模拟输入是通用的,可用于对种类繁多的电压信号类型进行数字化。提供了对单极、双极和真差分输入方案的支持。可以通过 JTAG TAP 全面访问片上传感器和外部通道,从而可以将 PC 板上现有的 JTAG 基础架构用于开发期间或现场部署后的模拟测试和高级诊断。系统监控器在 FPGA 通电之后和配置之前完全可运行。系统监控器在设计中不需要显式实例化即可获得对其基本功能的访问。这使得即使在设计周期的最后阶段也可以使用系统监控器。《Virtex-5 FPGA 系统监控器用户指南》中进一步讨论了 Virtex-5 FPGA 系统监控器。

4-24 通道 RocketIO GTP 收发器,能够以 100 Mb/s 到 3.75Gb/s 的速度运行。

? 完全时钟和数据恢复功能

? 支持 8/16 位或 10/20 位数据通路

? 可选 8B/10B 或基于 FPGA 的编码/解码功能? 集成 FIFO /弹性缓冲器? 支持通道绑定和时钟校正? 嵌入式 32 位 CRC 生成/检查

? 集成的间隔符检测或 A1/A2 检测功能? 可编程预加重(AKA 发射器均衡)? 可编程发射器输出摆幅

Virtex-5 LXT 和 SXT 平台特性

RocketIO GTP 收发器

本部分简述仅在 LXT 和 SXT 器件中使用的模块。

Virtex-5 LXT 、SXT 、TXT 和 FXT 器件最多包含 8 个嵌入式以太网 MAC ,每个以太网 MAC 模块有 2 个。这些模块具有以下特点:

? 符合 IEEE 802.3-2002 规范? 经过 UNH 一致性测试

? 使用 RocketIO 技术的 GRMII/GMII 接口,或者当与 SelectIO 收

发器配合使用时的 SGMII 接口

? 半双工或全双工? 支持巨型帧

? 1000 Base-X PCS/PMA :当与 RocketIO GTP 收发器配合使用

时,可提供完全 1000 Base-X 片上实现

? 对微处理器的 DCR 总线连接

Virtex-5 LXT 、SXT 、TXT 和 FXT 器件最多包含 4 个集成端点模

块。这些模块实现事务层、数据链路层和物理层功能,在尽量少用 FPGA 逻辑的情况下可提供完整的 PCI Express 端点功能。这些模块具有以下特点:

? 符合 PCI Express 基本规范 1.1

? 与 RocketIO 收发器配合使用可提供完整的端点功能? 每个模块支持 1 倍、4 倍或者 8 倍通道宽度

Virtex-5 LXT 、SXT 、TXT 和 FXT 平台特性

三态 (10/100/1000 Mb/s) 以太网 MAC

PCI Express 集成端点模块

本部分简述仅在 LXT 、SXT 、TXT 和 FXT 器件中使用的模块。

? 可编程接收器均衡? 可编程接收器终端? 嵌入式支持

- 带外 (OOB) 信令;串行 ATA

- 信标、电气闲置和 PCI Express 接收器检测

? 内置式 PRBS 生成器/校验器

《Virtex-5 FPGA RocketIO GTP 收发器用户指南》中进一步讨论了 Virtex-5 FPGA RocketIO GTP 收发器。

10 https://www.doczj.com/doc/3c14799129.html,/cn DS100 (v5.0) 2009 年 2 月 6 日

8-48 通道 RocketIO 串行收发器,能以 150 Mb/s 到 6.5 Gb/s 的速度运行

? 完全时钟和数据恢复功能

? 支持 8/16/32 位或 10/20/40 位数据通路

? 可选 8B/10B 编码,用于可编程 64B/66B 或 64B/67B 编码的变 速箱,或基于 FPGA 的编码/解码功能

? 集成 FIFO /弹性缓冲器? 支持通道绑定和时钟校正

? 双嵌入式 32 位 CRC 生成/检查? 集成的可编程字符检测

? 可编程去加重(AKA 发射器均衡)? 可编程发射器输出摆幅? 可编程接收器均衡? 可编程接收器终端? 嵌入式支持:

- 串行 ATA :带外 (OOB) 信令

- PCI Express :信标、电气闲置和接收器检测

? 内置 PRBS 生成器/校验器

《Virtex-5 FPGA RocketIO GTX 收发器用户指南》中进一步讨论了 Virtex-5 FPGA RocketIO GTX 收发器。

赛灵思提供具有常用复合功能的 IP 核,包括 DSP 、总线接口、处理器和处理器外设。客户使用赛灵思 LogiCORE TM 产品及第三方

AllianceCORE 参与方提供的内核,可以缩短开发时间、降低设计风

险并获得优良的设计性能。此外,CORE Generator TM 系统还允许客

户在 Virtex-5 FPGA 中实现 IP 核,以获得可预测和可重复的性能。

该系统提供简单的用户接口,用以生成针对 FPGA 优化的基于参数

的内核。

System Generator for DSP 工具允许系统架构设计师用手工设计的

IP 快速建立 DSP 功能模型并实现这些功能;另外,该工具为使用第

三方系统级 DSP 设计工具提供了接口。System Generator for DSP

可实现支持 Virtex-5 FPGA 的多种高性能 DSP 核,包括使用交织器/去交织器、Reed-Solomon 编码器/解码器和 Viterbi 解码器的赛灵思前向纠错解决方案。对于创建支持通信市场的高灵活性连接编解码器,这些内核是理想的选择。

使用 Virtex-5 FPGA RocketIO 收发器,可实现业界领先的连接和网络 IP 核,其中包括最先进的 PCI Express 、串行 RapidIO 、光纤通道和 10Gb 以太网内核。赛灵思 SPI-4.2 IP 核使用 Virtex-5 FPGA ChipSync 技术实现动态相位对齐,以获得高性能源同步运行。

? RISC 超标量架构

? 符合 32 位 Book E 规范? 7 级执行流水线

? 每周期可执行多条指令? 无序执行

? 集成 32KB 一级指令缓存和 32KB 一级数据缓存(64 路组关联)? CoreConnect TM 总线架构

? 可优化处理器带宽的纵横机连接

? PLB 同步逻辑(启用 CPU 到 PLB 的非整数时钟比率)? 辅助处理器单元 (APU) 接口和集成的 APU 控制器

- 基于 FPGA 的协处理器优化连接 - PowerPC 浮点指令的自动解码

- 允许使用自定义指令 - 极高效微控制器式接口连接

《Virtex-5 FPGA 的嵌入式处理器模块参考指南》中进一步讨论了 PowerPC 440 处理器。

Virtex-5 TXT 和 FXT 平台特性

IP 核

RocketIO GTX 串行收发器 (TXT/FXT)

一个或者两个 PowerPC 440 处理器核(仅 FXT )本部分简述仅在 TXT 和 FXT 器件中使用的模块。

赛灵思还为高级系统同步运行提供了 PCI 核。MicroBlaze TM 32 位内核提供业界最快的软处理解决方案,用来构

建面向网络、电信、数据通信以及嵌入式和消费市场的复杂系统。

MicroBlaze 处理器采用 RISC 架构,这种架构使用哈佛式独立 32 位

指令和全速运行的数据总线,可以从片上和外部两种存储器执行程

序和访问数据。一整套标准外设也启用了 CoreConnect TM ,以便为

MicroBlaze 设计人员提供兼容性和可重复利用性。

Virtex-5 FPGA 的所有 IP 核均可见于“赛灵思 IP 中心”门户网站,

该网站提供最新的知识产权核和参考设计,可以通过智能搜索快速

访问。

Virtex-5 FPGA 的 LogiCORE PCI Express 增强型端

点模块封装

这是一款推荐使用的封装,可以对 CORE Generator 系统提供的

PCI Express 集成端点模块进行配置。这种 IP 为端点应用提供多种易用功能和优化配置,可简化设计过程,缩短上市时间。通过注册,无需额外费用即可获得该内核的访问权限,包括比特流生成

功能。

应用说明和参考设计

Virtex-5 器件及封装组合和最大 I/O 数

可以通过赛灵思网站获取专门为 Virtex-5 系列编写的应用指南和参考设计,网址为:https://www.doczj.com/doc/3c14799129.html,/cn/virtex5

表 2:Virtex-5 器件及封装组合和最大可用 I/O 数

封装FF323FFG323FF324FFG324FF676FFG676FF1153FFG1153FF1760FFG1760FF665FFG665FF1136FFG1136FF1156FFG1156FF1738FFG1738FF1759FFG1759尺寸(毫米)19x1919x1927x2735x3542.5x42.527x2735x3535x3542.5x42.542.5x42.5器件

GT

I/O

GT

I/O

GT

I/O

GT

I/O

GT

I/O

GT I/O

GT

I/O

GT

I/O

GT

I/O

GT

I/O

XC5VLX30不适用220不适用400

XC5VLX50不适用220不适用440不适用560

XC5VLX85不适用440不适用560

XC5VLX110不适用440不适用800不适用800

XC5VLX155不适用800不适用800

XC5VLX220不适用800XC5VLX330不适用 1,200

XC5VLX20T 4

GTPs 172

XC5VLX30T 4

GTPs

172

8

GTPs 360

XC5VLX50T 8

GTPs

36012 GTPs 480

XC5VLX85T 12 GTPs 480XC5VLX110T 16 GTPs 64016 GTPs 640XC5VLX155T 16 GTPs 640

16 GTPs 640XC5VLX220T 16 GTPs 640XC5VLX330T 24 GTPs 960

XC5VSX35T 8

GTPs 360

XC5VSX50T 8

GTPs

36012 GTPs 480

XC5VSX95T 16 GTPs 640

XC5VSX240T 24 GTPs 960

XC5VTX150T 40

GTXs

360

40

GTXs 680

XC5VTX240T 48

GTXs

680

XC5VFX30T 8

GTXs 360

XC5VFX70T 8

GTXs

360

16GTXs 640XC5VFX100T 16GTXs

640

16 GTXs 640XC5VFX130T 20 GTXs 840XC5VFX200T

24 GTXs 960

注:

1. 倒装片封装也有无铅版本 (FFG)。

12 https://www.doczj.com/doc/3c14799129.html,/cn DS100 (v5.0) 2009 年 2 月 6 日

Virtex-5 FPGA 订购信息

修订历史

如图 1 所示的 Virtex-5 FPGA 订购信息适用于包括无铅封装在内的所有封装类型。

下表显示了了本文档的修订历史。

!!!! : XC5VLX50T-1FFG665C

?? ? ? :

C = ? (T J = 0°C to +85°C) I = ? (T J = –40°C to +100°C) ? ??

? ?(-1, -2, -3(1))

?DS100_01_111006

??

1?-3 ? ? ?Ё? ? ??

图 1:Virtex FPGA 订购信息

日期

版本

修订

2006 年 4 月 14 日 1.0赛灵思最初版本

2006 年 5 月 12 日 1.1首版发布到赛灵思网站。进行了少量排印修改,并为突出最新功能而更新了相关说明。从第 3 页“Virtex-5 FPGA 逻辑”中删除了 LUT 使用项号。

2006 年 9 月 6 日 2.0在整个文档中增加了 LXT 平台。其中包括对 RocketIO GTP 收发器、以太网 MAC 和 PCI Express 端点模块的说明。

2006 年 10 月12 日 2.1增加了 LX85T 器件。增加了对系统监控器说明和功能。

2006 年 12 月 28 日 2.2增加了 LX220T 器件。修改了表 1 中 LX330 的 I/O Bank 总数。修改了图 1 中的 XC5VLX50T-FFG665 示例。在第 7 页中阐明对 “差分 SSTL 1.8V 和 2.5V (I 和 II 级)”予以支持。

2007 年 2 月 2 日 3.0在整个文档中增加了 SXT 平台。2007 年 5 月 23 日 3.1删除了有关支持 IEEE 1149.6 的内容

2007 年 9 月 4 日 3.2在整个文档中将最高线速从 3.2Gb/s 修改为 3.75Gb/s 。2007 年 12 月 11 日 3.3增加了 LX20T 、LX155T 和 LX155 器件。

2007 年 12 月 17 日 3.4增加了 Disclaimer 。修订了第 3 页中的 CMT 部分。在第 10 页对“Virtex-5 FPGA 的 LogiCORE PCI Express 增强型端点模块封装”予以阐述。

2008 年 3 月 31 日 4.0在整个文档中增加了 FXT 平台。对以下部分中的相关信息予以阐述:“符合 PCI Express 规范的集成端点模块”和“三态以太网媒体访问控制器”。

为避免与 PLL 功能相混淆,删除了第 8 页“全局时钟”中的 PMCD 参考。2008 年 4 月 25 日 4.1在整个文档中添加了 XC5VSX240T 。

2008 年 5 月 7 日 4.2就以下内容更新了整个数据手册:RocketIO GTX 收发器的运行速度设计为从 150 Mb/s 到 6.5 Gb/s 。在第 5 页对 PPC440MC_DDR2 存储控制器予以阐述。

2008 年 6 月 18 日 4.3修改了第 2 页表 1 中的以太网 MAC 列,并增加了注 5。另外还更新了第 9 页 “三态 (10/100/1000 Mb/s) 以太网 MAC ”2008 年 9 月 23 日 4.4在整个文档中增加了 TXT 平台。

修订了第 10 页中的 RocketIO GTX 收发器数据通路支持。2009 年 2 月 6 日

5.0

修改了文档分类,将高级产品规范改成了产品规范。

Notice of Disclaimer

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN (“PRODUCTS”) ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT https://www.doczj.com/doc/3c14799129.html,/cn/warranty.htm THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

Virtex-5 FPGA 文档

有关 Virtex-5 系列 FPGA 的最新完整文档可以从赛灵思网站获得。除了最新的《Virtex-5 系列简介》,还可以下载以下文件:

《Virtex-5 FPGA 数据手册:直流和开关特性》(DS202)

本数据手册介绍了 Virtex-5 系列的直流和开关特性指标。

《Virtex-5 FPGA 用户指南》(UG190)

本指南包含以下章节:

?时钟资源

?时钟管理技术 (CMT)

?锁相环 (PLL)

?Block RAM

?可配置逻辑块 (CLB)

?SelectIO 资源

?SelectIO 逻辑资源

?高级 SelectIO 逻辑资源

《Virtex-5 FPGA XtremeDSP 设计注意事项》(UG193)

本指南介绍了 DSP48E Slice,并包含使用 DSP48E 数学函数和各种滤波器的参考设计。

《Virtex-5 FPGA 配置指南》(UG191)

本配置指南包罗万象,各章节涉及内容包括配置接口(串行和并行)、多比特流管理、比特流加密、边界扫描和 JTAG 配置以及重新配置技术。

《Virtex-5 FPGA 封装和管脚规范》(UG195)

本规范包含器件/封装组合和最大 I/O 数表、引脚定义表、管脚表、管脚图、机械图和热性能技术规范。《Virtex-5 FPGA PCB 设计指南》(UG203)

本指南提供了有关Virtex-5 器件PCB 设计的信息,重点讲述在PCB 和接口层制定设计决策的策略。

《Virtex FPGA 系统监控器用户指南》(UG192)

本指南概述了系统监控器的功能。

《Virtex-5 FPGA RocketIO GTP 收发器用户指南》

(UG196)

本指南介绍了 Virtex-5 LXT 和 SXT 平台提供的 RocketIO GTP

收发器。

《Virtex-5 FPGA RocketIO GTX 收发器用户指南》(UG198)

本指南介绍了 Virtex-5 TXT 和 FXT 平台提供的 RocketIO GTX

收发器。

《Virtex-5 FPGA 三态以太网 MAC 用户指南》(UG194)

本指南介绍了 Virtex-5 LXT、SXT、TXT 和 FXT 平台提供的专用三态以太网媒体访问控制器。

《用于 PCI Express 设计的 Virtex-5 FPGA 集成端点模块用户指南》(UG197)

本指南介绍了 Virtex-5 LXT、SXT、TXT 和 FXT 平台提供的符合PCI Express 规范的集成端点模块。

《Virtex-5 FPGA 中的嵌入式处理器模块参考指南》

(UG200)

本参考指南介绍了 Virtex-5 FXT 平台上提供的嵌入式处理器模块。

1 PCTEL扫频仪相关介绍 本部分主要是这对ASPS所需数据通过PCTEL SeeGull扫频仪获取时,对应扫频仪如何正常设置、安装以及对应测试模式的设置,文件的导出。适用于SeeGull扫频仪TD-LTE系列产品。 PCTEl用于路测数据采集的软件称为“SeeHawk”。在本手册中,我们主要是借用“SeeHawk”前台数据采集部分,来说明SeeGull扫频仪如何使用。本手册以下章节中如无特别说明,所述内容均适用于全系列SeeGull扫频仪产品。 1.1 支撑型号 支持ASPS所需的TOPN测试机制的及相应文件输出的PCTEL扫频仪的型号如下:MX SeeGull TD-LTE全频段扫频仪 不同型号的扫频仪上报能力上存在较大差异。 1.2 测量所需设备 需要准备的设备与备附件: 1、笔记本电脑 2、SeeGull 扫频仪 3、SeeHawk软件 4、扫频仪射频接收天线和GPS天线 5、TD-LTE数据线(USB线缆) 6、扫频仪AC/DC电源适配器 1.3 测量前准备工作 1、将TD-LTE射频天线连接到扫频仪前面板的RF端口,连接USB端口数据线至电脑 USB接口。 2、连接GPS天线到GPS端,将天线置于车顶。 3、接通设备电源,按扫频仪面板的power 开关。 4、USB端口处的指示灯橘红色闪烁表示扫频仪供电正常,设备与电脑还未接通。 5、按照电脑提示安装设备驱动程序,指示灯逐个变成绿色,扫频仪处于开工状态。 6、在测试电脑上完成SeeHawk安装。

1.4 软件的安装及配置 1.4.1 系统需求 为了使系统可靠运转,保证系统的性能要求,安装时务必保证系统具有以下配置。 硬件配置 CPU:奔腾Inel Core2 Duo,2.33G及以上 内存:1G及以上 硬盘: 80G及以上 软件配置 操作系统:Windows XP 专业版;Windows 7专业版 运行环境要求 在SeeHawk运行过程中,请关闭所有的杀毒软件、防火墙软件,避免这些软件对USB 通信的干扰。 1.4.2 软件安装 软件安装环境检测 浏览光驱内的文件,打开文件夹找到应用文件,双击该应用文件运行安装程序,开始软件的安装:

通信原理心得体会 篇一:通信原理学习心得 通信原理学习心得 一学期的通信原理课程结束了,但我对通信原理的学习永远不会结束。经过一个学期的学习我对通信原理有了深刻的认识,我知道这还远远不够,今后的日子里我要更加努力学习通信原理。学习是个艰难的过程,厌烦过,沮丧过,但同时也是充满着激情和快乐的。我想不管干什么都要自信,千万不要轻易的放弃,只要坚持不懈,一定会有结果的。 按照我的传统理解,通信就是信息的传输,在当今高度信息化的社会,信息和通信已经成为现代社会的命脉。所以我们要好好学习通信原理,可以预见,未来的通信系统对人们的生活方式和社会的发展将会产生更加重大和意义深远的影响。 通信原理是电子、通信、计算机络专业的一门理论性较强的专业基础课程,课程的重点是通信系统的性质、信号的传输、检测、处理的基本原理和方法以及信号调制,量化,编码,处理和传输的应用。该课程的特点是概念比较抽象,分析求解所用的数学知识较多。该课程的难点是理论性较强和比较抽象,然而我的数学基础并不够扎实,因此在数学分析与计算方面是一个难点,还有就是缺乏工程背景,而这门课又结合实际比较多,所以学这门课程并不容易,但我们要

好好学习通信原理。 对于通信原理这门课,一开始觉得很难,而且听学长们说通信原理是很难的课程,平时一定要好好学,不然自己学习习的日子根本就抓不到要点了。事实上好像也是如此,当然对于我这样的人,上课时 也不算是比较认真的,但是半学期的学习,我对通信原理确实有了一定的了解和认识。我知道学好通信原理需要一定的数学基础,所以我又翻阅了一下高数课本。翻阅高数课本之后,感觉轻松了一些。我认识到要完成通信,首先要对信号有一个充分的了解与认识,为了对这个信号进行传输我们要进行调制,并选择合适的信道,当然还要考虑噪声的干扰;在接收端我们通过解调把原始信号解调出来以完成我们的通信。 虽然该课程在学习上很困难,但我发现该课程在组织上遵循由特殊到一般、再由一般到特殊的符合认识规律的顺序,由通信系统性能分析到实际调制解调框图的设计等具体问题的应用的规律,后来又结合上机实验学习了MATLAB工具软件,通过Simulink或者MATLAB程序进行通信系统仿真,加深了我对通信系统的理解。 以上是我的学习心得,对于本门课程本想提出课程建议,但是老师讲的挺好的,基本没有什么建议可提。并且感觉老师讲的越来越好了,颜渊曾经这样评价自己的老师孔子,“仰

纵观收音机电路,其组成莫过于放大器和各种滤波器者。由于它要处理各种频率之信号,需要的频率比如中频信号和正在接收的某个频率信号,要让它们以最小的阻碍通过并根据需求进行放大,对于不需要的频率譬如不是想要接收的空中传输的各个发射台信号,收音机自身由于混频,交调,器件之非线性等所产生的各种新频率信号要为之设置最大的阻碍不许它们进入放大器。一部优秀的收音机他的接收部分中的滤波器件对这些个各种频率的电信号的那绝对是爱憎分明的;如果收音机中相应的滤波器对待敌我频率的阶级立场不够坚定,那它决不会是一只好鸡。那么怎样才能知道我们的收音机对他要的信号足够友好,而又对他不该要的信号有足够的抵制能力涅?科学家们搞了个叫做啥“扫频仪” 的玩意儿专门来查看,当然不光是查看而已,还可以一边调整机机里面的滤波器件(主要是那些俗称中周的家伙),一边用这个东西来实时监视调整过程中的达到的效果,直到使我们满意为止。扫频仪何能何德有如此之能力?原来他自身能够产生一定频率范围内的所有信号,包括收音机需要的和应该要强加抵制的。这些个频率的信号由低到高(当然如果你喜欢也可以由高到低的干)的挨个儿的扫过去,故得扫频仪之名也。这些从扫频仪出来的扫频信号,虽然频率不一样,但个头大小可是完全相等的,它们进入一个正常的收音机后,该滤的滤掉,该放大的放大,最后可真是几家欢喜几家愁了,机机认为需要的信号被放大了N 多倍,不需要的信号自然就被衰减到一个很小的值了。扫频仪再由专门的探头去挨个儿察看经过机机的各个频率信号之大小,把这些大小值以频率为横轴,幅值之大小为纵轴,在显示屏上画出一个连续的曲线,我们只要一看到这个曲线马上就知道在扫频范围内不同频率的通过状况,再看看是不是我们想要的那个样子。 国产扫频仪的开山鼻祖当属变态三(BT-3),电子管的,那个头绝对的威猛,据说里面用了好多颗6N11的电子管,好东西来的,新的6N11可能40元RMB 一颗也未必买到,我三天的饭钱也没这么多涅!这位老大后来可是儿孙满堂,晶体管版的,集成版的,,统一的再在后面加字母以示辈分之高低,如BT-3B,BT-3C,BT-3H等等等等。这种通用的扫频仪并非针对收音机,中心频率多在1-300M,扫频范围最小大约到几百个千赫,主要是牛逼的人士用来玩电视机的,对付收音机的调频基本还算凑合,对调幅可能就不怎么灵了,为此咱特的搞了个中频图示仪,专仪专用,AM 的,FM 的,大约还有其他的很多我没听说过的。还是我们一衣带血的睦邻,日本帝国的人民能干,专门搞了些特地用来干收音机的扫频仪,在收音机界最有名的大约就是目黑MSW-7125A 了,据说当时俺们收音机厂们可是花了好多万一套从他们那买了好多好多,现在大把的收音机厂关的关,转的转,于是这些个曾经辉煌的目黑MSW-7125A 们就有好多流落到我们这些成天不务正业的家伙手里,价钱几千就能搞到,风闻最初有八九千一台涅,上回鸟坛有人搞到一批卖二千一台,买者如潮涌,后来又有说这批仪器有些些问题云云,不得而知。我因一时心血来潮遂网罗各地二手仪器商信息终于某日以我自己认为的高价和二手仪器商认为的极低价二千五百现大洋获此MSW-7125A 一只,向本坛昭示本鸟将彻底告别摸黑年代,全面进入到崭新的目黑年代(全体起立,热烈鼓掌十分钟。双手向空中下按以示安静——掌声渐渐稀落)。 购仪过程中曾得到无锡tomcat 王老师的热情指导,在此表示感谢!得意之余,未免有卖弄之欲望,故著此说也。 本使用指南全面参考了红灯大师的大贴题曰“目黑meguro 7125A说明 书.(Thanks for Mr.Pentax007)'的使用说明,链接:

实验一常用信号的表示 【实验目的】 掌握使用MATLAB的信号工具箱来表示常用信号的方法。 【实验环境】 装有MATLAB6.5或以上版本的PC机。 【实验内容】 1. 周期性方波信号square 调用格式:x=square(t,duty) 功能:产生一个周期为2π、幅度为1 ±的周期性方波信号。其中duty表示占空比,即在信号的一个周期中正值所占的百分比。 例1:产生频率为40Hz,占空比分别为25%、50%、75%的周期性方波。如图1-1所示。 clear; % 清空工作空间内的变量 td=1/100000; t=0:td:1; x1=square(2*pi*40*t,25); x2=square(2*pi*40*t,50); x3=square(2*pi*40*t,75); % 信号函数的调用subplot(311); % 设置3行1列的作图区,并在第1区作图plot(t,x1); title('占空比25%'); axis([0 0.2 -1.5 1.5]); % 限定坐标轴的范围 subplot(312); plot(t,x2); title('占空比50%'); axis([0 0.2 -1.5 1.5]); subplot(313); plot(t,x3); title('占空比75%'); axis([0 0.2 -1.5 1.5]);

图1-1 周期性方波 2. 非周期性矩形脉冲信号rectpuls 调用格式:x=rectpuls(t,width) 功能:产生一个幅度为1、宽度为width、以t=0为中心左右对称的矩形波信号。该函数横坐标范围同向量t决定,其矩形波形是以t=0为中心向左右各展开width/2的范围。Width 的默认值为1。 例2:生成幅度为2,宽度T=4、中心在t=0的矩形波x(t)以及x(t-T/2)。如图1-2所示。 t=-4:0.0001:4; T=4; % 设置信号宽度 x1=2*rectpuls(t,T); % 信号函数调用 subplot(121); plot(t,x1); title('x(t)'); axis([-4 6 0 2.2]); x2=2*rectpuls(t-T/2,T); % 信号函数调用

频率特性测试仪及其应用第六章 应保持输入到被测在整个测量过程中,早期频率特性的测量用逐点测绘的方法来实现。就可以在坐标根据所得到的数据,网络信号的幅度不变,记录不同频率下相应输出的电压,而且有可能因测显然,这种方法不仅操作繁锁、费时,纸上描绘出该网络的幅频特性曲线。量频率间隔不够密而漏掉被测曲线上的某些细节,使得到的曲线不够精确。然后用示波器来显示信号通过被测扫频测量法是将等幅扫频信号加至被测电路输入端,在示波器屏幕上可直接显示出被测由于扫频信号的频率是连续变化的,电路后振幅的变化。电路的幅频特性。 (扫描信号)通用电子扫频信号扫描电压示波器发生器发生器X(扫频Y信号)峰值被测电路检波器 图6-1 扫频法测量电路的幅频特性 扫频测量法的仪器连接如图6-1所示。扫描电压发生器一方面为示波器X轴提供扫描信号,一方面又用来控制等幅振荡的频率,使其产生按扫描规律频率从低到高周期性重复变化的扫频信号输出。扫频信号加至被测电路,其输出电压由峰值检波器检波,以反映输出电压随频率变化的规律。 扫频法利用扫描电压连续自动地改变频率,利用示波器直观地显示幅度随频率的变化,与点频测量法相比较,由于扫频信号频率是连续变化的,不存在测试频率的间断点,因此不会漏掉突变点,且能够观察到电路存在的各种冲激变化,如脉冲干扰等。调试电路过程中,可以一边调整电路元件,一边观察显示的曲线,随时判明元件变化对幅频特性产生的影响,迅速查找电路存在的故障。扫频仪又称频率特性图示仪,这是将扫频信号源及示波器的X-Y显示功能结合为一体,并增加了某些附属电路而构成的一种通用电子仪器,用于测量网络的幅频特性。 一、扫频仪的基本工作原理 扫频仪的原理方框图如图6-2所示。 扫描电压发生器产生的扫描电压既加至X轴,又加至扫频信号发生器,使扫频信号的频率变化规律与扫描电压一致,从而使得每个扫描点与扫频信号输出的频率有一一对应的确定关系。扫描信号的波形可以是锯齿波,也可以是正弦波,因为光点的水平偏移与加至X轴的电压成正比,即光点的偏移位置与X轴上所加电压有确定的对应关系,而扫描电压与轴相应地成为频率坐标轴。X扫频信号的输出瞬时频率又有一一对应关系, 故.

1 创远扫频仪相关介绍 本部分主要是这对ASPS所需数据通过上海创远Eagle扫频仪获取时,对应扫频仪如何正常设置、安装以及对应测试模式的设置,文件的导出。适用于Eagle扫频仪TDD-LTE单模与多模系列产品。 上海创远用于路测数据采集的软件称为“Eagle无线环境评估分析系统”。在本手册中,我们主要是借用“Eagle无线环境评估分析系统”前台数据采集部分,来说明Eagle扫频仪如何使用。本手册以下章节中如无特别说明,所述内容均适用于全系列Eagle扫频仪产品。 1.1 支撑型号 支持ASPS所需的TOPN测试机制的及相应文件输出的创远扫频仪的型号如下: 不同型号的扫频仪上报能力上存在较大差异。 1.2 测量所需设备 需要准备的设备与备附件: 1、笔记本电脑 2、Eagle 扫频仪 3、Eagle无线环境评估分析系统软件 4、扫频仪4G射频接收天线和GPS天线 5、数据线(网线) 6、扫频仪AC/DC电源适配器 1.3 测量前准备工作 1、将TDD-LTE射频天线连接到扫频仪前面板的RF2端口(RF1是为其他制式预留的)。 2、连接GPS天线到GPS端,将天线置于车顶。 3、接通设备电源,按扫频仪面板的power 开关。

4、LAN口处的指示灯红色闪烁表示扫频仪供电正常,连接网线端口数据线至电脑网 口,配置电脑IP地址(T2311A型号射频模块默认对应IP地址192.168.0.40;T2311A+ 型号射频模块默认对应IP地址192.168.1.40请注意,PC端本地连接IP地址设置勿与 扫频仪地址相同,否则会由于IP地址冲突无法连接设备。如有冲突,请及时更改本 地连接IP地址,建议设置为与默认地址不冲突的其他IP地址,如192.168.0.111; 192.168.1.111,子网掩码默认255.255.255.0 即可。) 5、指示灯变成绿色闪烁,扫频仪处于开工状态。 6、在测试电脑上完成Eagle无线环境评估分析系统软件安装。 1.4 软件的安装及配置 1.4.1 系统需求 为了使系统可靠运转,保证系统的性能要求,安装时务必保证系统具有以下配置。 硬件配置 CPU:奔腾4,1.7G及以上 内存:1G及以上 硬盘:30G及以上 软件配置 操作系统:Windows XP SP3;Windows 7.0 32位 办公软件:Microsoft Office 2000 /2003;Microsoft Office 2007 运行环境要求 在Eagle无线环境评估分析系统运行过程中,请关闭所有的杀毒软件、防火墙软件,避免这些软件对USB通信的干扰。 1.4.2 软件安装 软件安装环境检测 浏览光驱内的文件,打开文件夹找到Eagle.msi应用文件,双击该应用文件运行安装程序,开始软件的安装:

第7章扫频仪的使用 扫频仪是线性系统的频率特性测试仪器,属于频域测试类仪器。频率特性:指电信号的电参数随频率变化的规律。 频域测量的主要内容包括两项: 1)线性系统的频率特性测量,分为幅频特性测量和相频特性测量。其中幅频特性测量的主要仪器是频率特性测试仪即扫频仪。 2)信号的频谱分析:对信号本身的分析和线性系统非线性失真的测量等,主要仪器是频谱分析仪。 7.1BT-3D扫频仪的使用 扫频仪型号种类很多,但结构大体相同,下面以BT-3D为例加以介绍。 BT-3D频率特性测试仪为卧式通用大屏幕宽带扫频仪,它由扫频信号源和显示系统组合而成,广泛应用于1~300MHz范围内各种无线电网络,接收和发射设备的扫频动态测试.例如,各种有源无源四端网络、滤波器、鉴频器及放大器等的传输特性和反射特性的测量,特别适用于各类发射和差转台、MATV系统、有线电视广播以及电缆的系统测试.本仪器功能齐全,既可1~300MHz范围内全频段一次扫频,满足宽带测试需要,也可窄带扫频和给出稳定的单频信号输出.输出动态范围大,谐波值小,输出衰减器采用电控衰减,可在50mV一0.5V 范围内任取电压,适用于各种工作场合. 7.1.1 BT-3D扫频仪使用 1、面板结构,如图7.1-1。 1)示波显示部分: 电源开关:ON、OFF,打开与关闭电源。 辉度旋钮:调节显示的亮暗。 Y位移旋钮:调节荧光屏上光点或图形在垂直方向上的位置。

Y增益旋钮:调节显示在荧光屏上图形垂直方向幅度的大小。 Y衰减按键“×1 、×10”:输入信号衰减有1,10,两个衰减档级。根据输入电压的大小选择适当的衰减档级进行信号的输入。 影像极性开关:---(“+”、“-”极性):用来改变屏幕上所显示的曲线波形正负极性。当开关在“+”位置时,波形曲线向上方向变化(正极性波形);当开关在“一”位置时,波形曲线向下方向变化(负极性波形)。当曲线波形需要正负方向同时显示时,只能将开关在“+”和“一”位置往复变动,才能观察曲线波形的全貌。 Y输入耦合按键AC / DC :交流、直流输入耦合选择,检波后的信号以交流或直流方式耦合输入。 Y轴输入插座:由被测电路的输出端用电缆探头引接此插座,使输入信号经垂直放大器,便可显示出该信号的曲线波形。 同示波器相比,扫频仪显示控制要简单些,当然,不同型号仪器取舍不同,比如,大多数还会有辉度、聚焦、X增益等控制。本仪器在后面板上包含X增益调节。 图7.1-1 BT-3D扫频仪面板 2)扫频源及扫频控制

¥ 课程设计报告? < 课程名称通信原理 设计题目 DSB与2ASK调制与解调 专业通信工程 班级 学号 姓名 完成日期 …

课程设计任务书 设计题目:DSB与2ASK调制与解调 设计内容与要求: 设计内容: 1.根据DSB的调制原理设计线路,进行仿真模拟调制DSB的调制和解调过程,并通过仿真软件观察信号以及的调制过程中信号波形和频谱的变化。 2. 根据ASK的调制原理设计线路,进行仿真模拟调制DSB的调制和解调过程,并通过仿真软件观察信号以及的调制过程中信号波形和频谱的变化。 3.在设计过程中分析信号变化的过程和思考仿真过程的设计原理。 ; 设计要求: 1.独立完成DSB与ASK的调制与解调; 2.运用仿真软件设计出DSB与ASK的调制线路 3.分析信号波形和频谱 指导教师:范文 2012年12月16日 课程设计评语 ( 成绩: 指导教师:_______________

年月日

一.调制原理: 调制: 将各种数字基带信号转换成适于信道传输的数字调制信号(已调信号或频带信号); 时域定义:调制就是用基带信号去控制载波信号的某个或几个参量的变化,将信息荷载在其上形成已调信号传输,而解调是调制的反过程,通过具体的方法从已调信号的参量变化中将恢复原始的基带信号。 频域定义:调制就是将基带信号的频谱搬移到信道通带中或者其中的某个频段上的过程,而解调是将信道中来的频带信号恢复为基带信号的反过程. 根据所控制的信号参量的不同,调制可分为: 调幅,使载波的幅度随着调制信号的大小变化而变化的调制方式。 调频,使载波的瞬时频率随着调制信号的大小而变,而幅度保持不变的调制方式。 调相,利用原始信号控制载波信号的相位。 调制的目的是把要传输的模拟信号或数字信号变换成适合信道传输的信号,这就意味着把基带信号(信源)转变为一个相对基带频率而言频率非常高的代通信号。该信号称为已调信号,而基带信号称为调制信号。调制可以通过使高频载波随信号幅度的变化而改变载波的幅度、相位或者频率来实现。调制过程用于通信系统的发端。在接收端需将已调信号还原成要传输的原始信号,也就是将基带信号从载波中提取出来以便预定的接受者(信宿)处理和理解的过程。该过程称为解调。

工厂新员工培训心得体会范文 忙碌而又充实的一周又过去了,在和大家共同培训学习的两周时间里,我对“人际关系、机会、竞争”的重要性有了强烈感受,在工作技能和熟练度上也都有了明显提升,对 工作的体会也更为深刻。 在自己进步的同时也有很多不足需要改善,比如工作的紧迫性和高效性;上班时个人 的言行举止;工作时吃苦耐劳的精神等一些细节要多加注意。 通过这两周的培训学习,我将自己的体会和心得整理总结为以下几点: 一、学会在工作中高效的完成每项任务 切斯特菲尔德曾经说过:“效率是做好工作的灵魂。”时间就是金钱,效率就是生命。虽然车间工作重复性很强,很多时候,我们都在重复一样的劳动,但它却不是简单的机械 运动,它需要的不仅仅是冲天的干劲,高涨的激情,更需要聪明的才智去完善和提高,一 定要养成拿到任务时先动脑再动手的好习惯。如此,既能省时间,又能省去许多不必要的 力气,达到事半功倍的效果。 二、团队精神至关重要 在车间的生产中,每一件产品都是通过工人之间的共同协作完成的。一件服装从最初 的设计到最终的成品,这中间都要通过很多道精细的工序才能制作出来,最后检验无误才 可出售。每一步都必须一丝不苟认真负责,任何一个环节出点问题,这件产品就不能出厂。因此,一切成绩都是大家共同努力、协作的结果,个人英雄主义是无法完成的。 三、抓住机遇,实现理想 我们小时候每个人都有自己的理想,并且在成长的过程中为之不懈的努力、追求。而 现在工作了,正是我们实现理想和人生价值的时刻。无论工作、生活,都应该要有合理的 规划,而且一定要付诸行动。作为新进厂的新员工,我们的优点在于丰富的创造力、高涨 的工作激情和干劲,当然也存在很多不足,缺少工作经验、工作技能还不是特别熟练,这 都是我们面临的、必须尽快解决的问题,所以在工作的时候就要抓住每次难得的机会,相 互学习,取长补短,充实并提高自己。 四、责任心是工作的基本要求 “成功者找方法,失败者找借口。”当我们拿到任务的时候,要争取在有限的时间内 把它做到最好。责任心是必不可少的,干一行爱一行,我们必须对自己的工作岗位尽到最 大的责任心,态度决定一切,没有对工作负责、认真的态度,是无法做好自己的本质工作的。如果在工作当中因为失误造成不良后果,我们必须勇于承担责任,不要互相推卸,迅 速想办法去解决,把损失降到最低。

基站维护测试仪 第一章绪言 本章内容包括YBT250基站维护测试仪使用说明以及仪器开 始使用时的一般情况。 1.1 产品说明 本仪器为现场测试蜂窝小区基站最佳的射频测试仪。仪器 是一个基于NetTek测试仪平台模块化的测试仪。其标准结构实际上由两部分组成,仪器模块和NetTek分析仪平台。仪器模块由执行射频分析的硬件和软件构成。NetTek 分析仪平台是在仪器 模块中运行软件的“计算机”。YBT250可作为一个仪器的模块来购买,并加入到Net Tek分析仪平台中。 在NetTek分析仪平台你可附加三个仪器的模块,以扩展仪器 测试功能。仪器模块与平台之间的信息传输是通过内部总线相连。 NetTek分析仪平台是基于Windows CE操作系统。当购买了 PCMCIA以太网和调制解调器卡,可以组网和上网运行。 NetTek分析仪平台产品特点如下: ?带有触摸屏界面的彩色或黑白显示功能 ?模块化仪器结构 ?坚固的外壳 ?可拆装电池块 ?红外通信方式 ?输入/输出端口 ?软件应用以及能支持通信,功率管理,仪器配置,文本编辑,上网浏览等多种用途。 1.2 安装模块 其操作步骤如下: 1.选择Start>Suspend。关闭或悬挂NetTek分析仪平台的电源。 2.断开到分析仪平台的所有电缆连接。 3.利用四角减振器支持来平置分析仪平台。 4.从分析仪平台的背面移走总线门(见下图)。

5.注意下方连接到平台总线连接器的YBT250模块。(见下图) 6.按下,使与总线连接器能稳固安置牢以及确保良好接触。 7. 蝶形螺丝定位,见上图。 8.每个蝶形螺丝,反时针方向向下转动1/4圈,使其能露出。 9.顺时针方向转动螺丝,拧紧。确保均匀拧紧所有螺丝,但不要过 紧。 10.为使蝶形螺丝头隐埋,再使每个螺丝头在顺时针方向上旋转1/4 圈。

通信原理课程设计心得体会 、时分解复用原理 为了提高信道利用率,使多路已抽样的信号组合起来沿同一信道传输而互相不干扰,称时分多路复用。时分复用的解调过程称为时分解复用。目前采用较多的是频分多路解复用和时分多路解复用。频分多路解复用用于模拟通信,而时分多路解复用用于数字通信。为了实现TDM传输,要把传输时间分成若干个时隙,在每个时隙内传输一路信号,将若干个原始的脉冲调制信号在时间上进行交错排列,从而形成一个复合脉冲串,该脉冲串扰码后经信道传输到达接收端。时分解复用通信,是把各路信号在同一信道上占有不同时间间隙进行通信分离出原来的模拟信号。由抽样定理可知,将时间上离散的信号变成时间上连续的信号,其在信道上占用时间的有限性,为多路信号沿同一信道传输提供了条件。时分解复用是建立在抽样定理的基础上的,因为抽样定理连续的基带信号由可能被在时间上离散出现的抽样脉冲所代替.具体说,就是把时间分成一些均匀的时间间隙,将各路信号的传输时间分配在不同的时间间隙,以达到互相分开,互不干扰的目的。抽样脉冲占据时间一般较短,在抽样脉冲之间就留出间隙.利用这些空隙便可以传输其他信号的抽样,因此,就可能用一条信道同时传送若干个基带信号,并且每一个抽

样值占用的时间越短,能够传输的数据也就越多.时分解复用信号在接收端只要在时间上恰当地进行分离,各个信号就能分别互相分开,互不干扰并不失真地还原出原来的模拟信号。 在通信系统中,同步具有相当重要的地位。通信系统能否具有有效、可靠地工作,在很大程度上依赖有无良好的同步系统。同步可分为载波同步、位同步、帧同步和网同步几大类型。他们在通信系统中都具有相当重要的作用。时分解复用通信中的同步技术包括位同步和帧同步,这是数字通信的又一个重要特点。时分解复用的电路原理就是先通过帧同步信号和位同步信号把各路信号数据分开,然后通过移位寄存器构成的并/串转换电路输出串行的数据,把时分复用的调制信号不失真的分离出来。 位同步 位同步的目的是确定数字通信中的个码元的抽样时刻,即把每个码元加以区分,使接受端得到一连串的码元序列,这一连串的码元列代表一定的信息。位同步是最基本的同步,是实现帧同步的前提。位同步的基本含义是收、发两端机的时钟频率必须同频、同相,这样接收端才能正确接收和判决发送端送来的每一个码元。因此,接收端必须提供一个确定抽样判决时刻的定时脉冲序列.

2015工厂新员工培训计划 第1篇:工厂新员工培训计划 一、新员工培训目的 1、为新员工提供正确的、相关的公司及工作岗位信息,鼓励新员工的士气 2、让新员工了解公司所能提供给他的相关工作情况及公司对他的期望 3、让新员工了解公司历史、政策、企业文化,提供讨论的平台 4、让新员工感受到公司对他的欢迎,让新员工体会到归属感 5、使新员工更进一步明白自己工作的职责、加强同事之间的关系 二、新员工培训内容 一)、就职前的培训(由部门经理负责) 主要是对新员工的到来表示欢迎,指定新员工工作部门的经理或组长作为新员工贴身学习的辅导老师,解答新员工提出的问题。 二)、部门岗位培训(新员工实际工作部门负责) 介绍新员工认识本部门员工;参观工作部门;介绍部门环境与工作内容、部门内的特殊规定;讲解新员工岗位职责要求、工作流程以及工作待遇,指定1名老职工带教新员工;1周内部门负责人与新员工进行交换意见,重申工作职责,指出新员工工作中出现的问题,回答新员工的提问;对新员工1周的表现进行评估,给新员工下一步工作提出一些具体要求。 三)、公司整体培训(内部培训师负责) 分发《员工培训手册》——(简述公司的历史与现状,描述公司在XX市地理位置,交通情况;公司历史与发展前景,公司的企业文化与经营理念;公司组织结构及主要领导,公司各部门职能介绍,主要服务对象,服务内容,服务质量标准等;公司有关政策与福利,公司有关规章制度,员工合理化建议采纳的渠道;解答新员工提出的问题。) 三、培训对象 XXX公司全体新进员工。 四、新员工培训教材 《员工培训手册》、《XXX公司规章制度》 五、培训地点 公司办公大楼。 六、培训时间 公司可根据员工实际情况安排,一般7天为宜。 七、新员工培训实施 1、召集公司负责培训人员,就有关公司新职工培训实施方案,征求与会者意见,完善培训方案。 2、尽快拿出具有针对性的培训教材,落实培训人选,配合公司组建从上至下的培训管理网络。 3、公司内部宣传"新员工培训方案",通过多种形式让全体职工了解这套新员工培训系统,宣传开展新员工培训工作的重要意义。 4、所有新员工在正式上岗前,都必须在公司集中培训1次(培训内容见中心岗前培训),然后再到具体工作部门进行培训(培训内容见部门岗位培训),公司可根据新员工基本情况实施相应的培训教材,培训合格发放结业证书,培训合格名单报集团人力资源部。 八、培训反馈与考核 1、培训所进行的公司→部门培训应在公司选定培训师指导下进行,公司每培训一

通信原理 实 验 报 告

实验一 数字基带信号实验(AMI/HDB3) 一、 实验目的 1、了解单极性码、双极性码、归零码、不归零码等基带信号波形特点 2、掌握AMI 、HDB 3的编码规则 3、掌握从HDB 3码信号中提取位同步信号的方法 4、掌握集中插入帧同步码时分复用信号的帧结构特点 5、了解HDB 3(AMI )编译码集成电路CD22103 二、 实验内容 1、用示波器观察单极性非归零码(NRZ )、传号交替反转码(AMI )、三阶高密度 双极性码(HDB 3)、整流后的AMI 码及整流后的HDB 3码 2、用示波器观察从HDB 3/AMI 码中提取位同步信号的波形 3、用示波器观察HDB 3、AMI 译码输出波形 三、 基本原理 本实验使用数字信源模块(EL-TS-M6)、AMI/HDB 3编译码模块(EL-TS-M6)。 BS S5S4S3S2S1 BS-OUT NRZ-OUT CLK 并 行 码 产 生 器 八选一 八选一八选一分 频 器 三选一 NRZ 抽 样 晶振 FS 倒相器 图1-1 数字信源方框图 010×0111××××××××× ×××××××数据2 数据1 帧同步码 无定义位 图1-2 帧结构 四、实验步骤 1、 熟悉信源模块和HDB3/AMI 编译码模块的工作原理。 2、 插上模块(EL-TS-M6),打开电源。用示波器观察数字信源模块上的各种信号波形。 用FS 作为示波器的外同步信号,进行下列观察: (1) 示波器的两个通道探头分别接NRZ-OUT 和BS-OUT ,对照发光二极管的发光状态,判断数字信源单元是否已正常工作(1码对应的发光管亮,0码对应的发光管熄);

电修车间级岗前安全培训内容 一、工作环境及危险因素 A、工作环境 (1)维修电工:炼铁厂所属区域各高低压配、送、用电设备;(2)风机工:高炉、烧结区域; B、危险因素 (1)炼铁厂所属区域各高低压配、送、用电设备存在的危险因素: A、高炉烧结煤气放散区,为易燃、易爆、气体中毒危险区 B、高炉、烧结各系统电缆沟内电缆发热、短路会造成火灾停电等电器事故。 C、高炉、烧结供电变压器在过载或故障情况下易发生瓦斯气体及着火爆炸。 D、高炉、烧结、高低压配电室存在人员触电,电缆、电气着火, 电缆电气爆炸等危险因素。 (2)高炉、烧结、除尘风机设备区域存在:煤气中毒风机叶飞出,电机着火、爆炸。 (3)高炉、烧结除尘设备区域存在:煤气中毒风机叶飞出,电机着火、爆炸;电场顶部有硅整流高压变压器,电压高,易发生触电事故,高空坠落、电场内有煤气中毒和高压触电危险。 二、所从事工种可能遭受的职业伤害和伤亡事故 (1)维修电工:可能遭受的职业伤害和伤亡事故有: A、触电、电弧伤害

由于操作不当或违反电力安全操作规程;或检修时不开具安全检修作业票,或不严格执行停机检修挂牌制度;点检时,不是两人以上进行,没有保持足够的安全距离、检修时,不做好停电、验电、放电、挂接地线等安全措施,不与相关人员联系好;各高低压开关柜停送电操作时,不认真填写工作票而引发触电事故。 B、高空坠落 在高空作业时,劳保穿戴不齐全,衣着不灵便紧凑,登高时不注意脚下站稳。不系安全带,或系安全带不正确使用,不检查安全带的可靠性;经过各种楼梯或在超过2米以上工作时,不注意脚下站稳,不慢上慢下,不遵循高挂低用的原则,不采取安全防护措施而引发安全事故。 C、煤气中毒 电器设备遍布炼铁厂区域,高炉炉顶、烧结点火炉、热风炉、喷煤等区域,以及各种煤气管线放散区都极有能发生煤气泄漏;巡检或检修时,不按要求配带煤气报警仪,监测CO的浓度,在煤气区域长时间逗留,而引发煤气中毒。 D、机械伤害 不按规定操作,机械运转时,进行检修作业;撤卸电机或大型电器设备时,不采取安全措施,砸伤、碰伤等。 三、所从事工种的安全职责、操作技能、及强制性标准 1、维修电工:《电工安全技术操作规程》 1)电工必须经过培训,持证上岗,身体具备无妨碍工作的病症。

日本目黑MSW—7125A扫频仪 使用指南 (一):仪器能够提供的具体指标为: 1.包括 IF(455KHz/10.7MHz),LW,MW,SW,FM波段 2.具有窄频与宽频扫频功能 3.扫频范围 455KHz/10.7MHz/0.1-3MHz/1.5-30MHz/63-110MHz 4.扫频宽度 10KHz-36MHz 5.输出电平(50欧负载) 100dBu(0.1rms)准确度±1dB 输出控制 80dB(1dB/每步进) 6.频率可变范围扫描范围内任意的5个频率点 7.设定方式(存储方式) 4位或5位最小设定位数 0.1KHz/1KHz/10KHz 8.显像管 23cm(9英寸)电磁偏转,垂直灵敏度 1mV/格,可变,附有20dB衰减器 9.频率响应 DC-10KHz 10.外形尺寸/重量约230W*330H*370Dmm/10.5kg (二)面板上各键及各位置功能 1、显示屏显示测试波形,这个部位无需操作 2、显示屏下部的左边一排灯:每个灯的上面都有一个波段代号 “455KHz”,“10.7MHz”,“LW-MW”,“SW”,“FM”,这排灯的左边标注着“band”意即波段的意思。在工作状态,这排灯肯定会有一个会点亮,表示当前工作在某一个波段。

BAND (波段)455KHZ 10.7MHZ LW-MW SW FM CHANNEL(通道号)1、2 、3、4、5 左边一排灯的下面有一排按键,共六个。每一个按键上方都有一个数字,从左往右依次为1,2,3,4,5,6,键左边标识有“CHANNEL”的字样,表示通道号。每个按键的中间都有一个小灯,当您按下某一个键时它中间的那颗灯就会点亮,告知您已经工作于此通道状态了。 3、通道的按键下面有两个稍微大些的黑色旋钮 左边的旋钮上边标识有“Y-GAIN”,工作时拧动它可以调节显示屏上显示曲线的幅度值,免得这根曲线太大跑到显示屏的外边或太小我们看不清楚,当这个钮拧到最大位置(顺时针旋到底)的时候,如果没有衰减的话垂直的幅度就是显示屏上1个厘米的长度代表1个毫伏特的电压。 如果这个旋钮不在最大位置而是中间某个位置?我们就要计算。在“Y-GAIN”钮的右下方有两个小小的可以拨来拨去的钮?正常工作的时候,一般都是拨在“OFF”的位置上,如果拨到另一边“0.1”的位置时,此时显示屏上当出现两条竖线,这个竖线的在显示屏上的长度值如果没有受到衰减的话,代表了0.1Vpp的信号在显示屏的长度,当您拧动上面“Y-GAIN”的钮时这个竖线的长度也会跟着变化,但不管它有多长,始终是代表了0.1Vpp的信号应该具有的长度,记住这个0.1Vpp信号的长度后,再把这个小开关拨回“OFF”的位置,拨回去后一定不要再去拧“Y-GAIN”这个钮了,此时再看显示屏上

中南大学《通信原理》 实验设计报告 学院: 专业班级: 姓名: 学号: 指导老师: 设计时间:

目录 第一部分硬件部分实验报告 实验一:模拟锁相环与载波同步 (1) 实验五:数字锁相环与位同步 (6) 实验六:帧同步 (13) 实验七:时分复用数字基带通信系统 (17) 第二部分实验设计部分 设计任务与要求 (22) 方案设计与论证 (22) 源程序与仿真结果 (24) 系统性能分析 (29) 程序调试 (29) 结论与心得 (30) 参考文献 (31)

第一部分硬件部分实验报告 实验一:模拟锁相环与载波同步 一、实验目的 1. 掌握模拟锁相环的工作原理,以及环路的锁定状态、失锁状态、同步带、捕捉带等基本概念。 2. 掌握用平方环法从2DPSK信号中提取相干载波的原理及模拟锁相环的设计方法。 3. 了解相干载波相位模糊现象产生的原因。 二、实验内容 1. 观察模拟锁相环的锁定状态、失锁状态及捕捉过程。 2. 观察环路的捕捉带和同步带。 3. 用平方环法从2DPSK信号中提取载波同步信号,观察相位模糊现象。 三、基本原理 通信系统中常用平方环或同相正交环(科斯塔斯环)从2DPSK信号中提取相干载波。本实验系统的载波同步提取模块用平方环,原理方框图如图3-1所示,电原理图如图3-2所示(见附录)。模块内部使用+5V、+12V、-12V电压,所需的2DPSK输入信号已在实验电路板上与数字调制单元2DPSK输出信号连在一起。 图3-1 载波同步方框图 本模块上有以下测试点及输入输出点: ? MU平方器输出测试点,VP-P>1V ? VCO VCO输出信号测试点,VP-P>0.2V ? Ud鉴相器输出信号测试点 ? CAR-OUT 相干载波信号输出点/测试点 图3-1中各单元与电路板上主要元器件的对应关系如下: ? 平方器 U25:模拟乘法器MC1496

工厂车间新员工安全培训的三级培训新员工安全培训的要求 为保证进入车间的每一位新员工都能顺利、及时、有效的进行安全培训,特制定此规定。 一、培训对象 所有新员工上岗前必须进行安全培训。 生管部、仓储部、物流部、工程部新入职员工及从其它部门调入到以上部门的员工。二、培训方式 培训方式由培训人根据需培训人员人数决定,可采取讲解、录像、幻灯、现场演示 等。 三、培训阶段划分 培训分为公司培训、车间培训、班组培训三大项。 四、培训内容 1、公司培训内容 A、安全生产管理制度:公司防火制度、吸烟管理制度、消防安全管理办法、员 工车辆管理规定、网络管理规定。 B、员工安全生产职责 C、公司安全禁令 D、安全事故案例宣导 2、车间培训内容 A、应急情况处理:火灾应急处理、人身伤害应急处理。

B、安全事项。 C、车间安全禁令 D、安全事故安全宣导 3、班组培训内容 A、岗位操作规程 B、设备安全操作要素 C、岗位危害告知与安全注意事项 D、车间安全禁令 E、相关事故案例宣导 五、培训要求 培训内容必须通俗易懂,每个受训员工必须完全理解安全培训内容,安全禁令必 须人手一份,牢记于心。 六、培训流程记录 培训全过程必须使用《员工安全教育档案》进行记录,《员工安全教育档案》由 新入职员工上岗时从人力资源处领取,每一级培训完成后在《员工安全教育档 案》上相应位置签字,并记录时间。 所有培训必须3日内完成,3日内由受训新员工将《员工安全教育档案》上交至 安全专干处。 七、培训跟踪、测试、评估

安全专干不定期对受训新员工培训情况进行抽查、测试,对于培训不合格、员工 存在疑问的可要求相关培训人解答疑问或进行再次培训。 八、相关奖惩规定 1、所有培训内容必须3日内完成,未完成的对相关责任人处以5元合作条罚款, 特殊情况无法完成的须向安全专干说明。 2、每月累计2次以上发生培训不到位情况的处以相关责任人合作条罚款5元。 员工安全教育档案 姓名岗位 级别培训内容培训人 1、安全生产管理制度 2、安全职责 3、安全禁令公司级 4、事故案例 培训时间员工签字 1、应急情况处理 2、安全事项 3、安全防护用品及安全设施使用方法车间级 4、部门及车间安全禁令 培训时间员工签字 1、岗位安全操作规程 2、设备安全操作要素

通信原理实验心得体会 091180024代岳通信工程众所周知,《通信原理》是电子、通信、计算机、自控和信息处理等专业的重要基础课,所以我们通信工程专业的同学在本学期除了平时要上每周2次,每次2节的通信原理理论课程外,还要上每周1次持续3个小时的实验课来帮助我们理解通信原理课的知识,使同学们掌握和熟悉通信系统的基本理论和分析方法,为后续的学习打下良好的基础。 在做本学期的实验前,我以为跟以往的电子类实验差不多,以验证为主,不会很难做,就像以前做物理实验一样,课上按照要求做完实验,然后课后两下子就将实验报告写完,下次课上一交,就OK了。直到做完本学期所有的通信原理实验时,我才知道其实并不容易做,因为自主设计占了很大一部分,需要查找资料和跟不断跟同学讨论问题来解决难点,但学到的知识与难度成正比,使我获益良多. 首先,在做实验前,一定要将课本上的知识吃透,因为这是做实验的基础,否则,在老师讲解时就很可能会听不懂,这将使我们在做实验时的难度加大,浪费课上完成实验的宝贵时间。比如做BPSK自行设计的实验,你要清楚BPSK系统的传输特性以及输入输出序列的原理,如果我们不清楚,在做实验时才去探索讨论,这将使你极大地浪费时间,使你事倍功半。同时,做实验时,一定要亲力亲为,不要钻空子,务必要将每个步骤,每个细节弄清楚,最好能理解明白。在完成实验后,还要进行一定的复习和思考。只有这样,你的才会印象深刻,记得牢固。否则,过后不久,也许是半个学期,就会忘得一干二净,这是很糟糕的

一种情况。在做实验时,老师还会根据自己的经验,将一些课本上没有的知识教给我们,拓宽我们的眼界,使我们认识到通信原理实验的应用是那么的广泛,可以大大增强我们的探索的兴趣。 通过完成本学期的通信原理实验,使我学到了不少实用的通信知识,加深了对通信系统的理解,加强了动手的能力,与理论课完成了很好的互补。更重要的是,在做实验的过程,我们收获了思考问题和解决问题的各种角度以及方法,提高了在实践中研究问题,分析问题和解决问题的能力,这与做其他的实验是通用的,让我受益匪浅,对以后的学习更加有信心。

通信原理实验报告 实验一抽样定理 实验二 CVSD编译码系统实验 实验一抽样定理 一、实验目的 所谓抽样。就是对时间连续的信号隔一定的时间间隔T 抽取一个瞬时幅度值(样值),即x(t)*s(t)=x(t)s(t)。在一个频带限制在(0,f h)内的时间连续信号f(t),如果以小于等于1/(2 f h)的时间间隔对它进行抽样,那么根据这些抽样值就能完全恢复原信号。 抽样定理告诉我们:如果对某一带宽有限的时间连续信号(模拟信号)进行抽样,且抽样速率达到一定数值时,那么根据这些抽样值就能准确地还原信号。这就是说,若要传输模拟信号,不一定要传输模拟信号本身,可以只传输按抽样定理得到的抽样值。 二、功能模块介绍 1.DDS 信号源:位于实验箱的左侧 (1)它可以提供正弦波、三角波等信号,通过连接P03 测试点至PAM 脉冲调幅模块的32P010 作为脉冲幅度调制器的调制信号x(t)。抽样脉冲信号则是通过P09 测试点连至PAM 脉冲调幅模块。 (2)按下复合式按键旋钮SS01,可切换不同的信号输出状态,例如D04D03D02D01=0010 对应的是输出正弦波,每种LED 状态对应一种信号输出,具体实验板上可见。 (3)旋转复合式按键旋钮SS01,可步进式调节输出信号的频率,顺时针旋转频率每步增加100Hz,逆时针减小100Hz。 (4)调节调幅旋钮W01,可改变P03 输出的各种信号幅度。 2.抽样脉冲形成电路模块 它提供有限高度,不同宽度和频率的抽样脉冲序列,可通过P09 测试点连线送到PAM 脉冲调幅模块32P02,作为脉冲幅度调制器的抽样脉冲s(t)。P09 测试点可用于抽样脉冲的连接和测量。该模块提供的抽样脉冲频率可通过旋转SS01 进行调节,占空比为50%。 3.PAM 脉冲调幅模块 它采用模拟开关CD4066 实现脉冲幅度调制。抽样脉冲序列为高电平时,模拟开关导通,有调制信号输出;抽样脉冲序列为低电平,模拟开关断开,无信号输出。因此,本模块实现的是自然抽样。在32TP01 测试点可以测量到已调信号波形。 调制信号和抽样脉冲都需要外接连线输入。已调信号经过PAM 模拟信道(模拟实际信道的惰性)的传输,从32P03 铆孔输出,可能会产生波形失真。PAM 模拟信道电路示意图如下图所示,32W01(R1)电位器可改变模拟信道的传输特性。