用Quartus II Timequest Timing Analyzer进行时序分析:实例讲解 (一)

(2012-06-21 10:25:54)

转载▼

标签:

杂谈

一,概述

用Altera的话来讲,timequest timing analyzer是一个功能强大的,ASIC-style的时序分析工具。采用工业标准--SDC(synopsys design contraints)--的约束、分析和报告方法来验证你的设计是否满足时序设计的要求。在用户的角度,从我使用TimeQuest的经验看,它与IC设计中经常用到的比如prime time,time craft等STA软件是比较类似的。用过prime time或time craft的朋友是非常容易上手的。

在这一系列的文章里,我将会拿一个DAC7512控制器的verilog设计作为例子,详细讲解如何使用TimeQuest进行时序设计和分析。

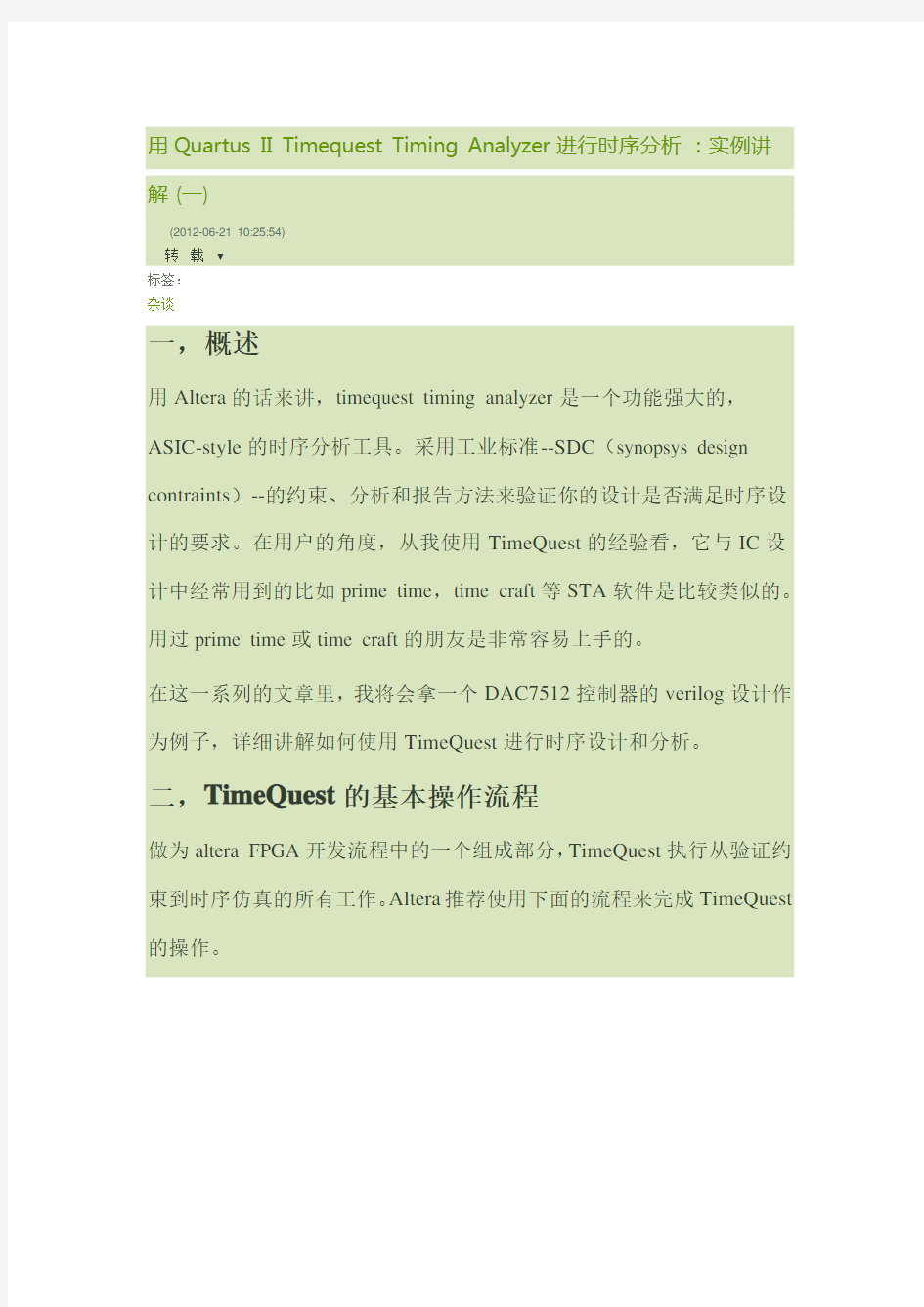

二,TimeQuest的基本操作流程

做为altera FPGA开发流程中的一个组成部分,TimeQuest执行从验证约束到时序仿真的所有工作。Altera推荐使用下面的流程来完成TimeQuest 的操作。

1. 建立项目并加入相关设计文件

不管做什么事情,都需要有一个目标或者说对象。我们用TimeQuest 做时序分析,当然也需要一个对象,这个对象实际上就是我们的设计。所以首先是要建立一个Quartus II的项目,并把所有需要的设计文件都加入到项目中去。需要注意的一点是,这里的设计文件,不仅仅包含逻辑设计相关的文件,也包含已经存在的时序约束文件,当然,需要以synopsys Design Constraints(.sdc)的格式存在的。

2. 对项目进行预编译(initial compilation)

项目建立以后,如果从来没有对项目进行过编译的话,就需要对项目进行预编译。这里的预编译是对应于全编译(full compilation)来讲的,我们可以理解为预编译是对项目进行部分的编译,而全编译是对项目进行完整的编译。做预编译的目的是为了生成一个initial design database,

然后我们可以根据这个database用Timequest采用交互的模式生成时序约束。实际上,对于小的设计,编译时间并不是很长的话,完全可以不去区分预编译和全编译,需要编译的时候,直接做全编译就可以了,做全编译的话,可以生成一个post-fit的database,完全可以给TimeQuest 使用。

3. 向设计中添加时序约束

在用TimeQuest做时序分析之前,必须要指定出对时序的要求,也就是我们通常所说的时序约束。这些约束包括时钟,时序例外(timing exceptions)和输入/输出延时等。

默认情况下,Quartus II 软件会给所有没有被下约束的时钟都设定为1GHz。没有任何的时序例外,也就是说所有的timing path都按1T去check。所有的输入/输出的延迟都按0来计算。这显然不符合绝大多数设计的时序要求,所以有必要根据设计的特性,添加必要的时序约束。

如上所述,时序约束主要包括三类:时钟,时序例外和输入/输出延迟。其中时钟和输入/输出延迟可以认为是在某种程度上增强时序设计的要求。而时序例外可以认为是在某种程度上降低时序设计的要求。比如说,仅仅设定一个时钟的频率为100MHz的话,这个时钟域里所有timing path都需要能工作在100MHz下。这显然是增强了时序设计的要求。可是如果在这个时钟域下面,有部分timing path是不需要做1T的check的,那么就可以通过添加时序例外来避免对这些timing path做1T 的check,即降低了时序设计的要求。

在用TimeQuest做时序分析时,如果非常熟悉设计的构架和对时序的要求,又比较熟悉sdc的相关命令,那么可以直接在sdc文件里输入时序约束的命令。而通常情况下,可以利用TimeQuest GUI提供的设定时序约束的向导添加时序约束。不过要注意的是,用向导生成的时序约束,并不会被直接写到sdc文件里,所以如果要保存这些时序约束,必须在TimeQuest用write sdc的命令来保存所生成的时序约束。

4. 执行完整的编译

在设定好时序约束以后,就需要对整个设计进行完整的编译。在编译过程中,软件会优化设计的逻辑、布局布线等来尽可能满足所有的时序约束。

如果没有添加时序约束,那么软件在编译的时候,会按照默认的时序约束对设计进行优化,对于绝大多数的设计,都会报出来时序的问题,但因为默认的时序约束与设计本身的要求在绝大多数情况下,都是不同的,所以这些时序的问题也并不是设计本身的问题,并没有太多的参考价值,而且很多初学者也不会注意到这个问题。这样就把设计中很多潜在的时序问题给隐藏起来了,最终带来的可能就是系统运行的不稳定,甚至是完全不能运行。

5. 验证时序

当完成编译以后,我们就可以用TimeQuest来验证时序了。在时序分析的过程中,TimeQuest会分析设计中所有的timing path,计算每一条timing path的延时,检查每一条timing path是否满足时序约束,最后按

照positive slack或negative slack来报告时序分析的结果。其中negative slack就表示对应的timing path不满足时序约束的要求(timing violation)。

如果遇到有不满足时序要求的情况,则可以根据对应的时序报告分析设计,确定如何优化设计使之满足时序约束。时序约束有任何变化的话,都需要重新编译设计。这个反复的过程可以让我们解决设计中的时序问题。

三,DAC7512控制器

DAC7512是一个具有三线串行接口的DAC。我们基于FPGA用Verilog语言实现了一个简单的DAC7512的控制器。下面是控制器的结构图:

DAC7512控制器由三个模块组成,PLL用来生成控制器所要的时钟

C0(25MHz)和C1(50MHz),其lock信号用来做为控制器的异步reset。da_data模块生成要送往DAC7512的数据,其中DA_DATA为数据,DA_DATA_EN为数据有效信号,该模块使用C0时钟,整个属于C0

时钟域。DAC7512模块用于将DA_DATA转换成符合DAC7512接口标准的串行数据并送给DAC7512,要用到C1(50MHz)和DA_SCLK(C1二分频,25MHz)两个时钟。

DAC7512控制器一共有四个输入输出端口。CLK_IN为PLL的基准时钟,为25MHz。DA_DIN,DA_SCLK和DA_SYNC为三线串口,都为输出端口。

由于C0,C1是由同一个PLL输出的,DA_SCLK是由C1经二分频得到的,三者之间是同步的,处于同一个clock group中。

DAC7512模块的详细设计资料可参照本博客中“FPGA设计中DAC7512控制的Verilog实现” 的文章。不过要注意一点的是,在串行总线上,DA_DIN是在DA_SCLK的下降沿有效的。把DA_DIN设计为C1时钟域的信号,并控制其值只在DA_SCLK为高电平的时候发生变化。这样可以把DA_DIN与DA_SCLK之间的时序要求转换为DA_DIN 在C1时钟域的时序要求,细节我们会在下面介绍。

四,用TimeQuest对DAC7512控制器进行时序分析在对某个对象下时序约束的时候,首先要能正确识别它,TimeQuest 会对设计中各组成部分根据属性进行归类,我们在下时序约束的时候,可以通过命令查找对应类别的某个对象。

TimeQuest对设计中各组成部分的归类主要有cells,pins,nets和ports 几种。寄存器,门电路等为cells;设计的输入输出端口为ports;寄存器,门电路等的输入输出引脚为pins;ports和pins之间的连线为nets。具体可以参照下图(此图出自Altera Time Quest的使用说明)。

下面我们按照本文第二部分用TimeQuest做时序分析的基本操作流程所描述的流程对DAC7512控制器进行时序分析。

建立和预编译项目的部分相对简单,涉及到的也只是QuartusII的一些基本操作,这里我们就不再做具体的叙述。主要介绍如何向项目中添加时序约束和如何进行时序验证。首先建立一个名称与项目top层名字一致的sdc文件,然后按照下面的步骤添加时序约束。

1. 创建时钟

添加时序约束的第一步就是创建时钟。为了确保STA结果的准确性,必须定义设计中所有的时钟,并指定时钟所有相关参数。TimeQuest支持下面的时钟类型:

a) 基准时钟(Base clocks)

b) 虚拟时钟(Virtual clocks)

c) 多频率时钟(Multifrequency clocks)

d) 生成时钟(Generated clocks)

我们在添加时序约束的时候,首先创建时钟的原因是后面其它的时序约束都要参考相关的时钟的。

基准时钟:

基准时钟是输入到FPGA中的原始输入时钟。与PLLs输出的时钟不同,基准时钟一般是由片外晶振产生的。定义基准时钟的原因是其他生成时钟和时序约束通常都以基准时钟为参照。

很明显,在DAC7512控制器中,CLK_IN是基准时钟。我们用下面的命令来创建这个基准时钟:

create_clock -name CLK_IN -period 40 -waveform {0 20} [get_ports

{CLK_IN}]

其中,create_clock是创建时钟的命令,后面是命令的各种选项。其

中-name CLK_IN选项给出了时钟的名字,即CLK_IN。-period 40给出了时钟的周期,即40ns。-waveform {0 20}给出了时钟的占空比,即50/50。最后的[get_ports {CLK_IN}] 是嵌套的tcl命令,给出了CLK_IN对应的port,实际上也就是CLK_IN的输入引脚。

在sdc文件里添加上述命令后,在quartusII里编译设计,然后通过tools –>TimeQuest Time Aanlyzer命令打开TimeQuest。在TimeQuest的Tasks 窗口,找到Report Clocks,双击之,TimeQuest就会在右边主窗口给出设计中已成功添加的时钟信息。如下图所示,可以看到CLK_IN,其类型为基准时钟,周期为40ns,频率为25MHz,targets项为CLK_IN,即表示这个时钟是连接在CLK_IN端口上的。这说明上面create_clock的命令已经在设计中正确创建了时钟CLK_IN。

实际上对于create_clock命令,我们可以通过quartus II的帮助系统(https://www.doczj.com/doc/336057021.html,/current/),查找它的语法。在QuartusII 的帮助里,可以查找到:

另外,帮助系统里有很详尽的关于该命令的描述,并且给出了各种使用的范例。不仅仅是这一个命令,所有的命令都可以在帮助系统里找到。如果看到一个陌生的命令,或者不知道命令该如何使用,那么最好的办法就是在帮助系统里查找该命令。

PLL时钟:

上面我们创建了基准时钟。下面我们创建PLL输出的时钟。

在Altera的FPGA中,PLL电路是通过ALTPLL的IP库被添加到设计中的。下图是一个典型的ALTPLL的结构图。

从图上可以看到,当我们选定了基准时钟和PLL的参数以后,PLL 的输出c0和c1的参数就随之确定了。所以在QuartusII环境下,可以通过一个简单的命令让软件自动生成PLL输出的时钟的时序约束。derive_pll_clocks

这个命令会自动创建PLL输出的C0和C1的相关时序约束。同样的,在sdc文件里添加该命令,然后编译,在TimeQuest里查看时钟信息。如下图所示,derive_pll_clocks在系统里添加了两个时钟,

PLL1|altpll_component|auto_generated|pll1|clk[0]和

PLL1|altpll_component|auto_generated|pll1|clk[1]。可以看出,时钟是按“PLL层次结构+时钟端口名字”的规则命名的。时钟的类型为created clock,周期频率是在PLL里设定好的。duty_cycle为50/50。Clock source 为PLL1|altpll_component|auto_generated|pll1|inclk[0],实际上就是我们之前定义的CLK_IN。

用derive_pll_clocks命令创建PLL相关的时钟很是方便,但不好的地方就是,时钟的命名太过复杂,我们在添加与此时钟相关的时序约束时,就必须用这种名字很长的时钟,容易出错,且可读性也差。所以建议还是采用create_generated_clock命令来创建PLL的时钟。

create_generated_clock命令的语法如下,可以从quartusII的帮助系统里找到每个参数的详细解释。

[-phase

-source

可以用下面的命令来创建PLL的两个时钟C0和C1。我们把时钟命名为CLK25M和CLK50M,source clock为CLK_IN。

create_generated_clock -name CLK25M -source CLK_IN -duty_cycle

50.000 -multiply_by 1 -master_clock {CLK_IN} [get_pins

{PLL1|altpll_component|auto_generated|pll1|clk[0]}]

create_generated_clock -name CLK50M -source CLK_IN -duty_cycle

50.000 -multiply_by 2 -master_clock {CLK_IN} [get_pins

{PLL1|altpll_component|auto_generated|pll1|clk[1]}]

用这两个命令创建的时钟与derive_pll_clocks命令创建的时钟的本质是一样的,只是给时钟定义了不同的名字。当然我们也可以用derive_pll_clocks中对时钟的命名方式来使用create_generated_clock命令。

同样的,可以按照上面的方法,在TimeQuest里查看创建时钟的结果,如下图所示。

到此为止,我们创建了PLL的基准时钟以及PLL输出的两个时钟CLK25M和CLK50M。

DA_SCLK时钟:

在TimeQuest的Tasks窗口里,选择Report Unconstrained Paths命令,TimeQuest会报告出所有需要下约束但实际并没有约束的情况。在Report里的Unconstrained Path列表下,我们可以查看这个报告。双击Clock Status Summary,就可以在主窗口看到所有时钟的情况。见下图,很明显,软件辨识出DAC7512模块下的DA_SCLK为时钟信号,但是我们并没有对该时钟添加约束,所以用红色将这个时钟显示了出来。下一步我们就来创建这个时钟。

DA_SCLK是用CLK50M通过二分频电路得到的。所以其source clock为CLK50M。但是,我们在使用create_generated_clock命令创建该时钟的时候,在-source的参数里,却不能直接使用CLK50M,而必须使用CLK50M所对应的pin,即

PLL1|altpll_component|auto_generated|pll1|clk[1]。这主要是因为-source

参数只支持pins,ports和registers。

DA_SCLK是由CLK50M通过二分频电路生成的,其代码如下:

reg DA_SCLK;

always @(posedge CLK50M or negedge RESET)

begin

if(~RESET)

DA_SCLK <= 1'b0;

else

DA_SCLK <= ~DA_SCLK;

end

可以看到,本质上DA_SCLK为一个寄存器的输出,所以使用

get_registers命令获取DA_SCLK。DA_SCLK是由CLK50M经二分频电路生成的,所以-divide_by的参数应该是2。

综上所述,用下面的命令创建DA_SCLK:

create_generated_clock -name DA_SCLK -divide_by 2 -source [get_pins {PLL1|altpll_component|auto_generated|pll1|clk[1]}] [get_registers {DAC7512:DAC7512|DA_SCLK} ]

到此为止,DAC7512控制器中所有4个时钟都创建好了。如下图所示:

我们再看TimeQuest中Unconstrained Paths中clock Status Summary,就会发现,所有的时钟都已经被添加了约束。

用Quartus II Timequest Timing Analyzer进行时序分析:实例讲解 (三)

(2012-06-26 10:28:46)

转载▼

标签:

杂谈

上面已经把DAC7512控制器中所有的时钟都创建好了。下面我们再额外讨论一下关于时钟属性方面的一些问题和在做时序分析时的处理方法。

对于具有单一时钟的系统,设计和时序分析都相对简单。但是现在很多设计都有多个甚至几十个时钟乃至更多的时钟。比如说DAC7512控制器,在设计中用到的时钟实际上是有3个,CLK25M,CLK50M和DA_SCLK。在对多时钟设计进行时序分析的时候,我们首先要搞清楚各时钟之间的关系。

当设计中有多个时钟时,时钟之间可能存在三种关系,分别是同步,异步和互斥。

如果两个或者多个时钟具有相同的source和固定的相位差,那么这些时钟是同步时钟。在DAC7512的控制器里,CLK25M,CLK50M和DA_SCLK的source都是CLK_IN,所以可以认为他们三个是同步的。

如果两个或者多个时钟之间没有任何关系,则称之为异步时钟。比如说CLKA来源于晶振A,而CLKB来源于其他系统的输入,CLKA 和CLKB就为异步时钟。对于异步时钟来讲,两个时钟域的时钟沿有可能在任意时刻出现,相互之间不会有任何关系。如果一条timing path的起始点是在CLKA,而终点在CLKB,即这条timing path跨越了CLKA 和CLKB两个时钟域,那么STA软件是不会对该timing path做分析的。实际上这等同于在这两个时钟之间设定了一条false path。

如果两个时钟不会相互作用,那么称这两个时钟为互斥的。举个例子来讲,PCIE GEN2可以工作在GEN1和GEN2两种模式,在GEN1模式下,时钟为125MHz,在GEN2的模式下,时钟为250MHz,但在某一个特定时间里,时钟只可能为125MHz或者250MHz,这两个频率的时钟不会共存,相互之间也不会有相互作用。

下图给出了时钟的三种关系的例子。

做时序分析时,在创建好所有的时钟后,需要定义这些时钟之间的关系。我们可以把同步时钟放到一个group中,然后在定义时钟之间的关系时,可以使用group来定义。在默认情况下,TimeQuest认为设计中所有的时钟都是同步的,并把所有的时钟都放在同一个group里。如果设计中有异步时钟,就需要用命令把异步时钟分组并定义出来。

在TimeQuest里,我们用set_clock_groups来定义时钟的group。下面是命令的语法,更详细的说明请参照quartusII的帮助系统。Syntax s et_clock_groups[-h | -help] [-long_help]

[-asynchronous] [-exclusive]

-group

[-physically_exclusive]

在DAC7512控制器里,CLK25M,CLK50M和DA_SCLK三个时钟是同步时钟。默认情况下,它们已经被软件放到了同一个group里,所以我们不需要对其做任何的处理。

但假设CLK25M属于一个group,而CLK50M和DA_SCLK属于另外一个group,我们就要用set_clock_groups命令把二者设为异步时钟,命令如下:

set_clock_groups -asynchronous -group {CLK25M} -group {CLK50M

DA_SCLK}

我们对比一下把CLK25M设定为CLK50M的异步时钟前后TimeQuest对时序分析的处理情况来看这个命令的作用。下面是在添加这个命令前后TimeQuest中Report clock transfer的结果。

在没有添加这个命令前,软件默认三个时钟都是同步时钟,所以会分析并报告出三个时钟之间所有的timing path。

在添加这个命令以后,软件认为CLK25M和CLK50M/DA_SCLK 是异步时钟,所以就直接将CLK25M和CLK50M/DA_SCLK之间的timing path设为false path。不再做更多的分析。

那如果我们假设CLK25M和CLK50M是互斥时钟的话,又会是什么情况呢?用下面的命令将CLK25M和CLK50M设为互斥时钟:

set_clock_groups -exclusive -group {CLK25M} -group {CLK50M}还是看TimeQuest中Report clock transfer的结果,可以发现

CLK25M和CLK50M之间的timing path都被设定为false path了。

再看一下关于Clock uncertainty的知识

简单的说,Clock uncertainty是指时钟边沿实际到达时间与理论到达时间之间的差异和变化。在做时序分析的时候,是需要加上clock uncertainty来计算timing path的延时的。Clock uncertainty的大小是比较难确定的,在ASIC设计中,clock uncertainty的值往往要根据所使用的工艺,以往项目的经验等各种因素来决定。但在FPGA的设计中,我们能参考的资料不多,特别是对于PLL输出的时钟,因为我们对PLL本身的参数并不是非常的了解,所以很难给出合适的clock uncertainty的值。

在FPGA设计中定义PLL的时候,我们要定义参考时钟的精度,这会直接影响到PLL输出时钟的clock uncertainty的值。如下图所示,25.000MHz即为输入基准时钟的精度。

时序分析基础与时钟约束实例(1) 文中实例配套SF-CY3开发套件。更多内容请参考《SF-CY3 FPGA套件开发指南》。 何谓静态时序分析(STA,Static Timing Analysis)? 首先,设计者应该对FPGA内部的工作方式有一些认识。FPGA的内部结构其实就好比一块PCB板,FPGA的逻辑阵列就好比PCB板上的一些分立元器件。PCB通过导线将具有相关电气特性的信号相连接,FPGA也需要通过内部连线将相关的逻辑节点导通。PCB板上的信号通过任何一个元器件都会产生一定的延时,FPGA的信号通过逻辑门传输也会产生延时。PCB的信号走线有延时,FPGA的信号走线也有延时。这就带来了一系列问题,一个信号从FPGA的一端输入,经过一定的逻辑处理后从FPGA的另一端输出,这期间会产生多大的延时呢?有多个总线信号从FPGA的一端输入,这条总线的各个信号经过逻辑处理后从FPGA 的另一端输出,这条总线的各个信号的延时一致吗?之所以关心这些问题,是因为过长的延时或者一条总线多个信号传输时间的不一致,不仅会影响FPGA本身的性能,而且也会给FPGA之外的电路或者系统带来诸多问题。 言归正传吧,之所以引进静态时序分析的理论也正是基于上述的一些思考。它可以简单的定义为:设计者提出一些特定的时序要求(或者说是添加特定的时序约束),套用特定的时序模型,针对特定的电路进行分析。分析的最终结果当然是要求系统时序满足设计者提出的要求。 下面举一个最简单的例子来说明时序分析的基本概念。假设信号需要从输入到输出在FPGA内部经过一些逻辑延时和路径延时。系统要求这个信号在FPGA内部的延时不能超过15ns,而开发工具在执行过程中找到了如图所示的一些可能的布局布线方式。那么,怎样的布局布线能够达到系统的要求呢?仔细分析一番,发现所有路径的延时可能为14ns、15ns、16ns、17ns、18ns,有两条路径能够满足要求,那么最后的布局布线就会选择满足要求的两条路径之一。 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,即有约束才会有分析。若设计者不添加时序约束,那么时序分析就无从谈起。特权同学常常碰见一些初学者在遇到问题时不问青红皂白就认为是时序问题,实际上只有在添加了时序约束后,系统的时序问题才有可能暴露出来。 下面我们再来看一个例子,我们假设有4个输入信号,经过FPGA内部一些逻辑处理后输出。FPGA内部的布线资源有快有慢之分,好比国道和高速公路。通过高速通道所需要的路径延时假设为3ns-7ns,但只有两条可用;而通过慢速通道的路径延时则>10ns。

Quartus II 中Tsu/Tco 的约束方法 Tsu/Tco 在Quartus II 的报告中有两种不同含义. 1. 片内的Tsu/Tco 是指前级触发器的Tco 和后级触发器的Tsu, 一般来说都是几百ps 级别的. 可以通过“List Paths”命令查看。这里的Tsu/Tco 主要由器件工艺决定, 工作时在受到温度,电压的影响略有变化.(如下图所示) 2. 管脚上的Tsu/Tco 它是保证系统Famx 重要的Timing 元素(如下图示). 比如: 两个芯片之间工作在100MHZ, 因为100M 的周期为10ns, (现忽略PCB 走线的延迟), 如果某信号对FPGA 来说是输入,那么前级芯片的Tco 加上FPGA 的Tsu 就不能够超过10ns. 如果某信号对于FPGA 来说是输出,那么FPGA 的Tco 加上后级芯片的Tsu 也不能够超过10ns. 只有这样,才能够保证片间通信正常。因此对FPGA 的管脚进行适当的Tco/Tsu 的时序约束,是至关

重要的Timing 设计技巧. 管脚上的Tsu/Tco 分为以下三个部分. 1. IOE 走线的延迟. 这个延迟在管脚的Tsu/Tco 延迟中占有相当的比 例,Altera 的器件为了降低Tsu/Tco 在IOE 上的延迟, 专门在IOE 中设置了两种类型的触发器, 即: Fast Input Register(FPGA 的管脚为输入时,优化Tsu), Fast Output Register(FPGA 的管脚为输出时,用于优化Tco) 2. 内部逻辑走线的延迟。在Altera 的FPGA 中, 由若干个基本资源LE 构成一个LAB,比如:StratixGx 是10 个LE 组成一个LAB. LAB 横向和纵向排列形成阵列. 在FPGA 中,以LAB 为基本单元,根据走线长度的不同,分为C4(表示横跨4 个LAB 的走线资源),C8,C16,R4,R8,16,R24 等不同的走线资源,不同的器件支持不同的走线资源。 3. 触发器的Tsu/Tco 的需求,这里的Tsu/Tco, 这是由器件工艺决定的,最小的Tsu/Tco 的要求. 在实际的工作环境中,受温度,电压的变化有微小的变化. 前面提到:对FPGA 的管脚进行适当的Tco/Tsu 的时序约束,是至关重要的Timing 设计技巧.关键是在出了问题的时候,怎么去解决? Quartus II 有四处可以对Tsu/Tco 进行约束. 1. 全局时序约束. 在Quartus II 中执行Assignments→Timing Setting 弹出如下界面.设计者可以根据系统Fmax 的要求去约束Tsu/Tco.

ASIC时序约束、时序分析 2009-11-13 22:13 A 时序约束的概念和基本策略 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPA 综合布线工具调整映射和布局布线过程,使设计达到时序要求。例如用OFFSET_IN_BEFORE约束可以告诉综合布线工具输入信号在以根据这个约束调整与IPAD相连的Logic Circuitry的综合实现过程,使结果满足FFS的建立时间要求。 附加时序约束的一般策略是先附加全局约束,然后对快速和慢速例外路径附加专门约束。附加全局约束时,首先定义设计的所有分组附加周期约束,然后对FPGA/CPLD输入输出PAD附加偏移约束、对全组合逻辑的PAD TO PAD路径附加约束。附加专门约束时速例外路径和多周期路径,以及其他特殊路径。 B 附加约束的基本作用 1. 提高设计的工作频率 对很多数字电路设计来说,提高工作频率非常重要,因为高工作频率意味着高处理能力。通过附加约束可以控制逻辑的综时,从而提高工作频率。 2. 获得正确的时序分析报告 几乎所有的FPGA设计平台都包含静态时序分析工具,利用这类工具可以获得映射或布局布线后的时序分析报告,从而对束作为判断时序是否满足设计要求的标准,因此要求设计者正确输入约束,以便静态时序分析工具输出正确的时序分析 3. 指定FPGA/CPLD引脚位置与电气标准 FPGA/CPLD的可编程特性使电路板设计加工和FPGA/CPLD设计可以同时进行,而不必等FPGA/CPLD引脚位置完全确定,从成后,设计者要根据电路板的走线对FPGA/CPLD加上引脚位置约束,使FPGA/CPLD与电路板正确连接。另外通过约束还特性。为了满足日新月异的通信发展,Xilinx新型FPGA/CPLD可以通过IO引脚约束设置支持诸如 AGP、BLVDS、CTT、G LVPECL、LVDSEXT、LVTTL、 PCI、PCIX、SSTL、ULVDS等丰富的IO接口标准。另外通过区域约束还能在FPGA上规划各个成模块化设计等。 C 周期(PERIOD)的含义 周期的含义是时序中最简单也是最重要的含义,其它很多时序概念会因为软件商不同略有差异,而周期的概念确是最通用的,周期面要讲到的其它时序约束都是建立在周期约束的基础上的,很多其它时序公式,可以用周期公式推导。周期约束是一个基本时序和具根据PERIOD约束检查时钟域内所有同步元件的时序是否满足要求。PERIOD约束会自动处理寄存器时钟端的反相问题,如果相迟将被默认限制为PERIOD约束值的一半。如下图所示, 图1 周期的定义 时钟的最小周期为: TCLK = TCKO +TLOGIC +TNET +TSETUP -TCLK_SKEW TCLK_SKEW =TCD2 -TCD1

如何在FPGA设计环境中加时序约束SDC 在给FPGA做逻辑综合和布局布线时,需要在工具中设定时序的约束。通常,在FPGA设计工具中都FPGA中包含有4种路径:从输入端口到寄存器,从寄存器到寄存器,从寄存器到输出,从输入到输出的纯组合逻辑。通常,需要对这几种路径分别进行约束,以便使设计工具能够得到最优化的结果。下面对这几种路径分别进行讨论: 从输入端口到寄存器: 这种路径的约束是为了让FPGA设计工具能够尽可能的优化从输入端口到第一级寄存器之间的路径延迟,使其能够保证系统时钟可靠的采到从外部芯片到FPGA的信号。约束名称:input delay。约束条件的影响主要有4个因素:外部芯片的Tco,电路板上信号延迟Tpd,FPGA的Tsu/Th,时钟延迟Tclk。Tco的参数通常需要查外部芯片的数据手册。计算公式:input delay = Tco+Tpd+Tsu-Tclk。FPGA的Tsu也需要查FPGA芯片的手册,FPGA速度等级不同,这个参数也不同。Tpd和Tclk需要根据电路板实际的参数来计算。通常,每10 cm的线长可以按照1ns来计算. 例如:系统时钟100MHz,电路板上最大延迟2 ns,时钟最大延迟为1.7 ns,Tco为3 ns,FPGA的Tsu为0.2 ns。那么输入延迟的值:max input delay = 2+3+0.2-1.7=3.5 ns。这个参数的含义是指让FPGA 的设计工具把FPGA的输入端口到第一级寄存器之间的路径延迟(包括门延迟和线延迟)控制在10 ns - 3.5 ns = 6.5 ns 以内。对于min input delay,则类似考虑FPGA寄存器的Th参数等。 寄存器到寄存器: 这种路径的约束是为了让FPGA设计工具能够优化FPGA内寄存器到寄存器之间的路径(register-to-register),使其延迟时间必须小于时钟周期,这样才能确保信号被可靠的传递。由于这种路径只存在于FPGA内部,通常通过设定时钟频率的方式就可以对其进行约束。对于更深入的优化方法,还可以采用对寄存器的输入和寄存器的输出加入适当的约束,来使逻辑综合器和布线器能够对某条路径进行特别的优化。还可以通过设定最大扇出数来迫使工具对其进行逻辑复制,减少扇出数量,提高性能。

在进行FPGA的设计时,经常会需要在综合、实现的阶段添加约束,以便能够控制综合、实现过程,使设计满足我们需要的运行速度、引脚位置等要求。通常的做法是设计编写约束文件并导入到综合实现工具,在进行FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。 一、周期约束 周期约束是Xilinx FPGA 时序约束中最常见的约束方式。它附加在时钟网线上,时序分析工具会根据周期约束来检查时钟域内所有同步元件的时序是否满足需求。周期约束会自动的寄存器时钟端的反相。如果相邻的两个元件的时钟相位是相反的,那么它们之间的延迟将被默认的限制成周期约束的一半。 在进行周期约束之前,必须对电路的时钟周期明了,这样才不会出现约束过松或者过紧的现象。一般情况下,设计电路所能达到的最高运行频率取决于同步元件本身的Setup Time 和Hold Time,以及同步元件之间的逻辑和布线延迟。周期约束一般是使用下面的约束方法: 1、period_item PERIOD=period {HIGH|LOW} [high_or low_item] 其中,period_item可以是NET或TIMEGRP,分别代表时钟线名称net name或元件分组名称group-name。用NET表示PERIOD约束作用到名为“net name”的时钟网线所驱动的同步元件上,用TIMEGRP表示PERIOD约束作用到TIMEGRP所定义的分组(包括FFS、LATCH和RAM等同步元件)上。period是目标时钟周期,单位可以是ps、ns、μS和ms 等。HIGH|LOW指出时钟周期中的第1个脉冲是高电平还是低电平,high or low time为HIGH LOW指定的脉冲的持续时间,默认单位是ns。如果没有该参数,时钟占空比是50%。例如,NET SYS_CLK PERIOD=10 ns HIGH 4ns 2、NET“clock net name”TNM_NET=“timing group name”; TIMESPEC“TSidentifier”=PERIOD “TNM reference”period {HIGH | LOW} [high or low item]INPUT_JITTER value; 很多时候为了能够定义比较复杂的派生关系的时钟周期,就要使用该方法。其中TIMESPEC在时序约束中作为一个标识符表示本约束为时序规范;TSidentifier包括字母TS和一个标识符identifier共同作为一个TS属性;TNM reference指定了时序约束是附加在哪一个组上,一般情况下加在TNM_NET定义的分组上。HIGH | LOW 指的是时钟的初始相位表明第一个时钟是上升沿还是下降沿;high or low item 表示的是时钟占空比,即就是high或者low的时间,默认为1:1, INPUT_JITTER 表示的是时钟的抖动时间,时钟会在这个时间范围内抖动,默认单元为ps。比如周期约束: NET "ex_clk200m_p" TNM_NET = TNM_clk200_p; TIMESPEC "TS_clk200_p" = PERIOD "TNM_clk200_p" 5.000 ns HIGH 50 %; 建立一个TNM_clk200_p的时序分组,包括时钟网络ex_clk200m_p驱动的所有同步

很多人发贴,来信询问关于约束、时序分析的问题,比如: 如何设置setup,hold时间?如何使用全局时钟和第二全局时钟(长线资源)?如何进行分组约束?如何约束某部分组合逻辑?如何通过约束保证异步时钟域之间的数据交换可靠?如何使用I/O逻辑单元内部的寄存器资源?如何进行物理区域约束,完成物理综合和物理实现?等等。。。 为了解决大家的疑难,我们将逐一讨论这些问题。 今天先讨论一下约束的作用? 有些人不知道何时该添加约束,何时不需要添加?有些人认为低速设计不需要时序约束?关于这些问题,希望下面关于约束作用的论述能够有所帮助!附加约束的基本作用有3: (1)提高设计的工作频率 对很多数字电路设计来说,提高工作频率非常重要,因为高工作频率意味着高处理能力。通过附加约束可以控制逻辑的综合、映射、布局和布线,以减小逻辑和布线延时,从而提高工作频率。 (2)获得正确的时序分析报告 几乎所有的FPGA设计平台都包含静态时序分析工具,利用这类工具可以获得映射或布局布线后的时序分析报告,从而对设计的性能做出评估。静态时序分析工具以约束作为判断时序是否满足设计要求的标准,因此要求设计者正确输入约束,以便静态时序分析工具输出正确的时序分析报告。 (3)指定FPGA/CPLD引脚位置与电气标准 FPGA/CPLD的可编程特性使电路板设计加工和FPGA/CPLD设计可以同时进行,而不必等FPGA/CPLD引脚位置完全确定,从而节省了系统开发时间。这样,电路板加工完成后,设计者要根据电路板的走线对FPGA/CPLD加上引脚位置约束,使FPGA/CPLD与电路板正确连接。另外通过约束还可以指定IO引脚所支持的接口标准和其他电气特性。为了满足日新月异的通信发展,Xilinx新型FPGA/CPLD可以通过IO引脚约束设置支持诸如AGP、BLVDS、CTT、GTL、

ISE时序约束笔记 ISE时序约束笔记1——Global Timing Constraints 时序约束和你的工程 执行工具不会试图寻找达到最快速的布局&布线路径。——取而代之的是,执行工具会努力达到你所期望的性能要求。 性能要求和时序约束相关——时许约束通过将逻辑元件放置的更近一些以缩短布线资源从而改善设计性能。 没有时序约束的例子 该工程没有时序约束和管脚分配 ——注意它的管脚和放置 ——该设计的系统时钟频率能够跑到50M 时序约束的例子

和上面是相同的一个设计,但是加入了3个全局时序约束。 ——它最高能跑到60M的系统时钟频率 ——注意它大部分的逻辑的布局更靠近器件边沿其相应管脚的位置 更多关于时序约束 时序约束应该用于界定设计的性能目标 1.太紧的约束将会延长编译时间 2.不现实的约束可能导致执行工具罢工 3.查看综合报告或者映射后静态时序报告以决定你的约束是否现实 执行后,查看布局布线后静态时序报告以决定是否你的性能要求达到了——如果约束要求没有达到,查看时序报告寻找原因。 路径终点 有两种类型的路径终点: 1.I/O pads 2.同步单元(触发器,锁存器,RAMs) 时序约束的两个步骤: 1.路径终点生产groups(顾名思义就是进行分组) 2.指点不同groups之间的时序要求 全局约束使用默认的路径终点groups——即所有的触发器、I/O pads等 ISE时序约束笔记2——Global Timing Constraints 问题思考 单一的全局约束可以覆盖多延时路径 如果箭头是待约束路径,那么什么是路径终点呢? 所有的寄存器是否有一些共同点呢?

XILINX时序约束使用指南笔记 第一章 时序约束介绍 第二章 时序约束方法 第三章 时序约束原则 第四章 在XST中指定时序约束 第五章 在Synplify中指定时序约束方法 第六章 时序约束分析

第一章 时序约束介绍 基本的时序约束包括: “PERIOD Constraints” “OFFSET Constraints” “FROM:TO(Multi‐Cycle)约束”

第二章 时序约束方法 1,简介: 2,基本的约束方法 根据覆盖的路径不同,时序要求变成一些不同的全局约束。 最普通的路径类型包括: 1,输入路径 2,同步元件到同步元件路径 3,指定路径 4,输出路径 XILINX的时序约束与每一种全局约束类型都有关。最有效的方法就是一开始就指定全局约束然后再加上指定路径的约束。在很多案例中,只要全局约束就可满足需求。 FPGA器件执行工具都是由指定的时序要求驱动的。如果时序约束过头的话,就会导致内存使用增加,工具运行时间增加。更重要的是,过约束还会导致性能下降。因此,推荐使用实际设计要求的约束值。 3,输入时序约束 输入时序约束包括2种 “系统同步输入” “源同步输入” 输入时钟约束覆盖了输入数据的FPGA外部引脚到获取此数据的寄存器之间的路径。输入时钟约束经常用”OFFSET IN”约束。指定输入时钟要求的最好方法,取决于接口的类型(源/系统同步)和接口是SDR还是DDR。 OFFSET IN定义了数据和在FPGA引脚抓取此数据的时钟沿之间的关系。在分析OFFSET IN 约束时,时序分析工具自动将影响时钟和数据延迟的因素考虑进去。这些因素包括: 时钟的频率和相位转换 时钟的不确定 数据延迟调整 除了自动调整,还可以在与接口时钟相关的”PERIOD”约束中另外增加时钟不确定。 关于增加”INPUT_JITTER”的更多信息,参见第三章的”PERIOD Constraints”。 “OFFSET IN”与单输入时钟有关,默认情况下,OFFSET IN约束覆盖了从输入pad到内部同步元件之间的所有路径。用于抓取那些从pad输入的数据的同步元件由指定的OFFSET IN 时钟触发。应用OFFSET IN约束被称为”global”方法。这是指定输入时序的最有效的方法。 系统同步输入 在体统同步接口中,发送和抓取数据共用一个系统时钟。板上的布线延迟和时钟倾斜限制了接口的工作频率。更低的频率也会导致系统同步输入接口典型的采用SDR应用。 系统同步SDR应用例子,见图2‐1。系统同步SDR应用中,在时钟上升沿从源器件发送

XDC约束技巧之时钟篇 Xilinx?的新一代设计套件Vivado中引入了全新的约束文件XDC,在很多规则和技 巧上都跟上一代产品ISE中支持的UCF大不相同,给使用者带来许多额外挑战。Xilinx工 具专家告诉你,其实用好XDC很容易,只需掌握几点核心技巧,并且时刻牢记:XDC的 语法其实就是Tcl语言。 XDC的优势 XDC是Xilinx Design Constraints的简写,但其基础语法来源于业界统一的约束规范SDC(最早由Synopsys公司提出,故名Synopsys Design Constraints)。所以SDC、XDC 跟Vivado Tcl的关系如下图所示。 XDC的主要优势包括: 1.统一了前后端约束格式,便于管理; 2.可以像命令一样实时录入并执行; 3.允许增量设置约束,加速调试效率; 4.覆盖率高,可扩展性好,效率高; 5.业界统一,兼容性好,可移植性强; XDC在本质上就是Tcl语言,但其仅支持基本的Tcl语法如变量、列表和运算符等等,对其它复杂的循环以及文件I/O等语法可以通过在Vivado中source一个Tcl文件的方式来 补充。(对Tcl话题感兴趣的读者可以参考作者的另一篇文章《Tcl在Vivado中的应用》)XDC与UCF的最主要区别有两点: 1.XDC可以像UCF一样作为一个整体文件被工具读入,也可以在实现过程中被当作一个个单独的命令直接执行。这就决定了XDC也具有Tcl命令的特点,即后面输入的约束在有冲突的情况下会覆盖之前输入的约束(时序例外的优先级会在下节详述)。另外,不同于UCF是全部读入再处理的方式,在XDC中,约束是读一条执行一条,所以先后顺序很重要,例如要设置IO约束之前,相对应的clock一定要先创建好。

Support of SDC Timing Constraints 1. Clock(时钟): create_clock命令为任何register, port或pin进行时钟特性描述,使其具有独一的时钟特性。 create_clock-period

用Quartus II Timequest Timing Analyzer进行时序分析:实例讲解 (一) (2012-06-21 10:25:54) 转载▼ 标签: 杂谈 一,概述 用Altera的话来讲,timequest timing analyzer是一个功能强大的,ASIC-style的时序分析工具。采用工业标准--SDC(synopsys design contraints)--的约束、分析和报告方法来验证你的设计是否满足时序设计的要求。在用户的角度,从我使用TimeQuest的经验看,它与IC设计中经常用到的比如prime time,time craft等STA软件是比较类似的。用过prime time或time craft的朋友是非常容易上手的。 在这一系列的文章里,我将会拿一个DAC7512控制器的verilog设计作为例子,详细讲解如何使用TimeQuest进行时序设计和分析。 二,TimeQuest的基本操作流程 做为altera FPGA开发流程中的一个组成部分,TimeQuest执行从验证约束到时序仿真的所有工作。Altera推荐使用下面的流程来完成TimeQuest 的操作。

1. 建立项目并加入相关设计文件 不管做什么事情,都需要有一个目标或者说对象。我们用TimeQuest 做时序分析,当然也需要一个对象,这个对象实际上就是我们的设计。所以首先是要建立一个Quartus II的项目,并把所有需要的设计文件都加入到项目中去。需要注意的一点是,这里的设计文件,不仅仅包含逻辑设计相关的文件,也包含已经存在的时序约束文件,当然,需要以synopsys Design Constraints(.sdc)的格式存在的。 2. 对项目进行预编译(initial compilation) 项目建立以后,如果从来没有对项目进行过编译的话,就需要对项目进行预编译。这里的预编译是对应于全编译(full compilation)来讲的,我们可以理解为预编译是对项目进行部分的编译,而全编译是对项目进行完整的编译。做预编译的目的是为了生成一个initial design database,

Quartus II Handbook, Volume 3 6-28 时钟约束(Clock Specification): 约束所有时钟(包括你的设计中特有的时钟)对准确的时序分析结果而言是必不可少的。Quartus II TimeQuest Timing Analyzer为各种各样的时钟配置和典型时钟提供许多SDC命令。 这个章节将介绍SDC可用的应用编程接口,以及描述指定的时钟特性。 时钟(Clocks) 使用create_clock命令为任何register, port或pin进行时钟特性描述,使其具有独一的时钟特性。例6–2展示了create_clock命令: Example 6–2. create_clock Command create_clock -period

Example 6–3. 100MHz Clock Creation create_clock –period 10 –waveform { 0 5 } clk Example 6–4和上例相差90度的相位。 Example 6–4. 100MHz Shifted by 90 Degrees Clock Creation create_clock –period 10 –waveform { 2.5 7.5 } clk_sys 使用create_clock命令约束时钟缺省的source Latency值为0。Quartus II TimeQuest Timing Analyzer自动为非虚拟时钟(non-virtual clocks)计算时钟网络延时(clock’s network latency)。 Quartus II Handbook, Volume 3 6-29 生成时钟(Generated Clocks) Quartus II TimeQuest Timing Analyzer可以把修改或改变主时钟(或者引入时钟)特性的分频时钟、波纹时钟和电路作为生成时钟。 你可以定义这些电路的输出作为生成时钟。这些定义可以让Quartus II TimeQuest Timing Analyzer分析这些时钟以及关联的时钟网络延时(network latency)。 使用create_generated_clock命令定义生成时钟。 Example 6–5. create_generated_clock Command create_generated_clock [-name

第1章FPGA中IO口时序分析 作者:屋檐下的龙卷风 博客地址:https://www.doczj.com/doc/336057021.html,/linjie-swust/ 日期:2012.3.1 1.1 概述 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。 1.2 FPGA整体概念 由于IO口时序约束分析是针对于电路板整个系统进行时序分析,所以FPGA需要作为一个整体分析,其中包括FPGA的建立时间、保持时间以及传输延时。传统的建立时间、保持时间以及传输延时都是针对寄存器形式的分析。但是针对整个系统FPGA的建立时间保持时间可以简化。 图1.1 FPGA整体时序图 如图1.1所示,为分解的FPGA内部寄存器的性能参数: (1) Tdin为从FPGA的IO口到FPGA内部寄存器输入端的延时; (2) Tclk为从FPGA的IO口到FPGA内部寄存器时钟端的延时; (3) Tus/Th为FPGA内部寄存器的建立时间和保持时间; (4) Tco为FPGA内部寄存器传输时间; (5) Tout为从FPGA寄存器输出到IO口输出的延时; 对于整个FPGA系统分析,可以重新定义这些参数:FPGA建立时间可以定义为:(1) FPGA建立时间:FTsu = Tdin + Tsu – Tclk; (2) FPGA保持时间:FTh = Th + Tclk; (3) FPGA数据传输时间:FTco = Tclk + Tco + Tout; 由上分析当FPGA成为一个系统后即可进行IO时序分析了。FPGA模型变为如图1.2所示。

入门:FPGA时序分析基础与时钟约束实例 2013-07-16 何谓静态时序分析(STA,Static Timing Analysis)? 首先,设计者应该对FPGA内部的工作方式有一些认识。FPGA的内部结构其实就好比一块PCB 板,FPGA的逻辑阵列就好比PCB板上的一些分立元器件。PCB通过导线将具有相关电气特性的信号相连接,FPGA也需要通过内部连线将相关的逻辑节点导通。PCB板上的信号通过任何一个元器件都会产生一定的延时,FPGA的信号通过逻辑门传输也会产生延时。PCB的信号走线有延时,FPGA的信号走线也有延时。这就带来了一系列问题,一个信号从FPGA的一端输入,经过一定的逻辑处理后从FPGA的另一端输出,这期间会产生多大的延时呢?有多个总线信号从FPGA的一端输入,这条总线的各个信号经过逻辑处理后从FPGA的另一端输出,这条总线的各个信号的延时一致吗?之所以关心这些问题,是因为过长的延时或者一条总线多个信号传输时间的不一致,不仅会影响FPGA本身的性能,而且也会给FPGA之外的电路或者系统带来诸多问题。 言归正传吧,之所以引进静态时序分析的理论也正是基于上述的一些思考。它可以简单的定义为:设计者提出一些特定的时序要求(或者说是添加特定的时序约束),套用特定的时序模型,针对特定的电路进行分析。分析的最终结果当然是要求系统时序满足设计者提出的要求。 下面举一个最简单的例子来说明时序分析的基本概念。假设信号需要从输入到输出在FPGA内部经过一些逻辑延时和路径延时。系统要求这个信号在FPGA内部的延时不能超过15ns,而开发工具在执行过程中找到了如图所示的一些可能的布局布线方式。那么,怎样的布局布线能够达到系统的要求呢?仔细分析一番,发现所有路径的延时可能为14ns、15ns、16ns、17ns、18ns,有两条路径能够满足要求,那么最后的布局布线就会选择满足要求的两条路径之一。 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,即有约束才会有分析。若设计者不添加时序约束,那么时序分析就无从谈起。特权同学常常碰见一些初学者在遇到问题时不问青红皂白就认为是时序问题,实际上只有在添加了时序约束后,系统的时序问题才有可能暴露出来。 下面我们再来看一个例子,我们假设有4个输入信号,经过FPGA内部一些逻辑处理后输出。FPGA内部的布线资源有快有慢之分,好比国道和高速公路。通过高速通道所需要的路径延时假设为3ns-7ns,但只有两条可用;而通过慢速通道的路径延时则>10ns。

基于时序逻辑的工作流建模与分析方法1 王远,范玉顺 (清华大学自动化系,北京 100084) 摘要提出了一种基于活动时序逻辑(TLA)的工作流建模与模型分析的形式化方法。该方法将模型及模型的性质都表示为一个TLA公式,对工作流模型性质的分析可以等价为对TLA中两个公式之间是否存在蕴涵关系的检验,从而建立了一个工作流模型各层次分析统一框架。一个工作流建模和分析的实例验证了所提出方法的有效性,该方法在建模、模型分析以及指导模型设计等方面都有较好的应用前景。 关键词工作流,活动时序逻辑,工作流模型分析 1基金项目:国家自然科学基金项目(60274046) 0 引言 工作流管理是实现企业过程集成和提高企业运行效率、柔性的一种全面的支撑技术。该技术在办公自动化(OA)、计算机支持的协同工作(CSCW)、经营过程重组(BPR)等几个领域中的应用证明,工作流模型的合理性验证与分析是成功实施工作流管理的关键[1]。工作流模型分析可以分为逻辑、时间和性能三个层次。逻辑层次关心的是工作流模型中事件点与事件点之间的关系,时间层次的分析是在逻辑层次的基础上研究模型中时间段与时间段之间的关系,而性能层次分析一般是指(考虑资源信息) 通过仿真或严格的理论分析,获得与系统性能相关的量化指标,来评估建立的工作模型是否满足目标需求。 工作流模型的验证与分析的方法与建模方法密切相关。工作流建模方法可以分为非形式化方法与形式化方法[2]。非形式化方法主要包括活动网络图法、ECA(Event-Condition-Action)规则方法、面向系统交互的工作流建模语言等,这些非形式化的建模方法普遍缺乏对模型验证与分析的支持。工作流建模的形式化方法以基于Petri网的建模方法为主,并在此基础上形成了一些工作流模型验证与分析的方法,然而这些基于Petri网的方法存在两个问题: 一是没有统一的方法框架,无法满足工作流模型多种性质的验证需要,而是针对一种性质,提出一种特殊的高级Petri网建模方法,找到该性质在Petri网中的表达方式,并针对这种表达方式提出一种验证算法,比如,用户需要验证模型中两个活动之间的时间距离约束,现有的方法无法验证,就只能依靠研究人员的创造力,提出一种特殊的Petri网,并发展一种专门的验证方法;二是在指导工作流模型的设计和工作流模型的综合方面无法满足需要,比如要设计一个满足给定性质的工作流模型,现有的模型验证方法就无法提供有力的支持。针对上述工作流模型分析验证中存在的问题,本文用时序逻辑作为理论基础,提出了一种基于时序逻辑的工作流建模与分析方法,为工作流模型各个层次的验证与分析提供了一种新思路。 1 TLA基本概念 时序逻辑作为一种表示各种动态系统行为和性质的逻辑语言,近年来在反应系统、实时系统的表示与验证、网络协议的分析、多媒体通信同步以及自然语言理解、专家系统、人工智能等方面得到了广泛的应用[3-5]。在本文提出的基于时序逻辑的工作流建模分析方法中,一个工作流过程模型被描述为一个时序逻辑系统中的公式,同时该模型需要被验证的和分析的性质也表示为一个时序逻辑公式,该方法对所验证的性质并没有特殊的限定。要分析工作流模型是否满足该性质,只需在相应的逻辑系统中利用逻辑推理和模型检查等技术检验这两个公式之间是否存在蕴涵关系。这就使得对工作流模型各层次的验证可以统一到一个方法框架中来。同时,由于在时序逻辑中并不区分公式表示的是模型还是模型的性质,这使得本文提出的方法在指导工作流模型的设计和工作流模型的综合方面有较好的应用前景。 本文使用的时序逻辑系统是活动时序逻辑

ISE工具时序约束主要约束主要包括周期约束,pad to pad 约束和偏移约束: (1)周期约束的计算如下图所示: (2)pad to pad 约束是存粹的组合逻辑约束; (3)偏移约束主要包括输入偏移和输出偏移,规定了外部时钟和数据与输入输出管脚之间的时序关系,不是用来约束内部逻辑的; (转)FPGA时序分析,时序约束知识 时序约束目的:一、提高设计的工作频率二、获得正确的时序分析报告(STA:静态时序分析) 常用的时序概念:周期,最大时钟频率、时钟建立时间、时钟保持时间、时钟到输出延时、管脚到管脚延时、Slack和时钟偏斜(Skew). 周期:如图1是周期示意图,当计算出Tperiod,那么当然fm ax=1/Tperiod,fm ax是显示设计最重要的性能指标之一。 时钟建立时间:如图3所示是时钟建立时间的计算方法 时钟保持时间:同样利用图3的模型计算Th=clkdelay-datadelay+Microhold 注意:前两个公式中提到的Microsetup 和Microhold一般均是一个小于1ns的常量。

时钟输出延迟:他是指在时钟有效到数据有效的最大时钟间隔如图4所示 Tco=clkdelay+datadelay+Microco slack:表示设计是否满足时序的一个称谓:正的slack表示满足时序,负的slack表示不满足时序。保持时间slac k是一个重要的概念,引起不满足的主要原因是时钟偏斜大于数据路径的偏斜。Quartus2时序分析工具和优化向导: 常用的三种时序约束设置方法:1 通过Assignment/timing settings 2 Assignment/timing wiard tool 3 Assignment/Assignment editor选择在图形界面下完成对设计的时序约束。一般情况下前两种是做全局的时序约束,后一种是做局部的时序约束,另外还可以通过修改.qsf文件来实现。 时序约束思想:时序约束一般都是先全局后个别,如果冲突则个别的优先级更高。 一、将编绎器设置为时序驱动编绎,即是指让编绎过程尽量向着满足时序约束方向努力!assignment/settings/fitter setting. 二、全局时钟设置如果在设计中只有一个全局时钟,或者所有的时钟同频,可以在Quartus2中只设置一个全局时钟约束。Assignment/timing settings 三、时序向导在用记对时序约束设置不熟悉的情况下,可以选择使用向导。Assignment/classic timing analyser wizards. 四、可以设置独立时钟与衍生时钟,衍生时钟是由独立时钟变化而来的,他是由独立时钟分频,倍频,移相等变化而来的,可以在设置中确定二者的关系Assignment/settings/timing analyse setting/classic timing analyse setting/individual clock。 五、通过assignment editor 设置个别时钟约束

最近在altera FPGA里设计一个外设的驱动模块,模块本身逻辑很简单如下图所示,但是模块和外设之间的时序约束问题搞的很头疼,今天先讲讲总结的一些Timequest下外设约束方法,特别是那毫无用户体验而言的Create Generated Clocks用法。 要让外设正确接收FPGA发出的数据,需要dout和clkout满足外设的建立保持时间,如下图所示。

时序分析是基于源reg的Tco、目的reg的Tsu,源reg到目的reg的Tdelay路径延迟以及到两个reg的clk skew计算出来的,现在Timequest 不知道外设接收reg和时钟输入端的延迟参数,无法分析,还需分若干步配置: 1.使用Create Clocks建立系统时钟sysclk create_clock -name {sysclk} -period 20.000 -waveform { 0.000 10.000 } [get_ports {sysclk}] Timequset里的所有时钟都需要手动设置,首先设置系统时钟,后面的时钟都要基于这个时钟才能生成。 2.使用Create Generated Clocks建立输出时钟clkout 外设的时钟源于FPGA的输出port clkout,如果不建立时钟,timequest只会把clkout当作一个普通的输出引脚,时序分析器认为目的reg缺少驱动时钟,无法分析。Timequest中将通过倍频、分频或者移相等生成的时钟都归为Generated Clocks,你可以使用Create Clocks创建试一下,不会提示创建失败,但是在最后的时序分析里不会加入clkout的clock network delay,Timequest没有你想象的那么智能,知道clkout 是从一个分频模块输出,自动加入模块延迟分析,它不知道这些。所以还是使用Create Generated Clocks来创建吧,先填写源时钟sysclk,再填写生成时钟和源时钟的关系,2分频,最后指定target 生成时钟到clkout引脚,这三个步骤看似没问题,结果却是创建失败,提示找不到sysclk 到clkout之间的路径,如下所示。 Warning: No paths exist between clock target "clk_out" of clock "clkout" and its clock source. Assuming zero source clock latency. 但是sysclk到clkout明明是有路径的啊,之间的逻辑也很简单,就是一个二分频关系,bdf图如下所示。 clk_div模块的代码如下: reg clk_div; always @(posedge clk or negedge rset_n) begin if(!rset_n) clk_div <= 0; else clk_div <= ~clk_div; end 尝试了很多方法都无效,最终实验成功了一种自认为很别扭的方法,“曲线救国”分两步走: 首先Create Generated Clocks 从引脚sysclk 到寄存器clk_div create_generated_clock -name {clk_div_r} -source [get_ports {sysclk}] -divide_by 2 -master_clock {sysclk} [get_registers {clk_div:inst4|clk_div}]