移位寄存器的串行扩展技术

- 格式:doc

- 大小:36.00 KB

- 文档页数:4

fpga移位寄存器用法FPGA(Field-Programmable Gate Array)是一种可编程的集成电路芯片,可以根据用户的需求进行灵活的数字电路设计和开发。

在FPGA设计中,移位寄存器(Shift Register)是一种常用的数字电路元件,用于将数据从一个位置传送到另一个位置。

移位寄存器的基本原理是通过时钟信号的控制,在一定的时间间隔内,将数据从输入端移动到输出端,并且保持在输出端一段时间。

移位寄存器可以用来实现各种功能,如数据传输、数据移位、数据缓存等。

在FPGA设计中,移位寄存器的使用非常广泛,下面将介绍移位寄存器的用法。

移位寄存器可以分为串行移位寄存器和并行移位寄存器两种类型。

串行移位寄存器是最基本的移位寄存器,它将输入数据按位依次移动到输出端。

串行移位寄存器可以采用不同的移位方向,如向左移位(Shift Left)或向右移位(Shift Right)。

串行移位寄存器的数据长度可以根据需要进行扩展,从几位到几十位不等。

并行移位寄存器是将输入数据同时移动到输出端的移位寄存器,也称为平行移位寄存器。

与串行移位寄存器不同的是,输入数据的每一位立即传送到输出端,而不是按位移动。

并行移位寄存器通常用于数据宽度较大的情况,可以大大提高数据传输的速度。

移位寄存器通常有两个主要的应用场景:数据传输和数据移位。

在数据传输方面,移位寄存器可以用来在不同的时钟域之间传输数据。

在设计中,时钟域是指由时钟信号控制的特定区域,在同一时钟域内的电路操作是同步的,而不同的时钟域之间的电路操作是异步的。

移位寄存器可以在不同的时钟域之间传输数据,并实现时钟域之间的数据同步。

在数据移位方面,移位寄存器可以用来对数据进行移位操作,如数据串行化和并行化。

数据串行化是将并行数据按位移动,将其转换为串行数据。

数据并行化是将串行数据按位移动,将其转换为并行数据。

这两种操作通常用于接口电路设计和数据通信系统中。

此外,移位寄存器还可以用于数据缓存和数据处理。

移位寄存器的设计及实现移位寄存器(Shift Register)是一种常用的数字逻辑电路器件,它能够将数据按照输入和输出的时序进行移位操作。

通过移位寄存器,我们可以实现数据的串行传输、并行-串行或者串行-并行转换、数据延迟等功能。

本文将对移位寄存器的设计与实现进行介绍。

一、移位寄存器的设计1.串行输入、串行输出的移位寄存器这种移位寄存器称为串行移位寄存器,它包括n个触发器,每个触发器提供一个数据位的存储空间。

数据通过一个输入端串行输入,然后通过触发器依次移位,最后从输出端串行输出。

2.并行输入、并行输出的移位寄存器这种移位寄存器称为并行移位寄存器,它包括n个触发器,每个触发器提供一个数据位的存储空间。

数据通过n个输入端并行输入到各个触发器,然后通过控制信号进行同步移位。

最后从n个输出端并行输出。

3.并行输入、串行输出的移位寄存器这种移位寄存器称为并行-串行移位寄存器,它先从n个输入端并行输入数据,然后通过控制信号进行同步移位,并将移位结果通过一个输出端串行输出。

4.串行输入、并行输出的移位寄存器这种移位寄存器称为串行-并行移位寄存器,它先从一个输入端串行输入数据,然后通过触发器进行移位,最后将移位结果从n个输出端并行输出。

1.触发器选择由于是8位移位寄存器,需要选择8个触发器。

常用的触发器有D触发器、JK触发器等,可以根据实际需求选择合适的触发器。

2.输入输出端口设计设计一个输入端口用于串行输入数据。

由于是串行输入,需要一个时钟信号和一个使能信号进行同步移位操作。

同时,设计一个输出端口用于串行输出数据。

3.控制信号电路设计根据串行输入、串行输出的要求,需要设计一个时钟信号和一个使能信号的电路。

使能信号在移位过程中保持逻辑高电平,只有当8位数据全部移位完成时才将使能信号置为逻辑低电平。

二、移位寄存器的实现1.设计一个8位移位寄存器电路,并连接8个D触发器。

2.将串行输入信号与D触发器的数据端相连,时钟信号与D触发器的时钟端相连,使能信号与D触发器的使能端相连。

附页:实验线路图:编译程序:源程序代码:1 汇编语言程序清单ORG 0000HLJMP MAINORG 000BHLJMP INTT0MAIN:MOV SP,#60HMOV TMOD,#01HSETB ET0SETB EAMOV TH0,#3CHMOV TL0,#0B0HSETB TR0MOV 30H, #0 ; 每中断一次加1MOV 31H, #0 ; 每秒加1, 当其值为100时清0 MOV 32H, #0 ; 个位MOV 33H, #0 ; 十位LP:MOV R0,#32HMOV R7,#2ACALL BINBCDMOV DPTR,#TABDSPLY:MOV A,@R0MOVC A,@A+DPTRCPL AMOV SBUF,ADSP1:JNB TI,DSP1CLR TIINC R0DJNZ R7,DSPLYLP1:MOV A,30HCJNE A, #10, LP1MOV 30H,#00HINC 31HMOV A,31HCJNE A,#100,LPMOV 31H,#0SJMP LPINTT0:MOV TL0,#0B0HMOV TH0,#3CHINC 30HRETITAB: DB 3FH,06H,5BH,4FH,66H,6DH,7DH,07H,7FH,6FHDB 0FFH,00H,73H; 入口参数二进制数存放在31H中; 出口参数 BCD数十位(33H), 个位(32H)BINBCD:MOV A,31HMOV B,#10DIV ABMOV 33H,AMOV A,BMOV 32H,ARETEND ; 程序结束2 C 语言程序清单#include <AT89X51.H>#include <intrins.h>#define uchar unsigned char#define uint unsigned int//共阴数码管段码:0~9,全亮,全灭,Puchartab[]={0x3F,0x06,0x5B,0x4F,0x66,0x6D,0x7D,0x07,0x7F,0x6F,0xFF,0x00,0x 73};uchar timer; //定时器每中断1次加1void main(void){uchar ten,one,count;SP=0x60;TMOD=0x01; //定时器T0方式1定时ET0=1; //开定时器T0中断EA=1; //开总中断TH0=0x3C; //每100ms中断一次TL0=0xB0;TR0=1; //启动定时器T0timer=0;count=0;do{do{ten=count/10; //求得十位one=count%10; //求得个位SBUF=~tab[one]; //发送个位while(~TI);TI=0;SBUF=~tab[ten]; //发送十位while(~TI);TI=0;while(timer<10); //延时1s,即10*100ms timer=0;count++; //每隔一秒,count值加1 }while(count<100); //从0计到99count=0;} while(1);}void intt0() interrupt 1{TH0=0x3C;TL0=0xB0;timer++;}。

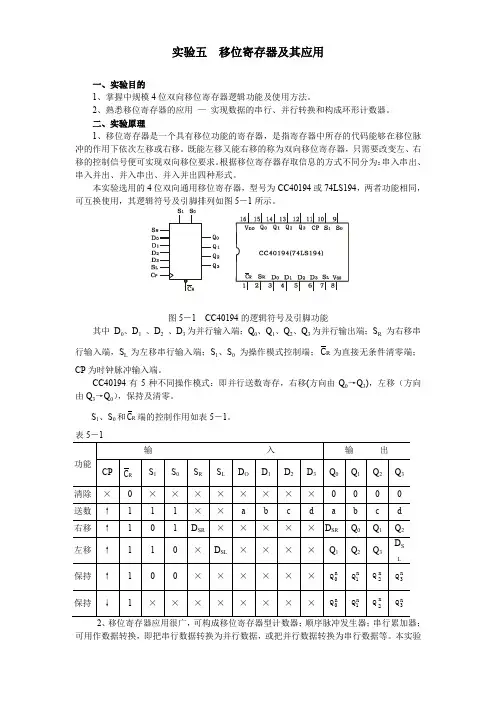

实验五移位寄存器及其应用一、实验目的1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。

2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。

二、实验原理1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。

既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。

根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。

本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图5-1所示。

图5-1 CC40194的逻辑符号及引脚功能其中D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;S R为右移串C为直接无条件清零端;行输入端,S L为左移串行输入端;S1、S0为操作模式控制端;RCP为时钟脉冲输入端。

CC40194有5种不同操作模式:即并行送数寄存,右移(方向由Q0→Q3),左移(方向由Q3→Q0),保持及清零。

S1、S0和R C端的控制作用如表5-1。

表5-12、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。

本实验研究移位寄存器用作环形计数器和数据的串、并行转换。

(1)环形计数器把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如图5-2所示,把输出端Q3和右移串行输入端S R 相连接,设初始状态Q0Q1Q2Q3=1000,则在时钟脉冲作用下Q0Q1Q2Q3将依次变为0100→0010→0001→1000→……,如表5-2所示,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。

图5-2 电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。

移位寄存器串入出与并入串出————————————————————————————————作者:————————————————————————————————日期:移位寄存器串入并出与并入串出在数字电路中,移位寄存器(英语:shift register)是一种在若干相同时间脉冲下工作的触发器为基础的器件,数据以并行或串行的方式输入到该器件中,然后每个时间脉冲依次向左或右移动一个比特,在输出端进行输出。

这种移位寄存器是一维的,事实上还有多维的移位寄存器,即输入、输出的数据本身就是一些列位。

实现这种多维移位寄存器的方法可以是将几个具有相同位数的移位寄存器并联起来。

移位寄存器的输入、输出都可以是并行或串行的。

它们经常被配置成串入并出(serial-in, parallel-out, SIPO)的形式或并入串出(parallel-in, serial-out, PISO),这样就可以实现并行数据和串行数据的转换。

当然,也有输入、输出同时为串行或并行的情况。

此外,还有一些移位寄存器为双向的,也就是说它允许数据来回传输,输入端同时可以作为输出端,输出端同时也可以作为输入端。

如果把移位寄存器的串行输入端,和并行输出端的最后一位连接起来,还可以构成循环移位寄存器(circular shift register),用来实现循环计数功能。

串入并出串入并出形式的移位寄存器接法,可以将输入的串行数据以并行格式输出。

串行通信要求的几位数据完成输入之后,就可以在输出端的各位同时读出并行数据。

并入串出并入串出形式的移位寄存器接法,通过下图所示D1-D4并行输入段接收4位外部并行数据,而Q为串行输出的引脚。

为了将数据写入到寄存器中,写/移位控制线必须保持低电平。

写入完成,需要移位时,写/移位控制线则必须处于高电平,而且必须给予时间脉冲,每提供一个时间脉冲,向左(或向右)移动一位。

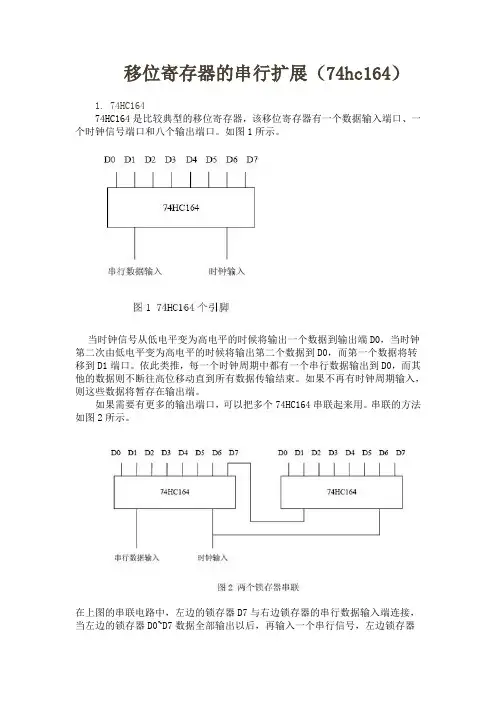

移位寄存器的串行扩展(74hc164)1. 74HC16474HC164是比较典型的移位寄存器,该移位寄存器有一个数据输入端口、一个时钟信号端口和八个输出端口。

如图1所示。

当时钟信号从低电平变为高电平的时候将输出一个数据到输出端D0,当时钟第二次由低电平变为高电平的时候将输出第二个数据到D0,而第一个数据将转移到D1端口。

依此类推,每一个时钟周期中都有一个串行数据输出到D0,而其他的数据则不断往高位移动直到所有数据传输结束。

如果不再有时钟周期输入,则这些数据将暂存在输出端。

如果需要有更多的输出端口,可以把多个74HC164串联起来用。

串联的方法如图2所示。

在上图的串联电路中,左边的锁存器D7与右边锁存器的串行数据输入端连接,当左边的锁存器D0~D7数据全部输出以后,再输入一个串行信号,左边锁存器D7数据将作为右边锁存器的输入数据并从右边锁存器D0端输出,从而实现了多个字节数据的移位锁存。

这样利用74HC164就实现了串行数据到并行数据的转换。

注意到在上面的两个图中,无论输出什么长度的数据,所需要的输入信号都只有两个,一个是串行数据输入,另一个是锁存器的时钟信号输入。

如果我们把这两个输入端口连接到单片机的两个输出端口上,其中单片机的一个端口串行输出数据,另一个端口输出时钟信号以便控制串行数据的锁存方式,那么我们就只需要两个单片机端口几乎实现任意数量的并口输出。

2. 8051串口方式0的工作原理与时序图3 串口方式0的时序8051串口方式0的时序如图所示,RXD(P3.0)为数据端,TXD(P3.1)为同步移位脉冲端,每次串行发送、接收8位数据(一帧),低位在先。

时钟为Fosc/12。

(1)发送执行任何一条MOV SUBF,#data指令时,启动内部串行发送允许,SEND置高电平,随后在TXD同步移位时钟的作用下,将数据data从RXD端移位输出。

一帧数据发送完毕时,内部发送中断请求TI有效。

要再次发送一帧时,须用软件清TI。

电路中的移位寄存器及其应用电路中的移位寄存器是一种重要的数字逻辑元件,它可以实现数据的移动和存储功能。

通过移动数据位,可以在电路中实现各种有趣的应用,从而扩展数字逻辑的功能。

在本文中,我们将探讨移位寄存器的原理、分类以及一些实际应用。

移位寄存器是一种特殊的寄存器,它可以用来存储和移动一串二进制数据。

它由一组触发器构成,每个触发器代表一个二进制位。

这些触发器可以分为串行和并行两种类型。

串行移位寄存器是将数据位顺序连接在一起形成一个串行的数据路径。

当时钟信号到来时,数据位会按照顺序依次移动。

最常见的是移位寄存器的左移和右移操作,左移时数据位向左移动一位,右移时数据位向右移动一位。

当移出的数据位被丢弃时,新的数据位会从移入端进入寄存器。

串行移位寄存器的优点是结构简单,占用空间小,但是移位速度较慢。

并行移位寄存器是将数据位同时移动的一种寄存器。

它的结构比串行移位寄存器复杂,需要更多的触发器来实现。

并行移位寄存器可以同时移动多个数据位,因此移位速度较快。

在并行移位寄存器中,移位操作是通过输入信号来控制的。

通过控制输入信号的状态,可以实现不同的移位模式,如循环移位、位反转等。

移位寄存器在数字逻辑中有着广泛的应用。

其中,最常见的应用是数据的存储与传输。

通过移位寄存器,可以将数据从一个地方传输到另一个地方,实现数据的存储和传递。

移位寄存器还可以用于实现数据的压缩和解压缩。

例如,在图像处理中,可以使用移位寄存器将图像数据进行压缩,从而减小图像文件的大小,并且可以在需要时恢复原始图像。

此外,移位寄存器还可以用于实现密码算法。

通过将数据进行移位和混合,可以实现数据的加密和解密,保证数据的安全性。

除了上述应用外,移位寄存器还被广泛用于时序控制电路中。

时序控制电路是一种通过控制信号来实现特定操作顺序的电路。

移位寄存器可以用于存储各种控制信号,并根据时钟信号的到来按照特定的顺序输出这些信号。

通过移位寄存器的组合和控制信号的变化,可以实现复杂的时序控制功能,如状态机和序列识别等。

并行输入串行输出移位寄存器原理移位寄存器是一种常见的数字电路元件,用于将数据进行移位操作。

它具有并行输入和串行输出的特点,可以将多个输入同时加载到寄存器中,并按照一定的顺序输出。

本文将介绍并行输入串行输出移位寄存器的原理及其工作方式。

一、移位寄存器的基本原理移位寄存器是由一组触发器组成的,每个触发器都具有数据输入D、时钟输入CLK和数据输出Q。

在并行输入串行输出移位寄存器中,触发器的数据输入D与并行输入数据相连,时钟输入CLK相连,数据输出Q与下一个触发器的数据输入D相连,最后一个触发器的数据输出Q为寄存器的串行输出。

当时钟信号到达时,触发器会将输入数据加载到自身,并将输出作为下一个触发器的输入。

通过多个触发器的串联,数据可以在寄存器中进行移位操作。

当所有输入数据加载完成后,通过寄存器的串行输出可以得到移位后的结果。

二、移位寄存器的工作方式1. 并行输入:将要移位的数据同时输入到寄存器的多个触发器中。

每个触发器都会将输入数据保存到自身。

这样可以实现一次性输入多个数据,提高了数据输入的效率。

2. 串行输出:通过触发器的串行输出将移位后的数据输出。

每当时钟信号到达时,触发器将自身的数据输出,并将输出作为下一个触发器的输入。

这样数据就会从一个触发器传递到下一个触发器,最终得到移位后的结果。

3. 移位操作:通过时钟信号的不断触发,移位寄存器中的数据可以进行移位操作。

每当时钟信号到达,数据会从一个触发器传递到下一个触发器,实现数据的移位。

当所有数据都完成移位后,可以通过最后一个触发器的串行输出得到移位后的结果。

三、应用场景并行输入串行输出移位寄存器常用于串行通信中的数据传输。

在串行通信中,数据需要按照一定的顺序进行传输,而移位寄存器可以实现数据的有序移位,保证数据的正确传输。

例如,在串行通信中,发送端需要将要发送的数据按照一定的格式进行编码,并通过串行方式发送出去。

接收端则需要将接收到的数据进行解码并按照相应的格式进行处理。

并行输入串行输出移位寄存器原理以并行输入串行输出移位寄存器原理为标题,下面将详细介绍该原理及其应用。

移位寄存器是一种常用的数字电路元件,可以实现数据的平行输入和串行输出。

它由多个触发器组成,每个触发器都可以存储一个位的信息。

在并行输入时,数据可以同时输入到每个触发器中,而在串行输出时,触发器之间的数据按照一定的顺序传递,从而实现数据的移位。

在移位寄存器中,最常见的是串行输入并行输出的移位寄存器,即数据按照一位一位的顺序输入到移位寄存器中,而输出则可以同时输出多个位的数据。

这种移位寄存器的应用非常广泛,例如在串行通信中,可以使用移位寄存器将并行数据转换为串行数据进行传输,而在显示器中,也可以使用移位寄存器逐行扫描显示像素点。

移位寄存器的工作原理基于触发器的特性。

触发器是一种存储状态的元件,它可以根据时钟信号的变化来改变输出状态。

在移位寄存器中,触发器之间通过时钟信号进行串行数据传输。

当时钟上升沿到来时,触发器将其输入数据更新到输出中,并将原来的输出传递给下一个触发器,从而实现数据的移位。

在移位寄存器中,有两种常见的触发器,分别是D触发器和JK触发器。

D触发器是最简单的触发器,它有一个数据输入端D和一个时钟输入端CLK,当时钟信号发生变化时,D触发器将D端的数据更新到输出端Q中。

而JK触发器是一种更复杂的触发器,它有两个数据输入端J和K,以及一个时钟输入端CLK。

当时钟信号发生变化时,JK触发器根据J和K的值来更新输出端Q。

通过组合不同类型的触发器,可以构建出不同类型的移位寄存器,满足不同的应用需求。

除了串行输入并行输出的移位寄存器外,还有并行输入串行输出的移位寄存器。

这种移位寄存器可以同时输入多个位的数据,并将其串行输出。

在这种移位寄存器中,每个触发器都有一个数据输入端,当时钟信号发生变化时,触发器将输入端的数据更新到输出端,并将原来的输出传递给下一个触发器。

通过这种方式,多个位的数据就可以按照一定的顺序进行移位输出。

移位寄存器的串行扩展技术编者按:移位寄存器的串行扩展技术是单片机串行口扩展的一种常用方法。

对于MCS-51系列单片机而言,将串口置为工作方式0,串口便工作在移位寄存器方式下了。

此时,单片机的RXD口作串行数据的发送/接收口,TXD口作移位脉冲输出口。

利用单片机串口的这一特性,可以十分方便地扩展I/O口线,本文便是一例。

通过本例,读者除了可以加深对串口工作方式0的理解外,还可以举一反三,将之用于其他需要进行I/O口扩展的场合,比如用串口扩展键盘等。

遥控数码报时闹钟CD4094是带输出锁存和三态控制的串入/并出高速转换器,具有使用简单、功耗低、驱动能力强和控制灵活等优点。

CD4094的引脚定义如图1。

其中{1}脚为锁存端,{2}脚为串行数据输入端,{3}脚为串行时钟端。

{1}脚为高电平时,8位并行输出口Q1~Q8在时钟的上升沿随串行输入而变化;{1}脚为低电平时,输出锁定。

利用锁存端可方便地进行片选和级联输出控制。

{15}脚为并行输出状态控制端,{15}脚为低电平时,并行输出端处在高阻状态,在用CD4094作显示输出时,可使显示数码闪烁。

{9}脚QS、{10}脚Q′S是串行数据输出端,用于级联。

QS端在第9个串行时钟的上升沿开始输出,Q′S端在第9个串行时钟的下降沿开始输出。

当CD4094电源为5V时,输出电流大于3.2mA,灌电流为1mA。

串行时钟频率可达2.5MHz。

1.CD4094作静态LED显示驱动器图2为用CD4094作驱动器的三位数码管静态显示电路略图。

单片机串口工作在方式0,即移位寄存器方式。

输出数据首先送到IC1,第二次输出的数据移至IC1时,先前输出数据则移到IC2,依此类推。

输出三次后,在IC1、IC2、IC3的Q1~Q8口分别得到数据3、数据2、数据1。

程序如下:(DISP为显示子程序)..................MOVSCON,#00H;置串口为方式0..................DISP:CLRP3.7;输出锁存MOVR0,#33H;显示值送33H、34H、35HMOVR7,#03H;置数码管个数3LP:MOVA,@R0MOVDPTR,#TAB;置字段码表首址MOVCA,@A+DPTR;查字段码表MOVSBUF,A;送字段码JNBTI,$ ;等待传送结束CLRTI;清串行中断标志INCR0;显缓区地址加1DJNZR7,LP;显示数码是否取完?SETBP3.7;允许输出显示NOPCLRP3.7;输出锁存RETTAB:DB3FH,06H,5BH,4FH,66H,6DH,7DH,07H,7FHDB6FH,00H说明:在串行口不作为其他使用,且显示的更新速度很低时,STROBE端可以始终接高;也可将P3.7口接到CD4094的{15}脚,从P3.7口输出一定频率的脉冲,使显示闪烁。

串行口扩展应用摘要:本文主要是单片机串行口在方式0下发送数据,外接一片8位串行输入并行输出的同步移位芯片——74LS164。

通过开关控制相应的LED灯亮灭。

关键字:单片机74LS164 串行口74LS164介绍:8 位移位寄存器(串行输入,并行输出)电特性的典型值如下:型号fm Pn54/74164 36MHz 185mW54/74LS164 36 MHz 80mW当清除端(CLEAR)为低电平时,输出端(QA-QH)均为低电平。

串行数据输入端(A,B)可控制数据。

当A、B 任意一个为低电平,则禁止新数据输入,在时钟端(CLOCK)脉冲上升沿作用下Q0 为低电平。

当A、B有一个为高电平,则另一个就允许输入数据,并在CLOCK 上升沿作用下决定Q0 的状态。

引出端符号CLOCK 时钟输入端CLEAR 同步清除输入端(低电平有效)A,B 串行数据输入端QA-QH 输出端极限值电源电压 (7V)输入电压………………………………… 5.5V工作环境温度54LS164…………………………………… -55~125℃74LS164…………………………………… -0~70℃储存温度…………………………………… -65℃~150℃74LS164是八位并出串行移位寄存器.功能是将数据串行移入,并行输出.P!4=VCC,P7=GND.P1=A,P2=B,两脚是数据串行移入口. P8=时钟. P9=清除.P3=QA,P4=QB,P5=QC,P6=QD,P10=QE,P11=QF,P12=QG,P13=QH是并行输出口.下图为74LS164与数码管的连接图。

1.系统分析(1)要求:通过开关控制相应的LED灯的亮灭。

(2)根据:MCS-51单片机内部有一个功能很强的全双工串行口:RXD/ P3.0 ,TXD/P3.5,可同时发送和接收数据。

发送和接收数据均可工作在查询方式和中断方式,使用十分灵活,可很方便地与其它计算机或串行传送信息的设备实现双机、多机通信。

移位寄存器的串行扩展技术

编者按:移位寄存器的串行扩展技术是单片机串行口扩展的一种常用方法。

对于MCS-51系列单片机而言,将串口置为工作方式0,串口便工作在移位寄存器方式下了。

此时,单片机的RXD口作串行数据的发送/接收口,TXD口作移位脉冲输出口。

利用单片机串口的这一特性,可以十分方便地扩展I/O口线,本文便是一例。

通过本例,读者除了可以加深对串口工作方式0的理解外,还可以举一反三,将之用于其他需要进行I/O口扩展的场合,比如用串口扩展键盘等。

遥控数码报时闹钟

CD4094是带输出锁存和三态控制的串入/并出高速转换器,具有使用简单、功耗低、驱动能力强和控制灵活等优点。

CD4094的引脚定义如图1。

其中{1}脚为锁存端,{2}脚为串行数据输入端,{3}脚为串行时钟端。

{1}脚为高电平时,8位并行输出口Q1~Q8在时钟的上升沿随串行输入而变化;{1}脚为低电平时,输出锁定。

利用锁存端可方便地进行片选和级联输出控制。

{15}脚为并行输出状态控制端,{15}脚为低电平时,并行输出端处在高阻状态,在用CD4094作显示输出时,可使显示数码闪烁。

{9}脚QS、{10}

脚Q′S是串行数据输出端,用于级联。

QS端在第9个串行时钟的上升沿开始输出,Q′S端在第9个串行时钟的下降沿开始输出。

当CD4094电源为5V时,输出电流大于3.2mA,灌电流为1mA。

串行时钟频率可达2.5MHz。

1.CD4094作静态LED显示驱动器

图2为用CD4094作驱动器的三位数码管静态显示电路略图。

单片机串口工作在方式0,即移位寄存器方式。

输出数据首先送到IC1,第二次输出的数据移至IC1时,先前输出数据则移到IC2,依此类推。

输出三次后,在IC1、IC2、IC3的Q1~Q8口分别得到数据3、数据2、数据1。

程序如下:(DISP为显示子程序)

..................

MOVSCON,#00H;置串口为方式0

..................

DISP:CLRP3.7;输出锁存

MOVR0,#33H;显示值送33H、34H、35H

MOVR7,#03H;置数码管个数3

LP:MOVA,@R0

MOVDPTR,#TAB;置字段码表首址

MOVCA,@A+DPTR;查字段码表

MOVSBUF,A;送字段码

JNBTI,$ ;等待传送结束

CLRTI;清串行中断标志

INCR0;显缓区地址加1

DJNZR7,LP;显示数码是否取完?

SETBP3.7;允许输出显示

NOP

CLRP3.7;输出锁存

RET

TAB:DB3FH,06H,5BH,4FH,66H,6DH,7DH,07H,7FH

DB6FH,00H

说明:在串行口不作为其他使用,且显示的更新速度很低时,STROBE端可以始终接高;也可将P3.7口接到CD4094的{15}脚,从P3.7口输出一定频率的脉冲,使显示闪烁。

2.CD4094作LED动态显示驱动器

用一片CD4094作段驱动,一片CD4094作位驱动,驱动8位带小数点的数码管(见图3)。

程序如下:(DISP为显示子程序)

MOVSCON#00H;置串口为方式0

……

DISP:CLRP3.7;输出锁存

MOVR0,#30H;显缓区首址送R0

MOVR4,#08H;置数码管个数为8

MOVR5,#0FEH;送位码初值

LP:MOVA,R5;取位码

MOVSBUF,A;送位码

JNBT1;等待传送结束

CLRT1;清串行中断标志

MOVA,@R0;取段码

MOVDPTR,#TAB;置段码表首址

MOVCA,@A+DPTR;查段码表

MOVSBUF,A;送段码

JNBT1;等待传送结束

CLRT1;清串行中断标志

STBP3.7;允许输出显示

LCALLDEL;延时1ms

MOVA,R5;取位码

RLA;位码左移一位

MOVR5,A

INCR0;显缓区地址加1

CLRP3.7;输出锁存

DJNZR4,LP;8位显示完否?

RET

DEL:MOVR7,#02H;延时1ms(fosc=12MHz)

DL:MOVR6,#0F8H

DJNZR6,$

DJNZR7,DL

RET

TAB:DB3FH,06H,5BH,4FH,66H,6DH,7DH,07HDB7FH,6FH。