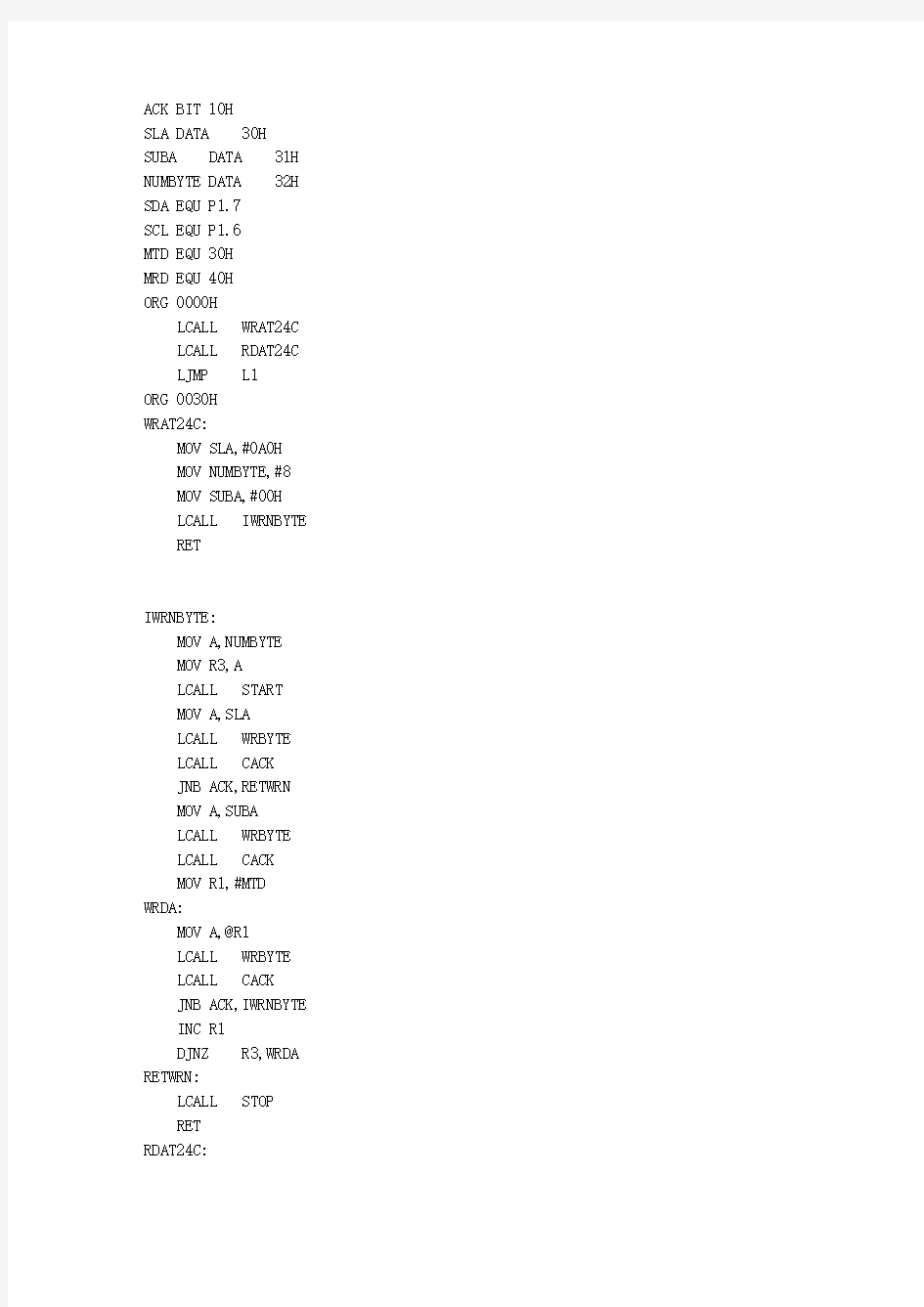

ACK BIT 10H

SLA DATA 30H SUBA DATA 31H NUMBYTE DATA 32H SDA EQU P1.7

SCL EQU P1.6

MTD EQU 30H

MRD EQU 40H

ORG 0000H

LCALL WRAT24C

LCALL RDAT24C

LJMP L1

ORG 0030H

WRAT24C:

MOV SLA,#0A0H

MOV NUMBYTE,#8

MOV SUBA,#00H

LCALL IWRNBYTE

RET

IWRNBYTE:

MOV A,NUMBYTE

MOV R3,A

LCALL START

MOV A,SLA

LCALL WRBYTE

LCALL CACK

JNB ACK,RETWRN

MOV A,SUBA

LCALL WRBYTE

LCALL CACK

MOV R1,#MTD WRDA:

MOV A,@R1

LCALL WRBYTE

LCALL CACK

JNB ACK,IWRNBYTE

INC R1

DJNZ R3,WRDA RETWRN:

LCALL STOP

RET

RDAT24C:

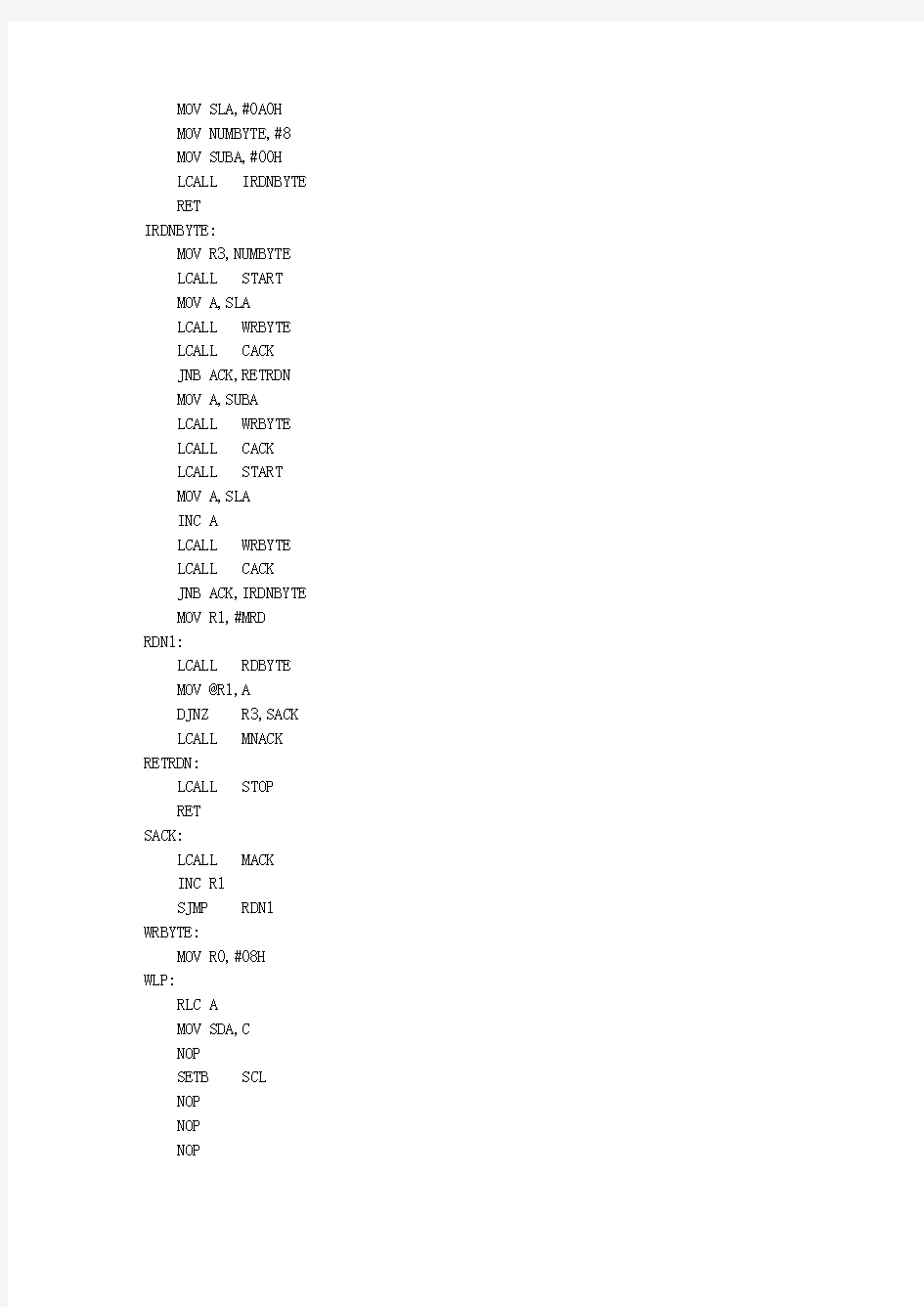

MOV SLA,#0A0H

MOV NUMBYTE,#8

MOV SUBA,#00H

LCALL IRDNBYTE

RET IRDNBYTE:

MOV R3,NUMBYTE

LCALL START

MOV A,SLA

LCALL WRBYTE

LCALL CACK

JNB ACK,RETRDN

MOV A,SUBA

LCALL WRBYTE

LCALL CACK

LCALL START

MOV A,SLA

INC A

LCALL WRBYTE

LCALL CACK

JNB ACK,IRDNBYTE

MOV R1,#MRD RDN1:

LCALL RDBYTE

MOV @R1,A

DJNZ R3,SACK

LCALL MNACK RETRDN:

LCALL STOP

RET

SACK:

LCALL MACK

INC R1

SJMP RDN1 WRBYTE:

MOV R0,#08H WLP:

RLC A

MOV SDA,C

NOP

SETB SCL

NOP

NOP

NOP

NOP

NOP

CLR SCL

WLP1:

DJNZ R0,WLP

NOP

RET RDBYTE:

MOV R0,#08H RLP:

SETB SDA

NOP

SETB SCL

NOP

NOP

MOV C,SDA

RLC A

CLR SCL

NOP

NOP

NOP

DJNZ R0,RLP

RET

START:

SETB SDA

NOP

SETB SCL

NOP

NOP

NOP

NOP

NOP

CLR SDA

NOP

NOP

NOP

NOP

CLR SCL

NOP

RET

STOP:

CLR SDA

NOP

NOP

NOP

NOP

NOP

NOP

NOP

SETB SDA

NOP

NOP

NOP

NOP

RET MACK:

CLR SDA

NOP

NOP

SETB SCL

NOP

NOP

CLR SCL

NOP

NOP

RET MNACK:

SETB SDA

NOP

NOP

SETB SCL

NOP

NOP

CLR SCL

NOP

NOP

RET CACK:

SETB SDA

NOP

NOP

SETB SCL

CLR ACK

NOP

NOP

MOV C,SDA

JC CEND

CEND:

NOP

CLR SCL

NOP

RET

L1:

END

山西大学自动化与软件学院 课程实验报告 实验课程计算机系统基础 实验名称总线与寄存器实验 实验地点线上 实验时间 6.30 学生班级软件工程1808班 学生学号 201802810825 学生姓名 指导教师

一:实验要求 理解并掌握总线与寄存器 二:实验目的 1、熟悉实验软件环境; 2、掌握总线以及数据通路的概念及传输特性。 3、理解锁存器、通用寄存器及移位寄存器的组成和功能。 二、实验内容 1、根据已搭建好的8位数据通路,熟悉总线连接的方法,理解74LS244芯片的作用,理解各相关信号在数据传输过程中起的作用; 2、通过拨码开关置数,将数据传送到各寄存器,将寄存器中数据显示出来,熟悉常用的寄存器。 三、实验器件 1、D触发器(74LS74、74LS175)、三态缓冲器(74LS244)。 2、寄存器(74LS27 3、74LS374 )和移位寄存器(74LS194) 四、实验原理 (见实验指导书) 五、实验步骤 注意:实验过程中应观察总线上及芯片引脚上显示的数据的变化情况,理解数据传送的过程和寄存器存数,从寄存器读数的原理。 实验(1)拨码开关输入数据至总线 ●====1;手动操作总线DIN上的拨码开关,在总线DIN上置位数据0x55,缓冲器244阻断。比较总线DIN与BUS状态的异同。 ●=0,比较总线DIN与BUS状态的异同,记录BUS总线的数据: BUS_7BUS_6BUS_5BUS_4BUS_3BUS_2BUS_1BUS_0BUS总 线 01010101AA 实验(2)D触发器数据锁存实验 ●=0,===1;通过拨码开关改变74LS74的D端(即BUS总线的BUS_0)的状态,按照下表置位74LS74的端、端,观察并记录CLK端上升沿、下降沿跳变时刻Q端、端的状态,填观测结果于表中。 CLK D Qn Qn+1n+1 01××010 110 10××001 101

ACK BIT 10H SLA DATA 30H SUBA DATA 31H NUMBYTE DATA 32H SDA EQU P1.7 SCL EQU P1.6 MTD EQU 30H MRD EQU 40H ORG 0000H LCALL WRAT24C LCALL RDAT24C LJMP L1 ORG 0030H WRAT24C: MOV SLA,#0A0H MOV NUMBYTE,#8 MOV SUBA,#00H LCALL IWRNBYTE RET IWRNBYTE: MOV A,NUMBYTE MOV R3,A LCALL START MOV A,SLA LCALL WRBYTE LCALL CACK JNB ACK,RETWRN MOV A,SUBA LCALL WRBYTE LCALL CACK MOV R1,#MTD WRDA: MOV A,@R1 LCALL WRBYTE LCALL CACK JNB ACK,IWRNBYTE INC R1 DJNZ R3,WRDA RETWRN: LCALL STOP RET RDAT24C:

MOV SLA,#0A0H MOV NUMBYTE,#8 MOV SUBA,#00H LCALL IRDNBYTE RET IRDNBYTE: MOV R3,NUMBYTE LCALL START MOV A,SLA LCALL WRBYTE LCALL CACK JNB ACK,RETRDN MOV A,SUBA LCALL WRBYTE LCALL CACK LCALL START MOV A,SLA INC A LCALL WRBYTE LCALL CACK JNB ACK,IRDNBYTE MOV R1,#MRD RDN1: LCALL RDBYTE MOV @R1,A DJNZ R3,SACK LCALL MNACK RETRDN: LCALL STOP RET SACK: LCALL MACK INC R1 SJMP RDN1 WRBYTE: MOV R0,#08H WLP: RLC A MOV SDA,C NOP SETB SCL NOP NOP NOP

微处理器中常用的集成串行总线是通用异步 接收器传输总线(UART)、串行通信接口(SCI) 和通用串行总线(USB)等,这些总线在速度、 物理接口要求和通信方法学上都有所不同。本文详细介绍了嵌入式系统设计的串行总线、驱动器和物理接口的特性,并为总线最优选择提供性能比较和选择建议。 由于在消费类电子产品、计算机外设、汽车和工业应用中增加了嵌入式功能,对低成本、高速和高可靠通信介质的要求也不断增长以满足这些应用,其结果是越来越多的处理器和控制器用不同类型的总线集成在一起,实现与PC软件、开发系统(如仿真器)或网络中的其它设备进行通信。目前流行的通信一般采用串行或并行模式,而串行模式应用更广泛。 微处理器中常用的集成串行总线是通用异步接收器传输总线、串行通信接口、同步外设接口(SPI)、内部集成电路(I2C) 和通用串行总线,以及车用串行总线,包括控制器区域网(CAN)和本地互连网(LIN)。这些总线在速度、物理接口要求和通信方法学上都有所不同。本文将对嵌入式系统设计的串行总线、驱动器和物理接口这些要求提供一个总体介绍,为选择最优总线提供指导并给出一个比较图表(表1)。为了说明方便起见,本文的阐述是基于微处理器的设计。 串行与并行相比 串行相比于并行的主要优点是要求的线数较少。例如,用在汽车工业中的LIN 串行总线只需要一根线来与从属器件进行通信,Dallas公司的1-Wire总线只使用一根线来输送信号和电源。较少的线意味着所需要的控制器引脚较少。集成在一个微控制器中的并行总线一般需要8条或更多的线,线数的多少取决于设计中地址和数据的宽度,所以集成一个并行总线的芯片至少需要8个引脚来与外部器件接口,这增加了芯片的总体尺寸。相反地,使用串行总线可以将同样的芯片集成在一个较小的封装中。 另外,在PCB板设计中并行总线需要更多的线来与其它外设接口,使PCB板面积更大、更复杂,从而增加了硬件成本。此外,工程师还可以很容易地将一个新器件加到一个串行网络中去,而且不会影响网络中的其它器件。例如,可以很容易地去掉总线上旧器件并用新的来替代。

高速串行总线的常用测试码型本文讨论了高速串行链路中常用的测试码型伪随机码流的原理,以及不同的测试码型对物理层测试结果的影响。 高速串行总线的常用测试码型 在当今的电信和计算机产品上,相比传统的并行总线,电路中的串行总线越来越多,速率越来越快。比如通信产品中的10GBase-KR、CPRI2代,计算机中的PCIeGen2、SATA6G,存储产品中的SAS6G、FC8.5G,这些串行总线都陆续的跨过了5Gbps。由于速率比较高,使得串行总线上的相关的收发器芯片(SERDES)、连接器、单板、背板的设计面临着越来越多的挑战。对于这些高速串行总线的物理层测试,测试码型的选用至关重要,在很多串行总线的规范中对测试码型有严格的要求。本文将对此进行探讨。 首先,串行总线的物理层测试通常分为发射机测试和接收机测试,又称为TX测试和RX测试。发射机测试通常包括眼图、抖动、信号波形、幅度、上升下降时间等测试项目,接收机测试通常包括误码率、抖动容限、接收机灵敏度等测试项目。对于眼图测试、误码率和抖动容限测试,最常用的测试码是伪随机码(PseudoRandomBinarySequence,简称PRBS),主要有PRBS7、PRBS15、PRBS23和PRBS31。除了PRBS以外,K28.5、1010、CJPAT等码型在很多串行总线的物理层测试中都很常用,特别是计算机上的串行标准(比如SATA、USB3.0、SAS)的测试码型有所不同,在本文中主要讨论最常用的测试码型——PRBS。 PRBS的实现方法 顾名思义,PRBS是伪随机码流,在其码流中包括了所有可能出现的比特组合,而且其出现的概率是相同的。PRBS信号是由PRBS码型发生器生成的。PRBS发生器通常是由线性反馈移位寄存器(LinearFeedbackShiftRegister,简称LFSR)和异或电路组成。如下图1所示为最简单的PRBS3的码型发生器,其多项式为X3+X2+1,即寄存器的第3位与第2位做异或(XOR)的逻辑运算后返回到寄存器的第1位,寄存器的第3位X3同时也是PRBS3发生器的输出。 图1:PRBS3码型发生器原理 在表格1中显示了PRBS3的n个周期的时钟后输出n个比特的码流。X1/X2/X3分别是3个比特移位寄存器的低位到高位,输出位是X3,初始状态为X1/X2/X3=1/1/1,如表格第1行所示。

简单描述: SPI 和I2C这两种通信方式都是短距离的,芯片和芯片之间或者其他元器件如传感器和芯片之间的通信。SPI和IIC是板上通信,IIC有时也会做板间通信,不过距离甚短,不过超过一米,例如一些触摸屏,手机液晶屏那些很薄膜排线很多用IIC,I2C能用于替代标准的并行总线,能连接的各种集成电路和功能模块。I2C 是多主控总线,所以任何一个设备都能像主控器一样工作,并控制总线。总线上每一个设备都有一个独一无二的地址,根据设备它们自己的能力,它们可以作为发射器或接收器工作。多路微控制器能在同一个I2C总线上共存这两种线属于低速传输; 而UART是应用于两个设备之间的通信,如用单片机做好的设备和计算机的通信。这样的通信可以做长距离的。UART和,UART就是我们指的串口,速度比上面三者快,最高达100K左右,用与计算机与设备或者计算机和计算之间通信,但有效范围不会很长,约10米左右,UART优点是支持面广,程序设计结构很简单,随着USB的发展,UART也逐渐走向下坡; SmBus有点类似于USB设备跟计算机那样的短距离通信。 简单的狭义的说SPI和I2C是做在电路板上的。而UART和SMBUS是在机器外面连接两个机器的。 详细描述: 1、UART(TX,RX)就是两线,一根发送一根接收,可以全双工通信,线数也比较少。数据是异步传输的,对双方的时序要求比较严格,通信速度也不是很快。在多机通信上面用的最多。 2、SPI(CLK,I/O,O,CS)接口和上面UART相比,多了一条同步时钟线,上面UART 的缺点也就是它的优点了,对通信双方的时序要求不严格不同设备之间可以很容易结合,而且通信速度非常快。一般用在产品内部元件之间的高速数据通信上面,如大容量存储器等。 3、I2C(SCL,SDA)接口也是两线接口,它是两根线之间通过复杂的逻辑关系传输数据的,通信速度不高,程序写起来也比较复杂。一般单片机系统里主要用来和24C02等小容易存储器连接。 SPI:高速同步串行口。3~4线接口,收发独立、可同步进行 UART:通用异步串行口。按照标准波特率完成双向通讯,速度慢 SPI:一种串行传输方式,三线制,网上可找到其通信协议和用法的 3根线实现数据双向传输 串行外围接口 Serial peripheral interface UART:通用异步收发器 UART是用于控制计算机与串行设备的芯片。有一点要注意的是,它提供了

实验六存储器和总线实验 一、实验目的 熟悉存储器和总线组成的硬件电路 二、实验要求 按照实验步骤完成实验项目,利用存储器和总线传输数据。 三、实验内容 (1)实验原理 实验所用半导体静态存储器电路原理如图所示,该静态存储器由一片6116(2k*8)构成,其数据线(D0-D7)已和数据总线(BUS-DIAP UNIT)相连接,地址线由地址锁存器(74LS273)给出,该锁存器的输入已连至数据总线。地址A0-A7与地址总线相连,显示地址内容。数据开关经三态门(74LS245)已连至数据总线,分时给出地址和数据。因为地址寄存器为8位,接入6116的地址A7-A0,而高三位A8-A10本实验装置已接地,其容量为256字节。6116由三根控制线:/CS(片选线)、OE(读线)、WE(写线)。当片选有效(/CS=0)时,同时OE=0时,(WE=0)时进行读操作。本实验中将OE引入接地,在此情况下,当/CS、WE=1时进行写操作。/CS=0、WE=0时进行写操作,其写时间与T3脉冲宽度一致。实验时T3脉冲由“单步”命令键产生,其它电平控制信号由二进制开关模拟,其中/CE(存储器片选信号为低电平有效,WE为写/读(W/R)控制信号,当WE=0时进行读操作、当WE=1时为写操作。 (2)实验步骤 1、控制信号连接:位于实验装置右侧边缘的RAM片选端(/CE)、写/读线(WE)、地址锁存信号(LDAR)与位于实验装置左上方的控制信号(/CE、WE、LDAR)之间对应相连。位于实验装置左上方CTR-OUT的控制信号(/SW-B)与左下方INPUT-UNIT(/SW-B)对应相连。 具体信号连接:/CE,WE,LDAR,/SW-B 2、完成上述连接,仔细检查无误后方可进入本实验。 在闪动是我“P”状态下按动增值命令键,时LED显示器自左向右第一位显示提示符“H”,表示装置已进入手动单元试验状态。(若当前处“H”状态,本操作可略) 3、内部总线数据写入存储器 给存储器的00、01、02、03、04地址单元中分别写入数据11、12、13、14、15,具体操作步骤如下:(以向00地址单元写入11数据为例,然后重复操作将数据分别写入各地址单元)。4,、读存储器的数据到数据总线 依次独处第00、01、02、03、04单元中的内容,观察上述各单元中的内容是否与前面写入的一致。具体步骤如下:(以从00单元独处11数据为例,其它则类似)

SPI、I2C、UART三种串行总线的区别 第一个区别当然是名字: SPI(Serial Peripheral Interface:串行外设接口); I2C(INTER IC BUS:意为IC之间总线) UART(Universal Asynchronous Receiver Transmitter:通用异步收发器) 第二,区别在电气信号线上: SPI总线由三条信号线组成:串行时钟(SCLK)、串行数据输出(SDO)、串行数据输入(SDI)。SPI总线可以实现多个SPI设备互相连接。提供SPI串行时钟的SPI 设备为SPI主机或主设备(Master),其他设备为SPI从机或从设备(Slave)。主从设备间可以实现全双工通信,当有多个从设备时,还可以增加一条从设备选择线。 如果用通用IO口模拟SPI总线,必须要有一个输出口(SDO),一个输入口(SDI),另一个口则视实现的设备类型而定,如果要实现主从设备,则需输入输出口,若只实现主设备,则需输出口即可,若只实现从设备,则只需输入口即可。 I2C总线是双向、两线(SCL、SDA)、串行、多主控(multi-master)接口标准,具有总线仲裁机制,非常适合在器件之间进行近距离、非经常性的数据通信。在它的协议体系中,传输数据时都会带上目的设备的设备地址,因此可以实现设备组网。 如果用通用IO口模拟I2C总线,并实现双向传输,则需一个输入输出口(SDA),另外还需一个输出口(SCL)。(注:I2C资料了解得比较少,这里的描述可能很不完备) UART总线是异步串口,因此一般比前两种同步串口的结构要复杂很多,一般由波特率产生器(产生的波特率等于传输波特率的16倍)、UART接收器、UART发送器组成,硬件上由两根线,一根用于发送,一根用于接收。 显然,如果用通用IO口模拟UART总线,则需一个输入口,一个输出口。 第三,从第二点明显可以看出,SPI和UART可以实现全双工,但I2C不行; 第四,看看牛人们的意见吧! wudanyu:I2C线更少,我觉得比UART、SPI更为强大,但是技术上也更加麻烦些,因为I2C需要有双向IO的支持,而且I2C使用上拉电阻,我觉得抗干扰能力较弱,一般用于同一板卡上芯片之间的通信,较少用于远距离通信。SPI实现要简单一些,UART需要固定的波特率,就是说两位数据的间隔要相等,而SPI 则无所谓,因为它是有时钟的协议。 quickmouse:I2C的速度比SPI慢一点,协议比SPI复杂一点,但是连线也比标准的SPI要少。

串行通信和并行通信图文解释: 并行通信传输中有多个数据位,同时在两个设备之间传输。发送设备将这些数据位通过 对应的数据线传送给接收设备,还可附加一位数据校验位。接收设备可同时接收到这些数据,不需要做任何变换就可直接使用。并行方式主要用于近距离通信。计算 机内的总线结构就是并行通信的例子。这种方法的优点是传输速度快,处理简单。 串行数据传输时,数据是一位一位地在通信线上传输的,先由具有几位总线的计算机内的发送设备,将几位并行数据经并--串转换硬件转换成串行方式,再逐位经 传输线到达接收站的设备中,并在接收端将数据从串行方式重新转换成并行方式,以供接收方使用。串行数据传输的速度要比并行传输慢得多,但对于覆盖面极其广 阔的公用电话系统来说具有更大的现实意义。 串行数据通信的方向性结构有三种,即单工、半双工和全双工。

串行传输和并行传输的区别: 从技术发展的情况来看,串行传输方式大有彻底取代并行传输方式的势头,USB 取代IEEE 1284,SATA取代PATA,PCI Express取代PCI……从原理来看,并行传输方式其实优于串行传输方式。通俗地讲,并行传输的通路犹如一条多车道的宽阔大道,而串行传输则是仅能允 许一辆汽车通过的乡间公路。以古老而又典型的标准并行口(Standard Parallel Port)和串行口(俗称COM口)为例,并行接口有8根数据线,数据传输率高;而串行接口只有1根数据线,数据传输速度低。在串行口传送1位的时间内, 并行口可以传送一个字节。当并行口完成单词“advanced”的传送任务时,串行口中仅传送了这个单词的首字母“a”。 根据组成字符的各个二进制位是否同时传输,字符编码在信源/信宿之间的传输分为并行传输和串行传输两种方式。 1、并行传输: 字符编码的各位(比特)同时传输。 特点: (1)传输速度快:一位(比特)时间内可传输一个字符; (2)通信成本高:每位传输要求一个单独的信道支持;因此如果一个字符包含8个二进制位,则并行传输要求8个独立的信道的支持; (3)不支持长距离传输:由于信道之间的电容感应,远距离传输时,可靠性较低。 2、串行传输: 将组成字符的各位串行地发往线路。 特点: (1)传输速度较低,一次一位; (2)通信成本也较低,只需一个信道。 (3)支持长距离传输,目前计算机网络中所用的传输方式均为串行传输。 方式: 串行传输有两种传输方式: 1、同步传输 2、异步传输 硬盘接口模式的区别,SATA的优点 PATA(IDE), SATA接口的区别以及SATA的优势

实验六总线数据传输控制实验 一、实验目的 1.理解总线的概念,了解总线的作用和特性。 2.掌握用总线传输数据的控制原理和方法。 二、实验原理 1.74LS374芯片的逻辑功能 2.了解通用寄存器部件的逻辑功能 三、实验过程 1.连线 1)连接实验一(输入、输出实验)的全部连线。 2)按逻辑原理图连接寄存器单元(REG UNIT)的B-R0,B-R1正脉冲信号。 3)连接寄存器单元(REG UNIT)的R0-B、R1-B到KA、KB,用KA、KB控制R0-B、 R1-B这两个低电平有效信号 4)连接运算器单元(ALU UNIT)S1、S0、M、299-B。 5)按逻辑原理图连接时钟单元(CLOCK UNIT)与微程序控制单元(MAIN CONTROL UNIT)的T4。

2.数据送R0操作过程 1)首先把手动控制开关单元(MANUAL UNIT)的控制开关全部拨到无效状态。 2)在输入数据开关拨一个实验数据(如“00001001”,即16进制的09H),把I/O-R 把实验数据送总线。 3)把B-R0信号拨动一下,即实现“1-0-1”,产生一个正脉冲,实验数据由总 线送0号通用寄存器(R0)保存。 4)把输入数据开关上的实验数据拨回到全0,拨上I/O-R控制开关,切断输入 数据与总线的联系,这时总线显示灯为“11111111”,处于悬空状态。 3.数据从R0读出送移位寄存器操作过程 1)拨下KA控制开关,产生R0-B 信号,把实验数据从R0送总线,总线显示灯 为“00001001”,显示R0寄存器状态 2)把299-B ,S1,S0,M拨成1111,确保时钟单元(CLOCK UNIT)的STEP/RUN 开关处于“STEP”状态,按一下“START”键发T4脉冲,把R0中的数据通过总线送入74LS299移位寄存器中。 3)拨上KA控制开关,使R0-B 信号无效,切断R0输出数据与总线的联系,总 线显示灯为“11111111”,处于悬空状态。 4.数据经移位寄存器移位后送R1的操作过程 1)把299-B ,S!,S0,M拨成0101,按下“START”键发T4脉冲,对74LS299移位寄存器中的数据进行一次带进位的循环右移,这时从总线上可看到移位后的实验数据。 2)把B-R1信号拨动一下,即实现“0—1—0”,产生一个正脉冲,实验数据通过总线送1号通用寄存器(R1)保存。 3)拨上299-B 控制开关,切断74LS299移位寄存器与总线的联系。

SERDES概述 写在开头:不出意外的话,这又是一个系列话题。包括串行,损耗,加重均衡等。小陈才疏学浅,只能写出个概述,望大神指正。 再写在开头:当小陈还是一个无忧无虑的大学生的时候,说过一句这样的话“懂你的人并不是你想要什么就给你什么,而是他给了你,你才发现这才是你想要的。”如Iphone之于手机,如频域之于信号分析。以前小陈觉得频域这东西不如时域好用,不明白这个想象中的东西怎么可能比实际存在的时域更加简单。直到脑子里能把一个个频域的点看成一个正弦波,直到发现一条复杂无比的通道能使用一个清晰的S参数表示。 为何串行 人们对高速的追求就像对美好生活的向往一样永无止境。在人们面前有两条路可以走,第一条是增加信道的数量,用更多的信道传输更多的信号,也就是我们所说的并行;第二条是提高单通道的信号速率,也就是我们所说的高速串行。 而在现在的高速传输中,SERDES早已成为了绝对的主流。主要是因为并行传输有着先天的劣势:时钟周期变得越来越短,并行的时序已经无法满足。 在之前的《串扰系列》中有说到,由于使用数字信号通信,信道的噪声容限有了很大的提升,DDR3信号的噪声裕量甚至能达到了600mV,相当于信号电平的40%。这40%的裕量将被反射,损耗,电源噪声,串扰等问题瓜分。串行信号同样面临着这样的问题,于是······ SERDES:“工程师爸爸,我上升沿陡,反射会比较严重!” 于是工程师把高速串行信号的驱动阻抗和接收阻抗都做成了100欧姆,与传输线相匹配:“我已经帮你把源端和末端两个最严重的反射给去掉啦,剩下的就靠你啦。” SERDES:“工程师爸爸,我翻转次数多,串扰会比较严重!”

多种工业应用串行总线特性及比较 由于在消费类电子产品、计算机外设、汽车和工业应用中增加了嵌入式功能,对低成本、高速和高可靠通信介质的要求也不断增长以满足这些应用,其结果是越来越多的处理器和控制器用不同类型的总线集成在一起,实现与PC软件、开发系统(如仿真器)或网络中的其它设备进行通信。目前流行的通信一般采用串行或并行模式,而串行模式应用更广泛。 微处理器中常用的集成串行总线是通用异步接收器传输总线、串行通信接口、同步外设接口(SPI)、内部集成电路(I2C) 和通用串行总线,以及车用串行总线,包括控制器区域网(CA N)和本地互连网(LIN)。这些总线在速度、物理接口要求和通信方法学上都有所不同。本文将对嵌入式系统设计的串行总线、驱动器和物理接口这些要求提供一个总体介绍,为选择最优总线提供指导并给出一个比较图表(表1)。为了说明方便起见,本文的阐述是基于微处理器的设计。 串行与并行相比 串行相比于并行的主要优点是要求的线数较少。例如,用在汽车工业中的LIN串行总线只需要一根线来与从属器件进行通信,Dallas公司的1-Wire总线只使用一根线来输送信号和电源。较少的线意味着所需要的控制器引脚较少。集成在一个微控制器中的并行总线一般需要8条或更多的线,线数的多少取决于设计中地址和数据的宽度,所以集成一个并行总线的芯片至少需要8个引脚来与外部器件接口,这增加了芯片的总体尺寸。相反地,使用串行总线可以将同样的芯片集成在一个较小的封装中。 另外,在PCB板设计中并行总线需要更多的线来与其它外设接口,使PCB板面积更大、更复杂,从而增加了硬件成本。此外,工程师还可以很容易地将一个新器件加到一个串行网络中

实验报告 专业:计算机科学与技术 班级:计算机科学与技术(1)班学号:201024131147 姓名:赵倩倩 课程名称:计算机组成原理 学年:2010—2011 学期1 课程类别:专业必修 试验时间:2011年11月7日

实验四:总线传输实验 一、实验目的 (1)理解总线的概念及其特性 (2)掌握总线传输控制特性 二、实验原理及基本技术路线图(方框原理图) 总线传输框如图5.4-1所示,他将几种不同的设备挂至总线上,有存储器、输入设备、输出设备、寄存器。这些设备都需要三态输出控制,按照传输要求恰当有序的控制它们,就可实现总线信息传输。 基本实验要求如下: 根据挂起在总线上的几个基本条件,设计一个简单的流程; 1)输入设备将一个数打入R0寄存器。 2)输入设备将另一个数打入地址寄存器。 3)将R0寄存器中的数写入带当前的地址的寄存器中。 4)将当前地址的寄存器中的数用LE数码管显示。 三、所用仪器、材料(设备名称、型号、规格等) TDN-CM+或TDN-CM++教学实验系统一台 四、实验方法、步骤 1)按照图5.4-2试验接线图进行连线。

(2)实验的具体操作步骤图如图5.4-3所示。 首先应关闭所有三态门(SW-B=1,R0-B=1,LED-B=1),并将关联的信号置为LDAR=0,LDR0=0,W/R(LED)=1,W/R(LED)=1.然后参照如下操作流程,先将数据开关打入到R0中;然后继续给开关置数,拨动LDR0控制信号做0→1→0动作,产生一个上升沿将数据打入到R0中;然后继续给数据开关置数,拨动LDAR控制信号做0→1→0动作产生一个上升沿将数据打入到AR中;关闭数据开关三态门,打开R0寄存器输出控制,使寄存器输出,使寄存器处于写状态(W/R=0,CS=0),将R0中的数写到存储器中;关闭存储器片选,关闭R0寄存器输出,使存储器处于读状态(W/R=1,CS=0),打开LED片选,拨动LED的W/R控制信号1→0→1动作,产生一个上升沿将数据打入到LED中。 五、实验过程原始记录(数据、图表、计算等) 打开输出三态门,在输入单元由开关给出要保存的数据00110111(37H),拨动控制信号LDR0,可将数据打入到寄存器R0中,继续给数据开关置数,这时

微处理器中常用的集成串行总线就是通用异步接收器传输总线(UART)、串行通 信接口(SCI)与通用串行总线(USB)等,这些总 线在速度、物理接口要求与通信方法学上都 有所不同。本文详细介绍了嵌入式系统设计 的串行总线、驱动器与物理接口的特性,并为 总线最优选择提供性能比较与选择建议。 由于在消费类电子产品、计算机外设、汽车与工业应用中增加了嵌入式功能,对低成本、高速与高可靠通信介质的要求也不断增长以满足这些应用,其结果就是越来越多的处理器与控制器用不同类型的总线集成在一起,实现与PC软件、开发系统(如仿真器)或网络中的其它设备进行通信。目前流行的通信一般采用串行或并行模式,而串行模式应用更广泛。 微处理器中常用的集成串行总线就是通用异步接收器传输总线、串行通信接口、同步外设接口(SPI)、内部集成电路(I2C) 与通用串行总线,以及车用串行总线,包括控制器区域网(CAN)与本地互连网(LIN)。这些总线在速度、物理接口要求与通信方法学上都有所不同。本文将对嵌入式系统设计的串行总线、驱动器与物理接口这些要求提供一个总体介绍,为选择最优总线提供指导并给出一个比较图表(表1)。为了说明方便起见,本文的阐述就是基于微处理器的设计。 串行与并行相比

串行相比于并行的主要优点就是要求的线数较 少。例如,用在汽车工业中的LIN串行总线只需要一根线来与从属器件进行通信,Dallas公司的1-Wire总线只使用一根线来输送信号与电源。较少的线意味着所需要的控制器引脚较少。集成在一个微控制器中的并行总线一般需要8条或更多的线,线数的多少取决于设计中地址与数据的宽度,所以集成一个并行总线的芯片至少需要8个引脚来与外部器件接口,这增加了芯片的总体尺寸。相反地,使用串行总线可以将同样的芯片集成在一个较小的封装中。 另外,在PCB板设计中并行总线需要更多的线来与其它外设接口,使PCB板面积更大、更复杂,从而增加了硬件成本。此外,工程师还可以很容易地将一个新器件加到一个串行网络中去,而且不会影响网络中的其它器件。例如,可以很容易地去掉总线上旧器件并用新的来替代。 串行总线的故障自诊断与调试也非常简单,可以很容易地跟踪网络中一个有故障的器件并用新器件替换而不会干扰网络。但另一方面,并行总线比串行速度快。例如,Rambus公司的“Redwood”总线速度可高达6、4GHz,而最高的串行速度不会超过几个兆赫。 在工业与汽车应用中常用的串行协议 1、UART

三、SPI是英文Serial Peripheral Interface的缩写,中文意思是串行外围设备接口,SPI是Motorola公司推出的一种同步串行通讯方式,是一种三线同步总线,因其硬件功能很强,与SPI有关的软件就相当简单,使CPU有更多的时间处理其他事务。 SPI概述 SPI:高速同步串行口。3~4线接口,收发独立、可同步进行. SPI,是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。是Motorola首先在其MC68HCXX系列处理器上定义的。SPI接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB 的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议,比如AT91RM9200. SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI 和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT或INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。 SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。也是所有基于SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)。 (1)SDO –主设备数据输出,从设备数据输入 (2)SDI –主设备数据输入,从设备数据输出 (3)SCLK –时钟信号,由主设备产生 (4)CS –从设备使能信号,由主设备控制 其中CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。这就允许在同一总线上连接多个SPI设备成为可能。 接下来就负责通讯的3根线了。通讯是通过数据交换完成的,这里先要知道SPI是串行通讯协议,也就是说数据是一位一位的传输的。这就是SCK时钟线存在的原因,由SCK提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。数据输出通过SDO 线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。完成一位数据传输,输入也使用同样原理。这样,在至少8次时钟信号的改变(上沿和下沿为一次),就可以完成8位数据的传输。 要注意的是,SCK信号线只由主设备控制,从设备不能控制信号线。同样,在一个基于SPI的设备中,至少有一个主控设备。这样传输的特点:这样的传输方式有一个优点,与普通的串行通讯不同,普通的串行通讯一次连续传送至少8位数据,而SPI允许数据一位一位的传送,甚至允许暂停,因为SCK时钟线由主控设备控制,当没有时钟跳变时,从设备不采集或传送数据。也就是说,主设备通过对SCK时钟线的控制可以完成对通讯的控制。SPI还是一个数据交换协议:因为SPI的数据输入和输出线独立,所以允许同时完成数据的输入和输出。不同的SPI设备的实现方式不尽相同,主要是数据改变和采集的时间不同,在时钟信号上沿或下沿采集有不同定义,具体请参考相关器件的文档。 在点对点的通信中,SPI接口不需要进行寻址操作,且为全双工通信,显得简单高效。在多个从设备的系统中,每个从设备需要独立的使能信号,硬件上比I2C系统要稍微复杂一些。 最后,SPI接口的一个缺点:没有指定的流控制,没有应答机制确认是否接收到数据。 AT91RM9200的SPI接口主要由4个引脚构成:SPICLK、MOSI、MISO及/SS,其中SPICLK是整个SPI总线的公用时钟,MOSI、MISO作为主机,从机的输入输出的标志,MOSI是主机的输出,从机的输入,MISO 是主机的输入,从机的输出。/SS是从机的标志管脚,在互相通信的两个SPI总线的器件,/SS管脚的电平低的是从机,相反/SS管脚的电平高的是主机。在一个SPI通信系统中,必须有主机。SPI总线可以配置成单主单从,单主多从,互为主从。 SPI的片选可以扩充选择16个外设,这时PCS输出=NPCS,说NPCS0~3接4-16译码器,这个译码器是需要外接4-16译码器,译码器的输入为NPCS0~3,输出用于16个外设的选择。 [编辑本段] SPI协议举例

计算机科学与技术系 实验报告 专业名称计算机科学与技术 课程名称计算机组成与结构 项目名称具有基本输入输出功能的总线接口实验班级 学号 姓名 同组人员无 实验日期 2015-10-24

一、实验目的 1.理解总线的概念及其特性; 2.掌握控制总线的功能和应用。 二、实验逻辑原理图与分析 2.1 实验逻辑原理图及分析 由于存储器和输入、输出设备最终是要挂接到外部总线上,所以需要外部总线提供数据信号、地址信号以及控制信号。在该实验平台中,外部总线分为数据总线、地址总线和控制总线,分别为外设提供上述信号。外部总线和CPU内总线之间通过三态门连接,同时实现了内外总线的分离和对数据流向的控制。地址总线可以为外部设备提供地址信号和片选信号。由地址总线的高位进行译码,系统的I/O地址空间被分为四个区,如图所示: 为了实现对于MEM和外设的读写操作,还需要一个读写控制逻辑,使得CPU 能控制MEM和I/O设备的读写,实验中的读写控制逻辑如下图所示:

三、 数据通路图及分析 (画出数据通路图并作出分析) 在理解读写控制逻辑的基础上设计一个总线传输的实验。实验所用总线传输实验框图如下图所示,它将几种不同的设备挂至总线上,有存储器、输入设备、输出设备、寄存器。这些设备都需要有三态输出控制,按照传输要求恰当有序的控制它们,就可实现总线信息传输。 分析:① 输入设备将一个数打入RO 寄存器; ② 输入设备将另一个数打入地址寄存器; ③ 将RO 寄存器中的数写入到当前地址的寄存器中; ④ 将当前地址的寄存器中的数用LED 数码管显示。 四、实验数据和结果分析 4.1 实验结果数据如图所示 ⑴输入设备将11H 打入RO 寄存器 ⑵将RO 中的数据11H 打入寄存器01H 单元

10.1指令流水 一、如何提高机器速度 1. 提高访存速度 2. 提高I/O 和主机之间的传送速度?提高整机处理能力高速芯片 Cache 多体并行 I/O 处理机 DMA 多总线 通道 高速器件 改进系统结构,开发系统的并行性 中断 3. 提高运算器速度高速芯片 改进算法 快速进位链

二、系统的并行性 时间上互相重叠 2. 并行性的等级 指令级(指令之间) (指令内部) 过程级(程序、进程)两个或两个以上事件在同一时刻发生 两个或两个以上事件在同一时间段发生 并行 1. 并行的概念 粗粒度软件实现细粒度 硬件实现 并发同时

取指令3执行指令3三、指令流水原理 2. 指令的二级流水 1. 指令的串行执行 取指令取指令部件 完成 总有一个部件空闲 指令预取 若取指和执行阶段时间上完全重叠… 执行指令 执行指令部件完成 取指令1执行指令1 取指令2执行指令2 取指令3 执行指令3 取指令2执行指令2 取指令1执行指令1

必须等上条指令执行结束,才能确定下条指令的地址, 造成时间损失 3. 影响指令流水效率加倍的因素 (1) 执行时间> 取指时间 (2) 条件转移指令对指令流水的影响 解决办法? 取指令部件 指令部件缓冲区 执行指令部件 猜测法

4. 指令的六级流水 串行执行 6 ×9 =54个时间单位完成一条指令 6 个时间单位 CO FO EI WO DI FI CO FO EI WO DI FI CO FO EI WO DI FI CO FO EI WO DI FI CO FO EI WO DI FI CO FO EI WO DI FI CO FO EI WO DI FI CO FO EI WO DI FI CO FO EI WO DI FI 指令1指令2指令3指令4 指令5指令6指令7指令8 指令9 1 2 3 4 5 6 7 8 9 10 11 12 13 14 t

实验报告 一、实验设计方案 实验框图 实验原理 1、SW_BUS低电平有效,此时将K[7..0]的数据送到总线,通过L[7..0]双向数据端口 输出显示总线的数据,使用的芯片是74244八位单向三态缓冲器; 2、R3_BUS、R2_BUS、R1_BUS低电平有效,其功能是将数据要传入的寄存器打开, 若相应的lddr为1(高电平有效),将数据传入相应的寄存器; 3、总线数据传输时,控制信号中只能有一个有效,寄存器的端口送至数据总线,所以 每个BUS接口对应每个R寄存器的显示; 4、通过读写的双重作用,实现R1和R2的数据交换。 表达式 Reg3←Reg1;Reg1←Reg2;Reg2←Reg3 方法一:vhdl代码 library ieee; use ieee.std_logic_1164.all; entity exp_bus is port(clk:in std_logic; sw_bus,r1_bus,r2_bus,r3_bus:in std_logic; k:in std_logic_vector(7 downto 0); lddr:in std_logic_vector(3 downto 1); l:inout std_logic_vector(7 downto 0)); end exp_bus; architecture rtl of exp_bus is

signal r1,r2,r3,bus_Reg:std_logic_vector(7 downto 0); begin ldreg:process(clk,lddr,bus_reg) begin if clk'event and clk='1' then if lddr(1)='1'then r1<=bus_reg; elsif lddr(2)='1'then r2<=bus_reg; elsif lddr(3)='1'then r3<=bus_reg; end if; end if; end process; bus_reg<=k when (sw_bus='0'and r1_bus='1'and r2_bus='1'and r3_bus='1')else r1 when (sw_bus='1'and r1_bus='0'and r2_bus='1'and r3_bus='1')else r2 when (sw_bus='1'and r1_bus='1'and r2_bus='0'and r3_bus='1')else r3 when (sw_bus='1'and r1_bus='1'and r2_bus='1'and r3_bus='0')else (others=>'0'); l<=bus_reg when (sw_bus='0' or r1_bus='0' or r2_bus='0' or r3_bus='0')else (others=>'Z'); end rtl; 方法二:bdf实验原理图

实验四:总线控制实验报告 一、实验目的: 1.理解总线的概念及其特性; 2.掌握总线传输控制特性; 二、实验设备 TDN-CM+计算机组成原理教学实验系统一台,排线若干。 三、实验内容 1. 总线的基本概念 总线是多个系统内部之间进行数据传输的公共通路,是构成计算机系统的骨架。借助总线连接,计算机在系统各个部件之间实现传送地址、数据和控制信息的操作。因此,所谓总线就是能为多个部件服务的一组公共信息线。 1.实验原理 实验所用总线传输实验框图如图7-1所示,它将几种不同的设备挂至总线上,有存储器、输入设备、输出设备、寄存器。这些设备都需要有三态输出控制,按照传输要求恰当有序的控制它们,就可实现信息传输。 实验要求 根据挂在总线上的几个基本部件,设计一个简单的流程: ⑴输入设备将一个数打入R0寄存器; ⑵输入设备将另一个数打入地址寄存器; ⑶将R0寄存器中的数写入到当前的存储器中; ⑷将当前地址存储器中的数用LED数码管显示。

1.实验步骤 ⑴按照图7-2实验接线图进行接线。 ⑵具体操作步骤如下:

初始状态应设为:关闭所有的三态门(SW-B=1,CE=1,R0-B=1),其他控制信号为:LDAR=0,LDR0=0,W/R(RAM)=1,W/R(LED)=1 第一组数据:(R0)=11H,(AR)=21H LED显示的数据为: 第二组数据:(R0)=A5H,(AR)=22H LED显示的数据为: 第三组数据:(R0)=FCH,(AR)=23H LED显示的数据为: 注意事项: 1、所有导线使用前须测通断; 2、不允许带电接线; 3、“0”——亮“1”——灭; 4、注意连接线的颜色、数据的高低位。 四、实验总结 实验过程出现了很多问题,只有在实验前做好充分准备,才能减少在实验过程中遇到的难题。实验主要是使我们理解总线的概念及其特性,并掌握总线传输控制特性,这对我们深入了解计算机组成原理这门课程更加有利。

摘要:集成电路设计越来越向系统级的方向发展,并且越来越强调模块化的设计。SPI(Serial Peripheral Bus)总线是Motorola公司提出的一个同步串行外设接口,容许CPU 与各种外围接口器件以串行方式进行通信、交换信息。本文简述了SPI总线的特点,介绍了其4条信号线,SPI串行总线接口的典型应用。重点描述了SPI串行总线接口在一款802.11b芯片中的位置,及该接口作为基带和射频的通讯接口所完成的功能,并给出了用硬件描述语言Verilog HDL 实现该接口的部分程序。该实现已经在Modelsim 中完成了仿真, 并经过了FPGA 验证, 最后给出了仿真和验证的结果。 在SOC设计中,利用EDA 工具设计芯片实现系统功能已经成为支撑电子设计的通用平台.并逐步向支持系统级的设计方向发展。而且,在设计过程中,越来越强调模块化设计。 SPI总线是Motorola公司提出的一个同步串行外设接口,具有接口线少、通讯效率高等特点。本文给出的是利用Verilog HDL实现的SPI总线模块,该模块是802.11b无线局域网芯片中一个子模块,该模块完成了芯片中基带(base band)与RF的通讯工作. 1 SPI总线接口概述 SPI(Serial Parallel Bus)总线是Motorola公司提出的一个同步串行外设接口,允许CPU 与各种外围接口器件(包括模/数转换器、数/模转换器、液晶显示驱动器等)以串行方式进行通信、交换信息。他使用4条线:串行时钟线(SCK)、主机输入/从机输出线(MISO)、主机输出/从机输入线(MOSI)、低电平有效的使能信号线(CS)。这样,仅需3~4根数据线和控制线即可扩展具有SPI接口的各种I/O 器件其典型结构如图1所示。 SPI总线具有以下特点: (1)连线较少,简化电路设计。并行总线扩展方法通常需要8根数据线、8~16根地址线、2~3根控制线。而这种设计,仅需4根数据和控制线即可完成并行扩展所实现的功能。 (2)器件统一编址,并与系统地址无关,操作SPI独立性好。 (3)器件操作遵循统一的规范,使系统软硬件具有良好的通用性。 2 SPI总线接口的设计与实现 该模块是802.1lb无线局域网芯片中的一子模块,其在芯片中的位置如图2所示。