数字逻辑实验实验报告

脚分配、1)分析输入、输出,列出方程。根据方程和IP 核库判断需要使用的门电路以及个数。

2)创建新的工程,加载需要使用的IP 核。

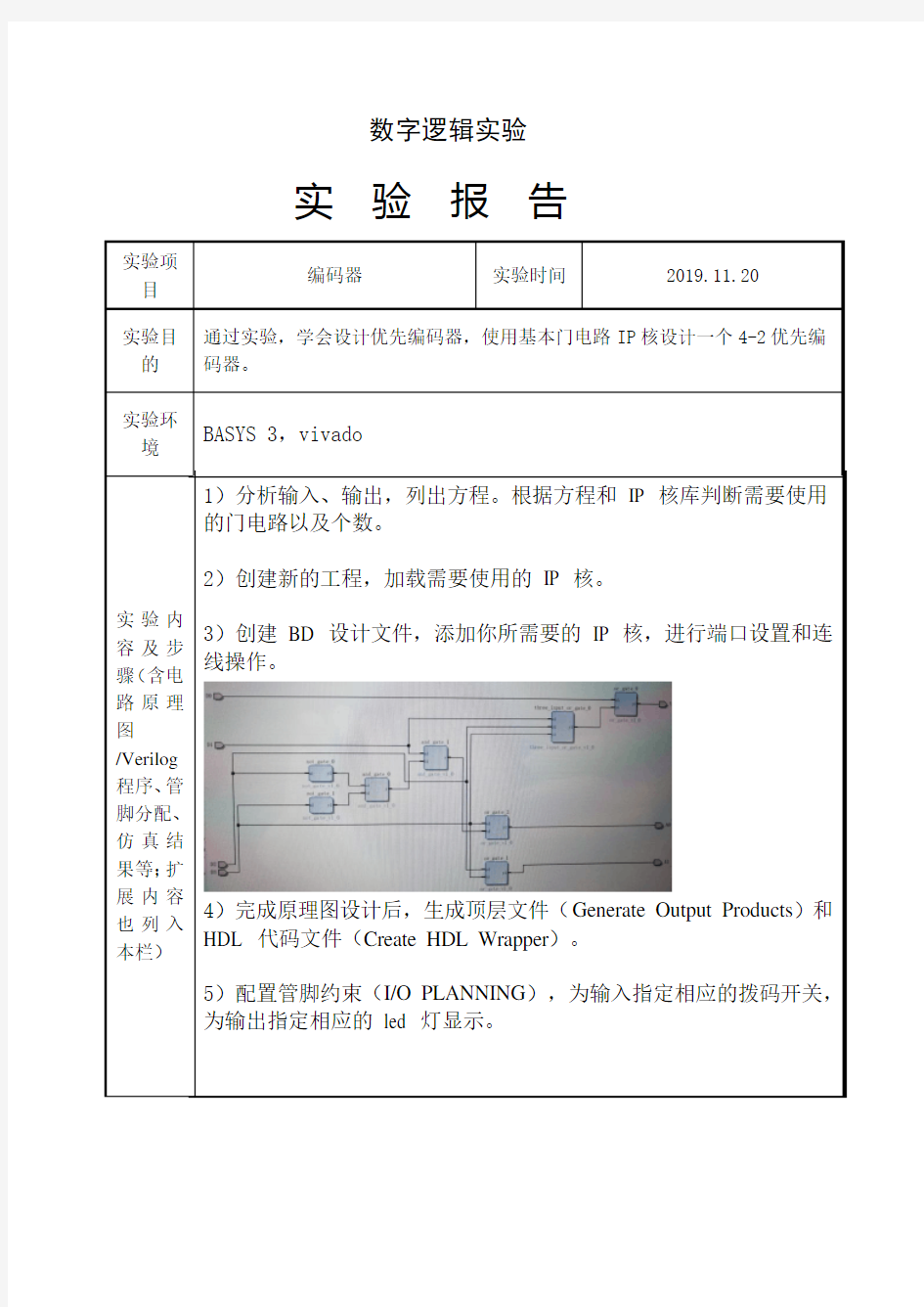

3)创建BD 设计文件,添加你所需要的IP 核,进行端口设置和连线操作。

4)完成原理图设计后,生成顶层文件(Generate Output Products)和HDL 代码文件(Create HDL Wrapper)。

5)配置管脚约束(I/O PLANNING),为输入指定相应的拨码开关,为输出指定相应的led 灯显示。

6)综合、实现、生成bitstream。

7)仿真验证,依据真值表,在实验板验证试验结果。

实验报告说明

数字逻辑课程组

实验名称列入实验指导书相应的实验题目。

实验目的目的要明确,要抓住重点,可以从理论和实践两个方面考虑。可参考实验指导书的内容。在理论上,验证所学章节相关的真值表、逻辑表达式或逻辑图的实际应用,以使实验者获得深刻和系统的理解,在实践上,掌握使用软件平台及设计的技能技巧。一般需说明是验证型实验还是设计型实验,是创新型实验还是综合型实验。

实验环境实验用的软硬件环境(配置)。

实验内容(含电路原理图/Verilog程序、管脚分配、仿真结果等;扩展内容也列入本栏)这是实验报告极其重要的内容。这部分要写明经过哪几个步骤。可画出流程图,再配以相应的文字说明,这样既可以节省许多文字说明,又能使实验报告简明扼要,清楚明白。

实验结果分析数字逻辑的设计与实验结果的显示是否吻合,如出现异常,如何修正并得到正确的结果。

实验方案的缺陷及改进意见在实验过程中发现的问题,个人对问题的改进意见。

心得体会、问题讨论对本次实验的体会、思考和建议。

实验四 译码器、编码器及其应用 实验人员: 班号: 学号: 一、实验目的 (1) 掌握中规模集成译码器的逻辑功能和使用方法; (2) 熟悉掌握集成译码器和编码器的应用; (3) 掌握集成译码器的扩展方法。 二、实验设备 数字电路实验箱,74LS20,74LS138。 三、实验容 (1) 74LS138译码器逻辑功能的测试。将74LS138输出Y 0????~Y 7????接数字实验箱LED 管,地址Y 2Y 1Y 0输入接实验箱开关,使能端接固定电平(Y YY 或GND )。电路图如Figure 1所示: Figure 1 E Y 1YY 2Y ?????????? YY 2Y ??????????≠100时,任意拨动开关,观察LED 显示状态,记录观察结果。 E Y 1YY 2Y ?????????? YY 2Y ??????????=100时,按二进制顺序拨动开关,观察LED 显示状态,并与功能表对照,记录观察结果。 用Multisim 进行仿真,电路如Figure 2所示。将结果与上面实验结果对照。

Figure 2 (2) 利用3-8译码器74LS138和与非门74LS20实现函数: Y =Y ???Y ???+Y ???Y ???+YYY 四输入与非门74LS20的管脚图如下: 对函数表达式进行化简: Y =Y ???Y ???+Y ???Y ???+YYY =Y ???Y ???Y ???+Y ???Y ???Y +A Y ???Y ???+YYY =Y 0+Y 1+Y 4+Y 7=Y 0????Y 1????Y 4????Y 7????????????????????? 按Figure 3所示的电路连接。并用Multisim 进行仿真,将结果对比。 Figure 3

实验一集成电路的逻辑功能测试 一、实验目的 1、掌握Multisim软件的使用方法。 2、掌握集成逻辑门的逻辑功能。 3、掌握集成与非门的测试方法。 二、实验原理 TTL集成电路的输入端和输出端均为三极管结构,所以称作三极管、三极管逻辑电路(Transistor -Transistor Logic 简称TTL电路。54 系列的TTL电路和74 系列的TTL电路具有完全相同的电路结构和电气性能参数。所不同的是54 系列比74 系列的工作温度范围更宽,电源允许的范围也更大。74 系列的工作环境温度规定为0—700C,电源电压工作范围为5V±5%V,而54 系列工作环境温度规定为-55— ±1250C,电源电压工作范围为5V±10%V。 54H 与74H,54S 与74S 以及54LS 与74LS 系列的区别也仅在于工作环境温度与电源电压工作范围不同,就像54 系列和74 系列的区别那样。在不同系列的TTL 器件中,只要器件型号的后几位数码一样,则它们的逻辑功能、外形尺寸、引脚排列就完全相同。 TTL 集成电路由于工作速度高、输出幅度较大、种类多、不易损坏而使用较广,特别对我们进行实验论证,选用TTL 电路比较合适。因此,本实训教材大多采用74LS(或74系列TTL 集成电路,它的电源电压工作范围为5V±5%V,逻辑高电平为“1”时≥2.4V,低电平为“0”时≤0.4V。 它们的逻辑表达式分别为:

图1.1 分别是本次实验所用基本逻辑门电路的逻辑符号图。 图1.1 TTL 基本逻辑门电路 与门的逻辑功能为“有0 则0,全1 则1”;或门的逻辑功能为“有1则1,全0 则0”;非门的逻辑功能为输出与输入相反;与非门的逻辑功能为“有0 则1,全1 则0”;或非门的逻辑功能为“有1 则0,全0 则1”;异或门的逻辑功能为“不同则1,相同则0”。 三、实验设备

学生学号0121410870432实验成绩 学生实验报告书 实验课程名称逻辑与计算机设计基础 开课学院计算机科学与技术学院 指导教师姓名肖敏 学生姓名付天纯 学生专业班级物联网1403 2015--2016学年第一学期

译码器的设计与实现 【实验要求】: (1)理解译码器的工作原理,设计并实现n-2n译码器,要求能够正确地根据输入信号译码成输出信号。(2)要求实现2-4译码器、3-8译码器、4-16译码器、8-28译码器、16-216译码器、32-232译码器。 【实验目的】 (1)掌握译码器的工作原理; (2)掌握n-2n译码器的实现。 【实验环境】 ◆Basys3 FPGA开发板,69套。 ◆Vivado2014 集成开发环境。 ◆Verilog编程语言。 【实验步骤】 一·功能描述 输入由五个拨码开关控制,利用led灯输出32种显示 二·真值表

三·电路图和表达式

四·源代码 module decoder_5( input [4:0] a, output [15:0] d0 ); reg [15:0] d0; reg [15:0] d1; always @(a) begin case(a) 5'b00000 :{d1,d0}=32'b1000_0000_0000_0000_0000_0000_0000_0000; 5'b00001 :{d1,d0}=32'b0100_0000_0000_0000_0000_0000_0000_0000; 5'b00010 :{d1,d0}=32'b0010_0000_0000_0000_0000_0000_0000_0000; 5'b00011 :{d1,d0}=32'b0001_0000_0000_0000_0000_0000_0000_0000; 5'b00100 :{d1,d0}=32'b0000_1000_0000_0000_0000_0000_0000_0000; 5'b00101 :{d1,d0}=32'b0000_0100_0000_0000_0000_0000_0000_0000; 5'b00110 :{d1,d0}=32'b0000_0010_0000_0000_0000_0000_0000_0000; 5'b00111 :{d1,d0}=32'b0000_0001_0000_0000_0000_0000_0000_0000; 5'b01000 :{d1,d0}=32'b0000_0000_1000_0000_0000_0000_0000_0000; 5'b01001 :{d1,d0}=32'b0000_0000_0100_0000_0000_0000_0000_0000; 5'b01010 :{d1,d0}=32'b0000_0000_0010_0000_0000_0000_0000_0000; 5'b01011 :{d1,d0}=32'b0000_0000_0001_0000_0000_0000_0000_0000; 5'b01100 :{d1,d0}=32'b0000_0000_0000_1000_0000_0000_0000_0000; 5'b01101 :{d1,d0}=32'b0000_0000_0000_0100_0000_0000_0000_0000; 5'b01110 :{d1,d0}=32'b0000_0000_0000_0010_0000_0000_0000_0000; 5'b01111 :{d1,d0}=32'b0000_0000_0000_0001_0000_0000_0000_0000; 5'b10000 :{d1,d0}=32'b0000_0000_0000_0000_1000_0000_0000_0000; 5'b10001 :{d1,d0}=32'b0000_0000_0000_0000_0100_0000_0000_0000; 5'b10010 :{d1,d0}=32'b0000_0000_0000_0000_0010_0000_0000_0000; 5'b10011 :{d1,d0}=32'b0000_0000_0000_0000_0001_0000_0000_0000; 5'b10100 :{d1,d0}=32'b0000_0000_0000_0000_0000_1000_0000_0000; 5'b10101 :{d1,d0}=32'b0000_0000_0000_0000_0000_0100_0000_0000; 5'b10110 :{d1,d0}=32'b0000_0000_0000_0000_0000_0010_0000_0000; 5'b10111 :{d1,d0}=32'b0000_0000_0000_0000_0000_0001_0000_0000; 5'b11000 :{d1,d0}=32'b0000_0000_0000_0000_0000_0000_1000_0000; 5'b11001 :{d1,d0}=32'b0000_0000_0000_0000_0000_0000_0100_0000; 5'b11010 :{d1,d0}=32'b0000_0000_0000_0000_0000_0000_0010_0000;

实验报告 1、基本门电路 一、实验目的 1、熟悉EDA工具的使用;仿真基本门电路。掌握基于Verilog的基本门电路的设计及其验证。 2、熟悉利用EDA工具进行设计及仿真的流程。基本门电路的程序烧录及验证。 3、学习针对实际门电路芯片74HC00、74HC02、74HC0 4、74HC08、74HC32、74HC86进行VerilogHDL设计的方法。 二、实验环境 Libero仿真软件。 三、实验内容 1、掌握Libero软件的使用方法。 2、进行针对74系列基本门电路的设计,并完成相应的仿真实验。 3、参考教材中相应章节的设计代码、测试平台代码(可自行编程),完成74HC00、74HC02、74HC0 4、74HC08、74HC32、74HC86相应的设计、综合及仿真。 4、提交针对74HC00、74HC02、74HC04、74HC08、74HC32、74HC86(任选一个 ....)的综合结果,以及相应的仿真结果。 四、实验结果和数据处理 1、所有 ..模块及测试平台代码清单 //74HC00代码-与非门 // module HC00(A,B,Y); input [4:1]A,B;

assign Y=~(A&B); endmodule //74HC00测试平台代码 // `timescale 1ns/1ns module testbench(); reg [4:1]a,b; wire [4:1]y; HC00 u1(a,b,y); initial begin a=4'b0000;b=4'b0001; #10 b=b<<1; #10 b=b<<1; #10 b=b<<1; a=4'b1111;b=4'b0001; #10 b=b<<1; #10 b=b<<1; #10 b=b<<1; end endmodule //74HC02代码-或非门 // module HC02(A,B,Y);

实验三译码器与编码器的设计与仿真 一、实验内容 1.参照芯片74LS138的电路结构,用VHDL语言设计3-8译码器; 2.参照芯片74LS148的电路结构,用VHDL语言设计8-3优先编码器。二、电路功能介绍 1.74148:8-3优先编码器(8 to 3 Priority Encoder) 用途:将各种输入信号转换成一组二进制代码,使得计算机可以识别这一信号的作用。键盘里就有大家天天打交道的编码器,当你敲击按键时,被敲击的按键被键盘里的编码器编码成计算机能够识别的ASCII码。译码器与编码器的功能正好相反。 2.74138:3-8译码器(3 to 8 Demultiplexer),也叫3-8解码器 用途:用一组二进制代码来产生各种独立的输出信号,这种输出信号可以用来执行不同的工作。显示器中的像素点受到译码器的输出控制。 逻辑框图:用逻辑符号(Symbol)来解释该电路输入与输出信号之间的逻辑关系,既省事又直观。如下图所示。 一、编码器 1.VHDL实现 library IEEE; use IEEE.std_logic_1164.all; entity pencoder is port ( i7,i6,i5,i4,i3,i2,i1,i0:in STD_LOGIC; a2,a1,a0,idle:out STD_LOGIC); 解 码 信 号 输 出 端低 电 平 有 效 代 码 输入 端 使能输入端

end pencoder; architecture pencoder_arch of pencoder is signal h:STD_LOGIC_VECTOR(7 downto 0); begin h(7)<=i7; h(6)<=i6 and not i7; h(5)<=i5 and not i6 and not i7; h(4)<=i4 and not i5 and not i6 and not i7; h(3)<=i3 and not i4 and not i5 and not i6 and not i7; h(2)<=i2 and not i3 and not i4 and not i5 and not i6 and not i7; h(1)<=i1 and not i2 and not i3 and not i4 and not i5 and not i6 and not i7; h(0)<=i0 and not i1 and not i2 and not i3 and not i4 and not i5 and not i6 and not i7; idle<=not i0 and not i1 and not i2 and not i3 and not i4 and not i5 and not i6 and not i7; a0<=h(1) or h(3) or h(5) or h(7); a1<=h(2) or h(3) or h(6) or h(7); a2<=h(4) or h(5) or h(6) or h(7); 2.波形图:

数字逻辑电路 实验报告 指导老师: 班级: 学号: 姓名: 时间: 第一次试验一、实验名称:组合逻辑电路设计

二、试验目的: 1、掌握组合逻辑电路的功能测试。 2、验证半加器和全加器的逻辑功能。 3、、学会二进制数的运算规律。 三、试验所用的器件和组件: 二输入四“与非”门组件3片,型号74LS00 四输入二“与非”门组件1片,型号74LS20 二输入四“异或”门组件1片,型号74LS86 四、实验设计方案及逻辑图: 1、设计一位全加/全减法器,如图所示: 电路做加法还是做减法是由M决定的,当M=0时做加法运算,当M=1时做减法运算。当作为全加法器时输入信号A、B和Cin分别为加数、被加数和低位来的进位,S 为和数,Co为向上的进位;当作为全减法时输入信号A、B和Cin分别为被减数,减数和低位来的借位,S为差,Co为向上位的借位。 (1)输入/输出观察表如下: (2)求逻辑函数的最简表达式 函数S的卡诺图如下:函数Co的卡诺如下: 化简后函数S的最简表达式为: Co的最简表达式为:

(3)逻辑电路图如下所示: 2、舍入与检测电路的设计: 用所给定的集成电路组件设计一个多输出逻辑电路,该电路的输入为8421码,F1为“四舍五入”输出信号,F2为奇偶检测输出信号。当电路检测到输入的代码大于或等于5是,电路的输出F1=1;其他情况F1=0。当输入代码中含1的个数为奇数时,电路的输出F2=1,其他情况F2=0。该电路的框图如图所示: (1)输入/输出观察表如下: B8 B4 B2 B1 F2 F1 0 0 0 0 0 0 0 0 0 1 1 0 0 0 1 0 1 0 0 0 1 1 0 0 0 1 0 0 1 0 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 1 1 1 1 0 0 0 1 1 1 0 0 1 0 1 1 0 1 0 0 1 1 0 1 1 1 1 1 1 0 0 0 1 1 1 0 1 1 1

数字逻辑实验报告(2) 姓名: 学号: 班级: 指导教师: 计算机科学与技术学院 20 年月日

数字逻辑实验报告(2)无符号数的乘法器设计

一、无符号数的乘法器设计 1、实验名称 无符号数的乘法器的设计。 2、实验目的 要求使用合适的逻辑电路的设计方法,通过工具软件logisim进行无符号数的乘法器的设计和验证,记录实验结果,验证设计是否达到要求。 通过无符号数的乘法器的设计、仿真、验证3个训练过程,使同学们掌握数字逻辑电路的设计、仿真、调试的方法。 3、实验所用设备 Logisim2.7.1软件一套。 4、实验内容 (1)四位乘法器设计 四位乘法器Mul4 4实现两个无符号的4位二进制数的乘法运算,其结构框图如图3-1所示。设被乘数为b(3:0),乘数为a(3:0),乘积需要8位二进制数表示,乘积为p(7:0)。 图3-1 四位乘法器结构框图 四位乘法器运算可以用4个相同的模块串接而成,其内部结构如图3-2所示。每个模块均包含一个加法器、一个2选1多路选择器和一个移位器shl。 图3-2中数据通路上的数据位宽都为8,确保两个4位二进制数的乘积不会发生溢出。shl是左移一位的操作,在这里可以不用逻辑器件来实现,而仅通过数据连线的改变(两个分线器错位相连接)就可实现。

a(0)a(1)a(2)a(3) 图3-2 四位乘法器内部结构 (2)32 4乘法器设计 32 4乘法器Mul32 4实现一个无符号的32位二进制数和一个无符号的4位二进制数的乘法运算,其结构框图如图3-3所示。设被乘数为b(31:0),乘数为a(3:0),乘积也用32位二进制数表示,乘积为p(31:0)。这里,要求乘积p能用32位二进制数表示,且不会发生溢出。 图3-3 32 4乘法器结构框图 在四位乘法器Mul4 4上进行改进,将数据通路上的数据位宽都改为32位,即可实现Mul32 4。 (3)32 32乘法器设计 32 32乘法器Mul32 32实现两个无符号的32位二进制数的乘法运算,其结构框图如图3-4所示。设被乘数为b(31:0),乘数为a(31:0),乘积也用32位二进制数表示,乘积为p(31:0)。这里,要求乘积p能用32位二进制数表示,且不会发生溢出。 图3-4 32 32乘法器结构框图 用32 4乘法器Mul32 4作为基本部件,实现32 32乘法器Mul32 32。 设被乘数为b(31:0)=(b31b30b29b28···b15b14b13b12···b4b3b2b1b0)2 乘数为a(31:0)=(a31a30a29a28···a15a14a13a12···a3a2a1a0)2 =(a31a30a29a28)2 228+···+ ( a15a14a13a12)2 212+···+ (a3a2a1a0)2 20

数字逻辑实验实验报告 脚分配、1)分析输入、输出,列出方程。根据方程和IP 核库判断需要使用的门电路以及个数。 2)创建新的工程,加载需要使用的IP 核。 3)创建BD 设计文件,添加你所需要的IP 核,进行端口设置和连线操作。 4)完成原理图设计后,生成顶层文件(Generate Output Products)和HDL 代码文件(Create HDL Wrapper)。 5)配置管脚约束(I/O PLANNING),为输入指定相应的拨码开关,为输出指定相应的led 灯显示。

6)综合、实现、生成bitstream。 7)仿真验证,依据真值表,在实验板验证试验结果。

实验报告说明 数字逻辑课程组 实验名称列入实验指导书相应的实验题目。 实验目的目的要明确,要抓住重点,可以从理论和实践两个方面考虑。可参考实验指导书的内容。在理论上,验证所学章节相关的真值表、逻辑表达式或逻辑图的实际应用,以使实验者获得深刻和系统的理解,在实践上,掌握使用软件平台及设计的技能技巧。一般需说明是验证型实验还是设计型实验,是创新型实验还是综合型实验。 实验环境实验用的软硬件环境(配置)。 实验内容(含电路原理图/Verilog程序、管脚分配、仿真结果等;扩展内容也列入本栏)这是实验报告极其重要的内容。这部分要写明经过哪几个步骤。可画出流程图,再配以相应的文字说明,这样既可以节省许多文字说明,又能使实验报告简明扼要,清楚明白。 实验结果分析数字逻辑的设计与实验结果的显示是否吻合,如出现异常,如何修正并得到正确的结果。 实验方案的缺陷及改进意见在实验过程中发现的问题,个人对问题的改进意见。 心得体会、问题讨论对本次实验的体会、思考和建议。

. 武汉理工大学

2017 年月日 实验一:一位全加器 实验目的: 1. 掌握组合逻辑电路的设计方法; 2. 熟悉Vivado2014 集成开发环境和Verilog 编程语言; 3. 掌握1 位全加器电路的设计与实现。 试验工具: 1.Basys3 FPGA 开发板 2.Vivado2014 集成开发环境和Verilog 编程语言。 实验原理: Ci+A+B={Co,S} 全加器真表

全加器逻辑表达式 S=A○+B○+Ci Co=A.B+ (A○+B).Ci 全加器电路图 实验步骤: (一)新建工程: 1、打开 Vivado 2014.2 开发工具,可通过桌面快捷方式或开始菜单中 Xilinx Design Tools->Vivado 2014.2 下的 Vivado 2014.2 打开软件; 2、单击上述界面中 Create New Project 图标,弹出新建工程向导。 3、输入工程名称、选择工程存储路径,并勾选Create project subdirectory选项,为工程在指 定存储路径下建立独立的文件夹。设置完成后,点击Next。注意:工程名称和存储路径中不能出现中文和空格,建议工程名称以字母、数字、下划线来组成 4、选择RTL Project一项,并勾选Do not specify sources at this time,为了跳过在新建工 程的过程中添加设计源文件。 5、根据使用的FPGA开发平台,选择对应的FPGA目标器件。(在本手册中,以Xilinx大学计 划开发板Digilent Basys3 为例,FPGA 采用Artix-7 XC7A35T-1CPG236-C 的器件,即Family 和Subfamily 均为Artix-7,封装形式(Package)为CPG236,速度等级(Speed grade)为-1,温度等级(Temp Grade)为C)。点击Next。 6、确认相关信息与设计所用的的FPGA 器件信息是否一致,一致请点击Finish,不一致,请返 回上一步修改。 7、得到如下的空白Vivado 工程界面,完成空白工程新建。

华中科技大学数字逻辑实验报告 姓名: 专业班级: 学号: 指导老师: 完成时间:

实验一:组合逻辑电路的设计 一、实验目的: 1.掌握组合逻辑电路的功能测试。 2.验证半加器和全加器的逻辑功能 3.学会二进制的运算规律。 二、实验所用组件: 二输入四与门74LS08,二输入四与非门74LS00,二输入四异或门74LS86,六门反向器74LS04芯片,三输入三与非门74L10,电线若干。 三、实验内容: 内容A:全加全减器。 实验要求: 一位全加/全减法器,如图所示: 电路做加法还是做减法运算是由M决定的,当M=0做加法,M=1做减法。当作为全加法起时输入A.B和Cin分别为加数,被加数和低位来的进位,S和数,Co位向上位的进位。当作为全减法器时输入信号A,B和Cin分别为被减数,减数和低位来的借位,S为差,Co为向上的借位。 实验步骤: 1.根据功能写出输入/输出观察表:

2. 3.做出卡诺图,确定输出和激励的函数表达式:

4.根据逻辑表达式作出电路的平面图: 5.检查导线以及芯片是否完好无损坏,根据平面图和逻辑表达式连接电路。 实验结果: 电路连接好后,经检测成功实现了一位全加/全减法器的功能。 内容B:舍入与检测电路的设计: 试验要求: 用所给定的集合电路组件设计一个多输出逻辑电路,该电路的输入为8421码,F1为“四

舍五入”输出信号,F2为奇偶检测输出信号。当电路检测到输入的代码大宇或等于(5)10时,电路的输出F1=1;其他情况F1=0。当输入代码中含1的个数为奇数时,电路的输出F2=1,其他情况F2=0。该电路的框图如下所示: (1)按照所设计的电路图接线,注意将电路的输入端接试验台的开关,通过拨动开关输入8421代码,电路输入按至试验台显示灯。 (2)每输入一个代码后观察显示灯,并将结果记录在输入/输出观察表中。 实验步骤 1.按照所给定的实验要求填写出F1,F2理论上的真值表。 2.根据真值表给出F1和F2的卡诺图。

数字逻辑实验报告

实验三、综合实验电路 一、实验目的: 通过一个综合性实验项目的设计与实现,进一步加深理论教学与实验软硬件平台的实践训练,为设计性实验做好充分准备。 二、实验原理: 根据要求的简单设计性的电路设计实验,应用基本器件与MSI按照电路设计步骤搭建出初级电路;设计型、综合型的较复杂实验电路 三、实验设备与器件: 主机与实验箱 四、实验内容: (1)实验任务:根据所学习的器件,按照电路开发步骤搭建一个时钟, 要求实现的基本功能有计时功能、校对时间功能、整点报时、秒表等功能。 (2)实验任务分析:完成该数字时钟,采用同步时序电路,对于计时 的的功能,由于时间的秒分时的进位分别是60、60、24,所以可以应用74LS163计数器分别设计2个模60计数器以及一个模24计数器,那么需要有7个秒输出,7个分输出,6个小时的输出;对于校对时间的功能,由74LS163的特性可知,当该器件处于工作状态时,每来一个CLK脉冲,计数值加1,所以可以手动控制给CLK脉冲,来进行时间的校对;对于整点报时功能,可以采用一个比较电路,当时间的分秒数值全部为零时,那么此时可以接通报时装置,可以在电路中设置报时的的时间;对于秒表功能,有两种方案,可以单独重新设计一个秒表装置,采用模100计数器以及两个模60计数器,可以进行优化,使用原先的两个模60计数器,这样可以简化电路,是电路简洁。 (3)实验设计流程:

(4)输入输出表: (5)各个功能模块的实现: A、计时功能模块的实现(电路图及说明)秒表部分及说明

说明:该部分是实现功能正常计时中的秒部分的计时工作。如图所示,图中采用两个74LS163来做一个模60计时器,计数的起止范围是0~59,(第一个74LS163采用模10计数,起止为0~9,第二个74LS163的计数起止范围是0~5),两个器件采用级联方式,用预置位方法实现跳转;该部分有7个秒输出,接到BCD译码显示器。 注解:第一个163器件: LDN端统一接到清零端ABCD端接地 ENP端接到VCC高电平ENT接高电平VCC 第二个163器件: LDN端统一接到清零端ABCD端接地 ENP端接到VCC高电平ENT接高电平第一个163的预置位段 分钟部分以及说明:

实验三译码器和编码器 一实验目的 1.掌握译码器、编码器的工作原理和特点。 2.熟悉常用译码器、编码器的逻辑功能和它们的典型应用。 二、实验原理和电路 按照逻辑功能的不同特点,常把数字电路分两大类:一类叫做组合逻辑电路,另一类称为时序逻辑电路。组合逻辑电路在任何时刻其输出的稳态值,仅决定于该时刻各个输入信号取值组合的电路。在这种电路中,输入信号作用以前电路所处的状态对输出信号无影响。通常,组合逻辑电路由门电路组成。 组合逻辑电路的分析方法:根据逻辑图进行二步工作: a.根据逻辑图,逐级写出函数表达式。 b.进行化简:用公式法、图形法或真值表进行化简、归纳。 组合逻辑电路的设计方法:就是从给定逻辑要求出发,求出逻辑图。一般分四步进行。 a.分析要求;将问题分析清楚,理清哪些是输入变量,哪些是输出函数。 b.列真值表。 c.进行化简:变量比较少时,用图形法。变量多时,可用公式化简。 d.画逻辑图:按函数要求画逻辑图。 进行前四步工作,设计已基本完成,但还需选择元件——集成电路,进行实验论证。 值得注意的是,这些步骤并不是固定不变的程序,实际设计时,应根据具体情况和问题难易程度进行取舍。 1.译码器 译码器是组合电路的一部分,所谓译码,就是把代码的特定含义“翻译”出来的过程,而实现译码操作的电路称为译码器。译码器分成三类: a.二进制译码器:如中规模2—4线译码器74LS139。,3—8线译码器74LS138等。 b.二—十进制译码器:实现各种代码之间的转换,如BCD码—十进制译码器74LS145等。 c.显示译码器:用来驱动各种数字显示器,如共阴数码管译码驱动74LS48,(74LS248),共阳数码管译码驱动74LS47(74LS247)等。 2.编码器 编码器也是组合电路的一部分。编码器就是实现编码操作的电路,编码实际上是译码相反的过程。按照被编码信号的不同特点和要求,编码器也分成三类: a.二进制编码器:如用门电路构成的4—2线,8—3线编码器等。 b.二—十进制编码器:将十进制的0~9编成BCD码,如:10线十进制—4线BCD码编码器74LS147等。 c.优先编码器:如8—3线优先编码器74LS148等。 三、实验内容及步骤 1.译码器实验 (1)将二进制2-4线译码器74LS139,及二进制3-8译码器74LS138分别插入实验系统IC 空插座中。 按图1.3.1接线,输入G、A、B信号(开关开为“1”、关为“0”),观察LED输出Yo、Y1、Y2、Y3的状态(亮为“1”,灭为“0”),并将结果填入表1.3.1中。

实验一 实验箱及小规模集成电路的使用 一 实验目的 1 掌握实验箱的功能及使用方法 2 学会测试芯片的逻辑功能 二 实验仪器及芯片 1 实验箱 2 芯片:74LS00 二输入端四与非门 1片 74LS86 二输入端四异或门 1片 74LS04 六非门 1片 三 实验内容 1 测试芯片74LS00和74LS86的逻辑功能并完成下列表格。 (1) 74LS00的14脚接+5V 电源,7脚接地;1、2、4、5、9、10、12、13脚接逻辑开关,3、6、8、11接发光二极管。(可以将1、4、9、12接到一个逻辑开关上,2、5、10、13接到一个逻辑开关上。)改变输入的状态,观察发光二极管。74LS86的接法74LS00基本一样。 表 74LS00的功能测试 表 74LS86的功能测试 (2)分析74LS00和74LS86的四个门是否都是完好的。 2 用74LS00和74LS04组成异或门,要求画出逻辑图,列出异或关系的真值表。 (3)利用74LS00和74LS04设计一个异或门。画出设计电路图。

实验二译码器和数据选择器 一实验目的 1继续熟悉实验箱的功能及使用方法 2掌握译码器和数据选择器的逻辑功能 二实验仪器及芯片 1 实验箱 2 芯片:74LS138 3线-8线译码器 1片 74LS151 八选一数据选择器 1片 74LS20 四输入与非门 1片 三实验内容 1 译码器功能测试(74LS138) 芯片管脚图如图所示,按照表连接电路,并完成表格。其中16脚接+5V,8脚接地,1~6脚都接逻辑开关,7、9、10、11、12、13、14、15接发光二极管。 表 2 数据选择器的测试(74LS151) 按照表连接电路,并完成表格。其中16脚接+5V,8脚接地;9、10、11,为地址输入端,接逻辑开关;4、3、2、1、12、13、14、15为8个数据输入端,接逻辑开关;G为选通输入端,Y为输出端,接发光二极管。

浙江大学城市学院实验报告 课程名称 数字逻辑设计实验 实验项目名称 实验十二 数据选择器应用 学生姓名 专业班级 学号 实验成绩 指导老师(签名 ) 日期 注意: ● 务请保存好各自的源代码,已备后用。 ● 完成本实验后,将实验项目文件和实验报告,压缩为rar 文件,上传ftp 。如没有个人 文件夹,请按学号_姓名格式建立。 ftp://wujzupload:123456@10.66.28.222:2007/upload ● 文件名为:学号_日期_实验XX ,如30801001_20100305_实验0 1 一. 实验目的和要求 1. 掌握数据选择器的逻辑功能和使用方法。 2. 学习用数据选择器构成组合逻辑电路的方法。 二. 实验内容、原理及实验结果与分析 1、用74LS151实现逻辑函数 要求实现BC A AC C B A Y ++=,自己写出设计过程,画出接线图,并验证其逻辑功能。 计算得到m0=m7=0,m2=m4=m5=m6=1,m1=m3=D (1) 设计原理图 (2) 仿真,模拟验证,若组合成总线显示时,需要注意高低位

(3)组合输出信号 (4)配置管脚 (5)下载到FPGA

(6) 74LS151的输入端接逻辑电平输出(拨位开关),输出端Z 接逻辑电 平显示(发光二极管)。逐项测试电路的逻辑功能,记录测试结果。 2、用74LS151实现逻辑函数 要求实现逻辑函数C B CD A B A F ++=,自己写出设计过程,画出接线图,并验证其逻辑功能。芯片插法,电源、地线接法与实验内容1相同,这里只需要自己实现逻辑函数,然后连线实现其功能。 (1) 设计原理图 (2) 仿真,模拟验证,若组合成总线显示时,需要注意高低位

《数字逻辑实验指导书》 实验一组合逻辑电路分析与设计 一、实验目的: 1、掌握PLD实验箱的结构和使用; 2、学习QuartusⅡ软件的基本操作; 3、掌握数字电路逻辑功能测试方法; 4、掌握实验的基本过程和实验报告的编写。 二、原理说明: 组合电路的特点是任何时刻的输出信号仅取决于该时刻的输入信号,而与信号作用前电路的状态无关。 (一)组合电路的分析步骤: (二)组合逻辑电路的设计步骤 首先根据给定的实际问题进行逻辑抽象,确定输入、输出变量,并进行状态赋值,再根据给定的因果关系,列出逻辑真值表。然后用公式法或卡诺图法化简逻辑函数式,以得到最简表达式。最后根据给定的器件画出逻辑图。 三、实验内容 (一)组合逻辑电路分析: 1.写出函数式,画出真值表; 2.在QuartusⅡ环境下用原理图输入方式画出原理图,并完成波形仿真; 3.将电路设计下载到实验箱并进行功能验证,说明其逻辑功能。(必做)

(二)组合逻辑电路设计 1.设计一个路灯的控制电路,要求在四个不同的路口都能独立地控制路灯的亮灭。(用异或门实现) 画出真值表,写出函数式,画出实验逻辑电路图。在QuartusⅡ环境下实现设计,完成对波形的仿真,并将设计下载到实验箱并进行功能验证。(必做) 要求:用四个按键开关作为四个输入变量;用一个LED彩灯(发光二极管)来显示输出的状态,“灯亮”表示输出为“高电平”,“灯灭”表示输出为“低电平”。 2.设计一个保密锁电路,保密锁上有三个键钮A、B、C。要求当三个键钮同时按下时,或A、B两 个同时按下时,或按下A、B中的任一键钮时,锁就能被打开;而当不符合上列组合状态时,将使电铃发出报警响声。试设计此电路,列出真值表,写出函数式,画出最简的实验电路。(用最少的与非门实现)。在QuartusⅡ环境下实现设计,完成对波形的仿真,并将设计下载到实验箱并进行功能验证。(选做) (注:取A、B、C三个键钮状态为输入变量,开锁信号和报警信号为输出变量,分别用F1用F2表示。设键钮按下时为“1”,不按时为“0”;报警时为“1”,不报警时为“0”,A、B、C都不按时,应不开锁也不报警。) 三、予习要求: 1.复习组合电路的分析方法和设计方法。 2.预习利用QuartusⅡ和可编程器件(PLD)进行数字电路设计的基本设计方法。 3.画出实验用电路图和记录表格,填好理论值,注明管脚号码。 四、报告要求: 1.实验目的和要求 2.实验主要仪器和设备 3.实验原理 4.实验方案设计、实验方法 5.实验步骤

数字逻辑实验报告:加法器

安徽师范大学 学院实验报告 专业名称软件工程 实验室 实验课程数字逻辑 实验名称加法器实验姓名 学号 同组人员 实验日期 2013.3.26

注:实验报告应包含(实验目的,实验原理,主要仪器设备和材料,实验过程 和步骤,实验原始数据记录和处理,实验结果和分析,成绩评定)等七项内容。具体内容可根据专业特点和实验性质略作调整,页面不够可附页。 实验目的:学会使用实验箱搭建基本组合逻辑电路。 实验原理:全加器是中规模组合逻辑器件,它实现二进制数码的加法运算,是计算机中最基本的运算单元电路。一位加法器有三个输入端Ai 、B i 、C i -1,即被加数,有两个输出端S i 和B i 即相加及向高一位的进位输出。 (全加真值表) Si=A i B i C i -1+A i B i C i -1+A i B i C i -1+A i B i C i -1 C i =A i B i +A i C i -1+B i C i -1 全加器主要用于数值运算;另外,全加器还可以实现组合逻辑函数。 主要仪器设备和材料:数字逻辑电路实验装置、芯片 74LS32、芯片 74LS08、 芯片74LS86,导线 实验过程和步骤: ①关闭实验箱的电源开关,将三个芯片正确地安装在实验箱装置上; ②分别用三根导线将三个芯片的第14号引脚与实验箱左下角的+5V 连接起来,,再分别用三根导线将三个芯片的第7号引脚与实验箱左下角的GND 连接 Ai B i C i -1 S i B i 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1

实验报告 课程名称_数字逻辑及系统设计实验学生学院____计算机____________ 专业班级软件2012(2)班 _ 学号 3112006177 学生姓名陈海兵 指导教师_____林小平 _________ 2013年 12 月24 日

一、 实验目的 1. 熟练掌握基本门电路的主要用途以及验证它们的逻辑功能。 2. 熟练掌握常用组合逻辑电路的基本原理及其逻辑电路功能。 3. 熟练掌握常用时序逻辑电路的基本原理及其逻辑电路功能。 4. 掌握Libero IDE 基于FPGA 的设计流程。 5. 熟悉FPGA 的设计与开发流程。熟悉芯片烧录的流程及步骤。 二、 实验要求 1. 要求每人能独立完成实验。严禁抄袭。 2. 能独立搭建Libero IDE 软件基础环境,掌握FPGA 的开发流程。 3. 按照实验指导书中P56-69的实验步骤进行设计,每一步骤均需要截图显示。 4. 完成3次仿真(综合前,综合后,布局布线后),并将仿真波形截图显示。 5. 将程序烧录到Actel Proasic3 A3P030 FPGA 核心板,在数字逻辑及系统实验箱上完成连 线,验证代码的正确性。 6. 纸制版的封面单面打印,其他页面必须双面打印。全班刻一张光盘。 三、 实验内容 1. 设计题目:用3-8译码器74HC138实现举重比赛的裁判表决电路的组合逻辑函数 ,写出模块代码和测试平台代码。 2. 74HC138功能表参照教材中P53表2-9,引脚图参照实验指导书中P30图2-16。 3. 把每一个步骤的实验结果截图,按实验指导书中P6图1-7中所列FPGA 引脚,手工分 配引脚,最后通过烧录器烧录至FPGA 核心板上。 4. 按分配的引脚连线,实测相应功能并记录结果。 四、 实验结果与截图 1. 模块及测试平台代码清单。 模块代码 // 74HC138.v module decoder3_8_1(DataIn,Enable1,Enable2,Enable3,Eq,y); input [2:0]DataIn; input Enable1,Enable2,Enable3; output [7:0]Eq; reg [7:0]Eq; output y; reg y; integer I; always @(DataIn or Enable1 or Enable2 or Enable3) begin if(Enable1||Enable2||!Enable3) Eq=0; AC BC AB Y ++=

《数字逻辑》实验指导 福建工程学院

电子技术实验室实验守则 一、实验课前:每个学生必须认真预习实验指导书和与本实验有关的教材内容,写出实验预习报告。明确实验目的和实验原理,了解实验内容与步骤,掌握仪器、仪表的使用方法,作好实验准备工作。 二、上实验课:学生必须认真听讲,接好线路后,需经指导教师复查批准,才准接通电源。 三、实验时,每个学生都应严肃认真,勤于动手、独立思考、细心操作,注意观察、如实作好记录。教师根据每个学生的实验技能,动手能力评定平时成绩。 四、实验过程中,如发现仪器设备有冒烟、焦味、异响、漏电等异常现象,应立即切断电源,保持现场,请指导教师检查处理。 五、实验完成后,需请指导教师检查预习报告和实验数据以及所使用的仪器设备,经教师检查签字后方可离开实验室。 六、学生因请假而需要补做实验者,应本人申请,经指导教师同意,并安排好时间补做。 七、每个学生必须爱护实验室的仪器设备,使用前,若发现故障及时请指导教师检查。与本实验无关的仪器设备不准动用,凡不听教师讲解,进行错误操作以致损坏设备者,按赔偿条例酌情处理。 八、实验室是教学场所,应保持整洁,安静,不得喧哗打闹,不准吸烟,不准随地吐痰,不准乱抛纸屑,不准在实验室内吃东西,不准在仪器设备上或桌面上涂写,穿拖鞋者一律不准进入实验室。 九、对违反上述规则又不听劝阻者,教师有权令其退出实验室

实验一门电路参数测试 一、实验目的 1. 了解 TTL 与非门电路的主要参数。 2. 掌握 TTL 与非门电路的主要参数和传输特性的测试方。 3. 熟悉 TTL 门电路的逻辑功能的测试方法。 二、实验器材 1、数字逻辑实验箱 2、万用表 3、74LS00芯片 三、实验原理 本实验采用四二输入“与 非门”74LS00,其引脚排列如 右图所示,它共有四组独立的 “与非”门,每组有两个输入 端,一个输出端。四与非门 74LS00 的主要参数有: 1.扇出系数NO:电路正常工作时能带动的同类门的数目称为扇出系数NO 。 2.输出高电平VOH:一般VOH≥2.4V. 3.输出低电平VOL:一般VOL≤0.4V. 4.高电平输入电流IIH:指当一个输入端接高电平,而其它输入端接地时从电源流过高电平输入端的电流。 5.低电平输入电流IIL(或输入短路电流IRD):指当一个输入端接地,而其它输入端悬空时低电平输入端流向地的电流。 6.电压传输特性曲线和关门电平VOFF: 下图所表示的V ~VO关系 曲线称为电压传输特性曲线。使 输出电压刚刚达到低电平时的最 低输入电压称为开门电平VON 。 使输出电压刚刚达到规定高电平 时的最高输入电压称为关门电平 VOFF。 7.噪声容限:电路能够保持 正确的逻辑关系所允许的最大抗 干扰电压值,称为噪声电压容限。 输入低电平时的噪声容限为VOFF- VIL ,输入高电平时的噪声容