接口与通讯技术复习

- 格式:doc

- 大小:459.50 KB

- 文档页数:13

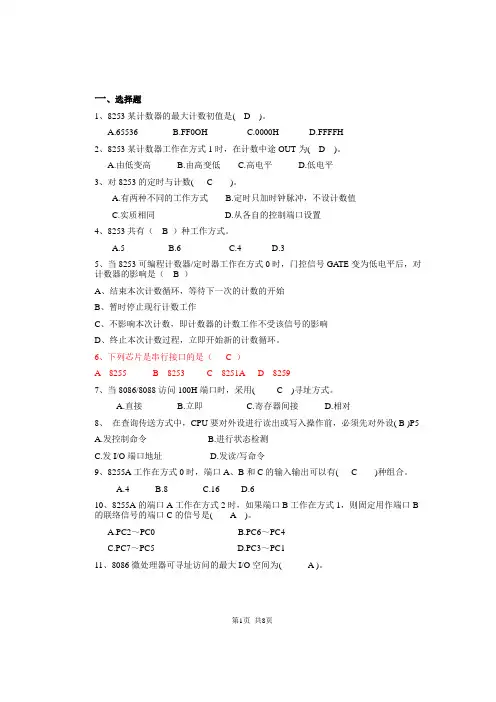

一、选择题1、8253某计数器的最大计数初值是( D )。

A.65536B.FF0OHC.0000HD.FFFFH2、8253某计数器工作在方式1时,在计数中途OUT为( D )。

A.由低变高B.由高变低C.高电平D.低电平3、对8253的定时与计数( C )。

A.有两种不同的工作方式B.定时只加时钟脉冲,不设计数值C.实质相同D.从各自的控制端口设置4、8253共有( B )种工作方式。

A.5B.6C.4D.35、当8253可编程计数器/定时器工作在方式0时,门控信号GA TE变为低电平后,对计数器的影响是( B )A、结束本次计数循环,等待下一次的计数的开始B、暂时停止现行计数工作C、不影响本次计数,即计数器的计数工作不受该信号的影响D、终止本次计数过程,立即开始新的计数循环。

6、下列芯片是串行接口的是( C )A 8255B 8253C 8251AD 82597、当8086/8088访问100H端口时,采用( C )寻址方式。

A.直接B.立即C.寄存器间接D.相对8、在查询传送方式中,CPU要对外设进行读出或写入操作前,必须先对外设( B )P5A.发控制命令B.进行状态检测C.发I/O端口地址D.发读/写命令9、8255A工作在方式0时,端口A、B和C的输入输出可以有( C )种组合。

A.4B.8C.16D.610、8255A的端口A工作在方式2时,如果端口B工作在方式1,则固定用作端口B 的联络信号的端口C的信号是( A )。

A.PC2~PC0B.PC6~PC4C.PC7~PC5D.PC3~PC111、8086微处理器可寻址访问的最大I/O空间为( A )。

第1页共8页A. 1KBB.64KBC.640KBD.1MB12、8086中断的类型码是( D )。

A.中断服务子程序的入口地址B.中断向量表的地址指针C.中断向量表的内容D.以上三项都不是13、2个8259可提供( C )个中断类型号。

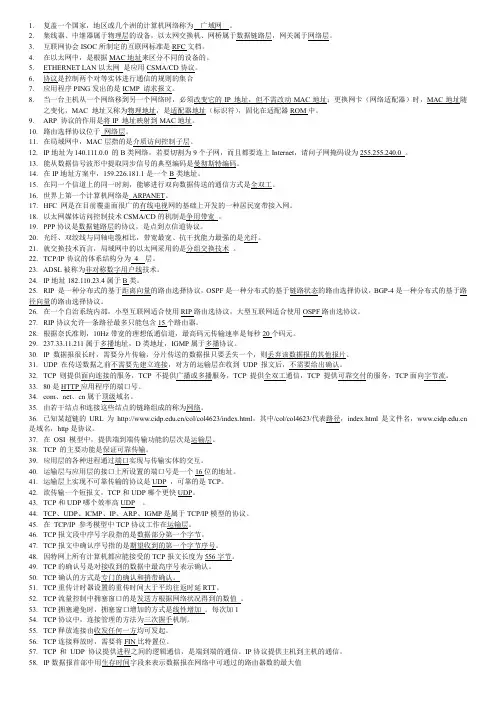

1.复盖一个国家,地区或几个洲的计算机网络称为广域网。

2.集线器、中继器属于物理层的设备,以太网交换机、网桥属于数据链路层,网关属于网络层。

3.互联网协会ISOC所制定的互联网标准是RFC文档。

4.在以太网中,是根据MAC地址来区分不同的设备的。

5.ETHERNET LAN以太网是应用CSMA/CD协议。

6.协议是控制两个对等实体进行通信的规则的集合7.应用程序PING发出的是ICMP 请求报文。

8.当一台主机从一个网络移到另一个网络时,必须改变它的IP 地址,但不需改动MAC地址;更换网卡(网络适配器)时,MAC地址随之变化,MAC 地址又称为物理地址,是适配器地址(标识符),固化在适配器ROM中。

9.ARP 协议的作用是将IP 地址映射到MAC地址。

10.路由选择协议位于网络层。

11.在局域网中,MAC层指的是介质访问控制子层。

12.IP地址为140.111.0.0 的B类网络,若要切割为9个子网,而且都要连上Internet,请问子网掩码设为255.255.240.0 。

13.能从数据信号波形中提取同步信号的典型编码是曼彻斯特编码。

14.在IP地址方案中,159.226.181.1是一个B类地址。

15.在同一个信道上的同一时刻,能够进行双向数据传送的通信方式是全双工。

16.世界上第一个计算机网络是ARPANET。

17.HFC 网是在目前覆盖面很广的有线电视网的基础上开发的一种居民宽带接入网。

18.以太网媒体访问控制技术CSMA/CD的机制是争用带宽。

19.PPP协议是数据链路层的协议,是点到点信道协议。

20.光纤、双绞线与同轴电缆相比,带宽最宽、抗干扰能力最强的是光纤。

21.就交换技术而言,局域网中的以太网采用的是分组交换技术。

22.TCP/IP协议的体系结构分为4 层。

23.ADSL被称为非对称数字用户线技术。

24.IP地址182.110.23.4属于B类。

25.RIP 是一种分布式的基于距离向量的路由选择协议,OSPF是一种分布式的基于链路状态的路由选择协议,BGP-4是一种分布式的基于路径向量的路由选择协议。

一、填空题1.一个频带限制在f m H Z以下的连续信号m(t),可以惟一地用时间每隔T__≤________秒的抽样值序列来确定。

2.PCM系统信道部分包括传输线路及_再生中继器___。

3.非均匀量化的宗旨是:在不增大量化级数N的前提下,利用降低大信号的信噪比来提高_小信号的量化信噪比。

4.ADPCM的主要特点是用自适应量化取代__固定量化。

5.为了提高通信信道的利用率,使信号沿同一信道传输而不互相干扰,称为__多路复用_。

6.为了保证在接收端能正确地接收或者能正确的区分每一路话音信号,时分多路复用系统中的收、发两端要做到同步。

7.所谓时钟同步是使收端的时钟频率与发端的时钟频率__相同_。

8.数字复接的同步指的是被复接的几个低次群信号的数码率____相同_。

9.数字分接器的功能是把高次群分解成原来的__低次群_。

10.PCM信号脉冲经过信道传输,各中继站和终端站接收的脉冲信号在时间上不再是等间隔的,而是随时间变动的,这种现象称为_相位抖动_。

11.SDH帧结构中安排有两大类开销:通道开销和___段开销__。

12.按字复接是每次复接各低次群的一个码字形成__高次群________。

13.SDH网同步通常采用__主从同步________方式。

14. PCM30/32系统中前方保护的前提状态是___同步状态____。

15.SDH网的基本网络单元有终端复用器、再生中继器、数字交叉连接设备和_分插复用器_。

16.抽样是将模拟信号在时间域上__离散化____的过程。

17.量化是将模拟信号在幅度上__离散化____的过程。

18.异步复接二次群1帧中信息码至少为__820____bit。

19.所谓PCM复用就是直接将多路信号__编码复用____。

20.SDH帧结构中包括段开销、信息净负荷和_管理单元指针_____三个区域。

21.SDH网的基本网络单元有再生中继器、分插复用器、数字交叉连接设备和_终端复用器(TM)_____。

资料范本本资料为word版本,可以直接编辑和打印,感谢您的下载通信系统复习题地点:__________________时间:__________________说明:本资料适用于约定双方经过谈判,协商而共同承认,共同遵守的责任与义务,仅供参考,文档可直接下载或修改,不需要的部分可直接删除,使用时请详细阅读内容填空1、相移QPSK调制属于(线性)调制。

2、GMSK调制属于(恒定包络)调制,它最主要的特点是已调信号具有(包络幅度)不变的特性。

3、在移动通信中,改进接收信号质量的三种常用技术为(分集)(均衡)(信道编码)4、常用的几种分集技术为(空间)分集,(极化)分集,角度分集,频率分集,时间分集。

5、常见的分集信号合并技术可分为(选择式合并)(最大化合并)(等增益合并)(开关式合并)6、电波在自由空间的传播衰耗与哪两个因素有关?(F)(d)7、描述信道衰落特性的特征量,通常有(衰落中值)(衰落率)(电平交叉率)(衰落深度)(衰落持续时间)8、呼损率即系统服务等级,写出呼损率定义的三种方式:(按时间计算)(按呼叫计算)(按负载计算)。

9、交织技术可以用来抗(突发)性误码,信道编码技术可以用来抗(随机)性误码10、语音的主观评定可分为(5)级,当收听的注意力为“中等程度的注意力” 时,可评定为(3)级。

11、m序列在一个周期为“1”码和“0”码元的的个数(大致相等),这个特性保证了在扩频时有较高的(载频)抑制度。

12、m序列和其移位后的序列逐位模二和运算,所得的序列是(m)序列。

13、沃尔什码就其正交性而言为(正交)码,其相关性为(良好的自相关性)和(处处为零的互相关性)。

14、直接序列扩频系统,不但具有一定的隐蔽性,还有很强的抗(白噪声)、(单频)及(窄带、宽带)的能力。

15、跳频有慢跳频和快跳频两种,GSM系统采用的是(慢)跳频,其速率大致为(217跳/s)。

16、语音编码通常有(波形编码)、(参量编码)和(混合编码)三类,数字蜂窝系统通常采用(混合)编码方式。

1.网络的定义计算机网络是把处在不同地理位置的独立计算机,用通信介质和网络设备进行互连,辅以网络软件进行控制,达到资源共享、协同操作的目的。

简单的说:一组互连的计算机和其他设备构成一个网络。

2.网络的分类局域网(LAN):其地域范围一般只有几公里。

城域网(MAN):其地域范围从几公里到几百公里,对于城域网最好的传输介质就是光纤。

广域网(WAN):其覆盖范围从几百公里到几千公里,是由终端设备、节点交换设备,和传送设备组成的。

3.网络拓扑结构星型网:每一终端均通过单一的传输链路与中心交换节点相连,具有结构简单建网容易,且易于管理的特点,缺点是中心设备负载过重,当其发生故障,每一节点均有专线与中心节点相连,使得线路利用率不高,信道容量浪费过大。

树型网:是一种分成网络适用于分级控制系统,树行网的同一线路可以连接多个终端,与星型相比具有节省线路,成本较低,和利于拓展的特点,缺点是对高点的节点和链路的要求过高。

4.OSI参考模型:应用层:为特定类型的网络应用提供了访问OSI环境的手段。

应用层确定进程之间通信的性质,以满足用户的需要;表示层:主要用于处理两个通信系统中交换信息的表示方式。

为上层用户解决用户信息的语法问题;会话层:在两个节点之间建立端连接。

为端系统的应用程序之间提供了对话控制机制;传输层:常规数据递送——面向连接或无连接。

为会话层用户提供一个端到端的可靠、透明和优化的数据传输服务机制;网络层:本层通过寻址来建立两个节点之间的连接,为源端的运输层送来的分组,选择合适的路由和交换节点,正确无误地按照地址传送给目的端的运输层;数据链路层:在此层将数据分帧,并处理流控制。

屏蔽物理层,为网络层提供一个数据链路的连接,在一条有可能出差错的物理连接上,进行几乎无差错的数据传输(差错控制);物理层:主要功能是利用物理传输介质为数据链路层提供物理连接,以便透明的传送比特流。

5.数据封装和解封装的过程P11封装:OSI参考模型中每个层次接收到上层传递多来的数据后都要将本层次的数据信息加入数据单元的头部,一些层次还要讲校验和等信息附加但数据单元的尾部。

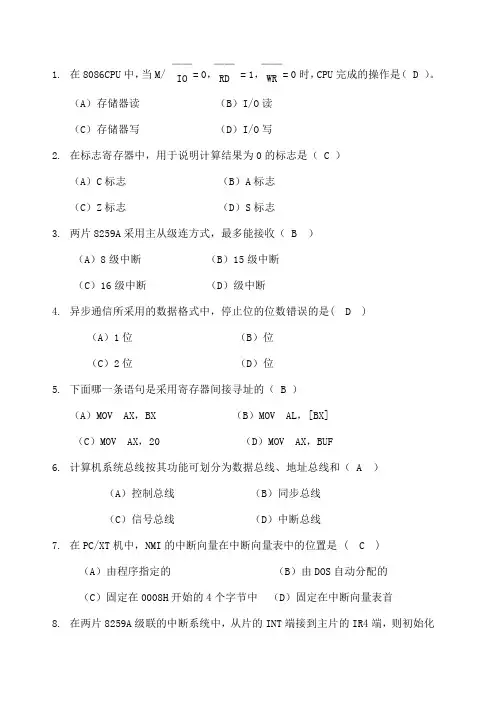

1.在8086CPU中,当M/ ——IO= 0,——RD = 1,——WR= 0时,CPU完成的操作是( D )。

(A)存储器读(B)I/O读(C)存储器写(D)I/O写2.在标志寄存器中,用于说明计算结果为0的标志是( C )(A)C标志(B)A标志(C)Z标志(D)S标志3.两片8259A采用主从级连方式,最多能接收( B )(A)8级中断(B)15级中断(C)16级中断(D)级中断4.异步通信所采用的数据格式中,停止位的位数错误的是( D )(A)1位(B)位(C)2位(D)位5.下面哪一条语句是采用寄存器间接寻址的( B )(A)MOV AX,BX (B)MOV AL,[BX](C)MOV AX,20 (D)MOV AX,BUF6.计算机系统总线按其功能可划分为数据总线、地址总线和( A )(A)控制总线(B)同步总线(C)信号总线(D)中断总线7.在PC/XT机中,NMI的中断向量在中断向量表中的位置是 ( C )(A)由程序指定的(B)由DOS自动分配的(C)固定在0008H开始的4个字节中(D)固定在中断向量表首8.在两片8259A级联的中断系统中,从片的INT端接到主片的IR4端,则初始化主、从片ICW3的数据格式分别是( B )(A)01H和40H (B)10H和04H(C)10H和40H (D)01H和04H9.CPU与输入/输出端口是通过哪些指令来完成信息交换( C )(A)MOV (B)MOVSB(C)IN或OUT (D)STOSB10.在标志寄存器中,符号标志是( S )(A)C标志(B)A标志(C)Z标志(D)S标志11.CPU与输入/输出接口电路是通过端口寄存器进行信息交换,这些端口寄存器包括了状态端口、控制端口和( B )(A)信息端口(B)数据端口(C)存储器端口(D)命令端口12.8088微处理器可寻址访问的最大I/O空间为( B )(A) 1KB (B) 64KB(C) 640KB (D) 1MB13.CPU与输入/输出端口是通过哪些指令来完成信息交换( C )(A)MOV (B)MOVSB(C)IN或OUT (D)STOSB14.在标志寄存器中,用于说明计算结果为0的标志是( C )(A)C标志(B)A标志(C)Z标志(D)S标志15.下面哪一个命题是正确的( C )(A)负数的反码与其真值数相同(B)负数的补码与其真值数相同(C)正数的原码、反码、补码与其真值数相同(D)[+0]反码16.在实模式下进行编写汇编程序,每一个逻辑段的大小不能超过( B )(A)32KB (B)64KB(C)128KB (D)256KB17.在BUF DB ,,5,9这条语句中,代表的含义是( A )(A)随机数(字节型)(B)字符的ASCII(C)随机数(字型)(D)随机数(双字型)18.CPU中程序计数器(PC)中存放的是( )(A)指令(B)指令地址(C)操作数(D)操作数地址19.8086CPU往8255端口B送数据时,则8255A芯片引脚A1AO为( B )(A)A1A0=00 (B)A1A0=01(C)A1A0=10 (D)A1A0=1120.CPU响应中断请求和响应DMA请求的本质区别是 ( C )程序控制需要CPU干预响应中断时CPU仍控制总线而响应DMA时,让出总线速度快21.堆栈的工作方式是 ( D )(A)先进先出(B)随机读写(C)只能读出不能写入(D)后进先出22.外设的中断类型码必须通过16位数据总线的 ( B ) 传送给8086。

通信技术基础知识.txt通信技术基础知识电信网(telecommunication network)是构成多个用户相互通信的多个电信系统互连的通信体系,是人类实现远距离通信的重要基础设施,利用电缆、无线、光纤或者其它电磁系统,传送、发射和接收标识、文字、图像、声音或其它信号。

电信网由终端设备、传输链路和交换设备三要素构成,运行时还应辅之以信令系统、通信协议以及相应的运行支撑系统。

现在世界各国的通信体系正向数字化的电信网发展,将逐渐代替模拟通信的传输和交换,并且向智能化、综合化的方向发展,但是由于电信网具有全程全网互通的性质,已有的电信网不能同时更新,因此,电信网的发展是一个逐步的过程。

电信网按不同的分类体系可以划分如下:按电信业务的种类分为:电话网、电报网、用户电报网、数据通信网,传真通信网、图像通信网、有线电视网等。

按服务区域范围分为:本地电信网、农村电信网、长途电信网、移动通信网、国际电信网等。

按传输媒介种类分为:架空明线网、电缆通信网、光缆通信网、卫星通信网、用户光纤网、低轨道卫星移动通信网等。

按交换方式分为:电路交换网、报文交换网、分组交换网、宽带交换网等。

按结构形式分为:网状网、星形网、环形网、栅格网、总线网等。

按信息信号形式分为:模拟通信网、数字通信网、数字模拟混合网等。

按信息传递方式分为:同步转移模式(STM)的综合业务数字网(ISDN)和异地转移模式(ATM)的宽带综合业务数字网(B-ISDN)等。

什么是智能网?智能网(Intelligentized Network)的思想起源于美国。

20世纪80年代初,AT&T公司就采用集中数据库方式提供800号(被叫付费)业务和电话记帐卡业务,这是智能网的雏形。

后来国际电联ITU-T (International Telecommunications Union)在1992年正式命名了智能网一词。

智能网是在现有交换与传输的基础网络结构上,为快速、方便、经济地提供电信新业务(或称增值业务)而设置的一种附加网络结构。

通信考试题目在当今信息社会中,通信技术的重要性不言而喻。

通信考试涵盖了各个领域的知识和技能,要求考生具备扎实的理论基础和实际操作经验。

本篇文章将介绍通信考试的一些常见题目和解答方法,帮助考生更好地应对考试挑战。

一、通信原理与技术通信原理与技术是通信考试的核心内容之一。

以下是几个常见的通信原理题目及其解答方法:1. 请简述传输介质对通信质量的影响。

传输介质是信息传递的媒介,会对通信质量产生影响。

不同的传输介质具有不同的传输速度、传输距离和信号衰减特性。

例如,光纤传输具有高速率、长距离传输和低衰减等优势,可用于长距离通信;而双绞线传输速率较低,适用于短距离通信。

因此,选择适合的传输介质对保证通信质量至关重要。

2. 请解释通信系统中的调制和解调过程。

调制是将要传输的信号转换成适合传输介质的形式,解调则是将接收到的信号恢复成原始信号。

调制过程包括三个基本步骤:信号源、调制器和载波。

信号源是要传输的原始信号,调制器将原始信号转换成与载波相结合的调制信号,这个过程称为调制。

接收端通过解调器对接收到的信号进行解调,即将调制信号还原为原始信号。

调制和解调过程的关键在于保证信号的传输质量和完整性。

二、无线通信技术随着移动通信技术的飞速发展,无线通信技术成为通信考试中的重要内容。

以下是几个常见的无线通信技术题目及其解答方法:1. 请简述蜂窝网络的工作原理。

蜂窝网络是一种将通信区域划分为许多小区域的通信网络。

它的工作原理是将整个通信区域划分为许多小颗粒状的“蜂窝”,每个蜂窝都有自己的基站,覆盖一定范围内的用户。

当用户移动到不同的蜂窝中时,手机会自动切换到相应的基站进行通信。

蜂窝网络有效提高了通信的容量和覆盖范围,增强了通信信号的稳定性,使用户能够在不同的区域内进行无缝通信。

2. 请解释CDMA技术的原理。

CDMA技术(Code Division Multiple Access)是一种利用码分多址技术进行通信的无线通信技术。

通信技术高考知识点通信技术是信息科学与技术中的重要分支,涉及到信息传输、信号处理和网络通信等领域。

在高考中,通信技术也是一个重要的考点。

本文将介绍通信技术高考知识点,包括通信网络基础、数字通信原理、模拟通信原理以及通信设备等内容。

一、通信网络基础通信网络基础是通信技术的基础知识,主要包括计算机网络、协议和接口以及网络安全等内容。

1. 计算机网络计算机网络是现代通信技术的基础,包括局域网、广域网以及互联网等。

在高考中,可以了解计算机网络的基本概念、网络拓扑结构、网络协议以及网络传输介质等内容。

2. 协议和接口协议和接口是通信技术中的重要概念,用于规定数据在通信中的传输格式和交互规则。

在高考中,需要了解常见的网络协议如TCP/IP协议、HTTP协议以及数据链路层的常见接口等知识。

3. 网络安全网络安全是保障通信数据的安全传输和存储的重要环节。

在高考中,可以了解网络攻击与防御、加密算法、防火墙以及虚拟私有网络(VPN)等网络安全相关知识。

二、数字通信原理数字通信原理是通信技术的核心内容,主要包括数字信号传输、调制解调技术以及误码控制等。

1. 数字信号传输数字信号传输是将模拟信号转换为数字信号,并通过信道传输的过程。

在高考中,可以了解数字信号的采样定理、量化处理、编码技术以及信道编码等相关知识。

2. 调制解调技术调制解调技术是将数字信号转换为模拟信号并传输,以及将模拟信号解析为数字信号的技术。

在高考中,可以了解常见的调制技术如调幅、调频以及调相等,并了解调制解调器的工作原理和应用场景。

3. 误码控制误码控制是指在信息传输过程中,通过编码和解码技术来降低传输过程中的误码率,提高通信质量。

在高考中,可以了解常见的误码控制技术如前向纠错编码(如海明码)、自动重传请求(ARQ)以及差错检测等相关知识。

三、模拟通信原理模拟通信原理是通信技术的传统领域,主要包括模拟调制技术、模拟信号传输以及模拟信号处理等内容。

1. 模拟调制技术模拟调制技术是将模拟信号调制为适合传输的信号并传输的技术。

兰大18秋《接口与通讯技术课程作业_B(满分)单选题当向8259A写入的操作命令字OCW2为01100100时,将结束( )的中断服务。

A: IRQ0B: IRQ1C: IRQ4D: IRQ6单选题当有6路模拟电压共用一个A/D转换器时,需在A/D转换器的输入端加一个( )模拟开关。

A: 6选1B: 8选1C: 1选6D: 1选8单选题8086中断系统中优先级最低的的是()。

A: 可屏蔽中断B: 不可屏蔽中断C: 单步中断D: 除法出错单选题关于8253,下列说法不正确的是( )。

A: 8253内部三个结构相同的计数器B: 8253内部有一个8位的计算器C: 8253内部计数器均可工作在计数模式下D: 8253工作方式3可以产生连续的方波单选题中断类型码为11H的中断所对应的中断矢量存放在0段以0044H开始的四个存储单元,0044H到0047H四个单元存放的数据分别为78、06H、45、68H,那么该系统中的10H中断所对应的中断矢量为___。

A: 0678H,6845HB: 7806H,4568HC: 4578H,6806HD: 7806H、6845H单选题设某微机系统要管理64 级中断,问组成该中断机构时需( )片8259。

A: 8 片B: 10 片C: 9 片D: 64 片单选题PCI的含义是( )。

A: 局部总线B: 系统总线C: 外围元件互连D: 图形加速器单选题内存地址与I/O端口统一编制存在的不利影响是()。

A: 地址容易重叠B: 减少了内存的可用范围C: 操作I/O端口的指令功能弱D: 减少了I/O端口地址的可用范围单选题8253工作在哪几种方式时,可输出1个时钟周期宽度(1 CLK)的负脉冲( ) 。

A: 方式0,4,5B: 方式2,4,5C: 方式1,2,4D: 方式0,2,4单选题下列哪一项不属于接口的功能()。

A: 总线仲裁B: 信息格式的转换C: 信息类型和电平的转换D: 缓冲输入/输出数据单选题3片8259A级联起来,可管理( )级中断。

现代通信技术复习题1.通信网的网络拓扑结构有哪些?网状型、星型、复合型、总线型、环型、树型2.通信网的传输媒质有哪些?信号复用方式有哪几种?有线传输媒介:电缆、光纤(1310nm、1550nm),无线传输媒介:自由空间(移动通信、微波通信300MHZ-1000GHZ、卫星通信)复用方式:频分复用、时分复用、码分复用3.为什么在通信网中引入交换?在通信网中引入交换设备的意义就就是在降低成本的前提下,保证网络的高可靠性、高性能、易维护、易扩展,最终达到网络的智能化管理。

(解决N²的问题)4.PCM30/32帧结构就是如何安排的?5.交换技术有哪些种类?窄带交换技术<2Mbit/s:电路交换、分组交换,宽带交换技术:快速电路交换、快速分组交换、异步转移模式、光交换6.OSI参考模型有哪七层?物理层、数据链路层、网络层、传输层、会话层、表示层、应用层7.信令有哪些类型?随路信令与共路信令的区别?NO、7信令属于哪一种?随路信令、共路信令(No、7信令)、线路信令、路由信令、管理信令区别:随路信令中信令通过话路来传送,信令信道与用户信息通道合在一起成一一对应关系,不构成与话路相对独立的信令网络。

共路信令中信令设备直连通道,信令传送与话路分开、无关的,将若干条话路的信令集中起来,在一条公共的高速数据链路上传送,从而实现了局间信令传送形式的高度统一8.本地电话网的汇接方式有哪几种?用户电话号码有几部分?去话汇接、来话汇接、来去话汇接; 本地:局号(4PQRS)与用户号(4),最长为8位,长途:国内长途字冠+长途区号+本地号码,国际长途字冠+国家号码+长途区号+本地号码,国际长途字冠00,国家号码1-3位9.交换机的软件有哪几部分?一次呼叫分为几个处理阶段?运行软件(操作系统、呼叫处理、维护管理)与支援软件输入处理、内部处理、输出处理10.信令网有几部分组成?如何提高信令网的可靠性?信令点SP、信令转接点STP、信令链路组成;优化拓扑结构、加强信令网的阻塞控制、故障防卫、使用差错控制技术、提高节点/设备的可靠性、使用网络保护与恢复技术11.交换机的硬件有哪几部分?模拟用户话路接口电路的功能有哪些?话路子系统(交换网络、信令设备、接口电路)控制子系统传输信号,放大信号,选频信号B(馈电)O(过压保护)R(振铃)S(监视)C(编译码)H(混合电路)T(测试)12.T接线器与S接线器的工作原理?T:时间接线器用来完成在一条复用线上时隙交换的基本功能,简称T接线器S:空间接线器用来完成对传送同步时分复用信号的不同复用线之间的交换功能,而不改变其时隙位置,可简称为S接线器13.ISDN的含义?基本接口速率就是多少?通道类型有哪些?以电话IDN为基础发展而演变成的通信网叫综合业务数字网2B+D:64kbit/s×2+16kbit/s=192kbit/s B通道、D通道、H通道14.SDH的优点有哪些?新型的复用映射方式、兼容性好、接口标准统一、网络管理能力强、先进的指针调整技术、独立的虚容器设计、组网与自愈能力强、系列标准规范15.SDH的帧结构就是如何安排的?各部分的内容就是什么?采用块状帧结构,并以字节为基础,它由纵向9行与横向270xN列字节组成,传输时由左及右,由上而下顺序排成串行码流依次传输。

北京化工大学2011——2012学年第一学期《移动通信》期末考试试卷标准答案课程代码 E E E 4 2 3 0 3 T班级:姓名:学号:分数:题号一二三四总分得分一、判断题(本题请在第4页的方框内作答)1、数字移动通信系统要求调制技术使已调信号的频谱越宽越好,以便更好地抗衰落×2、π/4-DQPSK是恒包络的调制技术,其优点是可采用成本低廉的非线性功放×3、欧洲数字集群标准TETRA采用的调制技术是π/4-DQPSK √4、RAKE接收可以很好地克服移动通信中的多普勒频移×5、多波束天线的采用可以减少蜂窝网络中的共道干扰√6、GSM通信系统中,为减少邻道干扰而使用干扰抵消和多用户信号检测器技术×7、FSK的解调由于其恒包络的特点不能采用包络检波×8、MSK信号既可采用鉴频器解调,也可采用相干解调√9、MSK是相位连续且满足最小频差的调制指数为1的一种特殊形式的FSK ×10、QPSK解调只能采用相干解调,而π/4-DQPSK既可采用相干解调也可采用非相干解调√11、多载波系统由于一个深衰落可影响到多个子载波,其抗衰落能力逊于单载波系统×12、OFDM的系统带宽比一般的FDMA系统的带宽可以节省三分之一×13、采用非线性功放可以一定程度上解决OFDM系统PAR较大的问题×14、MS移动到同一MSC的不同LA中,不需要进行位置登记×15、CDMA系统中,只要邻站和本站处于同频工作状态,则此时均为软切换×16、对于多载波系统,载波频率的偏移会导致子信道相互间产生干扰√17、自适应均衡器通过动态调整特性参数跟踪信道的变化,补偿信道传输特性,从而使整个系统能满足无码间串扰的传输条件√18、TDMA系统中,为便于克服码间干扰,在时隙中要插入自适应均衡器所需的训练序列√19、GSM系统中,每一个用户在入网时分配公用的密钥Ki和唯一的IMSI ×20、在IS-95蜂窝移动通信系统中,前向是指手机发往基站的方向×21、CDMA系统的频率复用系数可以为1,而GSM系统的频率复用系数不可能为1 √22、EDGE采用8PSK调制技术,从而将传输速率提高为GMSK调制的3倍√23、GSM网络中,BCCH信道和CCCH信道是不参与跳频的信道√24、处于通话状态中的MS从同一MSC下的某一BSC范围移动到另一BSC范围时,系统不必参与切换过程×25、蜂窝移动通信系统的最小区群的N值越大,其频率利用率将随之提高×26、采用顶点激励方式的基站天线采用全向天线模式×27、MS发,BS收的传输链路称为下行链路×28、GSM900网络的双工间隔为50MHz ×29、GSM帧长为4.62ms,每帧8个时隙√30、移动通信网的信道一般分为控制信道和业务信道两大类√31、信号强度排列如下:直射波、反射波、绕射波、散射波√32、GSM中,BCCH既是上行信道,又是下行信道×33、GSM中,MS与BS之间被定义为A接口,MSC与MSC之间被定义为Um接口×34、WCDMA系统的空中接口带宽为5MHz,其码片速率为3.84Mc/s√35、DTX技术的采用可以使移动台具有更长的待机和通话时间√36、WCDMA系统是干扰受限系统√37、IMEI是用于国际唯一区分移动用户的号码×38、GSM中鉴权和加密是两个独立的处理过程,两者间没有任何的关联×39、GSM网采用主从同步方式,BSC的同步基准从MSC来的数据流中提取,也可单独设置同步链路×40、扩频系统提高了系统的保密性、提升了系统的信噪比√41、IS-95蜂窝移动通信系统每个信道1.2288MHz,含有64个码道√42、TCH复帧由26个TDMA帧构成,而用于映射BCH和CCCH的复帧有51 个TDMA 帧√43、TDD称为时分双工,收发信号在时间上分开互不干扰,广泛地用于IS-95系统×44、一个BSC可以连接到多个MSC上,一个MSC也可以连接到多个BSC ×45、多径效应造成的衰落会随移动台运动速度的加快而加快√46、CDMA为干扰受限系统,当系统中增加一个通话用户时,所有用户的信噪比会下降√47、GSM通信系统中,SCH(同步信道)的作用包括帧同步和时隙同步√48、PCH为寻呼信道,当移动台申请开始一次通话时,利用它向基站发送请求×49、主叫用户到本侧交换机的信令为用户线信令,被叫用户到对端交换机信令为局间信令×50、TD-SCDMA的载频宽度是1.6MHz,其码片速率为1.28Mc/s √二、单选题(本题请在第4页的方框内作答)1、美国的IEEE 802.11a/g和欧洲ETSI的HiperLAN/2中,均采用了(B)技术A.GMSK B.OFDM C.64QAM D.MIMO2、处于空闲模式下的手机所需的大量网络信息来自(B)信道2A.CBCH B.BCCH C.RACH D.SDCCH3、一个用户在忙时一小时内先后进行了1分钟和5分钟的通话,此用户产生的话务量是(C )A.33毫爱尔兰B.66毫爱尔兰C.100毫爱尔兰D.10毫爱尔兰4、模拟移动通信系统采用的多址方式是(A),GSM移动通信系统采用的多址方式为()A.FDMA TDMA B.CDMA FDMA C.TDMA CDMA D.TDMA FDMA 5、GSM网常采用的切换方式是(B )A.移动台控制B.移动台辅助的网络控制C.网络控制D.基站控制6、我国目前有三大运营商获得了3G牌照,其中,WCDMA是由(B )在运营A.中国移动B.中国联通C.中国电信D.中国铁通7、(C)的作用是存储用户密钥,保证系统能可靠识别用户的标志,并能对业务通道进行加密。

第一章1、三网是指哪三网?电信网络、有线电视网络和计算机网络。

2、计算机网络的定义和特点,组成部分?定义:把分布在不同地点且具有独立功能的多个计算机,通过通信设备和线路连接起来,在功能完善的网络软件运行环境下,以实现网络中资源共享为目标的系统。

网络的特点:信息通过网络以比特和字节流—电子信号的方式流动—无人能看得见以小的信息包传送速度快高度准确地传送到原定的目的地组成部分:计算机,联网硬件和软件3、因特网发展历程经历了那三个阶段?第一阶段是从单个网络 ARPANET 向互联网发展的过程。

第二阶段的特点是建成了三级结构的因特网。

第三阶段的特点是逐渐形成了多层次 ISP 结构的因特网。

4、因特网的接入级有哪些?大致上可将因特网分为以下五个接入级网络接入点 NAP国家主干网(主干 ISP)地区 ISP本地 ISP校园网、企业网或 PC 机上网用户5、万维网是什么?万维网:World Wide Web是因特网的一部分,是图形化的,用鼠标点击的,带超级链接的因特网界面是一个资料空间,通过超文本传输协议(http)传送给使用者,而后者通过点击链接来获得资源。

第二章1、计算机网络按照传输技术划分有那些,各自工作方式是什么?按传输技术进行分类:广播式网络:仅有一条通信信道,由网络的所有机器共享。

广播系统可将分组或包发送到所有目标、子集或某一个机器。

点到点网络:由一对对机器之间的多条连接构成,一般来讲,小的、地理上处于本地的网络采用广播方式,而大的网络则采用点到点方式。

2、计算机网路按照作用范围有那些分类?按照通信介质有那些分类?网络拓扑结构划分?网络交换功能划分?按网络的作用范围划分:LAN、MAN、WAN、AN按通信介质划分:有线网、无线网按网络拓扑结构划分:星形结构、层次结构或树形结构、总线形结构、环形结构按网络交换功能划分:电路交换、报文交换、分组交换、混合交换3、计算机网络的通信方式?中央网络互联网通信方式:客户/服务器方式,对等方式4、什么是通信子网?子网通常在谈到广域网时才有意义,它指由网络经营者拥有的路由器和通信线路的集合;子网和主机构成了网络。

计算机接口技术总复习题及答案精品计算机接口技术总复习题及答案1章练习题一·单项选择题1. 8086微处理器可寻址访问的最大I/O空间是(②)。

① 1KB ② 64KB ③ 640KB ④ 1MB2.CPU的控制总线提供(④)。

①数据信号流②所有存储器和I/O设备的时序信号及控制信号③来自I/O设备和存储器的响应信号④前面②和③两项3. CPU的数据总线提供(①)。

①数据信号流②所有存储器和I/O设备的时序信号及控制信号③来自I/O设备和存储器的响应信号④地址信号流4. CPU的地址总线提供(④)。

①数据信号流②所有存储器和I/O设备的时序信号及控制信号③来自I/O设备和存储器的响应信号④地址信号流5. CPU在执行OUT DX,AL指令时,CPU往控制总线上送出的有效信号是(①)。

①IOW②MEMW③IOR④MEMR6. CPU在执行OUT DX,AL指令时,CPU往地址总线上送出的有效信号是(①)。

①DX寄存器所存放的地址② AL寄存器所存放的数据③IOR IOW④MEMR MEMW7. CPU在执行OUT DX,AL指令时,CPU往数据总线上送出的有效信号是(②)。

①DX寄存器所存放的地址② AL寄存器所存放的数据③IOR IOW④MEMR MEMW8. 8086 CPU寄存器中,能在操作数内存寻址时用作地址寄存器的是(②)。

① AX ② BX ③ CX ④ DX9. 8086CPU在作外设输入时,控制信号M/IO,DT/R必须是(②)。

① 11 ② 00 ③ 01 ④ 1010. 8086CPU基本总线周期中,地址信号在(①)时间发生。

① T1 ② T3 ③ T2 ④ T411. 8086CPU在作总线操作时,遇到READY=L后可插入(②)。

① 1个等待周期②等待周期个数由具体情况所定③ 2个等待周期④ 3个等待周期12. 8086系统中,SP(②)。

①只能指向奇地址单元②只能指向偶地址单元③最好指向偶地址单元④最好指向奇地址单元13. 8086 系统配置在最大方式比最小方式增加的一片专用芯片是(③)。

单片机原理及接口技术复习要点一、单片机原理:1.单片机的定义:单片机是一种集成电路芯片,具有处理器核心、存储器、输入输出接口和时钟电路等功能。

2.单片机的特点:小巧、低成本、低功耗、易编程、易扩展。

3.单片机的组成:-中央处理器(CPU):负责执行指令和进行运算。

-存储器:包括程序存储器(ROM)和数据存储器(RAM)。

-输入输出(I/O)接口:用于和外部设备进行数据交互。

-时钟电路:提供计时和同步信号。

4.单片机的工作原理:根据存储在ROM中的程序指令进行运算和控制,通过输入输出接口与外部设备进行数据交互。

二、接口技术:1.串行通信接口:-串行通信定义:通过串行方式发送、接收数据的通信方式,包括同步串行通信和异步串行通信。

-USART(通用同步/异步串行接口):用于实现串行通信,主要包括波特率发生器和数据传输控制寄存器。

-SPI(串行外设接口):用于与外部设备进行串行通信,包括主从模式、全双工传输和多主机系统等特点。

-I2C(串行二进制接口):用于实现系统内部的各个模块之间的串行通信,主要包括总线数据线(SDA)和总线时钟线(SCL)。

2.并行通信接口:-并行通信定义:同时传输多个数据位的通信方式。

-并行输入输出口(PIO):用于与外部设备进行并行通信,主要包括输入寄存器和输出寄存器。

-扫描输入输出(SIPO):用于通过一条串行线同时将多个输入信号引入单片机。

3.模数转换接口:-模数转换器(ADC):将模拟信号转换为数字信号,常用于采集模拟量信号。

-数模转换器(DAC):将数字信号转换为模拟信号,常用于输出模拟量信号。

4.脉冲宽度调制(PWM):-脉冲宽度调制定义:通过调节脉冲的宽度来控制信号的幅值的技术。

-PWM的应用:常用于控制电机的转速、控制LED的亮度等。

5.中断技术:-中断定义:当特定事件发生时,暂时中断正常程序的执行,转而执行特定代码,处理事件。

-中断的优先级:可以设置多个中断的优先级,高优先级的中断可以打断低优先级的中断。

《微型计算机接口技术与汇编语言》第1-2章微型计算机系统概论1.现代微机接口在硬件上的层次结构——设备接口和总线接口微机系统硬件——微处理器、存储器、I/O设备与I/O接口、总线2.I/O设备接口与CPU交换数据的方式(P9)I/O设备接口与CPU之间的数据交换,一般有查询、中断和DMA三种方式。

3.各主要寄存器的位数(P25)(1)数据寄存器:包括4个16位通用寄存器AX、BX、CX、DX;(2)段寄存器:一个段的描述包括段的长度、起始位置和段内偏移量,段长度可长可短,最多可达64KB。

段在存储器中的起始地址称为段地址,存放在段寄存器中,如CS(Code Segment)、DS(Data Segment)、ES(Extra Data Segment)、SS(Stack Segment)。

(3)指针寄存器和变址寄存器:包括4个16位的寄存器SP、BP、SI、DI;(4)指令指针寄存器:IP;(5)标志寄存器:Flag(16位)4.存储器物理地址的形成方法、物理地址的计算(P21)物理地址的形成算法是:段寄存器的值左移4位,再与偏移量相加,并且由微处理器内部的地址加法器完成,无需用户干预。

Append: 2.2.5 编程模型AX (16位) = AH (高8位)+AL(低8位)5.跨段前缀的作用(P35,P89)微处理器使用跨段前缀可以改变上述寄存器和表示偏移地址寄存器的默认组合(CS:IP,SS:SP的组合不能改变),但必须显式地说明寻址所使用的段寄存器名。

6.堆栈指针寄存器SP和指令指针寄存器IP的作用(P25)SP和BP都是用来存放堆栈变量在堆栈段中的偏移量,与SS寄存器联用来确定堆栈段中某一存储单元的地址,但有所分工。

IP用来存放代码段中的地址,它与CS寄存器联用确定下一条指令的首地址。

7.堆栈操作的原则——后入先出8.字存储单元的内容确定第3章汇编语言寻址方式和指令集1.TEST指令和AND指令的区别如TEST AL,37H和AND AL,37H都是与操作,但TEST不改变值2.XOR指令的作用(清零、某些位取反)3.指令LEA和MOV OFFSET mem、MOV mem指令的含义条件:(DS)=2000H,(SI)=4000H,(24000H)=12H,(24001H)=34H,(24002H)=56H;MOV AX, SI; (AX)=4000H;MOV AX, [SI]; (AX)=3412H;LEA AX, [SI]; (AX)=4000H;MOV AX, OFFSET [SI]; (AX)=4000H;LEA和MOV OFFSET等价。

4.寄存器间接寻址时,各间址寄存器隐含使用的段寄存器以及存储单元物理地址的计算(P56)操作数在存储器中的段地址,在默认的情况下,是这样指定的:如果使用BP作为间接寻址,则默认的段是堆栈段SS ,此时,操作数的地址为SS:BP ;如果使用BX 、SI 、DI 寄存器作为间接寻址,则默认段是数据段DS ,此时,操作数的地址为DS:BX ,或为DS:SI 、DS:DI 。

Append :直接端口寻址 :直接端口寻址是在指令中直接给出要访问的端口地址,一般采用2位十六进制数表示,也可以是符号,访问的端口范围0~255.间接端口寻址: 若访问的端口地址大于255时,就要用间接寻址方式。

可以访问的端口范围0~65535.字单元内容计算: 字节单元 地址啊第4章 伪指令与语句格式1.按要求写出完整的数据段定义(伪指令DB 、DW 、DD 、DQ 以及EQU 的使用;n DUP(?)的使用)(P81-P83)AA DW 10h, -30H ;为变量AA 定义2个字型存储单元 BB DB ?, ?, ? ;为变量BB 保留3个字节型存储单元DB 500 DUP(0) ;为堆栈申请500个字节存储单元,并赋值0 T EQU 6 ;为常量6定义一个符号名TF EQU T*3+8 ;为表达式定义一个符号名F ,计算后得F=26DATA_D DD 3*20,0FFFDH ;定义了DATA_D 为首址的两个双字地址,依次存放双字型数据0000003CH,0000FFFDH2.属性定义算符PTR的作用——BYTE PTR和WORD PTRPTR主要用于使语句中类型不明确的操作数地址变得明确。

MOVE BYTE PTR[BX], 50 ;把立即数50送入BX所指的字节单元MOVE WORD PTR[BX], 50 ;把立即数50送入BX所指的字单元3.假定伪指令ASSUME的作用和用法(P83)假定伪指令ASSUME的功能是用来设定段与段寄存器的对应关系,告诉汇编程序,哪些段是处理器当前可访问的段。

ASSUME CS:CODE, DS:DATA, SS:STACK ;段假定伪指令第5章汇编语言程序设计1.条件转移指令的格式、使用方法、编程——JZ/JNZ等(P105)比如:若PC6!=0,则转L1,否则转L2。

MOV DX, PC6;IN AL, DX;AND AL, 01000000B;JZ L1;/ JNZ L2;2.循环指令LOOP隐含使用的寄存器——CX(P108-P111)3.编程序段实现对指定外设的操作(包括状态查询及输入/输出)第6章 I/O端口地址译码技术1.I/O端口的编址方式——独立编址、统一编址(P132)2.独立编址方式下I/O端口的访问——IN、OUT指令的使用、编程;直接/间接寻址方式中I/O端口地址的范围;间接寻址方式中的间址寄存器(P133)3.在I/O端口地址译码电路中AEN的使用(设置AEN=0)(P136)AEN信号表示是否采用DMA方式传输,AEN=1为DMA方式,系统总线由DMA控制器占用;AEN=0,为非DMA方式,系统总线由CPU占用。

因此,当采用查询和中断方式时,就要使AEN信号为逻辑0,并参加译码,作为译码有效选中I/O端口的必要条件。

4.I/O端口地址译码电路的分析和设计——采用译码器74138(P137-P143)第7章定时/计数技术1.微机系统中的定时的种类——内部定时、外部定时(P146)2.82C54A的主要特性——3个16位计数通道,每个通道最多计65536个脉冲,6种工作方式(P147)3.82C54A的6种工作方式中方式2、3的特殊性——自动重新装载计数初值,输出重复波形,分频器(P153)4.82C54A计数初值的计算,采用BCD码计数时的计数初值确定(P155)(1)要求产生定时时间间隔的定时常数Tc=要求定时的时间/时钟周期脉冲=τ×CLK。

例如,已知CLK=1.19318MHZ,τ=5ms,求Tc,则Tc=5×10^-3s×1193180/s=5965。

(2)要求产生频率为f的信号波形的定时常数Tc=时钟脉冲的频率/要求的波形频率=CLK/f。

例如,已知CLK=1.19318MHZ,f=800HZ,求Tc,则Tc=1.19318×10^6HZ/800HZ=1491。

5.计数值超出一个通道计数能力时的处理方式(P156)采用两个或多个计数器串联起来计数或定时,例如,把0号计数器与1号、2号计数器串联使用。

第8章中断技术1.中断的分类——外部(硬)中断、内部(软)中断(P172)2.硬中断的分类——可屏蔽INTR(中断响应周期)、非屏蔽NMI(P172);中断允许标志IF 的作用——可屏蔽:IF=1,开放;IF=0,屏蔽3.8086中断系统中,中断号的取值范围(P174)系统对外部中断和内部中断、硬中断和软中断一律统一编号,共256个号,其中有一部分中断号已经分配给了中断源,尚有一部分中断号还空着,待分配,用户可以使用。

4.82C59A的主要特性——每片管理8级中断,固定优先级方式IR0优先级最高;两级级联最多可管理64级中断5.82C59A所管理中断源的中断类型号的确定——高5位、低3位6.82C59A写入ICW3的条件——级联系统写入(P184)8位,ICW3命令只有系统存在2片以上82C59A时才启用,否则不用ICW3命令。

7.中断向量的修改(提供相关的DOS系统功能调用,要求写出修改中断向量的程序段)(P191)第9章 DMA技术1.DMA传输的特点——快速性的原因采用DMA传输方式时让存储器与I/O设备(磁盘),或I/O设备与I/O设备之间直接交换数据,不需要经过累加器,从而减少了中间环节,并且内存地址的修改、传输完毕的结束报告都由硬件完成,因此大大提高了传输速度。

2.DMA读和DMA写的含义——针对M而言3.DMA的3种操作方式(单字节、请求、连续)之间的区别(1)单字节方式:操作一个字节就释放总线。

(2)连续(块字节)方式:操作结束(数据块操作结束,检索时找到关键字节或关键位)才释放(3)总线;在操作过程中,DREQ无效则等待其有效。

请求(询问)方式:操作结束或DREQ无效即释放总线。

4.对82C37A初始化时,向字节计数器中写入的内容——N-1(P208)基字节计数寄存器和当前字节计数寄存器:16位;初始化时装入数据块大小(N-1);二者同时写入(先低字节后高字节)。

5.DMA有效操作周期内的主控器——DMAC6.82C37A的时序中,过渡周期的含义——HRQ及HLDA(P213)过渡状态S0:DMAC发出HRQ之后,收到HLDA之前。

7.82C37A的时序中,状态周期S1出现的条件(P213)更新高8位地址;AEN、ADSTB有效,DMAC将M的A8~15放到DB0~7上;只有当 A8~15有变化时才出现S1。

8.83C37A在有效操作周期内,分别如何选中M和I/O两个介质(P213)选中两个介质;输出16位地址选中M:低8位由A0~7直接输出;高8位由DB0~7经外部锁存器(由ADSTB下降沿锁存)输出;发有效的DACK选中I/O。

9.什么叫软命令?82C37A有哪几条软命令(212)软命令:只要对特定地址进行一次写操作(即CS、内部端口地址和IOW同时有效),命令就生效,而与写入的具体数据无关。

(1)清先/后触发器软命令:将先/后触发器清0。

(2)总清除软命令:作用同RESET;清除命令、状态和请求寄存器以及暂存器、先/后触发器。

(3)清屏蔽寄存器软命令:4个通道屏蔽寄存器清0。

例如:OUT 0CH,AL ;清先/后触发器软命令OUT 0DH,AL ;总清除软命令OUT 0EH,AL ;清屏蔽寄存器软命令第10章并行接口1.并行接口的特点、并行接口中“并行”的含义(P219)所谓并行接口,就是接口电路与I/O设备之间采用多根数据线并行传输数据。

“并行”的含义——接口电路与I/O设备间的数据线。