西北工业大学_数字电子技术基础_实验报告_实验3

- 格式:doc

- 大小:2.16 MB

- 文档页数:11

数字电子技术基础第三次实验报告

一、描述QuartusII软件基本使用步骤

①编写Verilog代码,用文本编辑器正确编写源文件,并经modelsim仿真确认该电路

设计正确。

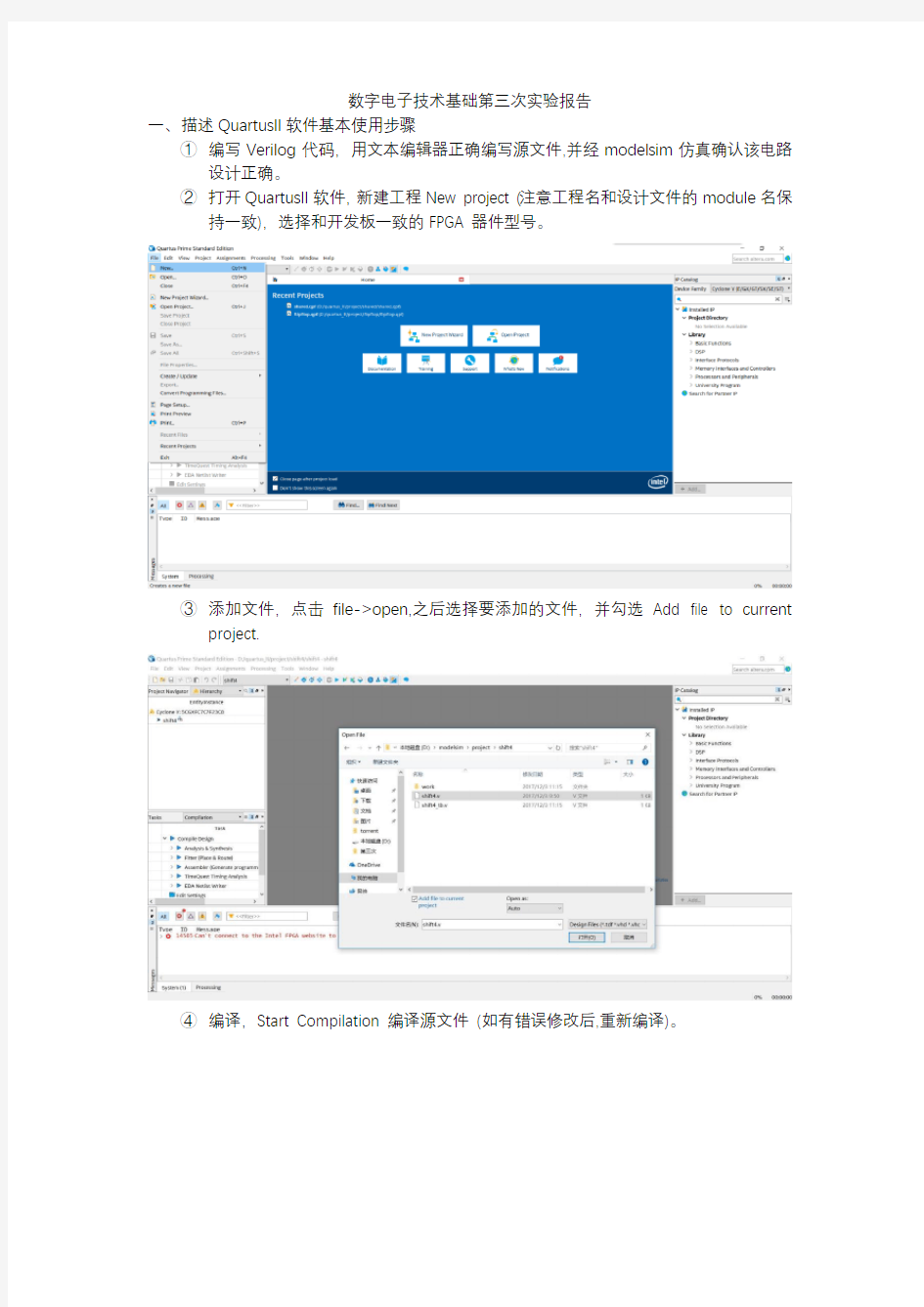

②打开QuartusII软件,新建工程New project (注意工程名和设计文件的module名保

持一致),选择和开发板一致的FPGA器件型号。

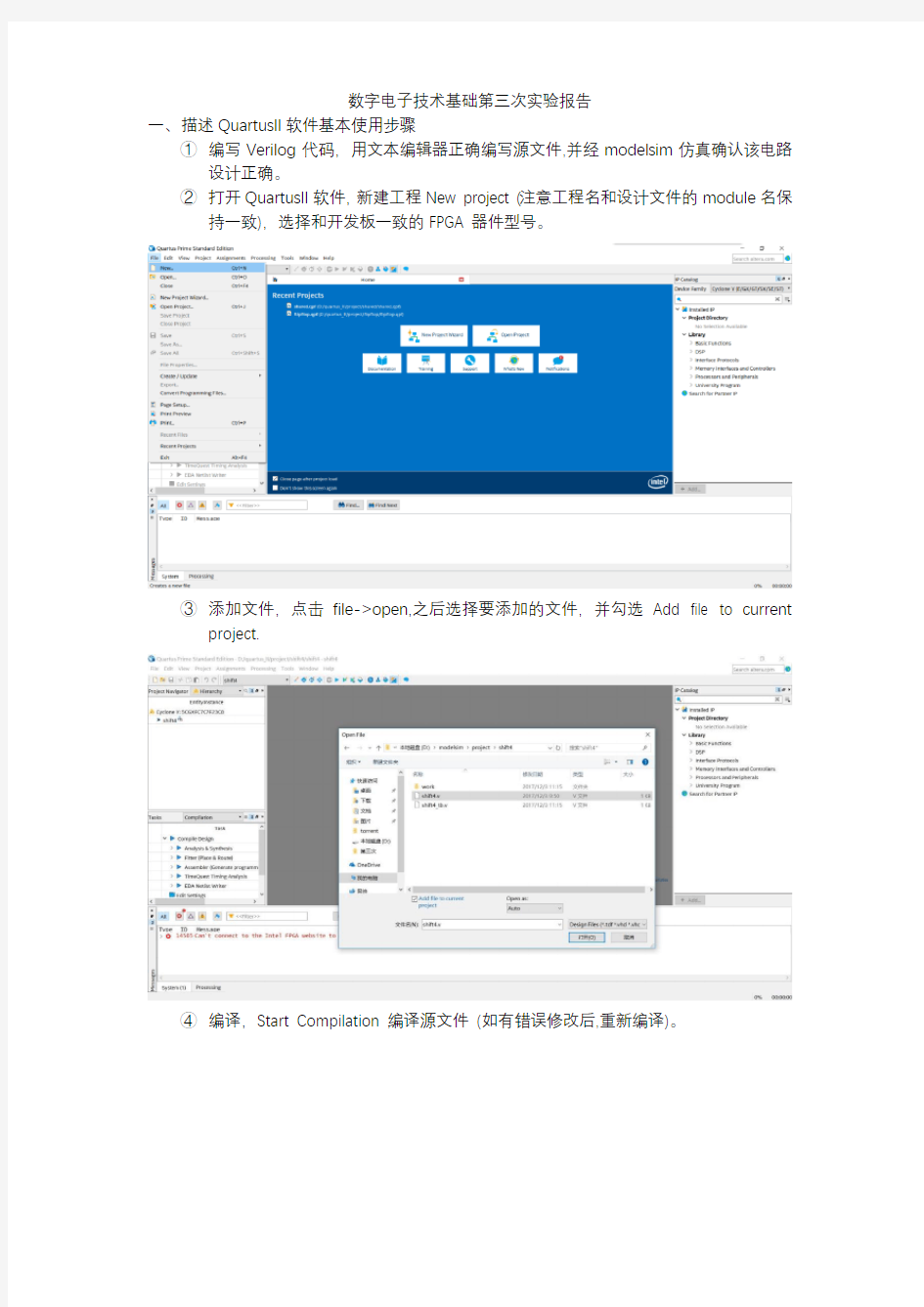

③添加文件,点击file->open,之后选择要添加的文件,并勾选Add file to current

project.

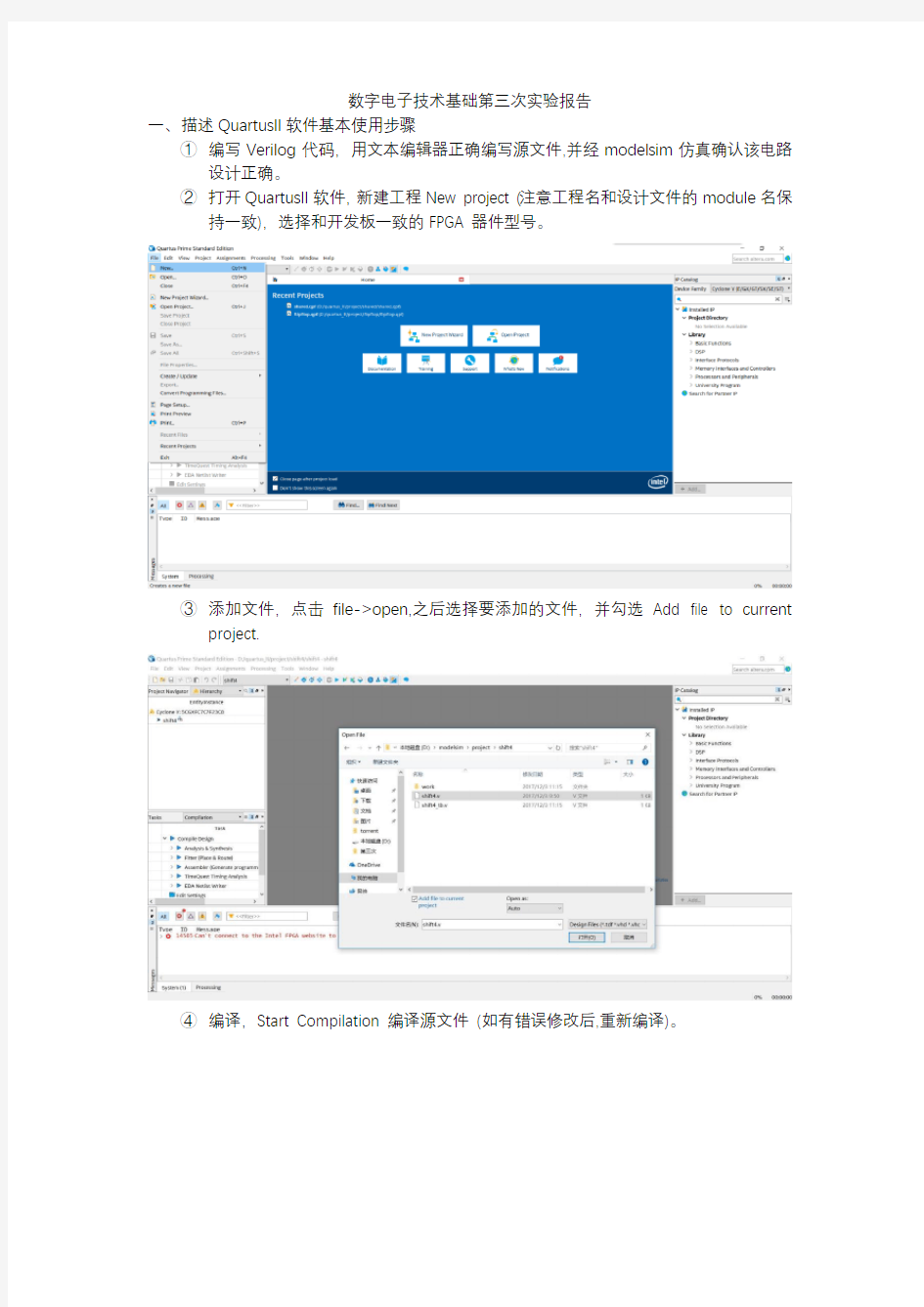

④编译,Start Compilation ,编译源文件(如有错误修改后,重新编译)。

⑤查看电路结构,使用Tool->RTL viewer工具查看电路图结构,是否和预期设计一致。

二、题目代码以及波形分析

1.设计一款时钟上升沿触发的D寄存器

a)编写模块源码

module flipflop(D,Clock,Q);

input D,Clock;

output reg Q;

always@(posedge Clock)

Q=D;

endmodule

b)测试模块

`timescale 1ns/1ps

module tb_flipflop;

reg Clock_test;

reg D_test;

wire Q_test;

initial

Clock_test=0;

always #20 Clock_test=~Clock_test;

initial

D_test=0;

always #77 D_test=~D_test;

flipflop UUT_flipflop(.Clock(Clock_test),.D(D_test),.Q(Q_test));

endmodule

c)仿真后的波形截图

每当时钟上升沿到来时,触发器把D的信号传给Q

d)综合后的RTL图形

2.设计一款4bBit具有并行加载功能的移位寄存器编写模块源码

a)编写模块源码

module muxdff(D0,D1,Sel,Clock,Q);

input D0,D1,Sel,Clock;

output reg Q;

wire D;

assign D=Sel?D1:D0;

always@(posedge Clock)

Q<=D;

endmodule

module shift4(R,L,w,Clock,Q);

input [3:0]R;

input L,w,Clock;

output wire [3:0]Q;

muxdff Stage3(w,R[3],L,Clock,Q[3]);

muxdff Stage2(Q[3],R[2],L,Clock,Q[2]);

muxdff Stage1(Q[2],R[1],L,Clock,Q[1]);

muxdff Stage0(Q[1],R[0],L,Clock,Q[0]); endmodule

b)测试模块

`timescale 1ns/1ps

module tb_shift4;

reg Clock_test;

reg L_test;

reg w_test;

reg [3:0]R_test;

wire [3:0]Q_test;

initial

Clock_test=0;

always #10 Clock_test=~Clock_test;

initial

begin

L_test=1;

#14

L_test=0;

//always #14 L_test=~L_test;

end

initial

w_test=0;

always #13 w_test=~w_test;

initial

R_test=4'b1010;

shift4 UUT_shift4(.Clock(Clock_test),.L(L_test),.w(w_test),.R(R_test),.Q(Q_test));

endmodule

c)仿真后的波形截图

L为0时并行加载,数组R为加载时的输入。L为1时移位,数组Q右移一位,左端补当前变量w的值。

d)综合后的RTL图形

3.设计一款4bit带复位功能的计数器

a)编写模块源码

module upcount(Reset,Clock,E,Q);

input Reset,Clock,E;

output reg [3:0]Q;

always@(posedge Reset,posedge Clock)

if(Reset)

Q<=0;

else if(E)

Q<=Q+1;

endmodule

b)测试模块

`timescale 1ns/1ps

module tb_upcount;

reg Reset_test;

reg Clock_test;

reg E_test;

wire [3:0]Q_test;

initial

Clock_test=0;

always #5 Clock_test=~Clock_test;

initial

begin

Reset_test=1;

E_test=0;

#2

Reset_test=0;

#8

E_test=1;

#184

Reset_test=1;

#2

Reset_test=0;

#32

E_test=0;

end

upcount UUT_upcount(.Reset(Reset_test),.Clock(Clock_test),.E(E_test),.Q(Q_test));

endmodule

c)仿真后的波形截图