CMOS低噪声放大器的噪声系数优化

- 格式:pdf

- 大小:748.85 KB

- 文档页数:3

减小放大器噪音的几种途径和方法做了这么多,说下心得了,是多年实践出来的。

后级放大器噪音的噪音引入,在设计合理的状况下,主要是电源和LAYOUT,把好这两关就基本问题不大。

但前级的放大器,也就是前置,就得考究了。

1、器件的挑选包括运放和三机管的挑选,都要尽量挑选低噪音的,包括输入噪音和偏置的噪音。

假如主要是运用于电压放大就偏重于电压噪音,电流放大的就是电流噪音了。

等器件,也是很考究的,电容尽量选用CBB材料,电解就用钽的,最好了。

电阻呢,频率低的最好就用法绕线电阻,那是最抱负的。

但假如频率高时,就必需用金属膜了。

2、考虑电路的环路噪音引入一个良好的布局和走线,要充分考虑电流的流向,尽量避开电流从信号输入端的地线流过。

普通的建议就是在敏感学号周围,用一个开个小天窗的地线铜环围上一圈。

电源电流以节点的形式,单独引到一个不敏感的参考点。

假如输入信号线比较长,也是用地线环抱至引出端。

3、一个良好的电源供给电路电源,在噪音方面的贡献,不行小视。

在高场合的应用时,普通都是用线性电源为多。

比如HP的可编程电源,都是用线性的,而不是用开关的电源。

它的噪音可以做到几个uV。

一个好的运放,是对电源有很好的抑制,但单靠它也不可的。

要想提高,就得额外加些辅助器件了。

它们普通对低频的抑制都十分好,所以主要就是考虑电源中的高频干扰的抑制了,假如加入LC,RC,共模滤波等等4、注重空间的电磁辐射一些敏感的器件,甚至会被空间的电荷和电磁所干扰。

应付这个,最好的方法就是加个屏蔽罩。

所以,看到有些电荷放大器不加罩,绝对会不稳定。

风吹一下值说不定就输出就开头漂了。

5、环境的影响假如有的工作温度变幻比较大的话,就得考虑环境温度了,有的工作场合会几十度的变幻,那就得考虑全部的器件的温度PPM值。

假如很难控制的话,就想方法恒温了。

比如做个恒温室加上恒温电路。

一个使用并联电阻反馈和系列感性调峰技术的小型宽带CMOS低噪声放大器摘要宽带低噪声放大器(LNA)利用分流电阻反馈和系列电感调峰技术达到宽频带内的输入匹配,功率增益和平滑的噪声系数(NF)响应。

此宽带低噪声放大器(LNA)是使用0.18米CMOS技术来实现的。

测量结果表明功率增益大于10 dB,从2到11.5 GHz的输入回波损耗低于10 dB。

三阶输入截点IIP3为+3 dBm,和带外NF范围从3.1至4.1分贝。

结果发现模拟与实测数据非常吻合,归因于与以往的设计相比此电路所需的被动元件数量更少。

此外,电路片的品质因数为190(MW每平方毫米),这在所有先前报道的以CMOS为基础的宽带低噪声放大器(LNA)中是最好的。

关键词CMOS,反馈,低成本,低噪声放大器(LNA),系列调峰,小芯片尺寸,宽带。

一·概述宽带系统最近获得关注是由于其高速的数据传输能力,所谓的超宽带(UWB)技术提供了频率在3.1到10.6 GHz有吸引力的高速无线信号的方案。

为了与天线和预选择滤波器接口匹配,低噪声放大器(LNA)在3.1到10.6 GHz的整个波段的输入阻抗应该接近50Ώ。

到现在为止,已经提出了许多为UWB LNA设计的宽带技术。

分布式放大器(DA)是广泛应用于宽带的技术,由于其固有的宽带频率响应伴随着良好的输入和输出阻抗匹配线性下降到DC。

然而,到目前为止,它的高功耗和芯片面积大,阻碍了其广泛应用[1][2]。

最近一个具有输入带通响应的宽带阻抗匹配的级联CMOS低噪声放大器已被报道[3]。

带通滤波器(BPF)基于拓扑结构采用了级联的输入阻抗放大器作为滤波器的一部分。

然而,在采用的滤波器输入端需要许多电抗性元件,这就不可避免地导致更大的芯片面积和噪声系数(NF)从而造成芯片实现的退化。

一个有效的方式来实现小功耗的宽带匹配和芯片面积为共栅输入拓扑结构。

然而,据报道共栅LNA具有较低的增益和比共源放大器更高的噪声系数[4]。

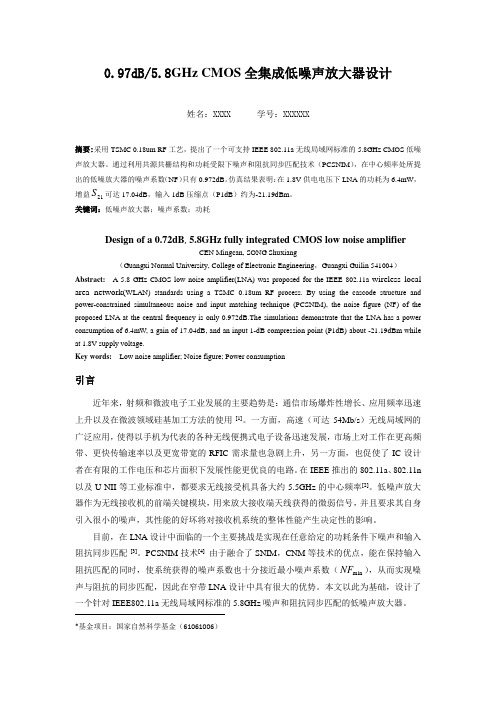

0.97dB/5.8GHz CMOS全集成低噪声放大器设计姓名:XXXX 学号:XXXXXX摘要:采用TSMC 0.18um RF工艺,提出了一个可支持IEEE 802.11a无线局域网标准的5.8GHz CMOS低噪声放大器。

通过利用共源共栅结构和功耗受限下噪声和阻抗同步匹配技术(PCSNIM),在中心频率处所提出的低噪放大器的噪声系数(NF)只有0.972dB。

仿真结果表明:在1.8V供电电压下LNA的功耗为6.4mW,S可达17.04dB,输入1dB压缩点(P1dB)约为-21.19dBm。

增益21关键词:低噪声放大器;噪声系数;功耗Design of a 0.72dB, 5.8GHz fully integrated CMOS low noise amplifierCEN Mingcan, SONG Shuxiang(Guangxi Normal University, College of Electronic Engineering,Guangxi Guilin 541004)Abstract: A 5.8 GHz CMOS low noise amplifier(LNA) was proposed for the IEEE 802.11a wireless local area network(WLAN) standards using a TSMC 0.18um RF process. By using the cascode structure and power-constrained simultaneous noise and input matching technique (PCSNIM), the noise figure (NF) of the proposed LNA at the central frequency is only 0.972dB.The simulations demonstrate that the LNA has a power consumption of 6.4mW, a gain of 17.04dB, and an input 1-dB compression point (P1dB) about -21.19dBm while at 1.8V supply voltage.Key words: Low noise amplifier; Noise figure; Power consumption引言近年来,射频和微波电子工业发展的主要趋势是:通信市场爆炸性增长、应用频率迅速上升以及在微波领域硅基加工方法的使用[1]。

一种低功耗CMOS LNA优化设计方法

周洪敏;张瑛;于映;丁可柯

【期刊名称】《南京邮电大学学报(自然科学版)》

【年(卷),期】2015(035)001

【摘要】基于SMIC 0.18 CMOS工艺,设计了一个工作频率为5.8 GHz的差分低噪声放大器.针对低功耗电路的设计要求,通过在输入级增加电容实现了限定功耗下的输入和噪声同时匹配.仿真结果表明,设计的低噪声放大器具有良好的综合性能指标.增益为22.47 dB,噪声系数为1.167 dB,输入反射系数(S11)、输出反射系数(S22)、反向隔离度(S12)分别为-24.74 dB、-17.37 dB、-31.52 dB.在1.5V电源电压下,功耗为17.3 mW.

【总页数】5页(P114-118)

【作者】周洪敏;张瑛;于映;丁可柯

【作者单位】南京邮电大学电子科学与工程学院,江苏南京210023;南京邮电大学电子科学与工程学院,江苏南京210023;南京邮电大学电子科学与工程学院,江苏南京210023;南京邮电大学电子科学与工程学院,江苏南京210023

【正文语种】中文

【中图分类】TN45

【相关文献】

1.一种CMOS超宽带LNA的优化设计方法 [J], 刘萌萌;张盛;王硕;张建良;周润德

2.基于低功耗约束的CMOS LNA的优化设计 [J], 刘高辉;张金灿

3.基于RF SOI CMOS工艺高线性低功耗LNA设计 [J], 何全;陈忠学;章国豪

4.一种新颖的低功耗CMOS LNA的优化设计 [J], 徐盼盼

5.低功耗CMOS UWB LNA设计综述 [J], 吴伟;李卫民;赵元富

因版权原因,仅展示原文概要,查看原文内容请购买。

第30卷 第2期2007年4月电子器件Ch inese Jou r nal Of Elect ro n DevicesVol.30 No.2Ap r.20075.8GHz All 2on 2Chip L ow N oise Amplif ier in 0.18μm CMOS f orApplicat ion of 802.11a System 3J IA N G D on g 2mi n g ,H U A N G Fen g 2y i3,L U J i n g 2x ue ,Z H AO L i a ng(Ins ti t ute of R F &O E 2IC ,S out heast Universit y ,N anj i ng 210096,China)Abstract :A n a nal ysi s of i nput 2matchi ng and noi se and linearit y i s present ed ,which follows up a met hod t o upgrade t he general performa nce of Low Noise Amplifier.Noi se opt imization i s t aken on by sof tware and a 5.8GHz al l 2on 2chip Low Noi se Amplifier i n 0.18μm CMOS t echnology i s present ed.Wit h t he mea sure 2ment dat a of i nduct ors applied by t he Foundry ,paramet er ext raction i s carri ed on for t hese i nduct ors.An accurate on 2chip inductor s model i s realized for t he ci rcui t sim ulation.The result is t hat t he total circuit ’s power consumption i s 13mW ,t he power gain i s 14dB ,t he noi se fi gure i s 2.05dB ,and t he li neari t y per 2for ma nce i s t he IIP3of -1dBm.K ey w or ds :low noi se amplifier ;CMOS technology ;noi se opti mization ;inductor model EEACC :2570;1220用于802.11a 系统的 5.8GH z 0.18μm CMOS 全集成低噪声放大器设计3蒋东铭,黄风义3,陆静学,赵 亮(东南大学射频与光电集成电路研究所,南京210096,China)收稿日期62823基金项目江苏省自然科学基金资助(B K 66)作者简介蒋东铭(2),男,在读硕士生从事射频集成电路设计研究,y_j @63;黄风义(62),男,教授,博士生导师,f y @摘 要:通过对输入匹配、噪声和线性度的分析,给出了改进低噪声放大器综合性能的方法.利用软件对电路进行噪声优化,设计出了一个0.18μm CMOS 工艺的5.8GHz 全集成低噪声放大器.采用工艺厂家提供的电感测试数据进行参数提取,得到精准的电感模型并用于电路仿真.设计结果是整个电路功耗13mW ,功率增益为14dBm ,噪声系数为2.05dB ,线性度指标IIP3为-1dBm.关键词:低噪声放大器;CMOS 工艺;噪声优化;电感模型中图分类号:TN 722.3;TN 702 文献标识码:A 文章编号:100529490(2007)022******* 随着宽带无线通信技术的不断发展和市场的不断扩大,5GHz 无线射频频段得到了越来越广泛的应用[1].CMOS 工艺的高集成度、低价、低功耗使其生产的射频芯片比砷化镓工艺或双极性硅工艺的芯片具有明显的性价比优势[2];在芯片系统(Syst em On Chip ,SOC)的提出,要求越来越多的电路元件集成到单个芯片上.低噪声放大器(LNA )是无线射频接收机前端的重要模块,它的噪声系数、增益和线性度等指标对整个射频接收机系统的性能有重要影响,其中噪声系数几乎决定了整个接收机的噪声性能[1,2].本文设计的低噪声放大器使用0.18μm CMO S 工艺,可应用于WLAN 802.11a 标准的5.725~5.825GHz 频段.全部采用片上元件来实现,其中电感采用的是片上螺旋电感.基于螺旋电感的测量数据进行了电感模型参数提取,并用于电路仿真,提高了电感模型的精确度,也避免了使用键合线电感时感值不易控制的缺点.8:20001:20040:1979do m ian g 1.co m 194hua n g se 1 低噪声放大器电路设计在满足输入匹配前提下获得低噪声一般都采用源极电感负反馈的方式来实现[7].实际电路中则采用共源-共栅(Cascode )结构,可以减小MOS 管的密勒效应,减小输入匹配和输出匹配之间的影响,同时增加反向隔离度[3].本次设计采用的电路结构如图1所示.通过对传统结构的改进,在输入电感L g 和MOS 管M 1之间并联了接地电容C p 来调节输入功率匹配和最小噪声匹配,并适当增加输入响应的平坦度.图1 L NA 电路图1.1 输入匹配对于射频信号,隔直电容C in 可以忽略.输入信号电路如图2.图中将电路划分了两个参考平面.参考平面1的左侧所表现的信号输入阻抗即为信号源图2 输入匹配电路的输入阻抗R s ,一般为50Ω.现定义参考平面2的右侧,即晶体管一侧的输入阻抗为Z in =R eq +j ω0L eq .因此为了实现功率匹配,则需要使参考平面2左侧的输入阻抗匹配为R eq -j ω0L eq .此时有R eq =R sω2C 2pR 2s+(1-ω20C p L g )2(1)L eq=L g -C p (ω20L 2g +R 2s )2ω20C 2p R 2s +(1-ω20C p L g )2(2)而根据[5],有Z =j ωL +j ω+L =L +j (ωL ω)(3)C gs 为栅极和源极之间的电容,g m 为MOS 管的跨导.当输入电路谐振在ω0频率时,参考平面2两侧电路的实数部分相等,而复数部分则相互抵消,从而实现最大功率传输.1.2 噪声优化共源共栅结构的低噪声放大器,其噪声系数主要由共源的NMOS 管决定,而共栅管对噪声系数的影响很小,可以忽略[8].源极电感L s 形成源极去偶结构,在提高线性度的同时并不引起噪声系数的增加[7].本次设计所用的片内电感由于Q 值不高,提高了设计难度.采用精确的片上电感模型,提高仿真模型的精确度,能更精确的仿真和优化噪声系数[3].片上电感模型将在后文叙述.根据功率约束噪声优化设计方法[4],可以得到M 1的最优栅宽为W opt =13ω0LC o x R ′s(4)上式中C o x 为栅氧化层电容,L 为有效沟道长度,R ′s 为等效电源内阻,输入匹配时近似为R eq .这一最优栅宽W opt 在20%范围内变化对噪声系数的影响不大,一般小于0.2dB 左右.对于栅宽W opt 的器件,得到最小噪声系数为[7]F min =1+2.4γαω0ωT(5)γ和α是与沟道长度相关的参数,由工艺给出,ωT 为MO S 管的截止频率ωT ≈g mC gs(6)通过增加栅极电压可增大MO S 管的跨导g m ,能够提高MOS 截至频率ωT ,降低噪声系数.1.3 电路的线性度共源共栅结构的电路,其线性度主要由共栅管M 2决定.因此改善M 2管的栅宽W 和提高栅极直流偏压V gs 能有效地提高整个电路的线性度[5].但是M 2管的V gs 的增加又会导致M 1管的源漏电压V ds 的降低,降低了M 1管的线性度.因此,在不增加整体电路直流电压的情况下,电路线性化的改善主要通过M 2管的栅宽优化来得到.2 电路仿真与优化本次设计采用TSMC 的0.18μm CMOS 工艺库,基于BSIM3模型,采用Agilent 公司的ADS2003C 来进行电路仿真.为了提高片上电感的准确度,对片上电感单独进行了建模和参数提取仿真时采用的为电感模型为双π模型,如图3利用工艺厂家提供的片上电感的S 参数测试数据,183第2期蒋东铭,黄风义等:用于802.11a 系统的5.8GHz 0.18μm CMO S 全集成低噪声放大器设计8i n0s 10C g s g m C gssg m C gs s 0s -10C gs..用自主开发的模型参数提取方法[6]对模型进行了参数提取.参数提取结果再进行S参数仿真并和测试结果进行对比,如图4.片上电感品质因素Q的测试结果与仿真结果的对比如图5.从图4和图5可以看出,该模型在0~15GHz频段内能够很精确地模拟片上电感的性质.图3 片上螺旋电感的双π模型图4 电感S参数仿真与测试结果对照图5 电感品质因素仿真与测试结果对照通过ADS软件对电路进行优化得到LNA主要参数选择如下:M1栅宽90μm,栅极偏压为0.8 V,M2栅宽80μm.仿真在25℃、输入输出负载50Ω条件下,采用1.8V电源供电,得到的结果如图6~图9.(1)图6为S11和S22参数曲线,分别表征了输入端口与输出端口的匹配程度.在5.8GHz频率上,输入反射系数和输出反射系数都达到了-25 dB,实现了较好的匹配.(2)图7为S21参数曲线,表征了整个电路的增益情况.由图可知,在5.8GHz时,正向传输增益接近14dB.(3)图8为噪声系数曲线在中心频率58G z处整个电路的噪声系数为5B对于L和L都用片内电感实现,由于Q值较低,因此这个噪图6 输入与输出反射系数S11,S22图7 功率增益S21声系数是比较合理的.图8 噪声系数(4)图9为电路的1dB压缩点和三阶互调点的曲线.从图中可知,电路的1dB压缩点输入功率(P1dB)约为-12dBm,三阶互调点输入功率(IIP3)约为-1dBm.图9 线性度P1dB与IIP33 版图设计版图设计采用Cadence设计工具和TSMC的0.18μm CMO S元件库.在设计中,对于高频信号采用8边形焊盘,并使用顶层金属,减小焊盘的寄生电容和耦合引起的损耗整个版图如图所示由于电感都选用片内元件,因此面积较大版图将交付工艺厂家流片加工283电 子 器 件第30卷8..H2.0d.g s.10...图10 低噪声放大器版图4 结论通过理论推导和软件优化,并采用精确电感模型进行了电路仿真,设计了一个中心频率5.8GHz,噪声系数为2.05dB的CMO S全集成低噪声放大器,且实现了输入输出的良好匹配.本文所采用的电路优化方法,可为射频集成电路在芯片系统设计提供参考.随着工艺的提高和成本的继续降低,CMOS工艺能够更多地利用片上电感来设计射频集成电路.参考文献:[1] Lee Tho m as H,Hi rad Samavat i,Ham i d R R.52GHz CMOSWi reless LANs[J].IEEE TM T T,2002,50(1):2682280.[2] Asad A Abi di.R F C MOS Comes of Age[J],IEEE Micro waveMagazine,Decem ber2003,47260.[3] Chi u Hu ng2Wei,Lu Shey2Shi,Li n Y o2Sheng.A2.172dB NF5GHz Band Mo nol it hic CMOS LNA wit h102mW DC PowerC o nsumpt ion[J],IEEE TM T T,Mar.2005,53(3):8132824.[4] M.Kumarasamy,et al.A Full y Integrat ed Vari abl e Gai n5.752GHz LNA wi t h on Chip Act ive Bal un fo r WL AN[C]//IEEE RFIC Sym po s i um,2003,4392442.[5] VojkanVidoj kovic,et al.Fully2Int er grat ed D EC T/Bl uet oot hMult i2ban d LNA In0.18μm CMOS[C]//IEEE ISCAS,2004, 5652568.[6] Lu J ingxue,Huang Fengyi,Yusong Chi.An Anal ytical Ap2p roach t o Paramet er Ext ract ion fo r On2Chip Spiral Induct ors Wit h Symmet ric Do ubl e2πEqui valent Circui t[C]//IEEE R FIC Symposiu m,2006,2212224.[7] Lee Tho mas H.CMOS射频集成电路设计[M],电子工业出版社,2004.[8] Behzad Razavi.模拟CMOS集成电路设计[M],西安交通大学出版社,2004.(上接第379页)[4] 李子东.实用粘结手册[M].上海:上海科学技术出版社,1987:1.[5] 浩宏奇,金志浩,王笑天.陶瓷钎焊的研究[J],兵器材料科学与工程,1994,17(1):13.[6] 陈铮.陶瓷2金属活性金属钎焊研究的现状和进展[J],华东船舶工业学院学报(自然科学版),2001,15(2):1.[7] Treheux D.et al.Metal/Ceram i c S oli d St at e Bo ndi ng:Mecha2nis ms and Mechanics[J].Script a Metall urgi cal et Mat eri alia,1994,31(8):1055.[8] IINO Y.Part ial Transient Li qui d2Phase Met al s L ayer Tech2nique of Ceramic2Met al B o ndi ng[J].J Mat er Sci L et t,1999,(10):104.[9] 陈铮,周飞,李志章等.陶瓷与金属活性钎焊的研究进展[J].材料科学与工程,1995,13(3):61.[10] 刘联宝.陶瓷2金属封接技术指南[M].国防工业出版社,1990.6:69.[11] 盛文彦,曾令可,王慧等.结构陶瓷表面改性技术[J],佛山陶瓷,2005,(4):[12] 郑立允,熊惟皓.金属陶瓷表面处理的研究进展[J],机械工程材料,2004,28(9):9.[13] 戴家辉,刘秀忠,陈立博.无铅钎料的立法与发展[J],山东机械,2005,(1):7.[14] 胡志田,何前进,徐道荣.无铅软钎料国内外的研究动态与发展趋势[J],焊接技术,200534(3):4[15] 李明雨,冯武锋,王春青.无焊剂钎焊技术的最新发展现状[J],焊接,1998,(2):2.[16] Lug scherder E,Zhuang H,et al.Alloy,in Parti cular a S ol derAl loy,Met hod for Joi ni ng W o rkpieces b y Solderi ng Using t heS ol der Allo y and Use of t he Allo y for S ol deri ng[P].WO97/03789.[17] Lug s cherder E,Zhuang H,et al.Lot legi erungen2Verwend2ung der Lo tlegierung und Verf ahrer zum Verbi nden vonWerkst offen durch L oten[P].DE Pat ent19526822c2. [18] Hil len F,Casti llo P,Ras s A et al.Solder Alloys and S ol de2ri ng Processes for Fl ux2Free S ol deri ng of Diffi cult2to2Wet Ma2 t eri al s[J],Wel ding&Cut ti ng,2000,(8):162.383第2期蒋东铭,黄风义等:用于802.11a系统的5.8GHz0.18μm CMO S全集成低噪声放大器设计8。

第17卷第4期 湖南工程学院学报 Vo1.17.No .42007年12月 Jour na lof Hunan I nstitute of Engineering Dec .2007收稿日期6基金项目国家自然科学基金资助项目(666)作者简介邓桂萍(),女,硕士研究生,研究方向射频集成电路设计一种高线性的C MOS 低噪声放大器结构邓桂萍1,王春华2(1.湘潭大学信息工程学院,湖南湘潭411105;2.湖南大学计算机与通信学院,湖南长沙410082) 摘 要:采用TS MC0.35μmC MOS 工艺,设计了一个5.7G Hz 可用于无线局域网的低噪声放大器,电路在采用单端共源共栅结构的基础上为改善线性度而引进低频陷波网络(Low -frequency -trap Net 2work),用ADS 软件仿真与优化.仿真结果表明,在电源电压1.5V 情况下,噪声系数NF 为1.22dB ,输入反射系数S 11为-15dB ,反向隔离性能S12为-32.9dB ,增益S21为17.8d B ,三阶交截点II P3为+12.7dBm ,功耗为8mW.关键词:低噪声放大器;无线局域网;线性度中图分类号:T M76 文献标识码:A 文章编号:1671-119X (2007)04-0005-040 引言随着无线通信事业的不断发展,人们对无线通信系统的要求越来越高,比如低电压低功耗、低噪声、大动态范围、高灵敏度和高线性度等,而处于接收机前端的低噪声放大器(l ow noise amplifier,简称LNA )对于提高整个系统的线性度起着关键作用.这就意味着我们在设计低噪声放大器中必须在增益、噪声、线性度及功耗等性能指标中要合理的折衷.近年来出现了大量关于提高线性度的文献[1-11],文献[1]采用中等反型区偏置的方法,利用MOSFET 的转移特性及高阶跨导特性,将其偏置在强反型与亚阈区之间的一个最佳栅源偏置电压,此处MOSFET 的三阶跨导为零,理论上电路的三阶非线性为零.但是,这个最佳偏置点对工作频率、负载阻抗、源极电感大小、工艺参数特别是阈值电压涨落等的变化非常敏感.因而实际中一般都是采用线性化技术来提高线性度.文献[2]采用直接补偿法,这种方法为了降低三阶交调,需要付出较大的功耗,而且增益和噪声性能还有所损失.文献[3]采用前馈补偿方法,这种方法实现的前馈补偿电路,电路的增益性能不会损失,但是也仍然需要付出较大的功耗代价.文献[4]采用亚阈区MO SFET 补偿法,利用亚阈区器件的三阶跨导与强反型器件的三阶跨导相抵消来提高LNA 的线性度,但是亚阈区MOSFET 的截止频率f T 很低,当信号频率较高时,补偿效果有可能下降,不适合频率比较高的情况.文献[5]改进文献[4]中的方法,在主支路和补偿支路使用了不同的负反馈电感,文献[6]把文献[4]中的亚阈区MOSFET 换成BJT,但是,因为标准C MOS 工艺中很难获得高性能的BJT,所以这样的改进有较大的局限性.文献[7]采用线性区MOSFET 补偿,这种方法与亚阈区MOSFET 补偿类似,只是用不同的方法去实现三阶跨导的“峰”.文献[8-9]根据Volterr a 级数分析对双极型晶体管BJT 放大器利用不同的带内和带外阻抗特性来提高电路的线性度.前面所提到的文献中只有文献[11]是针对5G HzC MOS LNA 的线性度而做的研究,提出采用前馈失真补偿方法(Feedf or ward D istorti on Cancella tion ),文献中的这种方法虽然对噪声影响不大,但是结构比较复杂,功耗增加许多.其它的文献基本上都是针对5G Hz 以下的电路而提出的线性化技术.本文将根据对单端C MOS 共源共栅结构进行Volterr a 级数分析的结果,提出一个采用低频陷波网络来提高线性度的工作于5.7G Hz C MOS 低噪声放大器,结构简单,用ADS 软件进行仿真优化验证.:2007-0-27:07021:1981-:.1 共源共栅结构的Volterra 级数分析首先对共源级进行Volterr a 级数分析[10].用来推导C MOS 低噪声放大器共源级交调表达式的电路模型如图1,v s 是源电压,Z g 是栅极阻抗,包括栅极电感及寄生电阻,Z s 是源极阻抗,C gs1是栅源电容,v gs 1是栅源电压,i d1是漏极电流,在这里我们忽略场效应管的输出电阻和栅漏电容.共源级的输入参考I M 3可以通过令s 1=j ω1,s 2=j ω2,s 3=j ω3得到,假定s ≈s 1≈s 2并且△s =(s 1-s 2)νs,那么我们可以把输入参考I M 3表示为:I M 3=34A 3(s 1,s 1,-s 2)A 1(2s 1-s 2)v s2≈12Kg 5mA 1(s )32A 1(2s )Z s (2s )+A 1(△s )1+sC gs (Z g +Z s )v s2(1)式中,k =μn C ox 2WL.u n 是电子迁移率,C o x 是栅氧化层电容,W 是管子宽度,L 是管子长度,g m 是跨导,A 1(s),A 2(s),A 3(s )是Volte rra 级数的系数[10].图1 共源级模型 图2 级联共栅级的模型 再来看级联共栅级的Volte rra 级数分析[10].为了把级联场效应管的影响加入三阶交调表达式中,我们使用由图2示出的级联共栅级电路模型.其中i d1是共源级的输出电流.g m 2和C gs2分别为M 2的跨导和栅源电容,假定场效应管M 2的输出电阻很大以致可以忽略.采用与推导共源级非线性方程相似的方法,我们可以得到:I M 2tota l=34g m 2K 21g4m1A 2s (S)[A 1(2s)Z s (2s)+A 1(△s)Z s (△s)][1-A 1(s )Z s ]1g m2+sC gs2-K 1K 23g 2m 1A 21(s )[1-A 1(△s )Z s (△s )]1g m2+sC gs21g m 2+△sC gs2-2K 1K 23g 2m1A 21(s)[1-A 1(2s)Z s (2s)]1g m2-sC gs21g m 2+△sC gs2v s2-K 1K 23g 2m1A 21(s )[1-A 1(△s )Z s (△s )]1g m 2+sC g s21g m 2+△sC gs2-2K 1K 23g2m 1A 21(s )[1-A 1(2s )Z s (2s )]1g m 2-sC gs21g m 2+△sC gs2(2) 然而这个表达式太复杂,我们无法直接从(2)式得出结论而提供对设计的指导,必须借助其他的数学工具,这里就不再详述. 提出的提高线性度方法由于整个放大器的非线性主要由第一级的非线性决定,在这里我们暂不考虑第二级的非线性.从(1)式我们可以看出,三阶交调项与1+sC gs (Z s +Z g )的模相关,对于感性负反馈,s C gs Z s 项为一个负实数而部分抵消了“1”这一项,但是对于阻性和容性负反馈就没有这样的抵消作用,因为阻性负反馈中该项为纯虚数,而容性负反馈中该项为正实数另外,三阶交调项还与()Z ()+(6 湖南工程学院学报 2007年2.2A 12s s 2s A 1△s)Z s (△s)的模相关,这一项由二阶互扰而产生.二阶互扰项表明,三阶交调的大小不光与工作频率相关,也与干扰频率的差和相关.因此,我们要想提高整个放大器的线性度,要么尽可能的减小二阶互扰项2A 1(2s )Z s (2s )+A 1(s )Z s (s )的模,要么尽可能的减小1+s C gs (Z s +Z g )的模.如果我们能使1+s C gs (Z s +Z g )的模趋于0,那么我们就能获得最佳线性度.在前面我们知道,如果是感性负反馈,sCgsZ s 项为一个负实数而可以部分抵消“1”这一项,但这是毕竟有限的.我们还注意到,sC gs Z g 中也有一部分为负实数而可以部分抵消“1”,实际上sC gs Z g 中产生负实数的是Z g 中的感性部分,猜想如果我们能使这一部分增大,那么能抵消“1”的部分又增大了,因而1+sC gs (Z s +Z g )的模减小而达到提高线性度的目的,但是Z g 中的感性部分L g 过大的话不利于我们整个放大器的片上集成,而且在源极电感负反馈结构中为满足输入匹配L g 还受谐振频率和阻抗匹配50Ω的限制.于是在这里我们引入低频陷波网络[8],如图3所示.图3 低噪声放大器结构3 提出的C MOS LNA 电路结构提出的C MOS LNA 电路结构如图3所示,其中M 1、M 2为共源共栅结构,M 1为输入器件,产生与输入电压成正比的小信号漏电流;共栅晶体管M 2用于减小输入与输出之间的相互作用提供良好的隔离性能并抑制了M 1的M ille r 效应;输入匹配仍采用源极电感负反馈结构并由L g 和L s 实现,这种结构在提供很低的噪声系数的同时容易得到50Ω的输入阻抗;L 2和C 2构成调谐电路实现输出匹配;直流工作时晶体管M 3与M 形成电流镜,M 3的宽度相对很小,这里取为M 宽度的十分之一,从而偏置电路消耗的电流最小;电阻R 要取足够的阻值以减小偏置电路的噪声电流;电阻R 1用来调节输入级晶体管M 1的栅源电压和漏极电流以决定静态功耗;C 1用于将射频与直流隔离,选择适当的电容(如10nF ),使其电抗值对于信号频率可忽略不计;L t 和C t 构成了低频陷波网络,为提高电路的线性度.表1 C MOS 低噪声放大器详细模拟结果参数模拟结果参数模拟结果电源电压 1.5V S 11-15dB 频率 5.7GHz S 12-32.9dB 噪声系数 1.22dB S 2117.8dB 功耗8m WII P3+12.7d Bm4 仿真结果根据图3所示电路原理结构,采用TS MC0135μmC MOS 工艺,使用A DS 软件对该LNA 进行模拟与分析优化.表1给出了本文提出的LNA 详细模拟结果,图4(a )~(d )给出了噪声系数NF,输入反射系数S 11,反向传输系数S 12及增益S 21随频率变化的趋势的仿真结果,图5.14(e)给出了线性度II P3仿真结果.7第4期 邓桂萍等:一种高线性的C MOS 低噪声放大器结构112图4 仿真结果5 结 论本文在根据对单端C MOS 共源共栅结构进行Vol 2terra 级数分析的结果的基础上,提出了一个采用低频陷波网络来提高线性度的工作于517G Hz C MOS 低噪声放大器,结构简单.采用TS MC0135μmC MOS 工艺使用A DS 软件进行仿真,仿真结果表明,该低噪声放大器结构具有良好的性能:在电源电压1.5V 情况下,噪声系数NF 为1122d B ,输入反射系数S 11为-15d B ,反向隔离性能S 12为-3219d B,增益S 21为1718dB,三阶交截点II P3为+1217d Bm ,功耗为8mW .参 考 文 献[1] T ool e B,Plett C,CloutierM.RF Circuit I m plica ti onsof Mod 2erat e Inv ersi on Enhanced Li near Regi on in MOSFETs [J ].I EEE T RA NS .C I RC U IT S AN D SY ST E MS —I :REG U LAR PAPE RS,2004,51(2):319-328.[2] D ing Y,Ha ryani R.A +18d Bm IIP3LNA in 0.35u mC MOS[C ].I n:P r oceedings of I EEE ISSCC,2001:161-162.[3] Aparin V,B r own G,Lars on L E .L I NE AR IZ ATI ON OFC MOS LNA ’S V I A OPTI M U M G ATE B I A S -IN G[C ].In:Proceedings of the 2004I nterna ti ona l Sy mposiu m onC ircuits and System s,2004,4:748-751.[4] Ki m TW ,Ki m B,L ee K .Highly Linea r Rece iv e r Front-end Adop ting MOSFET Transconductance L i neariza -ti on by Multi p le Ga ted Tran sist ors[J ].IEEE J.S o lid -St a te C ircuits,2004,39(1):223-229.[5] Aparin V,Lars on L E .Modi fied Deriv a tiv e SuperpositionM eth od for Linearizati on FET Lo w -Noise Amp lifi e rs [J ].IEEE T .M icro wav e T heory and Technique,2005,53(2):571-581.[6] Xin C,Sanchez S E .A L inearization Technique For RFLo w Noise Amp lifier [C ].In:Proceedings of IEEEIS CAS,2004.[7] Tanaka S,Behbahani F,Abidi A A.A Linea riza ti onTechnique For C MOS RF Powe r Amp lifie rs [C ].In:Proceedings of IEEE Sy mposiu m on VLS I Circuits,1997:93-94.[8] Keng L F .High 2frequency Analysis of Linearity I mp r ove 2ment Technique of Com mon 2e m itter Transconductance stag e Using a Lo w 2Frequency 2Trap Net w ork[J ].I EEE J .S OL I D 2ST ATE CIRCUITS,2000,35(8):1249-1252.[9] Keng L F,Robert G .H igh 2frequency Nonlinear ityAnaly 2sis of Co mmon 2e m itte r and Differential 2pair Transcon Ductance Stages [J ].IEEE J.S OL I D -ST A T E C I R 2CU ITS,1998,33(4):548-555.[10]Z hang WC,Chen KS .Nonli nearity ana l ysis of C MOS LNA based on Volterra se ri e s[C ].The 3rd C ross Stra it Tri 2R egi ona l R adio Science and W ire less Technology Conference,2002.[11]L in M,W ang H,L i Y,Chen H.A Novel IP3BoostingT echnique U sing Feedfor wa rd D istorti on Cance lla ti on Me th od f o r 5G Hz C MOS LN A [J ].Ana l og Integrated Circuits and Si gnal P r ocessing,2006.A H i ghly L i n ea r CMO S Low Noise Am pli f i erDENG Gui -p ing 1,WANG Chun -hua2(1.Collage of Infor ma tion Engineering,Xiangtan University,Xiangtan 411105,Chi na;2.School of Co mpute r and Co mm unicati on,Hunan Univ e rsit y,Changsha 410082,Chi na)Abstrac t:A 5.7G Hz C MOS low noise a mp lifier (LNA )i mplemented with TS MC 0.35um standa r d C MOS tech 2nol ogy is p r e sented .The pr oposed LNA intr oduce s the l ow 2frequency 2tra p ne t w ork int o the single 2end common 2source common 2ga te cascade topology .Si m ulated and analyzed by the A D S s oft wa r e,the f oll owing pa r ame ters are y f 5V ,f B ,f 25B ,ff 23B ,B ,II 3+B W K y f ;;y8 湖南工程学院学报 2007年achieved:unde r the suppl v oltag e o 1.the n oise ig ure is 1.22d the input r e lecti on is 1d the reverse trans mitted coe icient is 2.9d the gain is 17.8d the P is 12.7d m and the po wer is 8m .e wor ds:lo w n oise a mpli ier wir e less l ocal net work linea rit。