FPGA设计方案

- 格式:doc

- 大小:939.50 KB

- 文档页数:34

fpga的设计流程

随着技术的发展,fpga设计技术也变得越来越成熟,越来越多的产品使用fpga进行控制,它们可以被用来实现很多种复杂的功能,但是在使用之前,需要进行一个系统的设计流程。

本文将对fpga的设计流程进行详细的介绍,帮助用户更好的实现fpga的功能。

首先,在使用fpga之前,用户需要确定fpga的目标功能,也就是要实现什么样的功能,这一步可以粗略的定义出完成的任务,也就是fpga的功能的架构。

其次,编写fpga的硬件结构,这一步要求用户熟悉fpga的硬件结构,以及fpga可以实现的功能结构,确定硬件结构后,可以使用EDA工具进行搭建。

第三,使用 HDL(硬件描述语言)进行编程,这一步是实现fpga 功能的关键,用户需要使用HDL,也就是Verilog或者VHDL来编写代码,使用这些语言来编写硬件电路及对应的功能,以完成fpga功能的部署和调试。

第四,使用仿真工具仿真和调试,完成了上述步骤后,用户可以使用仿真工具,仿真fpga的硬件结构,以及编写好的代码,以便发现硬件和软件的错误,以及调试软件程序以确保功能正常。

第五,烧录fpga,经过仿真和调试,用户需要将fpga烧录成fpga 芯片,这一步需要使用烧录器,将编写的程序烧录到fpga芯片,以实现fpga的功能。

第六,测试功能,最后,用户需要测试实现的功能是否符合预期。

以上就是fpga的设计流程,从fpga的功能定义到实际实现,需要涉及很多步骤,需要用户对fpga充分的了解,以此来确保设计的正确性和合理性。

研发设计 I RESEARCH DESIGN樓块图1系统总体设计框图近几年,随着FPGA (可编程逻辑器件)规模的日益增大, 我国数字电路设计取得了迅猛发展,硬件设计环境不断向实 用化、可靠化方向发展,为功能电路设计工作的有序开展提 供了硬件支持。

为此,如何科学设计和实现FPGA 开发平台 硬件系统、不断完善相关功能电路是相关软件开发人员必须思考和解决的问题。

1.系统总体设计FPGA 开发平台硬件系统主要由网 络模块、PS 2接口模 块和U S B 模块等模 块组成,系统总体 设计框图如图1所 示。

为了保证该系 统的运行性能,相关软件开发人员要重视对这些模块的设计与实现,为用户带 来良好的体验感。

1.1网络(D M 900A )模块电路设计网络(DM 900A )作为一种先进的接口芯片,充分利用 了以太网的应用优势,具有以下几种特征:①能够实现物理 层接口的全面集成;②内部含有FIFO 缓存,主要用于对大 量字节的接收和发送:③能够很好地兼容和支持不同类型的 主机工作模式;④在HP 证背景下,能够很好地实现自动翻 转功能和直接互联功能;⑤能够充分利用tcp /tp 加速器的应 用优势,避免CPU 承担过高的存储负担,从而实现对整机 运行性能的全面提高:⑥极大地缩短了读写时间。

总之,在 以太网控制器的应用背景下,相关软件开发人员要严格遵循 相关网络传输标准和要求,从而实现网速的提高和网络环境 的优化。

同时,在对网络模块电路进行科学设计的过程中, 确保该电路能够实现对相关接口的集成和应用,并采用接口 输入的方式将各种接口与芯片进行深度融合,以促进FPGA 开发平台硬件系统向智能化、自动化、信息化方向不断发展。

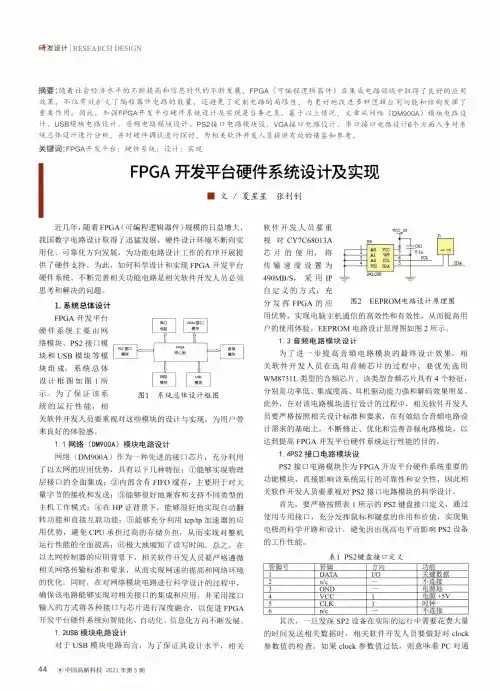

1.2USB 模块电路设计对于U S B 模块电路而言,为了保证其设计水平,相关软件开发人员要重 视对 CY 7C 68013A 芯片的使用,将 传输速度设置为摘要:随着社会经济水平的不断提高和信息时代的不断发展,FPGA (可编程逻辑器件)在集成电路领域中取得了良好的应用 效果,不仅有效扩大了编程器件电路的数量,还避免了定制电路的局限性,为更好地改进多种逻辑应用功能和结构发挥了 重要作用。

FPGA时钟设计在FPGA设计中,时钟设计需要考虑以下几个方面:1.时钟源:时钟源可以是外部信号源,也可以是FPGA内部的时钟发生器。

外部时钟源一般来自外部设备或者振荡器。

FPGA内部的时钟发生器可以根据需要生成所需的时钟频率。

2.时钟分频:时钟分频是指将输入的时钟频率分频为所需的输出频率。

在一些应用中,需要将时钟频率降低到一个更低的频率,以降低功耗或满足特定的应用需求。

3.时钟分配:在FPGA设计中,可能会有多个模块需要使用时钟信号。

时钟分配是指将时钟信号分配给各个模块,以确保它们能够按照同步的方式工作。

4.时钟域划分:在FPGA设计中,可能会存在多个时钟域,即不同的时钟频率和时钟相位。

时钟域划分是指将设计中的电路划分为不同的时钟域,并确保时钟跨域的数据传输正确。

5.时钟驱动和延迟:时钟驱动和延迟是指时钟信号的传输延时。

由于FPGA中的逻辑电路通常具有不同的传输延时,所以时钟信号需要正确地驱动各个子模块,以确保数据的正常传输。

在进行FPGA时钟设计时,需要考虑以下几个关键问题:1.时钟频率选择:时钟频率选择需要综合考虑系统的需求和FPGA的性能。

较高的时钟频率可以提高系统的工作速度,但也会增加功耗和电磁干扰。

较低的时钟频率可以降低功耗和电磁干扰,但会降低系统的工作速度。

2.时钟相位对齐:时钟相位对齐是指在不同时钟域之间进行数据传输时,需要确保时钟相位的对齐。

时钟相位对齐可以通过插入寄存器或者使用FPGA的时钟管理资源来实现。

3.时钟缓冲和驱动:时钟缓冲和驱动是指对时钟信号进行放大和驱动,以确保时钟信号能够正常传输和驱动其他模块。

时钟缓冲和驱动可以使用FPGA内部的时钟管理资源,如PLL和BUFIO等。

4.时钟分频策略:时钟分频策略是指根据需要将时钟频率分频为所需的频率。

时钟分频可以使用FPGA内部的分频器来实现,也可以使用逻辑电路来实现。

在FPGA时钟设计过程中,需要进行时钟约束设置,即设置时钟频率、时钟相位和时钟域等约束条件。

交织/解交织的FPGA设计与实现一.交织与解交织器的设计方案任意交织器的的交织与解交织的过程都可以总结为:交织是按顺序地址读入输入数据,按交织地址输出数据,即顺序写入,交织读出;解交织是按交织地址输入数据,按顺序地址读出数据,即:交织写入、顺序读出。

设计中利用一个存储器存储交织地址,这样做一方面在实现不同的交织器时。

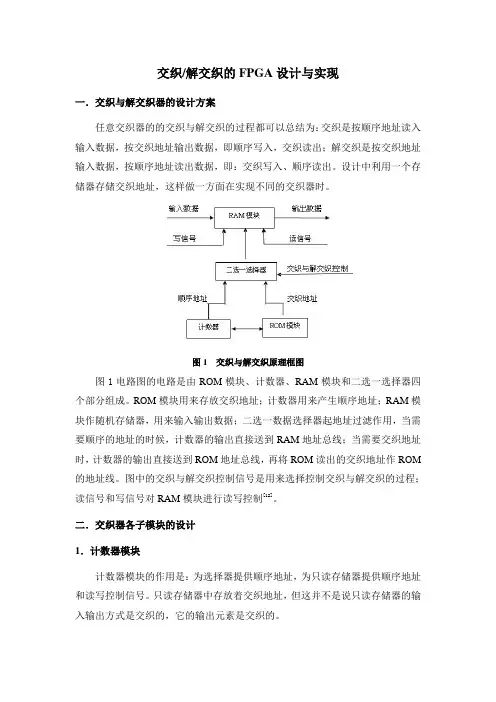

图1 交织与解交织原理框图图1电路图的电路是由ROM模块、计数器、RAM模块和二选一选择器四个部分组成。

ROM模块用来存放交织地址;计数器用来产生顺序地址;RAM模块作随机存储器,用来输入输出数据;二选一数据选择器起地址过滤作用,当需要顺序的地址的时候,计数器的输出直接送到RAM地址总线;当需要交织地址时,计数器的输出直接送到ROM地址总线,再将ROM读出的交织地址作ROM 的地址线。

图中的交织与解交织控制信号是用来选择控制交织与解交织的过程;读信号和写信号对RAM模块进行读写控制[12]。

二.交织器各子模块的设计1.计数器模块计数器模块的作用是:为选择器提供顺序地址,为只读存储器提供顺序地址和读写控制信号。

只读存储器中存放着交织地址,但这并不是说只读存储器的输入输出方式是交织的,它的输出元素是交织的。

图2所示为计数器模块:图2 计数器模块上面的模块是由程序实现的程序的代码(见附录),上图中clk是时钟信号,clr是清零信号,ena是使能信号,q就是输出。

输出显示的是0-15这16位的数字。

主要的作用就是读顺序地址的,和后面的那个交织地址能够对应起来。

图3所示的是计数器模块的功能仿真波形:图3 计数器模块的功能仿真波形图3仿真波形中的clk,clr,ena,q,cout与图2中的是一样的。

当clk为时钟信号,clr是复位信号当clr为高电平的时候q的输出就为0,ena为使能信号,cout在q从0到15输出后出现一个高电平,在15的地方显示高电平。

2.选择器模块选择器主要就是起选择作用的,起到了地址过滤的作用,当需要顺序地址的时候计数器就直接读出来送到RAM的总线上去,然后按照输入的正常顺序读出来。

引言随着经济和科学技术的发展,电梯在高层建筑物的作用越来越凸出。

目前电梯主要分为机械系统与控制系统两大部份,而电梯的控制系统主要有三种控制方式分别是:继电路控制系统(“早期安装的电梯多位继电器控制系统)、基于FPGA控制系统、微机控制系统。

实现继电路控制系统方法很多,可以用标准逻辑器件、可编程序控制器PLC、单片机等方案来实现。

但是这些方法的功能修改及调试都需要硬件电路的支持,在一定程度上增加了功能修改及系统调试的困难,且该系统由于故障率高、可靠性差、控制方式不灵活以及消耗功率大等缺点,已渐渐被人民淘汰。

微机控制系统虽在智能控制方面有较强的功能,但也存在抗扰性差,系统设计复杂,一般维修人员难以掌握其维修技术等缺陷,没能广泛应用电梯中。

而基于FPGA的电梯控制系统由于可靠性高,使用维修方便,抗干扰性强,设计和调试周期较短等优点,在电梯控制中得到广泛应用,从而使电梯由传统的继电器控制方式发展为计算机控制的一个重要方向,成为当前电梯控制和技术改造的热点之一。

本文给出一个基于FPGA的6层自动升降电梯控制系统的设计方案。

它的设计是采用通俗易懂的Verilog HDL硬件描述语言使用EDA技术在Quartus II软件平台上设计完成,程序设计、编译以及时序仿真通过后再下载到开发板配合外围电路(模拟电梯的电路)来验证该系统的可行性。

这个系统分主要有6个模块,分别是键盘响应寄存处理模块、上升/下降请求寄存处理模块、电梯运行和停止处理模块、开门/关门与延时处理模块、电梯运行方向判断模块和电梯运行状态显示模块。

通过模块化设计不仅提高了程序编程错误的排查能力还提高了系统的可靠性。

1 概论1.1 电梯国内外现状1.1.1国内现状电梯作为中国对外最早的行业经过多年的发展,电梯产品无论在数量和质量都有了显著的提高,和国外产品差距越来越小。

考虑到经济性,现有国内的电梯控制系统,通常采用微机或可编程逻辑控制器对变频器进行多段速控制。

FPGA的UART完整设计FPGA(现场可编程门阵列)是一种可编程逻辑设备,可以用于实现各种数字系统。

其中一个常见的应用是实现串行通信接口,如UART(通用异步收发器)。

UART是一种用于串行数据传输的通信协议,常用于连接计算机和外部设备(如传感器、显示器等)。

UART通信有两个关键部分:发送和接收。

在FPGA中,我们可以使用电平转换器、计数器和状态机等模块来设计和实现UART。

首先,我们需要设计发送模块。

发送模块的任务是将数据从FPGA发送到外部设备。

以下是发送模块的设计步骤:1.配置串行通信参数:确定波特率、校验位和停止位等参数。

2.设计数据缓冲区:创建一个FIFO(先进先出)缓冲区,用于存储要发送的数据。

3.生成波特率时钟:使用计数器和时钟分频器来生成适当速率的时钟信号。

4.串行化数据:将数据从缓冲区读取,并将其转换为串行比特流。

5.加入校验位和停止位:根据配置的参数,在数据的末尾添加校验位和停止位。

6.发送数据:将串行的比特流发送到外部设备。

接下来,我们需要设计接收模块。

接收模块的任务是从外部设备接收数据并传输到FPGA。

以下是接收模块的设计步骤:1.配置串行通信参数:确定波特率、校验位和停止位等参数,与发送模块保持一致。

2.生成波特率时钟:使用计数器和时钟分频器来生成适当速率的时钟信号。

3.接收数据:从外部设备接收串行比特流。

4.分析校验位和停止位:验证接收到的数据的校验位和停止位是否正确。

5.并行化数据:将串行比特流转换为并行数据,并存储到接收缓冲区中。

6.处理接收到的数据:根据串行通信协议,处理接收到的数据。

在设计中,需要考虑以下事项:1.时钟同步:确保发送端和接收端使用相同的时钟源,并进行合适的时序调整,以保持数据的稳定性和正确性。

2.缓冲区管理:使用FIFO缓冲区来处理发送和接收的数据,以防止数据丢失和冲突。

3.错误处理:根据串行通信协议,实现适当的错误检测和纠正机制,以确保数据的完整性和正确性。

大学fpga课程设计大全一、课程目标知识目标:1. 理解FPGA的基本原理和结构,掌握FPGA设计流程;2. 学习数字电路设计基础,掌握Verilog HDL或VHDL语言;3. 掌握FPGA设计中常用的模块及其功能,如乘法器、除法器、缓存器等;4. 了解FPGA在通信、信号处理、图像处理等领域的应用。

技能目标:1. 能够运用所学知识,独立完成简单的FPGA设计项目;2. 能够分析并优化FPGA设计的性能,提高资源利用率;3. 掌握FPGA设计过程中的调试技巧,解决常见问题;4. 培养团队协作能力,学会与他人共同完成复杂的FPGA设计项目。

情感态度价值观目标:1. 培养学生对FPGA技术的兴趣,激发学习热情;2. 培养学生严谨、细致的学习态度,提高解决问题的能力;3. 增强学生的创新意识,鼓励尝试新方法、新技术;4. 培养学生的团队合作精神,提高沟通与协作能力。

课程性质:本课程为大学电子类、通信类等相关专业高年级学生的专业选修课,旨在帮助学生掌握FPGA设计的基本知识和技能,培养实际工程应用能力。

学生特点:学生具备一定的电子技术基础,对数字电路和编程有一定了解,具有较强的学习能力和动手能力。

教学要求:结合实际应用,注重理论与实践相结合,强化实践操作环节,提高学生的实际工程能力。

通过课程学习,使学生能够达到上述课程目标,为今后从事相关领域工作打下坚实基础。

二、教学内容1. FPGA基本原理与结构:包括FPGA的发展历程、基本组成、工作原理等,对应教材第一章内容。

2. 数字电路设计基础:涵盖数字逻辑、组合逻辑、时序逻辑设计基础,以及Verilog HDL/VHDL语言基础,对应教材第二章内容。

3. FPGA设计流程:介绍FPGA设计流程的各个阶段,包括设计规划、代码编写、仿真验证、综合布局布线、下载配置等,对应教材第三章内容。

4. 常用FPGA模块设计:学习乘法器、除法器、缓存器等模块的设计方法,对应教材第四章内容。

6FPGALX75TFPGA开发方案 FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,能够在硬件布局中实现复杂的数字电路。LX75T FPGA是Xilinx公司推出的一款高性能FPGA芯片,具有广泛的应用领域。本篇文章将简要介绍LX75T FPGA的特点、开发流程以及应用案例。

一、LX75TFPGA的特点 LX75TFPGA是一种面向高度并行应用的FPGA芯片,其主要特点如下: 2.低功耗:LX75TFPGA采用了32纳米工艺制造,功耗得到了有效控制。在低功耗模式下,LX75TFPGA的功耗可以降低到仅为0.95W。

3. 快速开发:LX75T FPGA支持使用VHDL(VHSIC硬件描述语言)或Verilog(硬件描述语言)进行开发,具有丰富的开发工具和资源库。开发者可以使用Xilinx的ISE(Integrated Software Environment)软件,通过图形界面和硬件描述语言进行编程。

二、LX75TFPGA的开发流程 LX75TFPGA的开发流程通常包括以下几个步骤: 1. 开发准备:首先,开发者需要确定目标应用的需求,包括功能、性能等方面的要求。然后,根据需求选择适合的开发平台,如Xilinx的ISE软件。此外,还需要准备硬件开发板、开发文档和相关的开发资源。

2. 设计和仿真:在LX75T FPGA上进行设计之前,开发者需要使用VHDL或Verilog等硬件描述语言进行设计,并通过仿真工具进行验证。开发者可以使用Xilinx公司提供的ModelSim仿真工具,对设计进行功能验证和性能评估。 3. 设计实现:一旦设计和仿真验证通过后,开发者可以使用Xilinx的ISE软件对设计进行实现。ISE软件通过综合、映射和布局布线等步骤,将设计转换为可加载到LX75T FPGA上的位流文件(bitstream)。

4.硬件调试:在将位流文件加载到LX75TFPGA上之后,开发者需要进行硬件调试。调试过程中,开发者可以利用开发板上的各种调试接口和信号分析工具,对设计进行验证和优化。

基于FPGA的数据采集系统设计引言数据采集系统在很多领域中都扮演着重要的角色,例如工业自动化、医疗设备、通信系统等等。

为了提高数据采集系统的性能和可靠性,使用FPGA作为其核心处理器是一个不错的选择。

本文将介绍如何设计一个基于FPGA的数据采集系统,包括架构设计、硬件设计和软件设计等。

一、架构设计一个基于FPGA的数据采集系统的主要架构包括传感器接口、数据处理模块和数据存储模块。

传感器接口负责将传感器的模拟信号转换为数字信号,然后通过数据处理模块进行数据处理和计算,最后将结果存储到数据存储模块中。

在传感器接口模块中,可以选择使用ADC(模数转换器)将模拟信号转换为数字信号。

ADC的选择需要根据采集系统的需求和传感器的特性来确定。

一般而言,高分辨率的ADC可以提高数据采集系统的精度,但会增加系统的复杂度和成本。

数据处理模块可以采用FPGA中的片上处理器(DSP)或使用FPGA的逻辑单元进行数据处理和计算。

使用DSP可以提高系统的处理能力和灵活性,但也会增加功耗和成本。

另一方面,使用FPGA的逻辑单元可以在保证性能的同时降低成本和功耗。

数据存储模块可以选择使用FPGA中的存储器或外部存储器。

FPGA中的存储器速度较快,但容量有限,适合存储少量实时数据。

如果需要存储大量数据,可以选择外部存储器,如SD卡、硬盘等。

二、硬件设计硬件设计是基于FPGA的数据采集系统的关键部分。

首先,需要选择合适的FPGA器件,根据数据采集系统的需求来确定FPGA器件的规格和性能。

其次,需要设计适配器板,将传感器信号接口与FPGA器件连接起来。

适配器板一般包括ADC、放大器、滤波器等电路。

最后,需要设计适配器板和FPGA器件之间的连线,保证信号的稳定和可靠传输。

硬件设计过程中还需要考虑功耗、成本和稳定性等因素。

功耗是一个重要的指标,特别是对于移动设备或电池供电的设备而言。

如何降低功耗是硬件设计中需要重点考虑的问题。

此外,成本也是硬件设计中需要考虑的因素之一,特别是对于大规模的数据采集系统。

FPGA设计的四种常用思想与技巧FPGA(Field-Programmable Gate Array)设计是一种在可编程逻辑器件中实现数字电路的方法。

FPGA设计的目标是实现高性能和可重配置性。

在进行FPGA设计时,有一些常用的思想和技巧可以帮助提高设计效率和性能。

下面将介绍四种常用的FPGA设计思想和技巧。

一、级联式管脚规划级联式管脚规划是一种在FPGA设计中常用的思想和技巧。

FPGA器件通常具有多个I/O管脚,而每个管脚都有特定的功能。

合理地规划管脚可以提高设计的可重用性和可维护性。

一种常用的级联式管脚规划方法是按照功能对管脚进行分组,并将每个功能组的管脚连接到同一位置。

例如,可以将所有时钟信号管脚连接到一个区域,将所有输入信号管脚连接到另一个区域,将所有输出信号管脚连接到另一个区域。

这样做可以使设计更加清晰,方便信号的布线和修改。

二、状态机设计状态机设计是一种常用的FPGA设计思想和技巧。

状态机是一种特殊的数字电路,在FPGA设计中可以用于实现复杂的逻辑控制。

在进行状态机设计时,首先需要确定状态机的状态数和状态转换条件。

然后,可以使用状态图或状态表来描述状态机的行为。

接下来,可以使用具体的硬件描述语言(如VHDL或Verilog)来实现状态机。

状态机设计可以极大地简化控制逻辑的复杂性,提高设计的可读性和维护性。

它还可以实现更高的性能和时序要求。

三、并行处理并行处理是一种常用的FPGA设计思想和技巧。

FPGA器件通常具有多个可并行计算的资源,如DSP(Digital Signal Processor)模块、片上RAM(Random Access Memory)和多路复用器等。

在进行并行处理时,可以使用这些资源来提高设计的性能和吞吐量。

例如,可以使用DSP模块进行乘法运算,使用片上RAM进行数据存储,使用多路复用器实现多路选择等。

并行处理可以充分利用FPGA器件的并行计算能力,提高设计的运算速度和效率。

FPGA设计流程指南前言本部门所承担的FPGA设计任务主要是两方面的作用:系统的原型实现和ASIC的原型验证。

编写本流程的目的是:●在于规范整个设计流程,实现开发的合理性、一致性、高效性。

●形成风格良好和完整的文档。

●实现在FPGA不同厂家之间以及从FPGA到ASIC的顺利移植。

●便于新员工快速掌握本部门FPGA的设计流程。

由于目前所用到的FPGA器件以Altera的为主,所以下面的例子也以Altera为例,工具组合为modelsim + LeonardoSpectrum/FPGACompilerII + Quartus,但原则和方法对于其他厂家和工具也是基本适用的。

目录1. 基于HDL的FPGA设计流程概述 (1)1.1 设计流程图 (1)1.2 关键步骤的实现 (2)1.2.1 功能仿真 (2)1.2.2 逻辑综合 (2)1.2.3 前仿真 (3)1.2.4 布局布线 (3)1.2.5 后仿真(时序仿真) (4)2. Verilog HDL设计 (4)2.1 编程风格(Coding Style)要求 (4)2.1.1 文件 (4)2.1.2 大小写 (5)2.1.3 标识符 (5)2.1.4 参数化设计 (5)2.1.5 空行和空格 (5)2.1.6 对齐和缩进 (5)2.1.7 注释 (5)2.1.8 参考C语言的资料 (5)2.1.9 可视化设计方法 (6)2.2 可综合设计 (6)2.3 设计目录 (6)3. 逻辑仿真 (6)3.1 测试程序(test bench) (7)3.2 使用预编译库 (7)4. 逻辑综合 (8)4.1 逻辑综合的一些原则 (8)4.1.1 关于LeonardoSpectrum (8)4.1.1 大规模设计的综合 (8)4.1.3 必须重视工具产生的警告信息 (8)4.2 调用模块的黑盒子(Black box)方法 (8)参考 (10)修订纪录 (10)1. 基于HDL的FPGA设计流程概述1.1 设计流程图说明:●逻辑仿真器主要指modelsim,Verilog-XL等。

Lattice公司的CrossLink-NX系列是有各种应用的低功耗FPGA,支持各种高带宽传感器和显示器接口,视频处理和机器学习推理.采用低功耗28nm FD-SOI技术,基于Lattice Nexus FPGA平台. CrossLink-NX系列组合了极为灵活的FPGA和低功耗以及高可靠性,提供小型占位面积封装.FPGA支持各种接口包括MIPI D-PHY (CSI-2, DSI), LVDS, SLVS, subLVDS, PCI Express (Gen1, Gen2), SGMII (吉比特以太网)等. CrossLink-NX的处理特性包括多达39K逻辑单元,56个18x18乘法器,2.9Mb嵌入存储器(包括EBR和LRAM区块),分布式存储器,DRAM接口(支持DDR3, DDR3L, LPDDR2和LPDDR3高达1066Mbpsx16数据宽度).CrossLink-NX FPGA还支持快速配置重新配置基于SRAM的逻辑结构和超块配置(低于3ms)可编sysI/O™.用户设计的安全特性包括比特流加密和密码保护.除了FD-SOI技术的高可靠性特性(由于极低的SER),有源可靠性特性包括内置基于帧的SED/SEC和ECC,而内置的ADC可用在系统的监视功能.器件支持高达1.8V VCCIO,支持混合电压1.0 V, 1.2 V, 1.5 V, 1.8 V,高速差分高达1.5Gbps.本文介绍了CrossLink-NX FPGA主要特性, CrossLink-NX-40和CrossLink-NX-17器件简化框图, PFU框图,Slice框图,DSP功能框图以及评估板CrossLink-NX FPGA主要特性,框图,电路图和材料清单.CrossLink™-NX family of low-power FPGAs can be used in a wide range of applications, and are optimized for bridging and processing needs inEmbedded Vision applications – supporting a variety of high bandwidthsensor and display interfaces, video processing and machine learninginferencing. It is built on Lattice Nexus FPGA platform, using low-power 28 nm FD-SOI technology.It combines the extreme flexibility of an FPGA with the low power and high reliability (due to extremely low SER) of FD-SOI technology, and offers small footprint package options.CrossLink-NX supports a variety of interfaces including MIPI D-PHY(CSI-2, DSI), LVDS, SLVS, subLVDS, PCI Express (Gen1, Gen2), SGMII(Gigabit Ethernet), and more. Processing features of CrossLink-NX include up to 39K Logic Cells, 56 18x18 multipliers, 2.9 Mb of embedded memory (consisting of EBR and LRAM blocks), distributed memory, DRAM interfaces (supporting DDR3, DDR3L, LPDDR2, and LPDDR3 up to 1066 Mbps x 16data width).CrossLink-NX FPGAs support fast configuration of its reconfigurableSRAM-based logic fabric, and ultra-fast configuration (in under 3 ms) of its programmable sysI/O™. Security features to secure user designs includebitstream encryption and password protection. In addition to the highreliability inherent to FD-SOI technology (due to its extremely low SER),active reliability features such as built-in frame-based SED/SEC (for SRAM-based logic fabric), and ECC (for EBR and LRAM) are also supported. Built-in ADC is available in each device for system monitoring functions.Lattice Radiant™ design software allows large complex user designs to be efficiently implemented on CrossLink-NX FPGA family.Lattice CrossLink-NX系列低功耗FPGA开发方案Synthesis library support for CrossLink-NX devices is available forpopular logic synthesis tools. Radiant tools use the synthesis tool output along with constraints from its floor planning tools, to place and route the user design in CrossLink-NX device. The tools extract timing from therouting, and back-annotate it into the design for timing verification.Lattice provides many pre-engineered IP (Intellectual Property)modules for CrossLink-NX family. By using these configurable soft IP cores as standardized blocks, you are free to concentrate on the unique aspects of your design, increasing your productivity.Programmable I/O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM Embedded Block RAM (EBR) and rows ofsysDSP Digital Signal Processing blocks, as shown in Figure 2.1. TheCrossLink-NX-40 devices have two rows of DSP blocks and contain three rows of sysMEM EBR blocks. In addition, CrossLink-NX-40 devices includes two Large SRAM blocks. The sysMEM EBR blocks are large, dedicated 18 Kb fast memory blocks and have built-in ECC and FIFO support. EachsysMEM block can be configured to a single, pseudo dual or true dual port memory in a variety of depths and widths as RAM or ROM. Each DSP block supports variety of multiplier, adder configurations with one 108-bit or two 54-bit accumulators supported, which are the building blocks for complex signal processing capabilities.Each PIC block encompasses two PIO (PIO pairs) with their respective sysI/O buffers.The sysI/O buffers of the CrossLink-NX devices are arranged in seven banks allowing the implementation of a wide variety of I/O standards. The Wide Range (WR) I/O banks that are located in the top, left and right sides of the device provide flexible ranges of general purpose I/O configurations up to 3.3 V VCCIOs. The banks located in the bottom side of the device are dedicated to High Performance (HP) interfaces such as LVDS, MIPI, DDR3, LPDDR2, and LPDDR3 supporting up to 1.8 V VCCIOs.The Programmable Functional Unit (PFU) contains the building blocks for logic, arithmetic, RAM and ROM functions. The PFU block is optimized for flexibility, allowing complex designs to be implemented quickly andefficiently. Logic Blocks are arranged in a two-dimensional array. Theregisters in PFU and sysI/O blocks in CrossLink-NX devices can beconfigured to be SET or RESET. After power up and the device isconfigured, it enters into user mode with these registers SET/RESETaccording to the configuration setting, allowing the device entering to aknown state for predictable system function. In addition, CrossLink-NX-40 devices provide various system level hard IP functional and interface blocks such as PCIe, D-PHY, I2C, SGMII/CDR, and ADC blocks. PCIe hard IPsupports PCIe 2.0 and D-PHY supports up to 2.5 Gbps per lane. CrossLink-NX devices also provide security features to help secure user designs and deliver more robust reliability features to the user designs by usingenhanced frame-based SED/SEC functions.Other blocks provided include PLLs, DLLs, and configuration functions. The PLL and DLL blocks are located at the corners of each device.CrossLink-NX devices also include Lattice Memory Mapped Interface(LMMI) which is a Lattice standardized interface for simple read and write operations to support controlling internal IPs.Every device in the family has a JTAG port. This family also provides an on-chip oscillator and soft error detect capability. The CrossLink-NXdevices use 1.0 V as their core voltage.CrossLink-NX FPGA主要特性:· Programmable Architecture· 17K to 39K logic cells· 24 to 56 18 x 18 multipliers (in sysDSP™ blocks)· 2.5 to 2.9 Mb of embedded memory blocks (EBR, LRAM)· 36 to 192 programmable sysI/O (High Performance and Wide Range I/O)· MIPI D-PHY· Up to two hardened 4-lane MIPI D-PHY interfaces· Up to eight lanes total· Transmit or receive· Supports CSI-2, DSI· 20 Gbps aggregate bandwidth· 2.5 Gbps per lane, 10 Gbps per D-PHY interface · Additional Soft D-PHY interfaces supported by High Performance (HP)sysI/O· Transmit or receive· Supports CSI-2, DSI· Up to 1.5 Gbps per lane· Programmable sysI/O supports wide variety of interfaces· High Performance (HP) on bottom I/O dual rank· Supports up to 1.8 V VCCIO· Mixed voltage support (1.0 V, 1.2 V, 1.5 V, 1.8 V)· High-speed differential up to 1.5 Gbps· Supports soft D-PHY (Tx/Rx), LVDS 7:1 (Tx/Rx), SLVS (Tx/Rx), subLVDS (Rx)· Supports SGMII (Gb Ethernet) – 2 channels (Tx/Rx) at 1.25 Gbps· Dedicated DDR3/DDR3L and LPDDR2/LPDDR3 memory support with DQS logic, up to 1066 Mbps data-rate and x16 data-width· Wide Range (WR) on Left, Right and Top I/O Banks· Supports up to 3.3 V VCCIO· Mixed voltage support (1.2 V, 1.5 V, 1.8 V, 2.5 V, 3.3 V)· Programmable slew rate (slow, med, fast)· Controlled impedance mode· Emulated LVDS support· Hot-socketing· Power Modes – Low Power versus High-Performance· User selectable· Low-Power mode for power and/or thermal challenges· High-Performance mode for faster processing· Small footprint package options· 4 x 4 mm2 to 10 x 10 mm2 package options· 2x SGMII CDR at up to 1.25 Gbps – to support 2 channels SGMII using HP I/O· CDR for RX· 8b/10b decoding· Independent Loss of Lock (LOL) detector for each CDR block· sysCLOCK™ analog PLLs· Three in 39K LC and two in 17K LC device· Six outputs per PLL· Fractional N· Programmable and dynamic phase control· sysDSP Enhanced DSP blocks· Hardened pre-adder· Dynamic Shift for AI/ML support· Four 18 x 18, eight 9 x 9, two 18 x 36, or 36 x 36· Advanced 18 x 36, two 18 x 18, or four 8 x 8 MAC· Flexible memory resources· Up to 1.5 Mb sysMEM™ Embedded Block RAM (EBR)· Programmable width· ECC/FIFO· 80k to 240k bits distributed RAM· Large RAM Blocks· 0.5 Mbits per block· Up to five blocks (2.5 Mb total) per device· SERDES – PCIe Gen2 x1 channel (Tx/Rx) hard IP in 39K LC device · Hard IP supports· Gen1, Gen2, Multi-Function, End Point, Root Complex· APB control bus· AHB-Lite for data bus· Internal bus interface support· APB control bus· AHB-Lite for data bus· AXI4-streaming· Configuration – Fast, Secure· SPI – x1, x2, x4 up to 150 MHz· Master and Slave SPI support· JTAG· I2C and I3C· Ultrafast I/O configuration for instant-on support· Less than 15 ms full device configuration for LIFCL-40· Bitstream Security · Encryption· Cryptographic engine· Bitstream encryption – using AES-256· Bitstream authentication – using ECDSA · Hashing algorithms – SHA, HMAC · True Random Number Generator · AES 128/256 Encryption· Single Event Upset (SEU) Mitigation Support· Extremely low Soft Error Rate (SER) due to FD-SOI technology · Soft Error Detect – Embedded hard macro· Soft Error Correction – Without stopping user operation· Soft Error Injection – Emulate SEU event to debug system error handling · ADC – 1 MSPS, 12-bit SAR · 2 ADCs per device· 3 Continuous-time Comparators · Simultaneous sampling · System Level Support· IEEE 1149.1 and IEEE 1532 compliant · Reveal Logic Analyzer· On-chip oscillator for initialization and general use · 1.0 V core power supplyCrossLink-NX FPGA 系列产品:图1.CrossLink-NX FPGA 系列简化框图:CrossLink-NX-40器件图2.CrossLink-NX FPGA系列简化框图:CrossLink-NX-17器件图4.CrossLink-NX FPGA系列Slice框图图3.CrossLink-NX FPGA系列PFU框图图5.CrossLink-NX FPGA 系列时钟框图图6.CrossLink-NX FPGA 系列DSP 功能框图。

基于FPGA的函数信号发生器设计函数信号发生器是一种能够产生不同类型信号的测试设备,通常在电子电路实验中使用。

基于FPGA的函数信号发生器设计利用可编程逻辑器件FPGA,可以实现更高的灵活性和可定制性,同时减少了硬件开发成本。

本文将详细介绍基于FPGA的函数信号发生器的设计原理、主要模块和实现方法。

一、设计原理二、主要模块1.时钟生成器模块:时钟信号是产生各种信号波形的基础,因此需要设计一个时钟生成器模块来产生稳定的时钟信号。

可以使用FPGA内部的锁相环(PLL)或计数器来实现。

2.波形选择模块:为了产生不同类型的信号波形,需要设计一个波形选择模块。

通过该模块,用户可以选择所需的信号波形,如正弦波、方波、三角波等。

3. 波形生成模块:根据用户的选择,使用FPGA内部的逻辑门电路来实现不同类型的信号波形的生成。

可以利用查找表(Look-Up Table,简称LUT)来存储不同波形的采样点数据,并通过控制逻辑将这些数据输出为相应的信号波形。

4.频率控制模块:通过频率控制模块,可以对信号波形的频率进行控制。

可以根据用户的输入,通过改变时钟信号的频率或改变波形采样点的间隔来实现频率的调节。

5.幅值控制模块:通过幅值控制模块,可以对信号波形的幅值进行控制。

可以通过改变逻辑门的阈值电压或者改变DAC(数字模拟转换器)的输出电平来实现幅值的调节。

三、实现方法2.硬件设计:根据设计需求,选择合适的FPGA芯片、外部时钟源、AD/DA转换器等外部器件。

根据电路原理图,进行相应的电路布局和连线。

在确认电路无误后,进行焊接和组装工作。

在软件和硬件设计完成后,可以通过控制板上的按钮、旋钮等输入设备来调节信号波形的频率、幅值等参数,从而实现不同类型的信号波形的生成。

总结:基于FPGA的函数信号发生器设计利用FPGA的可编程特性,可以实现信号波形的灵活生成和控制。

通过设计合适的模块,可以产生多种类型的信号波形,并对其频率、幅值等参数进行调节。

基于fpga的毕业设计题目FPGA全称为Field-Programmable Gate Array,是一种基于实现了数百万个门电路的可编程逻辑器件,可用于实现各种数字电路功能。

FPGA对于毕业设计来说是一种非常优秀的选择,笔者将在下面的文章中介绍一种基于FPGA的毕业设计题目,并分步骤阐述其实现过程。

题目:基于FPGA的音乐舞台灯光控制器设计思路:1. 功能设计:本设计的主要功能是通过FPGA控制LED灯光的颜色、亮度和闪烁效果,同时控制舞台上与音乐的节拍相同的灯光变化。

因此,该设计需要实现音频采集、音乐分析、音乐控制灯光、舞台灯光控制等多种功能。

2. 硬件设计:本设计需要FPGA、音频采集模块、灯光控制模块等硬件部分。

其中,音频采集模块使用声卡购买或自行制作,灯光控制模块可以使用MOS管或者二极管。

FPGA需要选择性价比高的型号,同时需要考虑IO口资源的数量,以便控制舞台上的灯光。

3. 软件设计:软件部分需要进行音频采集、音乐分析、灯光控制数据的处理和传输等方面的编程设计。

软件设计中需要选择选用VHDL或Verilog进行FPGA的开发与调试,使用相关的软件工具进行音乐分析的预处理与处理,使用Verilog-HDL的设计软件Quartus进行核心程序的实现。

具体实现:1. 音频采集部分:如前所述,可以通过声卡购买或自行制作。

采集到音频信号后,将其从声卡中解码出数字信号,并通过DSP的处理,提取出所需要的信号数据,如采样率,频率等。

2. 音乐分析:在采集完音频信号后,需要进行预处理。

理论上,音乐的频谱在FFT变换后得到会随时间在一个平面内移动。

因此,可以在FFT之后得到一个时间和频率坐标系的数据。

然后再选择想要控制的频率区间,提取信号数据,如频率、振幅等作为控制灯光的参考源。

3. 灯光控制:基于分析得到的音乐信号,将其作为变化引擎进行舞台灯光的控制。

将选定的信号参考源输入到SPİ输出,连接到控制器的输入通道,对应输出通道连接的相应亮度与闪烁相应的MOS管。

精品 welcome FPGA课程设计 题目:全天候温度纪录仪的设计与FPGA实现

姓名: 学号: 院系:信息科学与工程学院 专业: 计算机技术 精品

welcome 摘要

本设计有效的克服了传统的数字温度计的缺点,采用自上而下的设计思路,绘制出了系统结构流程图,最后又在硬件上通过对其进行调试和验证。基于FPGA在Quartus II13.0软件下应用Verilog HDL语言编写程序,采用ALTRA公司Cyclone- IV系列的EP4CE40F23I7 芯片进行了计算机仿真,并给出了相应的仿真结果。该电路能够实现很好的测温功能。

关键字:数字温度计;FPGA;Quartus II130.;Verilog HDL;EP4CE40F2317

Abstract This design effectively overcomes the traditional digital thermometer’s weaknesses and takes a top-down approach to design flow chart of system, and finally pass the circuits to the hardware to debug and verify it. This design is based on FPGA using Verilog HDL language to write program in Quartus II software, adopting EP4CE40F23I7 chip of Cyclone- IV series of ALTRA company for computer simulation and at the same time showing the corresponding simulation result. This circuit is able to carry out excellent temperature- measurement function.

KeyWords: Digital thermometer; FPGA; Quartus II 13.0;Verilog HDL;EP4CE40F2317 精品

welcome 目录

一、 设计要求 ............................................................................................................................ 1 1.1 设计题目 ......................................................................................................................... 1 1.2 选题背景 ......................................................................................................................... 1 1.3 设计要求: ..................................................................................................................... 1 二、 系统设计 ............................................................................................................................ 2 2.1 系统设计图 ..................................................................................................................... 2 2.2 系统设计说明 ................................................................................................................. 2 三、 硬件设计 ............................................................................................................................ 3 3.1 FPGA简介 ...................................................................................................................... 3 3.2 LCD1602液晶显示 ...................................................................................................... 5 3.3 DS18B20温度传感器 .................................................................................................. 7 3.4 AT24C02读写模块 ...................................................................................................... 9 3.5 按键模块设计 ................................................................................................................. 12 四、 软件设计 .......................................................................................................................... 12 4.1 Quartus II软件介绍 ................................................................................................... 12 4.2 系统架构图 ................................................................................................................... 13 4.3 系统控制器 ................................................................................................................... 13 4.4 系统调试 ....................................................................................................................... 14 精品 welcome 五、 代码附录 .......................................................................................................................... 15 5.1 顶层模块 ....................................................................................................................... 15 5.2 LCD驱动部分代码 ...................................................................................................... 18 5.3 DS18B20驱动模块 .................................................................................................... 21 精品

welcome 全天候温度纪录仪的设计与FPGA实现

一、 设计相关 1.1 设计题目 全天候温度纪录仪的设计与FPGA实现 1.2 选题背景 当今电子产品正向功能多元化,体积最小化,功耗最低化的方向发展。它与传统的电子产品在设计上的显著区别是大量使用大规模可编程逻辑器件,使产品的性能提高,体积缩小,功耗降低同时广泛运用现代计算机技术,提高产品的自动化程度和竞争力,缩短研发周期。FPGA开发技术正是为了适应现代电子技术的要求,吸收众多学科最新科技成果而形成的一门新技术。基于Verilog HDL语言的设计开发更是灵活多变,容易上手,方便开发人员开发新产品。 时代在发展,人们的物质生活水平在不断提高,新产品、新技术层出不穷,电子技术的发展更是日新月异。可以毫不夸张的说,电子技术的应用无处不在,电子技术正在不断地改变我们的生活,改变着我们的世界。一个方便实用的温度计对于大众来说更是生活中不可或缺的一件产品。 美国ALTERA公司的可编程逻辑器件采用全新的结构和先进的技术,加上最新的QUARTUS开发环境,更具有高性能,开发周期短等特点,十分方便进行电子产品的开发和设计本节将从FPGA嵌入式应用开发技术与温度计发展的客观实际出发,通过对该技术发展状况的了解,以及课题本身的需要,指出研究基于FPGA的芯片系统与设计——全天候温度记录仪的设计与实现的必要性。