单片机原理及接口技术课后习题第10章 答案

- 格式:doc

- 大小:264.00 KB

- 文档页数:15

第十章复习思考题答案

1. 与并行扩展方法相比,串行总线扩展方法有哪些优点?

与并行扩展方法相比,串行总线扩展传输连线少,可以使应用系统的硬件设计简化;串行总线的故障自诊断和调试也更为简单。

2. 在I2C总线中,主机和从机是如何确定的?它们在总线工作时起什么作用?

I2C总线是一个多主机总线,即总线上可以有一个或多个主机(或称主控制器件),总线运行由主机控制。主机是指启动数据的传送(发启动状态)、发出时钟信号、发出终止信号的器件。通常,主机由单片机或其它微处理器担任。被主机访问的器件叫从机,它可以是其它单片机或外围芯片,如:A/D、D/A、LED或LCD驱动、串行存储器芯片。

3. 在I2C总线主从系统中,S状态和P状态是由哪一方发出的?它们的作用是什么?

S状态和状态P是由主机发出的。在总线上出现S状态后,标志着总线处于“忙”状态。如果总线上出现P状态时,在该状态出现一段时间后,总线处于“闲”状态。

4. 简述I2C总线的数据传输过程。

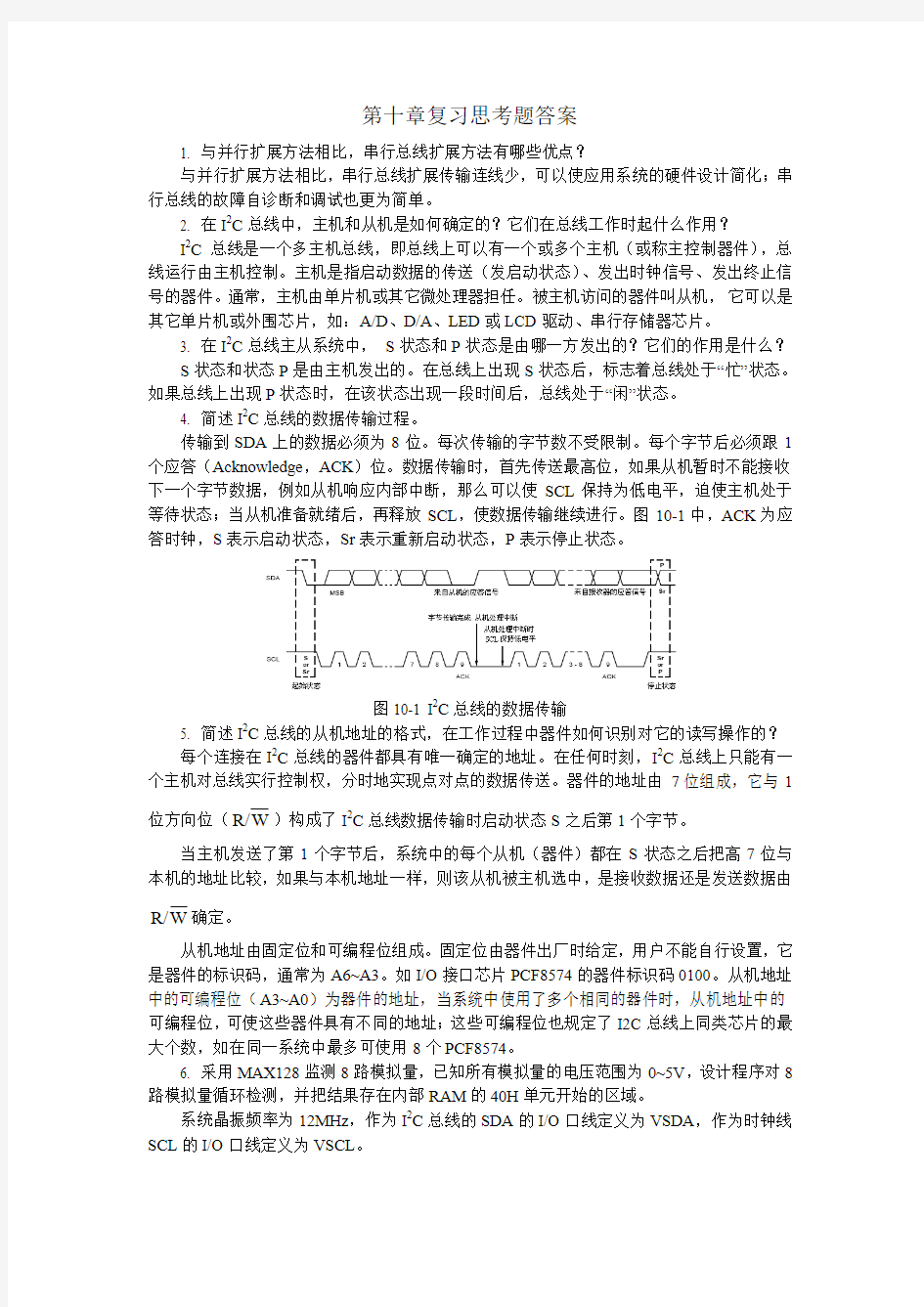

传输到SDA上的数据必须为8位。每次传输的字节数不受限制。每个字节后必须跟1个应答(Acknowledge,ACK)位。数据传输时,首先传送最高位,如果从机暂时不能接收下一个字节数据,例如从机响应内部中断,那么可以使SCL保持为低电平,迫使主机处于等待状态;当从机准备就绪后,再释放SCL,使数据传输继续进行。图10-1中,ACK为应答时钟,S表示启动状态,Sr表示重新启动状态,P表示停止状态。

图10-1 I2C总线的数据传输

5. 简述I2C总线的从机地址的格式,在工作过程中器件如何识别对它的读写操作的?

每个连接在I2C总线的器件都具有唯一确定的地址。在任何时刻,I2C总线上只能有一个主机对总线实行控制权,分时地实现点对点的数据传送。器件的地址由7位组成,它与1

R/)构成了I2C总线数据传输时启动状态S之后第1个字节。

位方向位(W

当主机发送了第1个字节后,系统中的每个从机(器件)都在S状态之后把高7位与本机的地址比较,如果与本机地址一样,则该从机被主机选中,是接收数据还是发送数据由R/确定。

W

从机地址由固定位和可编程位组成。固定位由器件出厂时给定,用户不能自行设置,它是器件的标识码,通常为A6~A3。如I/O接口芯片PCF8574的器件标识码0100。从机地址中的可编程位(A3~A0)为器件的地址,当系统中使用了多个相同的器件时,从机地址中的可编程位,可使这些器件具有不同的地址;这些可编程位也规定了I2C总线上同类芯片的最大个数,如在同一系统中最多可使用8个PCF8574。

6. 采用MAX128监测8路模拟量,已知所有模拟量的电压范围为0~5V,设计程序对8路模拟量循环检测,并把结果存在内部RAM的40H单元开始的区域。

系统晶振频率为12MHz,作为I2C总线的SDA的I/O口线定义为VSDA,作为时钟线SCL的I/O口线定义为VSCL。

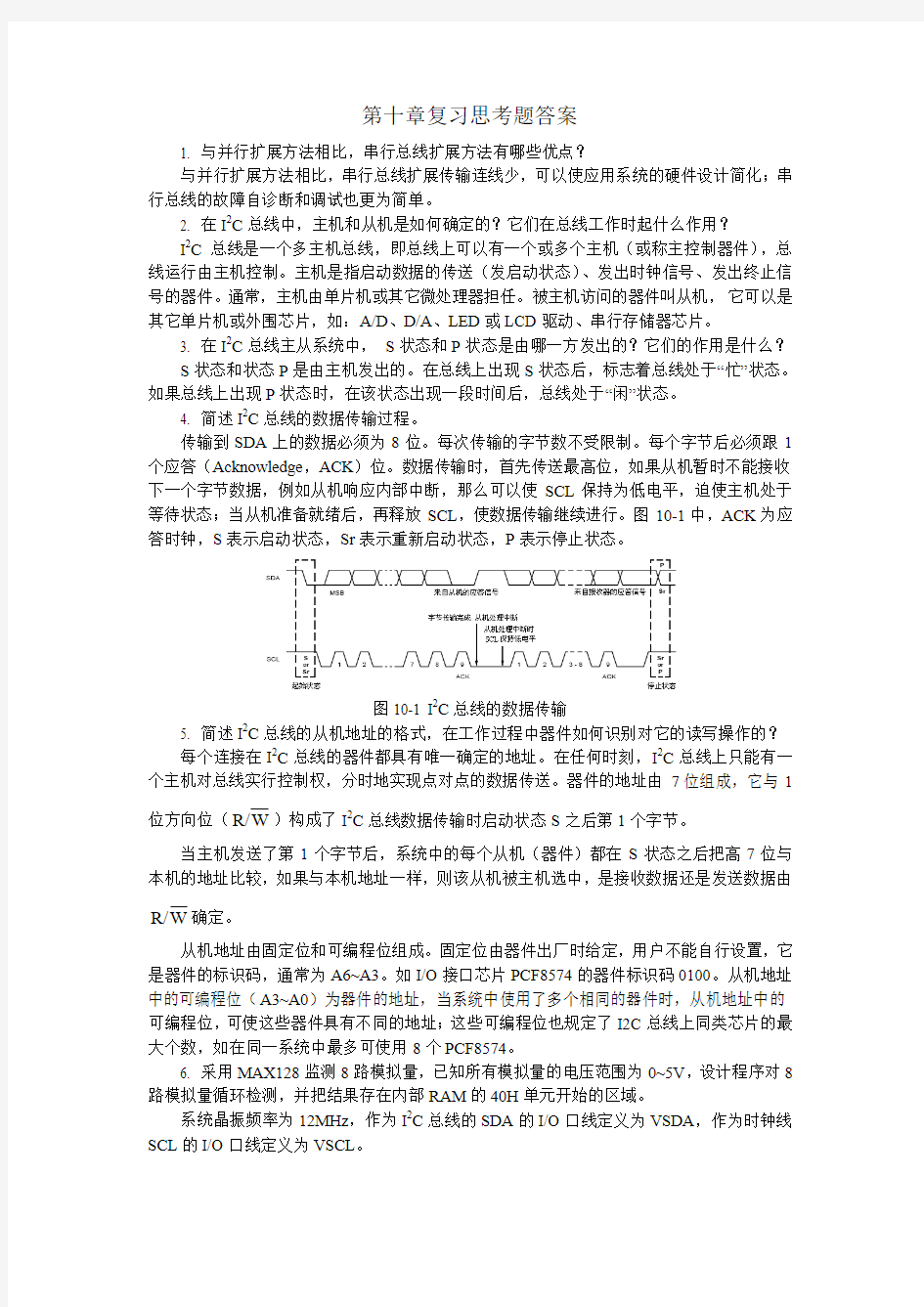

程序流程图:

图10-2 程序流程图汇编源代码:(部分子程序为参见教材)

VSDA BIT P1.6 ;定义虚拟I2C总线数据线端口VSCL BIT P1.7 ;定义虚拟I2C总线时钟线端口CHN EQU 50H

ORG 0000H

JMP MAIN

ORG 0030H

MAIN:

MOV R3,#8

MOV R1,#40H

MOV CHN,#0

AD_LOOP:

LCALL MAX128_READ

LCALL DELAY100MS

INC CHN

DJNZ R3,AD_LOOP

JMP MAIN

MAX128_READ:

LCALL STAT

MOV A,#01010000B ;器件地址,写操作

LCALL WRBYT ;写入一个字节

LCALL CACK ;检查应答位

JB F0,$

MOV A,CHN

SWAP A

ANL A,#01110000B

ORL A,#10001000B ;控制字节,CHN通道

LCALL WRBYT ;写入一个字节

LCALL CACK ;检查应答位

JB F0,$

LCALL STOP

LCALL DELAY100MS

LCALL STAT

MOV A,#01010001B ;器件地址,读操作

LCALL WRBYT ;写入一个字节

LCALL CACK ;检查应答位

JB F0,$

LCALL DELAY10MS ;延时10ms 转换时间

LCALL RDBYT ;读取一个字节

MOV @R1,A ;存放高字节

INC R1

LCALL MACK ;发送应答标志位

LCALL RDBYT ;读取一个字节

ANL A,#0F0H

MOV @R1,A ;存放低字节

INC R1

LCALL MNACK ;发送非应答位/数据

LCALL STOP ;发送结束IIC信号

RET

7. 单片机应用系统采用MAX128作为A/D转换器,现要求每隔50ms对CH6通道采样一次,并把采样值存在R6和R7中。

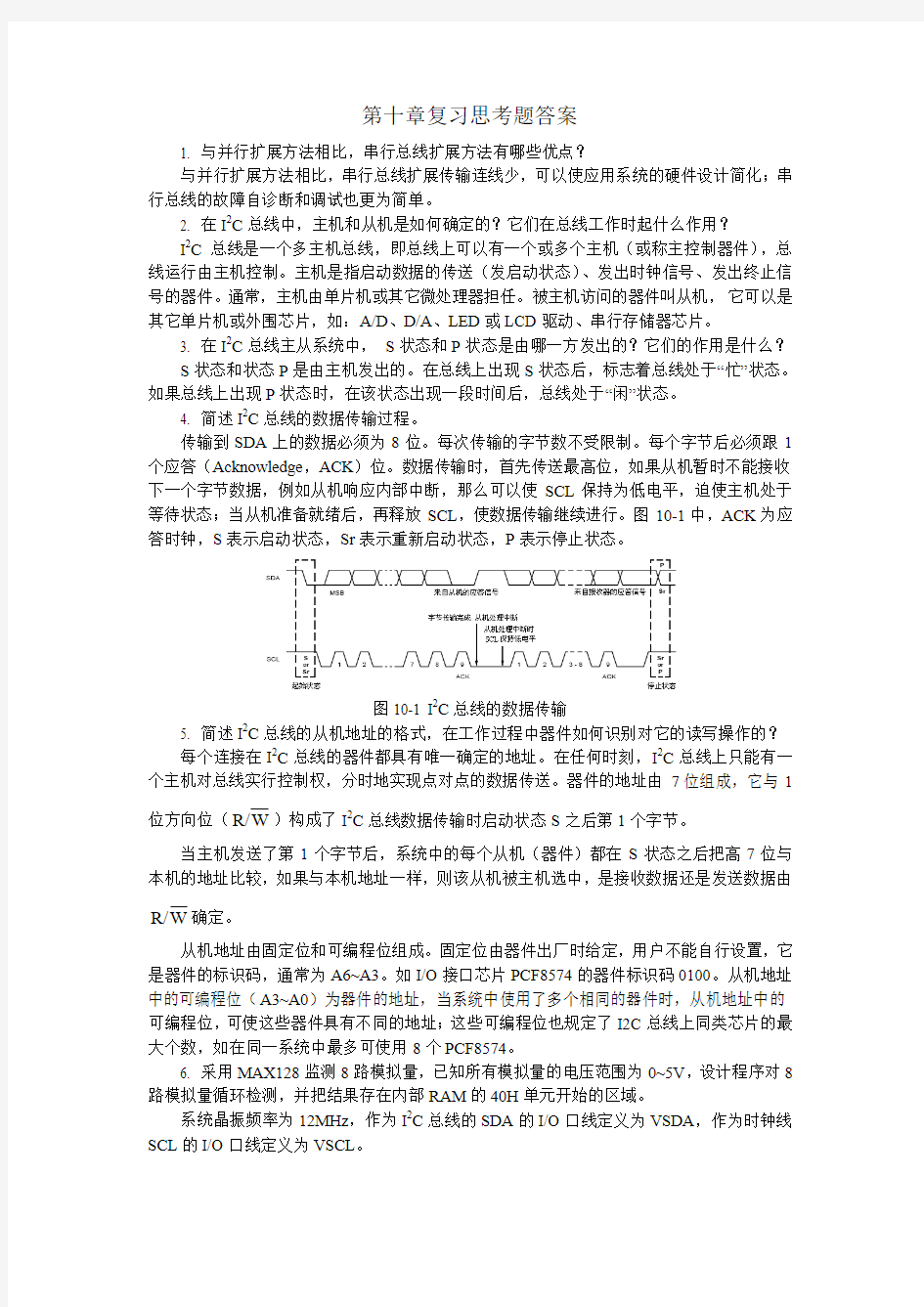

设系统晶振频率为12MHz,作为I2C总线的SDA的I/O口线定义为VSDA,作为时钟线SCL的I/O口线定义为VSCL。程序流程图如图图10-3所示。

图10-3程序流程图汇编源代码:(部分子程序为参见教材)

VSDA BIT P1.6 ;定义虚拟I2C总线数据线端口VSCL BIT P1.7 ;定义虚拟I2C总线时钟线端口ORG 0000H

JMP MAIN

ORG 0030H

MAIN:

LCALL MAX128_READ

LCALL DELAY50MS ;延时50MS

JMP MAIN

MAX128_READ:

LCALL STAT

MOV A,#01010000B ;器件地址,写操作

LCALL WRBYT ;写入一个字节

LCALL CACK ;检查应答位

JB F0,$

MOV A,#11101000B ;控制字节,6通道

LCALL WRBYT ;写入一个字节

LCALL CACK ;检查应答位

JB F0,$

LCALL STOP

LCALL DELAY10MS

LCALL STAT

MOV A,#01010001B ;器件地址,读操作

LCALL WRBYT ;写入一个字节

LCALL CACK ;检查应答位

JB F0,$

LCALL DELAY10MS ;延时10ms 转换时间