触摸按键设计指导V1.0.1

- 格式:pdf

- 大小:623.24 KB

- 文档页数:9

触摸按键设计指导V1.0 1.触摸按键原理图设计

1.1 BF6910/11ASXX系列触摸按键芯片应用电路

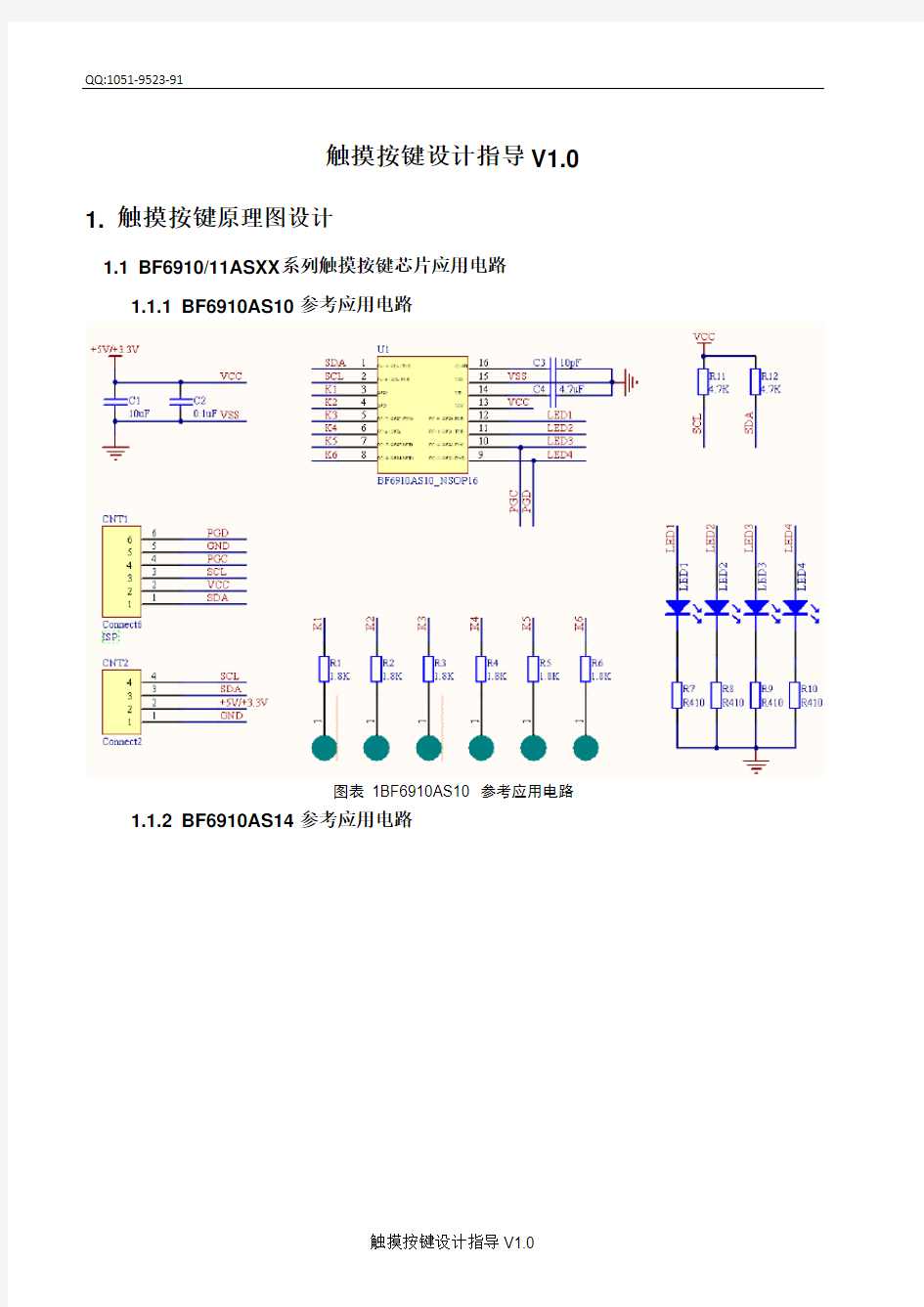

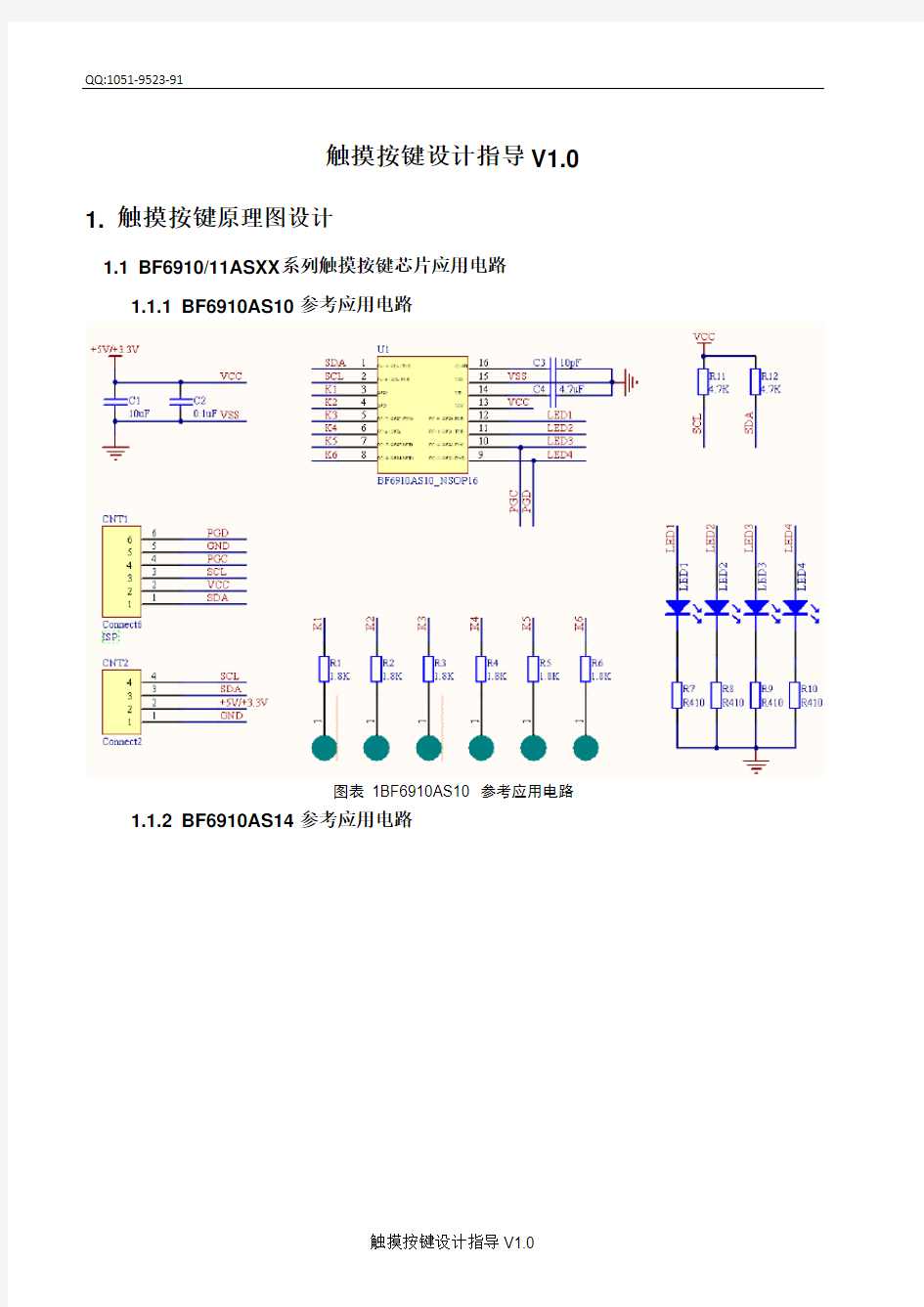

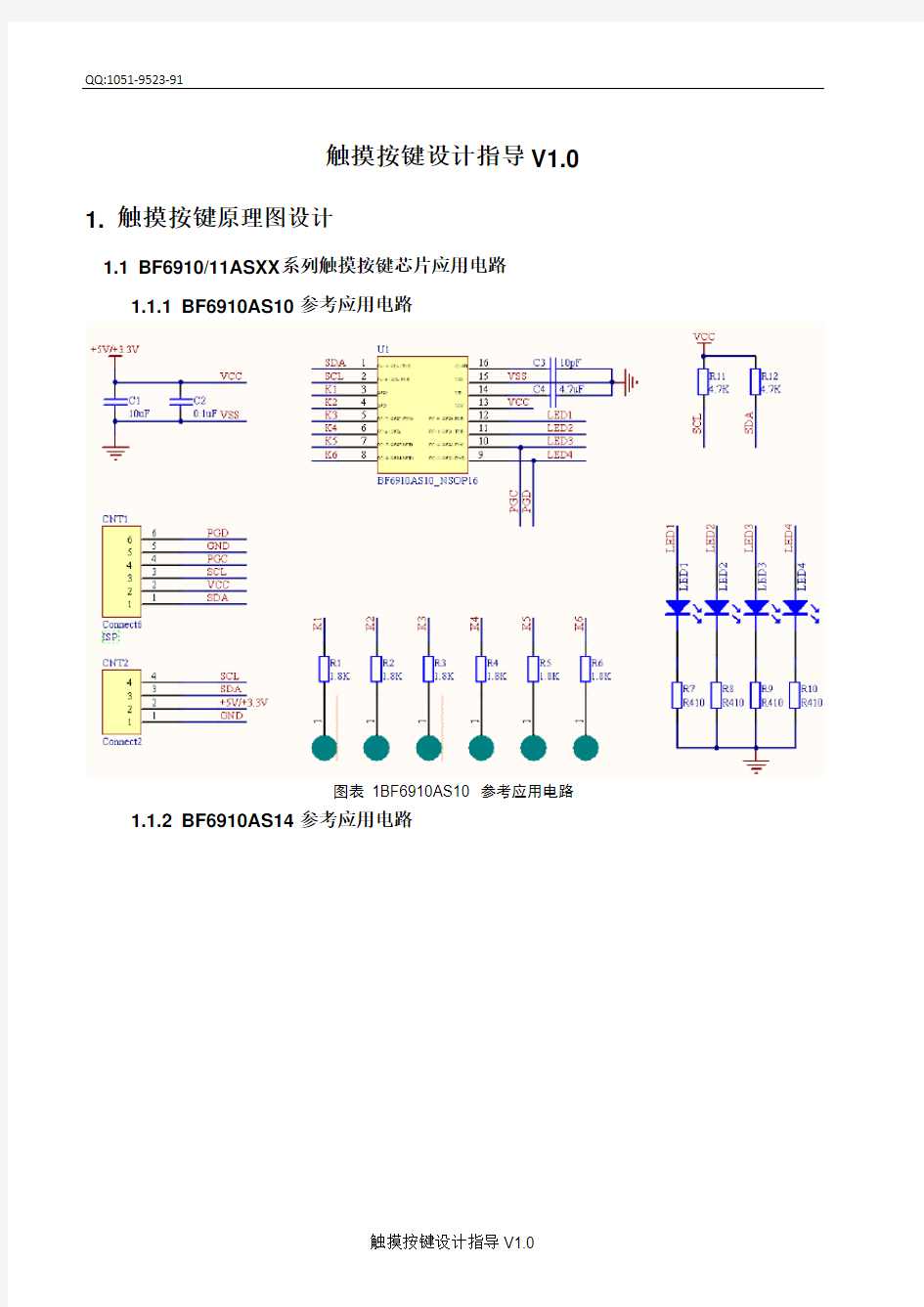

1.1.1 BF6910AS10 参考应用电路

图表1BF6910AS10 参考应用电路

1.1.2 BF6910AS14 参考应用电路

图2 BF6910AS14 应用电路1.1.3 BF6911AQ22参考应用电路

图3 BF6911AQ22 参考应用电路1.1.4 BF6911AS22参考应用电路

图4 BF6911AS22 参考应用电路

2.PCB Layout设计

2.1 PCB布局

1.触摸通道与触控芯片、其它元件布局在不同的层。

2.触摸通道电阻尽量靠近芯片。

3.芯片大小滤波电容靠近芯片放置。

4.预留测试接口,以方便调试。

2.2 走线:

1. 尽量把触摸通道走线放在底层,触摸通道在顶层。

2. 触摸通道、触摸通道走线与铺地之间的间距至少30mil。

3. 不要把触摸通道走线布置在触摸通道下面。

4. 触摸通道走线间距应当至少是触摸通道走线宽度的两倍。

5. 时钟、数据或周期信号走线都不应该与触摸通道走线相邻平行布设。这些信号线应当尽可能

地与触摸通道走线垂直,或者布设在PCB的其他区域。如果时钟、数据或任何周期信号走线确实需要与触摸的信号走线平行布设,它们应当被布设在不同的层并且不能重叠,而且应当尽可能地缩短信号线平行部分的长度。

6.电源走线,触摸芯片最好用一根独立的走线从板子的供电点取电,不要和其他的电路(如LED

回路)共用电源回路。触摸IC的供电从滤波电路输入,保持VDD与VSS并行,输入路径短而粗(40mil 左右)。

7.采用星形接地,触摸芯片的地线不要和其他电路共用,应该单独连到板子电源输入的接地点,

也就是通常说的采用“星形接地”。

8.单面板走线,如果采用单面PCB板,并用弹簧或其它导电物体做感应通道,感应通道到触控IC

引脚的连线不走或少走跳线。

9.Sensor走线长度:或,这样可以减少来自射频的干扰。

10.Sensor通道电阻:500Ω~2K,起衰减共振作用。

2.3 铺地:

1.空白的地方可以网格铺地(线宽6mil、网格大小为30mil)。

2.触摸通道正对背面稍大些面积不要铺地,如果需要在比较潮湿的环境工作时,触摸通道所在

层不要铺地。

3.为降低串扰,应当尽可能地增大两个触摸通道之间的间距以及触摸通道与触摸通道走线之间

的距离。在可能的情况下,在两个触摸通道之间铺地、触摸通道走线之间加入铺地。

4.铺地被用来填充PCB的空白区域,铺地能够帮助触摸模块屏蔽外部噪声源,还能够稳定触摸线路的固有电容。然而,使用铺地时需要事先要注意,铺地会增加触摸的固有电容,还会增加由于水滴导致的误触的可能性。

5.建议使用网状的铺地,而非实心的铺地,建议使用网状铺地(线宽度为6mil,网格尺寸为30mil),铺地的角度应设置为45度。

6.触摸通道到铺地之间的间距应当至少为0.75mm(30mil)。

8.如果对覆盖板使用部分导电材料(不能整片的覆盖按键),建议不要在顶层布设铺地。

2.4其它:

良好的PCB设计和布局,能够使电容感应应用更加可靠。在PCB设计中,还要考虑其他的重要因素,包括以下几方面:

1.PCB上无浮地,PCB的空白区域可铺地或留空。

2.触摸按键表面要加上阻焊油,以防长时间暴露在空气中被氧化。

3.如果按键的位置靠近PCB边缘,最好在按键周围用地线将按键围住,以防从侧面引入的干扰。

4.触摸通道上方是否有导电材质,如有需要接地,触摸按键部分上方不能有导电材质。

5.在触控IC的 SDA、SCL线路中串联(10~100 )电阻,SDA、SCL接10pF左右的电容到地,以便过滤连接主板和触摸模块的走线所引起的噪声干扰,或来自可能导致IIC信号失真的电源噪声的干扰。

6. PCB layout时一定避免电源或者地线形成闭合环路或回路,此时会引入很大的干扰,系统抗干扰性非常差。

7. 触摸按键覆盖物一般采用ABS、亚克力、玻璃等非导电材料作为面板材料。

8. 触摸按键与触摸按键上方的面板要保证良好的粘合度,不能有空气间隙,建议采3M等不导电胶进行粘合。

2.5PCB Layout 实例:

图表 5 Top Layer

图表 6 Bottom Layer

图表7 Top Layer

图表8 Bottom Layer 3.附录:

3.1芯片型号:

3.2常见材料介电常数: