等精度数字频率计设计

- 格式:pdf

- 大小:2.45 MB

- 文档页数:18

等精度数字频率计测量方法:一、测频原理所谓“频率”,就是周期性信号在单位时间变化的次数。

电子计数器是严格按照f=N/T的定义进行测频,其对应的测频原理方框图和工作时间波形如图1 所示。

从图中可以看出测量过程:输入待测信号经过脉冲形成电路形成计数的窄脉冲,时基信号发生器产生计数闸门信号,待测信号通过闸门进入计数器计数,即可得到其频率。

若闸门开启时间为T、待测信号频率为fx,在闸门时间T内计数器计数值为N,则待测频率为:fx = N/T若假设闸门时间为1s,计数器的值为1000,则待测信号频率应为1000Hz或1.000kHz,此时,测频分辨力为1Hz。

图1 测频原理框图和时间波形二、方案设计2.1总体方案设计等频率计测频范围1Hz~100MHz,测频全域相对误差恒为百万分之一,故由此系统设计提供100MHz作为标准信号输入,被测信号从tclk端输入,由闸门控制模块进行自动调节测试频率的大小所需要的闸门时间,这样可以精确的测试到被测的频率,不会因闸门开启的时间快慢与被测频率信号变化快慢而影响被测频率信号导致误差过大,被测信号输入闸门控制模块后,在闸门控制模块开始工作时使encnt端口输出有效电平,encnt有效电平作用下使能标准计数模块(cnt模块)和被测计数模块(cnt模块),计数模块开始计数,直到encnt 重新回到无效电平,计数模块就将所计的数据送到下一级寄存模块,在总控制模块的作用下,将数据进行load(锁存),然后寄存器里的数据会自动将数据送到下一模块进行数据处理,最后送到数码管或者液晶显示屏(1602)进行被测信号的数据显示。

闸门、计数、寄存的总控制模块2.2理论分析采用等精度测量法,其测量原理时序如图1所示从图1中可以得到闸门时间不是固定的值,而是被测信号的整周期的倍数,即与被测信号同步,因而,不存在对被测信号计数的±1 误差,可得到:变形后可得:对上式进行微分,可得:由于 dn=± 1 ,因而可推出:从式(5)可以看出:测量误差与被测信号频率无关,从而实现了被测频带的等精度测量;增大T或提高fs可以提高测量精度;标准频率误差为dfs/fs,因为晶体的稳定度很高,再加上FPGA核心芯片里集成有PLL锁相环可对频率进一步的稳定,标准频率的误差可以进行校准,校准后的标准误差便可以忽略。

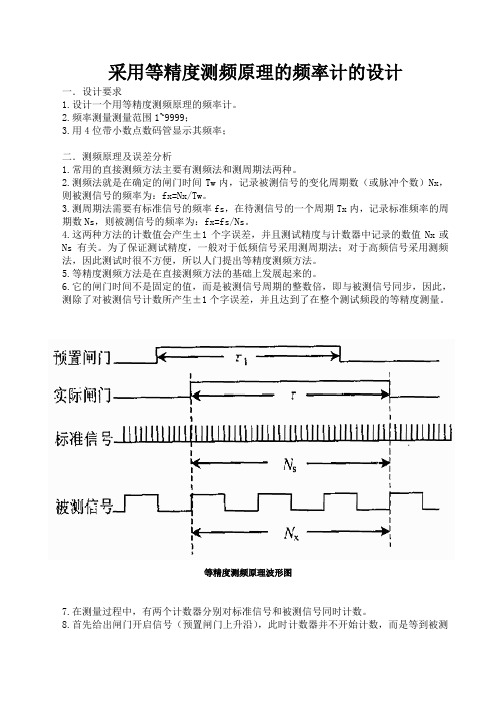

采用等精度测频原理的频率计的设计一.设计要求1.设计一个用等精度测频原理的频率计。

2.频率测量测量范围1~9999;3.用4位带小数点数码管显示其频率;二.测频原理及误差分析1.常用的直接测频方法主要有测频法和测周期法两种。

2.测频法就是在确定的闸门时间Tw内,记录被测信号的变化周期数(或脉冲个数)Nx,则被测信号的频率为:fx=Nx/Tw。

3.测周期法需要有标准信号的频率fs,在待测信号的一个周期Tx内,记录标准频率的周期数Ns,则被测信号的频率为:fx=fs/Ns。

4.这两种方法的计数值会产生±1个字误差,并且测试精度与计数器中记录的数值Nx或Ns有关。

为了保证测试精度,一般对于低频信号采用测周期法;对于高频信号采用测频法,因此测试时很不方便,所以人门提出等精度测频方法。

5.等精度测频方法是在直接测频方法的基础上发展起来的。

6.它的闸门时间不是固定的值,而是被测信号周期的整数倍,即与被测信号同步,因此,测除了对被测信号计数所产生±1个字误差,并且达到了在整个测试频段的等精度测量。

等精度测频原理波形图7.在测量过程中,有两个计数器分别对标准信号和被测信号同时计数。

8.首先给出闸门开启信号(预置闸门上升沿),此时计数器并不开始计数,而是等到被测信号的上升沿到来时,计数器才真正开始计数。

然后预置闸门关闭信号(下降沿)到时,计数器并不立即停止计数,而是等到被测信号的上升沿到来时才结束计数,完成一次测量过程。

可以看出,实际闸门时间τ与预置闸门时间τ1并不严格相等,但差值不超过被测信号的一个周期9.设在一次实际闸门时间τ中计数器对被测信号的计数值为Nx,对标准信号的计数值为Ns。

10.标准信号的频率为fs,则被测信号的频率为11.由式(1)可知,若忽略标频fs的误差,则等精度测频可能产生的相对误差为12.δ=(|fxc-fx|/fxe)×100% (2)13.其中fxe为被测信号频率的准确值。

毕业论文声明本人郑重声明:1.此毕业论文是本人在指导教师指导下独立进行研究取得的成果。

除了特别加以标注地方外,本文不包含他人或其它机构已经发表或撰写过的研究成果。

对本文研究做出重要贡献的个人与集体均已在文中作了明确标明。

本人完全意识到本声明的法律结果由本人承担。

2.本人完全了解学校、学院有关保留、使用学位论文的规定,同意学校与学院保留并向国家有关部门或机构送交此论文的复印件和电子版,允许此文被查阅和借阅。

本人授权大学学院可以将此文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本文。

3.若在大学学院毕业论文审查小组复审中,发现本文有抄袭,一切后果均由本人承担,与毕业论文指导老师无关。

4.本人所呈交的毕业论文,是在指导老师的指导下独立进行研究所取得的成果。

论文中凡引用他人已经发布或未发表的成果、数据、观点等,均已明确注明出处。

论文中已经注明引用的内容外,不包含任何其他个人或集体已经发表或撰写过的研究成果。

对本文的研究成果做出重要贡献的个人和集体,均已在论文中已明确的方式标明。

学位论文作者(签名):年月关于毕业论文使用授权的声明本人在指导老师的指导下所完成的论文及相关的资料(包括图纸、实验记录、原始数据、实物照片、图片、录音带、设计手稿等),知识产权归属华北电力大学。

本人完全了解大学有关保存,使用毕业论文的规定。

同意学校保存或向国家有关部门或机构送交论文的纸质版或电子版,允许论文被查阅或借阅。

本人授权大学可以将本毕业论文的全部或部分内容编入有关数据库进行检索,可以采用任何复制手段保存或编汇本毕业论文。

如果发表相关成果,一定征得指导教师同意,且第一署名单位为大学。

本人毕业后使用毕业论文或与该论文直接相关的学术论文或成果时,第一署名单位仍然为大学。

本人完全了解大学关于收集、保存、使用学位论文的规定,同意如下各项内容:按照学校要求提交学位论文的印刷本和电子版本;学校有权保存学位论文的印刷本和电子版,并采用影印、缩印、扫描、数字化或其它手段保存或汇编本学位论文;学校有权提供目录检索以及提供本学位论文全文或者部分的阅览服务;学校有权按有关规定向国家有关部门或者机构送交论文的复印件和电子版,允许论文被查阅和借阅。

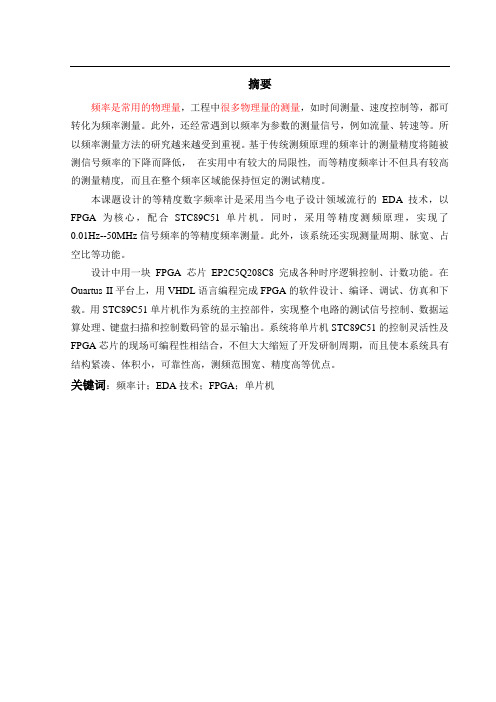

摘要频率是常用的物理量,工程中很多物理量的测量,如时间测量、速度控制等,都可转化为频率测量。

此外,还经常遇到以频率为参数的测量信号,例如流量、转速等。

所以频率测量方法的研究越来越受到重视。

基于传统测频原理的频率计的测量精度将随被测信号频率的下降而降低,在实用中有较大的局限性, 而等精度频率计不但具有较高的测量精度, 而且在整个频率区域能保持恒定的测试精度。

本课题设计的等精度数字频率计是采用当今电子设计领域流行的EDA技术,以FPGA为核心,配合STC89C51单片机。

同时,采用等精度测频原理,实现了0.01Hz--50MHz信号频率的等精度频率测量。

此外,该系统还实现测量周期、脉宽、占空比等功能。

设计中用一块FPGA芯片EP2C5Q208C8完成各种时序逻辑控制、计数功能。

在Ouartus II平台上,用VHDL语言编程完成FPGA的软件设计、编译、调试、仿真和下载。

用STC89C51单片机作为系统的主控部件,实现整个电路的测试信号控制、数据运算处理、键盘扫描和控制数码管的显示输出。

系统将单片机STC89C51的控制灵活性及FPGA芯片的现场可编程性相结合,不但大大缩短了开发研制周期,而且使本系统具有结构紧凑、体积小,可靠性高,测频范围宽、精度高等优点。

关键词:频率计;EDA技术;FPGA;单片机AbstractFrequency is monly used physical quantity, lots of measurement of physical quantity in the project, such as the measurement of time, the control of velocity, can be changed into the measurement of frequency. Besides, the measured signal with a frequency parameter, such as the rate of flow, the rotational speed, is often encountered. So the research of the method of measuring frequency has bee more and more significant in the real application.According to the principles of traditional frequency measurement , the measurement accuracy of frequency will decrease with the signal frequency decrease .but it has more limitations in the real application, equal precision frequency meter not only has high accuracy, but also maintains constant test accuracy in the whole frequency region .With the help of FPGA and cooperating with the single chip puter STC89C51,The digital frequency design in our program has realized the precision measurement of 0.01Hz-50MHz signal frequency by adopting the current EDA technique prevailing in the electronic designs and using the principle of multi-period synchrony frequency measurement. Besides, the system can plete the cycle, pulse width, duty cycle measurement function .In this design, using an FPGA chip EP2C5Q208C8 pletes a variety of temporal logic control and counting function. In the platform of Ouartus II, using VHDL language pletes FPGA software design, piler, debugging, simulation, and download. By use of the STC89C51 single chip puter as the main controlling parts, the control of the tested signal, the scan of keyboard and the output display of LED can be realized. The system bines the control flexibility of STC89C51 with programmable performance of FPGA, ,not only can it shorten the period of the development and research, but also it has the advantages of pact structure, little volume, high reliability, wide scope and high precision.Keywords:Frequency meter,EDA technique,FPGA, Single chip puter()原创性声明和使用授权说明原创性声明本人郑重承诺:所呈交的(),是我个人在指导教师的指导下进行的研究工作及取得的成果。

等精度頑率廿o测Si模挟的片外输入果作者:林军招弟任战淸指导老iJih杰(黄冈师学院物理科学于技术学院林军招弟BffiS黄冈438000 )蘭机和FPGA沟成的最小系貌为核心,以89C52单片机作为控制中心,汇编诸言编程oFPGA主芯片是Altera公司的Cyclone系列的EP1C6Q240C8, VHDL语言编程,设双向口,等精度测颐模块,耀盘编码甘描模块等。

測颐模块的片外输人采作者:林军招弟I俯指导老加:杰(黄冈师学院物理科学于技术学院林军招弟任战涛黄冈438000 )K5:本设廿以单片机和FPGA构成的最小系鋭为核心,以89C52单片机作为控制中呛,汇编讯言编程。

FPGA主芯片是Altera公司的Cyclone系列的EP1C6Q240C8, VHDL S言编程,设双向口,等精度測頫模块,健盘编码甘描模块等。

测频模块的片外输入呆作者:林军招弟任拔涛指导老加:杰(黄冈师学院胸理科学于技术学院林军招弟任故涛黄冈438000 )摘要:本设廿以单片机和FPGA构成的E小系筑为核4以89C52单片机作为控制中呛,汇编讯言编程。

FPGA主芯片是Altera公司的Cyclone系列的EP1C6Q240C8, VHDL 言编程,设双向口,等精度d頑模快,建盘编码扫描模块等。

测频模块的片外输入呆作者:林军招弟任战淸指导老帅:杰(黄冈师学院物理科学于技术学院林军招弟任檢涛黄冈438000 )摘要:本设廿以单片机和FPGA构成的最小系境为核心,以89C52单片机作为控制中心,汇编培言编程。

FPGA主芯片是Altera公司的Cyclone系列的EP1C6Q240C8, VHDL培言编程,设双向口,等ft H « i模块,建盘编码扫描模块等。

测频模块的片外输人采用带宽运赦OPA637加大,并使用TL3116和LM311构建迟滞比较器整形为方波信号送人FPGA由可编程逻辑组建的K频单元运算;显示呆用TC6963C腔制液晶显示模快;等精度测量法。

姓名:郑中权班级:电子1班 数电课设报告江苏科技大学2017/10/12100MHz等精度频率计设计(基于Verilog HDL)一、设计要求:提供一个幅值为10mV ~ 1 V,频率为 1 ~ 100MHz的正弦信号,需测试以下指标:1.频率:测频范围 1Hz ~ 100MHz,测频精度为测频全域内相对误差恒为百万分之一。

2.占空比:测试精度 1% ~ 99%3.相位差:测试两个同频率的信号之间的相位差,测试范围 0 ~ 360二、设计分析使用FPGA数字信号处理方法,首先需要将正弦信号转换成可读取的数字方波信号,再经过FPGA设计计算得出所需测量值。

三、模电部分首先选择比较器,对于 100 MHz 信号,比较器灵敏度需要达到5ns内,TI公司的LTV3501灵敏度为4.5ns,符合要求由TLV3501数据手册得知:当频率低于 50MHz 的时候,正弦波的峰峰值需大于20mV,频率高于50MHz时,峰峰值需大于 1V。

然后需要选择放大器,当正弦波幅值为 10mV时,放大倍数需大于35。

方法通过二级放大,一级用OPA847放大20倍,二级用OPA675放大8倍,得到总放大倍数160的正弦波。

经转换后的输出电压符合TTL电平要求,可以被识别出0和1。

四、数电部分开发板:Cyclone IV E: EP4CE6E22C8板载时钟为 50MHz,带4个按键和一个复位键(按键按下为0,抬起为1),四个七段数码管(共阳),FPGA的引脚可由杜邦线引出。

设计思路:测量频率:输入一个100MHz的基准频率,由计数器CNT1来计算基准频率的上升沿个数,即周期数。

输入一个被测信号,它由计数器CNT2来测量周期数。

两个信号在同一个使能信号EN(使能信号时间为1~2s)下开始计数,计数完后,存储计数结果,由(CNT1 * 10)可以算出具体的计数时间(单位ns),再由((CNT1 * 10ns)/CNT2 )*10^9可算得被测信号频率,单位Hz。

摘要本文基于FPGA的等精度测频原理,给出了通过FPGA来设计等精度频率计的具体方法。

并在此基础上增加了测量周期、脉冲宽度、占空比的功能。

设计中,以Alteta FPGA 系列CycloneⅡ EP2C5T144C8器件为核心;运用VHDL语言设计功能模块;运用SOPC设计技术来配置NiosII系统,进行信号的控制、数据读取、运算处理、液晶的显示。

关键词:等精度频率计;FPGA;NiosⅡ;AbstractThe principle of cymometer of equal precision based on FPGA is introduced in this paper. The specific methods are given to design the system through the FPGA. It is also adds much more function such as cycle, pulse width, duty cycle measurement. It uses Altera Corporation CycloneII series ship--EP2C5T144C8 as a core; adopts Verilog Hardware Description Language to implement function module; adopts the SOPC technique to configuration NiosII system. the NiosⅡsystem is used for signal controlling, data processing , calculation, and display。

Key Word:equal precision frequency meter; FPGA; NiosⅡ;目录摘要 (I)Abstract (I)1 引言 (1)2 系统设计 (1)2.1设计要求 (1)2.2方案论证与比较 (2)2.3 设计思路 (2)2.4 系统的总体设计 (3)3 模块电路的设计 (4)3.1 CycloneⅡ SOPC Board 简介 (4)3.2 频率、周期测试模块 (5)3.2.1 等精度测频法原理 (5)3.2.2 等精度测周期法原理 (6)3.2.3 实现方法 (6)3.2.4 仿真 (7)3.3 脉宽、占空比测试模块 (8)3.3.1 脉宽测量原理 (8)3.3.2 占空比测量原理 (8)3.3.3 实现方法 (8)3.3.4 仿真 (8)3.4 液晶显示 (9)3.4.1 LCM128645ZK液晶概述 (9)3.4.2 液晶的控制 (9)4 NIOSⅡ系统的设计 (11)4.1 NIOSⅡ系统的分析 (11)4.2 基于NIOSⅡ IDE的软件设计 (12)4.2.1 主要的库函数说明 (12)4.2.2 系统流程图 (12)5 系统测试 (14)5.1 测试仪器 (14)5.2数据记录与分析 (14)5.2.1 频率、周期测试 (14)5.2.2 脉宽测试 (16)5.2.3 占空比测试 (17)5.3 设计不足 (17)6 结束语 (18)致谢 (19)参考文献 (20)附录 (21)1 引言在电子测量技术中,频率测量是最基本的测量之一。

基于FPGA的等精度频率计的设计随着科学技术的发展,频率计作为一种重要的测量仪器,在许多领域都得到了广泛的应用。

而基于FPGA的等精度频率计以其高速、高精度等特点,成为了当今科研和工程实践中的重要工具。

FPGA(Field Programmable Gate Array)是一种可编程的现场逻辑门阵列,具有高度可靠性、可编程性和高性能的特点。

在设计基于FPGA的等精度频率计时,我们可以利用FPGA的计数器、控制器和输入输出端口等资源来实现频率测量功能。

首先,我们需要设计一个数值控制计数器,用于计数输入信号的脉冲数。

这个计数器可以是一个简单的二进制计数器,也可以是一个分频器。

在设计计数器时,需要考虑输入信号的频率范围、计数器的位宽和计数器的溢出处理等问题。

通过控制计数器的计数周期,我们可以实现不同精度的频率测量。

其次,我们需要设计一个定时器,用于测量计数器计数的时间。

定时器可以利用FPGA内部的时钟资源来实现,通过控制定时器的计时周期和测量精度,我们可以得出频率计算的结果。

为了提高测量精度,我们可以使用多级定时器进行测量,并通过加权平均等方法来处理测量结果。

然后,我们需要设计一个参数配置模块,用于设置频率计的参数。

通过参数配置模块,用户可以设置计数器的位宽、定时器的计时周期和测量精度等参数,从而灵活地适应不同的测量需求。

最后,我们需要设计一个显示模块,用于显示频率计算结果。

通过显示模块,用户可以直观地了解输入信号的频率和测量精度。

显示模块可以利用FPGA内部的LED显示灯、LCD显示屏或者数码管等硬件资源来实现。

除了基本的频率计功能,我们还可以考虑一些增强功能的设计。

例如,可以添加一个触发器,用于检测输入信号的上升沿或下降沿,并通过触发器的输出信号来控制频率计的启动和停止。

此外,还可以添加一个存储器,用于记录多次测量结果,并通过数据接口将结果传输给上位机或其他设备。

总结起来,基于FPGA的等精度频率计的设计需要充分利用FPGA的计数器、控制器和输入输出端口等资源,通过设计数值控制计数器、定时器、参数配置模块和显示模块等功能模块,实现高速、高精度的频率测量。

数字频率计设计报告数字频率计是一种用于测量信号频率的仪器,广泛应用于电子领域。

本文将针对数字频率计的原理、工作方式以及应用进行详细介绍。

一、引言数字频率计是一种基于数字信号处理技术的测量仪器,它能够精确地测量信号的频率。

它广泛应用于通信、无线电、音频和视频等领域,对于各种信号的频率测量具有重要意义。

二、原理数字频率计的测量原理基于信号的周期性特征。

当一个信号通过数字频率计时,它会被转换成数字信号,并通过计数器进行计数。

通过计数器的计数结果和时间基准的参考值进行比较,就可以得到信号的频率。

三、工作方式数字频率计的工作方式通常分为两种:直接计数法和间接计数法。

1. 直接计数法:该方法直接对信号进行计数,通过计数器对信号的脉冲进行计数,并将计数结果进行处理得到频率值。

这种方法简单直接,但对于高频率信号的计数精度较低。

2. 间接计数法:该方法通过将信号的频率分频至低频范围内进行计数。

通过将高频信号分频后再进行计数,可以提高测量的精度。

四、应用数字频率计在各个领域都有广泛的应用,以下是一些常见的应用场景:1. 通信领域:数字频率计在通信系统中被用于测量信号的载波频率,确保信号的稳定传输。

同时,数字频率计还可以用于频率偏移的测量,以评估通信系统的性能。

2. 无线电领域:数字频率计被用于测量无线电频率,对于射频信号的测量具有重要意义。

它可以用于无线电台站的调试和维护,以确保无线电信号的质量和稳定性。

3. 音频和视频领域:数字频率计在音频和视频设备的校准和测试中被广泛应用。

它可以测量音频和视频信号的频率,以确保音频和视频设备的正常工作。

4. 科学研究领域:数字频率计在科学研究中也起到了重要的作用。

比如,在天文学研究中,数字频率计可以用于测量天体的射电信号频率,从而研究宇宙的演化和结构。

五、总结数字频率计作为一种精确测量信号频率的仪器,在电子领域中有着广泛的应用。

本文从原理、工作方式和应用等方面对数字频率计进行了详细介绍。

信息与电子工程学院

课程设计报告

课程名称 等精度数字频率计设计

班 级 电子信息工程141

姓 名

学 号

指导教师 陈寿法

1

一、 项目综述

大三刚学单片机是老师布置的作业。主要是给学弟学妹参考,没有配程序,哈哈。现在总

结比较生疏了,所以上传了一些以前手写的资料。我用的是C语言编写的,花了大概5天

时间,中途遇到了很多问题,照片里分析了一些解决经验。

该设计采用了一种创新的手法大大提高了频率测量的精度,并且没有增加额外的设计成

本。本项目主要阐述了选择 AT89C52 单片机作为核心器件,采用模块化布局,设计一个

等精度数字频率计设计。

1.1 设计要求

:

(1)

测量范围:0.5Hz~5MHz

(2)

测试误差:<0.01%

一、(3)被测信号为TTL电平。测量结果用6位数字实时显示,显示值的小数点

位置、量纲(频率单位)自动变化(确保显示结果有6位有效数字)。显示器采

用LCD显示屏。设计目的:

针对检测技术课程要求,对学生进行检测装置的电路设计、安装、编程调试

等各个环节的综合性训练,培养学生运用课程中所学的理论与实践紧密结合,独

立地解决实际问题的能力。

二、任务与目标:

设计一基于单片机的等精度数字频率计。

设计完成一个由MCS-51 单片机控制的等精度数字频率计,要求对频率在

一定范围内的输入信号的频率实现等精度测量,即测量精度不受被测信号频率的

改变而变化,显示的量纲随被测信号频率变化而自动切换。

具体功能要求如下:频率测量范围0.5Hz~5MHz,测量误差在0.01%以内,

被测信号为TTL电平。测量结果用6位数字实时显示,显示值的小数点位置、

量纲(频率单位)自动变化(确保显示结果有6位有效数字)。显示器采用LCD

显示屏。

三、主要内容与基本要求:

2

1、硬件设计:完成原理图设计,并焊接元件完成频率计硬件制作。

2、软件设计:用MCS-51汇编语言或C语言完成单片机的程序设计。

3、软硬件联调:调试硬件、软件,查出错误,实现等精度数据频率计的功能。

4、对不同频率的信号进行测试,并对实验数据进行分析。

5、书写课程设计报告。

图 2-1 基于 AT89C52 单片机简易频率计电路原理图

3

3-1 主程序流程图

五、结果分析

当频率输入 0.1HZ 时,数码管显示 0.1HZ,显示正确。

六、总结

4

1).编程难点:量程转换,精度控制。

2).编程中遇到的问题:

a.数值显示问题:通过编写显示程序解决。

b.计数准确度:采用中断+T0,T1计数器,Ns>220 ,U3_D=0。

c.计数显示6位:将整形变量分别取出所需值,再通过循环,显示数字。

d.主函数结构:时间控制变量Time11与计数控制变量Ns位置分配

3).整体评价:芯片资料储存不足,需补充。遇到问题多思考,不行及时请教老师;珍惜机

会,完成练习。

附录:

5

6

7

8

9

10

11

12

13

14

15

16

17