Cypress SRAM和非易失性存储器选型指南

- 格式:pdf

- 大小:1.95 MB

- 文档页数:82

EZ_USB技术参考手册 1.4版本塞普拉斯半导体公司198 Champion CourtSan Jose,CA 95134-1709Tel.:(800)858-1810(toll-free in the U.S.)(408)943-2600塞普拉斯公司免责声明协议本文文件所包含的信息可随时更改而不另行通知,不得解释为塞普拉斯半导体公司成立的承诺。

对于本文檔中出现的任何错误,即使采取了合理的预防措施,塞普拉斯半导休公司不承担任何责任。

如果没有塞普拉斯公司事先的书面同意,本文檔中的任何内容都不能以任何形式或方式被复制或转载。

塞普拉斯半导体产品并不适用、有意的、或者授权,作为组件在系统设计过程中强加于设计之中、或其它有意支持或维持生命的应用、或其它任何由塞普拉斯半导体产品应用的失败而导致的个人受伤或死亡。

买主购买或使用塞普拉斯半导体产品,用于任何无意或无授权的应用,买主应该保护并保挂塞普拉斯半导体和官员、雇员、下属公司、隶属机构及其经销商无害,反对所有因债权、损失、伤害、花费及其合理的律师费,由于直接或间接的任何意想不到或未经授权而引起的人身伤害或死亡的索赔,即使索赔诉讼是由于塞普拉斯公司设计或生产的产品疏忽所引起的。

接受此文檔将被解释为已经接受了以上条款。

EZ-USB技术参考手册,1.4版本版权@2000-2006.塞普拉斯半导体公司版权所有.商标名单Cypress,the Cypress Logo,EZ-USB,Making USB Universal,Xcelerator,and ReNumeration是塞普拉斯半导体公司的商标或注册商标。

Machintosh是苹果计算机公司的注册商标。

Windows是微软的注册商标。

I2C是飞利浦电子的注册商标。

SmartMedia是东芝公司的注册商标。

所有在本手册中使用的其它产品或公司名字可以是他们各自的商标、注册商标或服务商标。

第一章EZ-USB简介1.1简介通用串行总线(USB)作为计算机外设设备的连接方法已经获得了广泛接受。

ARM®Cortex TM-M032位微处理器SWM20P系列MCU数据手册华芯微特科技有限公司Synwit Technology Co., Ltd.目录相关文档 (7)缩写表 (7)寄存器描述列表缩写约定 (7)文档下载地址 (7)1概述 (8)2特性 (9)3选型指南 (12)4功能方框图 (13)5管脚配置 (14)5.1SWM20PG6S6 (14)5.2管脚定义 (15)5.3管脚复用功能 (18)6功能描述 (20)6.1存储器映射 (20)6.2中断控制器(NVIC) (21)6.3系统定时器(SYSTIC) (36)6.4系统控制器 (43)6.5系统管理(SYSCON) (53)6.6端口控制模块(PORTCON) (103)6.7通用I/O (GPIO) (142)6.8加强型定时器(TIMER) (164)6.9基础定时器(BTIMER) (192)6.10正交编码器(QEI) (203)6.11看门狗定时器(WDT) (218)6.12实时时钟(RTC) (230)6.13UART接口控制器(UART) (251)6.14I2C总线控制器(I2C) (272)6.15SPI总线控制器(SPI) (298)6.16脉冲宽度调制(PWM)发生器 (323)6.17预驱电路(GATE DRIVER) (379)6.18模拟数字转换器(SAR ADC) (383)6.19旋转坐标计算(CORDIC) (415)6.20除法器(DIV) (426)6.21FLASH控制器与ISP操作 (437)6.22比较器(CMP) (450)6.23放大器(OPA) (462)7典型应用电路 (471)8电气特性 (472)8.1绝对最大额定值 (472)8.2DC电气特性 (473)8.3AC电气特性 (474)8.4模拟器件特性 (478)8.5DRIVER特性 (486)9封装尺寸 (488)9.1SSOP28 (488)10版本记录 (489)图目录图4-1功能方框图 (13)图5-1 20PG6S6封装管脚配置图 (14)图6-1 systic模块结构图 (37)图6-2 SysTick计数时序图 (38)图6-3时钟结构框图 (54)图6-4端口唤醒示意图 (58)图6-5 PORTCON模块结构框图 (104)图6-6 引脚配置示意图 (105)图6-7 IO输入上拉下拉 (106)图6-8 推挽输出 (106)图6-9 开漏输出 (107)图6-10 TIMER 模块结构框图 (165)图6-11定时器工作示意图 (166)图6-12计数器工作示意图 (167)图6-13级联模式工作示意图 (168)图6-14 脉冲发送示意图 (169)图6-15 输出脉冲比较点1等于周期脉冲发送示意图 (169)图6-16单次高电平捕捉示意图 (170)图6-17单次低电平捕捉示意图 (170)图6-18 HALL记录值 (171)图6-19 HALL对应关系图 (172)图6-20 BTIMER 模块结构框图 (193)图6-21定时器工作示意图 (194)图6-22定时器RELOAD工作示意图 (195)图6-23 QEI模块结构框图 (204)图6-24 增量式正交编码盘示意图 (205)图6-25 三相信号正向/反向旋转时序关系 (205)图6-26 QEI计数器索引复位模式 (206)图6-27 计数匹配复位模式 (206)图6-28 正交编码器x4计数模式示意图 (207)图6-29 正交编码器x2计数模式示意图 (207)图6-30 WDT模块结构框图 (219)图6-31 普通模式WDT工作示意图 (220)图6-32 WDT配置为RESET模式波形图 (221)图6-33 WDT配置为中断模式波形图 (221)图6-34 窗口模式看门狗发生中断及复位与计数值之间的关系示意图 (221)图6-35 RTC模块结构框图 (231)图6-36 UART模块结构图 (252)图6-37 UART字符格式 (253)图6-38 自动波特率示意图 (254)图6-39 LIN Fram示意图 (256)图6-40 Break信号不够长示意图 (257)图6-41 Break信号恰好够长示意图 (257)图6-42 Break信号足够长示意图 (257)图6-43硬件流控 (258)图6-44 对方发送8个数据接收FIFO示意图 (259)图6-45 对方发送9个数据接收FIFO示意图 (259)图6-46 发送FIFO示意图 (260)图6-47 I2C模块结构框图 (273)图6-48 I2C通信示意图 (274)图6-49 Master SCL周期配置示意图 (275)图6-50 Master 寄存器时序示意图 (277)图6-51 Slave 寄存器时序示意图 (279)图6-52 SPI模块结构框图 (299)图6-53 SPI模式波形图 (300)图6-54 SSI模式单次输出波 (301)图6-55 SSI模式连续输出波形 (301)图6-56主机模式接口框图 (302)图6-57从机模式接口框图 (302)图6-58 philips数据格式 (302)图6-59 MSB对齐数据格式 (303)图6-60 PCM短帧数据格式 (303)图6-61 PCM 长帧数据格式(PCMSYNW = 0) (304)图6-62 PCM 长帧数据格式(PCMSYNW = 1) (304)图6-63 SPIFLASH四线读帧格式 (304)图6-64 SPIFALSH四线模式外部连接图 (304)图6-65 PWM模块结构框图 (324)图6-66 PWM死区示意图 (325)图6-67 边沿对齐模式下向上计数时计数器启动与停止波形 (326)图6-68 边沿对齐模式下向下计数时计数器启动与停止波形 (327)图6-69 中心对齐模式下计数器启动与停止波形 (328)图6-70 非对称中心对齐模式下计数器启动与停止波形 (328)图6-71 边沿对齐模式下计数器计数过程波形 (329)图6-72 中心对称模式下计数器计数过程波形 (329)图6-73 硬件刹车控制和软件刹车控制计数器计数情况 (330)图6-74 计数器重载波形 (331)图6-75 边沿对齐模式下PWM信号产生波形 (332)图6-76 中心对齐模式下PWM信号产生波形 (332)图6-77 非对称中心对齐模式下PWM信号产生波形 (333)图6-78 BRK中心对齐模式下PWM信号产生波形 (333)图6-79 TRIGGER控制波形 (334)图6-80 重复计数功能波形图 (335)图6-81 PWM触发ADC采样示意图 (335)图6-82 电平翻转示意图 (336)图6-83 挖坑前波形 (337)图6-84 挖坑后波形 (337)图6-85 预驱电路结构框图 (380)图6-86 参考应用电路图 (382)图6-87 ADC模块结构框图 (384)图6-88 ADC时钟示意图 (385)图6-89 中心对称模式下PWM触发ADC采样示意图 (386)图6-90 SAR ADC连续采样示意图 (387)图6-91 SAR ADC多通道连续采样示意图 (388)图6-92比较器框图 (451)图6-93 比较器迟滞功能示意图 (453)图6-94 HALL对应关系图 (453)图6-95 P端分压模式结构示意图 (454)图6-96 P端分压模式结构图 (454)图6-97放大器框图 (463)图6-98典型放大电路 (464)图6-99 PGA内部结构图 (465)图6-100 PGA应用参考图 (466)图7-1典型应用电路图 (471)图8-1 上电复位时间示意图 (477)图9-1 SSOP28封装尺寸图 (488)表格目录表格3-1 SWM20P系列MCU选型表 (12)表格5-1 PA复用功能 (18)表格5-2 PB复用功能 (18)表格5-3 PM复用功能 (19)表格6-1存储器映射 (20)表格6-2中断编号及对应外设 (22)表格8-1绝对最大额定值 (472)表格8-2 DC电气特性(Vdd-Vss = 5.0V, Tw =25℃)) (473)表格8-3内部振荡器特征值 (474)表格8-4外部4-32MHZ晶体振荡器 (475)表格8-5外部振荡器典型电路 (476)表格8-6 SAR ADC特征值 (478)表格8-7放大器特征值 (479)表格8-8比较器特征值 (480)表格8-9LDO特征值 (481)表格8-10 绝对最大额定值 (486)表格8-11 绝对最大额定值 (486)表格8-12 绝对最大额定值 (486)表格8-13 动态电特性值 (487)相关文档缩写表寄存器描述列表缩写约定文档下载地址/support-1/3.html1概述SWM20P系列32位MCU(以下简称SWM20P)内嵌ARM® CortexTM-M0内核,凭借其出色的性能以及高可靠性、低功耗、代码密度大等突出特点,可应用于工业控制、电机控制、白色家电等多种领域。

铁电存储器中高能质子引发的单粒子功能中断效应实验研究佚名【摘要】利用中国原子能科学研究院的中高能质子实验平台,针对两款商用铁电存储器开展了中高能质子单粒子效应实验研究,发现其中一款器件在质子辐照下发生了单粒子翻转和单粒子功能中断.本文主要针对单粒子功能中断效应展开了后续实验研究.首先通过改变质子能量对器件进行辐照,发现单粒子功能中断截面随质子能量的提高而增加.为进一步研究器件发生单粒子功能中断的机理,利用激光微束平台开展了辅助实验,对铁电存储器的单粒子功能中断效应的敏感区域进行了定位,最后发现铁电存储器单粒子功能中断是由器件外围电路发生的微锁定导致的.【期刊名称】《物理学报》【年(卷),期】2018(067)023【总页数】7页(P226-232)【关键词】铁电存储器;中高能质子;单粒子功能中断效应【正文语种】中文1 引言1.1 铁电存储器的抗辐照背景铁电存储器(ferroelectric random access memory,FRAM)作为新型半导体存储器中的一种,与传统的随机存储器(random access memory,RAM)不同之处在于断电后能继续保持数据.它与市场上的静态随机存储器(static random access memory,SRAM)可以实现替换,可以说是SRAM和FLASH存储器最好工艺的结合[1].相较于Flash,FRAM具有更高的读写次数,更快的读写速度以及超低的功耗[2].FRAM具有高达10万亿次的读写循环,是标准电可擦可编程只读存储器(electrically erasable programmable read-only memory,EEPROM)的100万倍,写入速度为EEPROM的76倍,而功耗却只有EEPROM的3%.FRAM的工艺由铁电薄膜技术与互补金属氧化物半导体(complementary metal oxide semiconductor,CMOS)工艺结合而成,采用具有自发极化特性的钙钛矿材料作为存储介质[3−6],使得存储单元不受辐射环境中产生电荷波动的影响,从而具有优良的抗辐照性能[7,8].所有的这些优点使得FRAM自诞生之日起就在航天航空应用领域成为热门.在国内,FRAM重离子单粒子效应的相关研究已经开展.辜科等[9,10]对1 M的FRAM进行了不同种类重离子的实验研究,得到了该器件发生单粒子翻转(single event upset,SEU)的线性能量传递(linear energy transfer,LET)阈值和单粒子翻转截面以及发生单粒子闩锁的LET值并利用TCAD工具对存储单元的翻转进行了仿真;Zhang等[11]对一款4 M商用FRAM进行了重离子辐照,发现了至少六种单粒子效应,并确定是由外围电路的异常造成的.在复杂的空间辐射环境中,质子分布广泛并占据很大的比例,如宇宙射线中80%为高能质子,太阳风中95%是质子,极光辐射和范·艾伦辐射带的内带中也存在着大量质子[12].因此,对质子源引发的单粒子效应进行实验研究具有重要的意义.由于之前国内并无中高能质子加速器,所以目前国内对于FRAM质子单粒子效应方面的研究仍处于空白.直到近年来中国原子能科学研究院的中高能质子加速器成功出束,这方面的工作才得以开展.1.2 国外的工作2008年NASA在印第安纳大学对型号同为FM22L16的商用FRAM进行了地面质子辐照测试,发现了两种单粒子效应:单粒子翻转(SEU)和单粒子功能中断(singleevent function interrupt,SEFI),并得到了图1所示的SEU翻转截面随质子能量变化的趋势[13],但是并未对SEFI现象进行深入分析.2010年2月,NASA在首颗快速、经济可承受科学技术卫星(fast and af f ordable science and technology satellite,FASTSAT)上搭载一款商用FRAM进行在轨测试(辐照环境主要是质子),在一年的在轨测试时间内并未发现有单个或多个字节的翻转[14].作为新型非易失性存储器,FRAM在质子辐照下发生的单粒子效应也与传统SRAM有所不同:SRAM在相同能量质子辐照下会产生SEU[15,16],而FRAM则会产生SEU和SEFI.对比NASA的地面质子辐照测试,发现实验现象一致,但NASA对于FRAM的SEFI的研究并未深入.在实验中我们发现,SEFI出现的频率较高(如图4所示),甚至器件的失效是由SEFI引起的.所以SEFI对FRAM在质子辐照环境下正常工作状态造成的影响不可忽视,本文使用100 MeV以下的质子束流对FRAM的SEFI进行了实验.图1 不同质子能量下FRAM SEU翻转截面[13]Fig.1 .SEU cross section of FRAM verses dif f erent proton energy[13].2 实验2.1 实验器件及设备本实验选用两款产自Cypress公司的商用FRAM,型号为FM28V100和FM22L16,它们的特征尺寸分别为90 nm和130 nm,容量为1 M和4 M,后者的存储单元工艺结构为2T2C,前者未知.实验平台采用中国原子能科学研究院自主研发的100 MeV质子回旋加速器,如图2所示.它可以产生100 MeV以下的质子束流,利用降能片来实现能量的降低,通过法拉第筒进行注量率的测量,二次电子监督器对注量进行束流监督.通过束流诊断,确定中子质子比小于千分之一,束流的空间均匀性大于75%.这样的质子束流可以认为是稳定可靠的,并且能够满足本实验的要求.实验中选择90,70,50和30 MeV的质子能量,实际注量率为6.9×106p/(cm2·s).由于FRAM 的累计失效剂量高达280 K·rad(Si)以上[17,18],辐照过程中每只器件所接受的质子总剂量远远小于失效累计剂量的80%,可以忽略总剂量效应对本实验的影响.图2 中国原子能科学研究院100 MeV质子回旋加速器Fig.2 .100 MeV proton cyclotron of China institute of atomic energy.2.2 测试系统实验所用的测试系统如图3所示,测试板由ARM(advanced RISC machine)模块,FPGA(f i eld-programmable gate array)模块及电源模块组成.ARM模块接收上位机发送的配置信息及测试命令,并将这些命令解析后发送给FPGA模块,FPGA 模块输出存储器的控制时序,通过I/O接口将操作命令及控制时序信息传递给器件,对器件进行存取操作.器件读出的信息通过I/O口反馈给FPGA模块,FPGA模块分析比较器件是否发生了效应并记录这些数据,依次传递给ARM模块和上位机,使其显示并存储这些信息.图3 FRAM测试系统示意图Fig.3 .Illustration of FRAM testing system.在上述能量点下,根据器件的数据位数,分别向FRAM中填入棋盘式数据格式55或5555,然后在质子束流辐照的过程中对器件进行动态和静态的测试.动态测试通过测试系统在质子辐照过程中实时地从FRAM中读出数据,并和之前写入的棋盘式数据进行比较来判断是否发生了数据错误.静态测试在质子辐照过程中不进行读出操作,辐照结束后才开始读出数据判断是否发生了单粒子效应(single event ef f ect,SEE).2.3 实验结果与分析在上述参数的束流辐照下,FM28V100型FRAM未观察到任何单粒子效应,但是FM22L16型FRAM在辐照过程中发生了一些单粒子效应:当质子束流打开时,测试系统立刻监测到大量的瞬态错误,这些错误每隔几个周期会短暂消失,接着又重新出现(如图4所示),束流停止后器件中留下极少甚至是没有留下错误.将这个过程中发生的SEE详细地分为4种,如表1所列.动态测试中当质子注量累计较低时,器件发生软SEFI,SEU和多位翻转 (multiple-bit-upset,MBU)效应,而随着注量累计增加,器件发生了硬SEFI效应,无法读出器件的SEU和MBU信息,此时断电操作不能使器件恢复正常,视为器件发生了失效.在静态测试过程中,累计注量低时未检测到SEE,累计注量高时,发现了硬SEFI效应.在两个月后对器件进行加电测试,所有发生硬SEFI的FRAM功能恢复正常,此时可以读出器件的SEU与MBU信息.图4 FRAM在质子辐照过程中的SEFI现象Fig.4 .SEFI phenomenon of FRAM using proton irradiation.功能中断截面计算公式为其中δ为功能中断截面;n为功能中断发生时测试系统回读的错误个数;Φ为质子的注量.根据上述公式计算出功能中断截面并进行比较,发现由SEFI造成的错误截面随着质子能量的增加而增加,如图5所示(由于多只器件的失效,未能准确给出30 MeV能量下的截面数据).表1 FRAM在质子辐照过程出现中的SEETable 1 .SEE happened using proton irradiation for FRAM.效应表现Soft SEFI DUT(device under test)在测试周期中检测到大量的瞬态错误,束流停止后也消失Hard SEFI DUT在测试周期中检测到大量的瞬态错误,束流停止后不会消失SEU DUT中留下单个字节的错误,可通过重写恢复MBU DUT中留下多个字节的错误,并且错误地址连续,可通过重写恢复图5 FRAM的SEFI截面随质子能量的变化Fig.5 .FRAM SEFI cross section verses dif f erent proton energy.2.4 SEFI效应机理探索该实验中,器件SEFI效应在质子辐照环境下出现的频率较高,并且硬SEFI导致FRAM失效.SEFI对FRAM造成的影响不可忽视.为了更进一步地探索FRAM中的SEFI敏感区,使用西北核技术研究所的脉冲激光单粒子模拟装置对FM22L16存储器进行实验,使用波长为1064 nm的激光脉冲,对器件的版图从背部进行全面扫描[19].如图6所示,从版图左下角每隔25µm入射一个激光脉冲,每秒入射两个脉冲,激光的能量为5 nJ,一直到版图的右上角结束.在激光扫描的过程中对FRAM预先写入数据再进行动态的回读测试,并同时观察测试过程中是否会出现错误,一旦有SEFI 效应发生,立刻停止激光扫描,并记录下该点坐标,然后继续测试.结果发现激光脉冲在器件的整个外围电路中扫描(图6中A,B区域)均能够引起SEU 效应,存储阵列C区内的激光脉冲不能引发任何单粒子效应,能够引发SEFI效应的区域只有在外围电路中的某一块区域,如图6中B区红点所示.需要指出的是,脉冲激光的直径远远小于图中红点的直径,红点表示SEFI敏感区所在的范围,并非单一点.另外当激光能量小于5 nJ时,可被监测的敏感点个数减少,而激光能量大于5 nJ时,可被监测的敏感点个数增加.在FRAM的电源输出端串联一个100 Ω的分压电阻,利用高频示波器监测波形,结果发现在使用激光微束造成器件SEE时,伴随着每次SEFI的发生,器件的电源输出端都能捕捉到一个微电流的产生(如图7所示),并且在该SEFI过程中的所有出错地址均是连续的.显然FRAM的外围电路才是其SEE敏感区,而红点所在区域是器件SEFI敏感区.FRAM的外围电路基于传统的CMOS工艺加工而成,而集成电路中CMOS工艺易受辐射环境的影响[20−22],特别是缓存器和寄存器,受到辐射环境的影响会导致短暂的读写错误,甚至是功能中断[23].图8(a)所示是一个简化的可控硅电路原理图,Vdd和Vss通过寄生电阻分别与PNP和NPN双极管的基极相连,寄生电阻的存在使其通常保持在关闭的状态,但是当任何一个双极管基极的偏置增加时,电路中流动的电流会增大.一旦双极管的电流增益大于1,电路中的电流再生,直到两个双极管饱和,此时由于流过可控硅结构的电流过大,实际上改变了硅的有效掺杂状态,使其阻值变低[24].图6 FM22L16 FRAM中的SEFI敏感区域Fig.6 .SEFI Sensitivity area ofFM22L16 FRAM.图7 伴随SEFI效应产生的电流波Fig.7 .Electric wave of FRAM accompanied with SEFI.图8 (a)电子电路中寄生的可控硅结构;(b)简化的可控硅原理图Fig.8 .(a)Silicon controlled rectif i er parasitic in digital circuits;(b)simplif i ed silicon controlled rectif i er .在本实验的辐射环境中,质子带一个单位的正电荷,由于其原子质量很轻,所以在物质中的穿透能力较强.当能量低于3 MeV的质子入射到电子器件中时,会通过直接电离的方式在硅中沉积出电子-空穴对,改变电子器件的逻辑或工作状态,这在纳米级尺寸的器件中表现较为突出[16].而本实验选择的中高能质子穿透器件时,库仑力对质子的阻碍能力减弱,此时质子主要与材料物质发生核反应生成重离子和其他次级粒子,重离子带有更多单位的正电荷,并且原子质量较重,穿透能力较弱,会在相对较短的路径中通过直接电离的方式,产生电子-空穴对.而对激光脉冲而言,激光入射器件时,光子被材料吸收,沿着其入射方向电离出电子-空穴对[25],这与低能质子及重离子的直接电离过程十分相似.辐照环境产生的载流子的积累会使得CMOS工艺中的可控硅结构打开,图8(b)所示为电子电路中的可控硅结构示意图,电子空穴对在衬底中被Vss至Vcc的内部电场所收集,电流流过内部寄生衬底电阻时,基极的偏置增大,电路中流动的电流会增大.如果偏置足够高,可控硅结构被触发进入电流再生模式,器件发生单粒子锁定,测试系统对器件失去控制,直到给器件断电,并重新加电才能恢复正常[26,27].在本实验中SEFI发生时,测试系统并未对器件失去控制,因此可以认为可控硅结构中未达到电流增益状态,而是发生了微锁定现象,此时寄生可控硅结构中有电流流过,PMOS管和NMOS管的开关作用失效.FRAM的数据读取和写入过程的顺利执行是有外围电路中的寄存器参与的,这些寄存器中有命令寄存器和地址寄存器,用来响应电路外部传入的命令代码和地址信号.在外围电路的寄存器发生微锁定时,产生了如图7所示的微小电流,其持续的时间为激光或质子在材料中产生的电子-空穴能够维持可控硅结构的寄生二极管中基极正向偏置的时间.在这个时间内,寄存器无法响应,FRAM的读出功能失效,测试系统回读出大量的错误,当这个时间结束后,电流消失,寄存器恢复正常,测试系统读出正确的数据,上一个周期中读出的错误消失,直到下一次微锁定发生时这种情况再次出现,如图4所示.随着质子能量的增高,通过核反应产生的次级重离子种类和能量也增加,在硅衬底中电离出的电子-空穴对随之增加,外围寄存器发生微锁定效应的时间越长,测试系统回读的错误数越多,导致FRAM的功能中断截面随着质子能量的增加而增加.在NASA对Intel生产的微处理器理器(microprocessor)、协处理器(coprocessor)、集成外围(integrated peripheral)的辐照效应研究中,发现其中某一个部分发生SEU均会导致其他两个部分随之发生SEE,推测这是由于各部分的总线连接造成的[28].因此认为,外围电路中发生的微锁定电流,通过总线的连接可以在器件的输出端被观测到,如图7所示.3 结论本文对两款商用FRAM开展了质子单粒子实验研究,通过比较两款器件在质子辐照下的表现,发现特征尺寸对FRAM的SEE敏感性的影响与传统SRAM不同,虽然FM28V100的特征尺寸比FM22L16小,但FM28V100在90 MeV以下的质子能量辐照下未发生SEE,反而是特征尺寸较大的FM22L16出现了SEE.这是因为FM28V100的容量比FM22L16小,外围电路面积也比后者小,导致SEE敏感单元(如寄存器)在版图布局中的比例小,在相同的质子辐照环境下未发生SEE.利用不同能量的质子束流对FRAM进行辐照,FM22L16型FRAM在30—90 MeV的质子能量下均能检测到SEFI效应,并且器件SEFI截面随着质子能量的增加而增加.通过激光微束的辅助实验,发现器件发生SEU效应的敏感区分布在整个外围电路中,而器件发生SEFI的敏感区只分布在外围电路中的某一块区域.本文认为外围电路中参与读写过程的寄存器在辐照环境下发生了微锁定,使其在读取数据的过程中失效,导致数据读取失败.与单粒子锁定现象不同,微锁定产生的电流未超过FRAM的正常工作电流(15 mA),可以自主恢复.这个电流持续的时间决定了FRAM的功能中断截面的大小.最后利用高频示波器在激光脉冲辐照器件时,对FRAM的输出电流进行同步采样,发现伴随着SEFI效应的发生,输出端会俘获到一段瞬态电流,为器件发生SEFI效应机理提供了支撑.参考文献【相关文献】[1]Dahl B A,Cruz-Colon J,Baumann R C,Rodriguez J A,Zhou C,Rodriguez-Latorre J,Khan S,San T,Trinh T 2015 IEEE Radiation Ef f ects Data Workshop(REDW)Boston,MA,USA,July 13–17,2015 p1[2]Zhou Y C,Tang M H 2009 Materials Review 23 1(in Chinese)[周益春,唐明华 2009材料导报23 1][3]Zhao Y Q,Liu B,Yu Z L,Ma J M,Wan Q,He P B,Cai M Q 2017 J.Mater.Chem.C 5 5356[4]Zhao Y Q,Ma Q R,Liu B,Yu Z L,Yang J L,Cai M Q 2018 Nanoscale 10 8677[5]Yu Z L,Ma Q R,Zhao Y Q,Liu B,Cai M Q 2018 J.Phys.Chem.C 17 9275[6]Zhao Y Q,Wang X,Liu B,Yu Z L,He P B,Wan Q,Cai M Q,Yu H L 2018 Org.Electron.53 50[7]Rusu A,Salvatore G,lonescu A M 2009 International Semiconductor Conference Sinaia,Romania,October 12–14,2009 p517[8]Yan S A 2017 Ph.D.Dissertation(Xiangtan:Xiangtan University)(in Chinese)[燕少安 2017博士学位论文(湘潭:湘潭大学)][9]Gu K,Li P,Li W,Fan X 2015 Microelectronics&Computer 32 147(in Chinese)[辜科,李平,李威,范雪 2015微电子学与计算机32 146][10]Gu K,Li P,Li W 2015 Microelectronics&computer 32 110(in Chinese)[辜科,李平,李威2015微电子学与计算机32 110][11]Zhang Z Z,Lei Z F,Yang Z L,Wang X H,Wang B,Liu J,En Y F,Chen H,Li B 2015 IEEERadiation Effects Data Workshop(REDW)Boston,MA,USA,July 13–17,2015 p1[12]Li T S,Chen J,Wang Z Q 2008 Radiation Protection bulletin 26 1(in Chinese)[李桃生,陈军,王志强 2008辐射防护通信26 1][13]O’Bryan M V,LaBel K A,Buchner S P,Ladbury R L,Poivey C F,Oldham T R,Campola M J,Carts M A,Berg M D,Sanders A B,Mackey S R 2008 2008 IEEE Radiation Ef f ects Data Workshop(REDW)Tucson,AZ,USA,July 14–18,2008 p11[14]Zhai Y H,Li W,Li P,Hu B,Huo W R,Li J H,Gu K 2012 Materials Review 26 34(in Chinese)[翟亚红,李威,李平,胡滨,霍伟荣,李俊宏,辜科2012材料导报26 34][15]Luo Y H,Zhang F Q,Wang Y P,Wang Y M,Guo X Q,Guo H X 2016 Acta Phys.Sin.65 068501(in Chinese)[罗尹虹,张凤祁,王燕萍,王园明,郭晓强,郭红霞2016物理学报65 068501] [16]He A L,Guo G,Chen L,Shen D J,Ren Y,Liu J C,Zhang Z C,Cai L,Shi S T,Wang H,Fan H,Gao L J,Kong F Q 2014 Atomic Energy Science and Technology 48 2365(in Chinese)[何安林,郭刚,陈力,沈东军,任义,刘建成,张志超,蔡莉,史淑廷,王惠,范辉,高丽娟,孔福全2014原子能科学技术48 2365][17]Zhang X Y,Guo Q,Lu W,Zhang X F,Zheng Q W,Cui J W,Li Y D,Zhou D 2013 Acta Phys.Sin.62 156107(in Chinese)[张兴尧,郭旗,陆妩,张孝富,郑齐文,崔江维,李豫东,周东2013物理学报62 156107][18]Wei J N,Guo H X,Zhang F Q,Luo Y H,Ding L L,Pan X Y,Zhang Y,Liu Y H 2017 Chin.Phys.B 26 096102[19]Wei J N 2017 M.S.Thesis(Xiangtan:Xiangtan University)(in Chinese)[魏佳男 2017硕士学位论文(湘潭:湘潭大学)][20]Zhou X J,Yu Z G,Li B 2014 Research&Process of SSE 34 577(in Chinese)[周昕杰,于宗光,李博 2014固体电子学研究与进展34 577][21]Xiao X S,Li N,Tong J 2012 IEEE Trans.Nucl.Sci.59 211[22]Xuan S X,Li N,Tong J 2013 IEEE Trans.Nucl.Sci.60 3932[23]Bosser A L,Gupta V,Javanainen A,Tsiligiannis G,LaLumondiere S D,Brewe D,Ferlet-Cavrois V,Puchner H,Kettunen H,Gil T,Wrobel F,Saigné F,Virtanen A,Dilillo L 2018 IEEE Trans.Nucl.Sci.10 1109[24]Tausch J,Sleeter D,Radaelli D,Puchner H 2007 2007 IEEE Radiation Ef f ects Data Workshop(REDW)Honolulu,HI,USA,July 23–27,2007 p185[25]Huang J G,Han J W 2004 Science China 34 121(in Chinese)[黄建国,韩建伟 2004中国科学34 121][26]Yang S Y,Cao Z,Xue Y X 2007 Nuclear Electronics&Detection Technology 27 567(in Chinese)[杨世宇,曹洲,薛玉雄2007核电子学与探测技术27 567][27]Lü Q,Zhang C H,Fu X Y,Deng M,Li W H 2015 Communication Countermea sures 3446(in Chinese)[吕强,张朝辉,洑小云,邓明,李文华2015通信对抗34 46][28]Label K A,Moran A K,Hawkins D K,Sanders A B 1996 IEEE Radiation Ef f ects Data Workshop(REDW)Indian Wells,CA,USA,July 19–23,1996 p19。

红色飓风II开发板USB2FPGA实验指导(ver1.0)Red Logic工作室二〇〇六年四月三日目录第一章FX2特性介绍 (3)1.1介绍 (3)1.2结构 (3)1.3特征 (4)第二章Slave FIFO传输 (5)2.1概述 (5)2.2硬件连接 (5)2.3 Slave FIFO的几种传输方式 (6)2.3.1 同步Slave FIFO写 (6)2.3.2 同步Slave FIFO读 (9)2.3.3异步Slave FIFO写 (11)2.3.4异步Slave FIFO读 (12)第三章寄存器设置 (15)3.1 IFCONFIG (15)3.2 PINFLAGSAB/CD (16)3.3 FIFORESET (17)3.4 FIFOPINPOLAR (18)3.5 EPxCFG (18)3.6 EPxFIFOCFG (19)3.7 EPxAUTOINLENH/L (20)3.8 EPxFIFOPFH/L (21)3.9 INPKTEND (22)3.10 OUTPKTEND (22)3.11 EPxFIFOIE和EPxFIFOIRQ (22)3.12PORTACFG (23)3.13 EPxFIFOBCH EPxFIFOBCL (23)3.14 EP24\68FIFOFLAG (24)3.15其它通用寄存器 (25)第四章同步slave fifo测试操作指南 (26)4.1安装软件包 (26)4.2同步写FIFO测试 (26)4.3同步读FIFO测试 (30)4.4同步读写FIFO测试 (31)第五章红色飓风II开发板USB2FPGA软件设计 (33)5.1 68013固件程序设计 (33)5.2 FPGA源代码设计 (35)第六章USB2FPGA硬件原理图 (37)第七章改板后注意的问题 (37)附录1 版本历史 (39)一.FX2特性介绍1.1介绍Cypress Semiconductor公司的EZ-USB FX2是世界上第一款集成USB2.0的微处理器,它集成了USB2.0收发器、SIE(串行接口引擎)、增强的8051微控制器和可编程的外围接口。

如何选择DSP的外部存储器dsp的速度较快,为了保证dsp的运行速度,外部存储器需要具有一定的速度,否则dsp访问外部存储器时需要加入等待周期。

1)对于c2000系列:c2000系列只能同异步的存储器直接相接。

c2000系列的dsp目前的最高速度为150mhz。

建议可以用的存储器有:cy7c199-15:32k×8,15ns,5v;cy7c1021-12:64k×16,15ns,5v;cy7c1021v33-12:64k×16,15ns,3.3v。

2)对于c3x系列:c3x系列只能同异步的存储器直接相接。

c3x系列的dsp的最高速度,5v的为40mhz,3.3v的为75mhz,为保证dsp无等待运行,分别需要外部存储器的速度<25ns和<12ns。

建议可以用的存储器有:rom:am29f400-70:256k×16,70ns,5v,加入一个等待;am29lv400-55(sst39vf400):256k×16,55ns,3.3v,加入两个等待(目前没有更快的flash)。

sram:cy7c199-15:32k×8,15ns,5v;cy7c1021-15:64k×16,15ns,5v;cy7c1009-15:128k×8,15ns,5v;cy7c1049-15:512k×8,15ns,5v;cy7c1021v33-15:64k×16,15ns,3.3v;cy7c1009v33-15:128k×8,15ns,3.3v;cy7c1041v33-15:256k×16,15ns,3.3v。

3)对于c54x系列:c54x系列只能同异步的存储器直接相接。

c54x系列的dsp的速度为100mhz或160mhz,为保证dsp无等待运行,需要外部存储器的速度<10ns或<6ns。

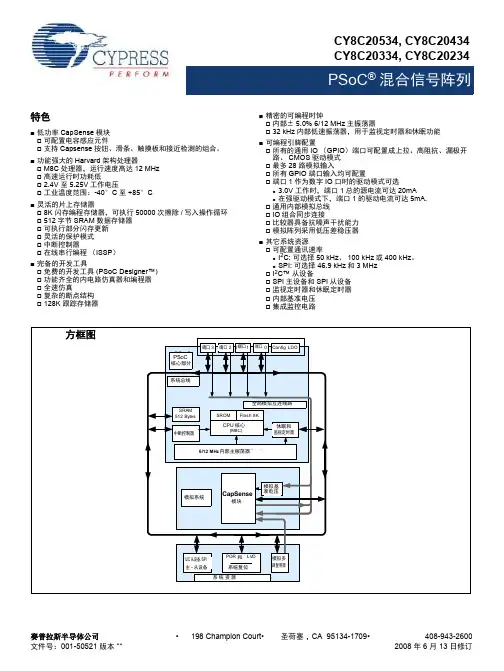

应用手册 AN2292PSoC™ CapSense™的布局指南作者:Ryan Seguine、Mark Lee相关项目:否相关器件系列:CY8C21x34、CY8C24794相关应用手册:AN2233a、AN2277、AN2293、AN2318摘要本应用手册将从PCB布局、覆盖厚度、材料选择和底板设计方面来介绍PSoC CapSense应用的布局指南。

引言电容式传感是一种在前置面板显示、消费类电子和汽车应用中迅速获得广泛推广的接口技术。

该技术为我们带来了无限商机。

由于涉及到的应用数不胜数,因此这里讲的设计原理只能作为基本指南。

本文将介绍一些关于PSoC CapSense的布局和系统设计指南。

PSoC CapSense解决方案的基本电路和固件相对简单,开关操作环境的物理设计则更加简单。

设计电容式传感系统时主要应考虑三方面的问题:印制电路板(PCB)、覆盖材料以及与PCB或电容传性感无关的其他因素。

如欲了解PSoC CapSense的电气和物理特性,请参见应用手册《AN2233a:电容性开关扫描》。

如欲了解CSR用户模块(UM)的有关介绍,请参见UM数据表单。

PCB指南PCB的布局应尽可能减小非按钮、滑块、触摸板等元件的影响。

我们把按钮、滑块和触摸板元件作为导电材料来看待,如铜就是构成按钮、滑块或触摸板的仅有的材料。

从按钮、滑块和触摸板到PSoC的供电线迹不在有效传感范围内,因此不是按钮、滑块和触摸板元件的一部分。

电路无效传感部分仅仅起到减小传感区内检测到目标能力的作用。

与电容式传感无关的PCB线迹和目标也会对按钮、滑块和触摸板元件造成影响,这种影响通常是有害的。

图1. 传感元件定义传感元件PCB布局要尽可能减小这些相互影响,或者,即使不能减小到最小,也要让所有电容性元件都统一。

CSR用户模块确实提供相关算法,能调整阵列中所有物体的原生电容(native capacitance)的差异,不过要尽可能保持阵列的平衡。

局部总线控制器(LBC)允许实现具有特定定时要求的存贮器系统。

·SDRAM器提供了到使用存贮体交叉和连续页面模式的SDRAM接口,通过一条复用的地址/数据总线实现高性能。

生成总线时钟的内部DLL保证电路板设计时数据上升沿性能的改善。

·GPCM为较为简单、性能较低的存贮器和内存映射设备提供接口。

由于不支持突发,所以它具有较低的性能。

所以,GPCM控制的存贮体主要用于引导装入和访问低性能的内存映射的外设。

·UPM支持刷新定时器,外部总线的地址复用和产生可编程的行地址和列地址选通控制信号,允许到DRAM的、突发SRAM和几乎其他所有类型外设的最小粘合接口。

UPM可以用来产生灵活的、用户定义的控制存贮设备的控制信号的定时模式。

这些模式定义了读、写、突发读或突发写期间的外部控制信号的行为。

还可以使用刷新定时器周期地启动用户定义的刷新模式。

图10-20. LBC中的存贮控制器的基本操作可以把每个存贮体(片选)通过其基址寄存器中的机器选择位(BR n[MSEL])分配给这三种机器的任何一个,如图10-20所示。

如果存贮体匹配,对应的机器(GPCM、SDRAM 或UPM)就掌管控制访问的外部信号,并一直保持控制直到操作结束。

10.4.1 基本系统结构下面几个小节介绍LBC的基本系统结构。

10.4.1.1 地址和地址空间检查将已定义的基址写入BR n寄存器,将对应的地址掩码写入OR n寄存器。

每当请求访问局部总线时,将内部事务的地址与每一个存贮体进行比较。

该地址由OR n[BA]和OR n[AM]屏蔽,通过将该地址的19个最高有效位与每个存贮体的基址进行比较来译码地址。

如果与一个存贮控制器存贮体匹配,那么就使用由该存贮体的BR n和OR n所定义的属性控制存贮器的访问;如果与多个存贮体匹配,那么编号最小的存贮体处理存贮器访问(也就是说,存贮体0的优先级高于存贮体1)。

10.4.1.2 外部地址锁存允许信号(LALE)局部总线使用一条复用的地址/数据总线,所以LBC必须辨别在同一条总线(LAD[0:31])上出现的地址阶段和数据阶段。

CapSense 最佳实践作者:Mark Lee相关项目:无摘要用于 CapSense 系统设计的最佳实践终于面世了。

其中所涵盖的主题包括感应方式、布板(PCB Layout )和布局指南以及 CapSense 工具和技术概述。

引言在便携式媒体播放器和移动手持终端等大容量、高可视性产品的应用中,电容式感应作为一种接口技术已被广泛采用。

此举使更多的常规消费类电子产品产生了对该技术的需求,进而引起了技术的显著创新和多种竞争技术的出现。

虽然这些技术各有千秋,但基本原理都是Sensor 与其环境之间的电容变化的测量。

我们对可编程模块和固定功能的 IC 进行对比,由于可编程 IC 将可定制码用于开发解决方案,因此它允许在设计方面具有更大的灵活性。

PSoC® CapSense 将微处理器、可编程的数字和模拟源、片内存储器和其他特性相结合,从而在电容式系统设计中实现了最大的灵活性。

本应用手册简要描述了用于 CapSense设计的最佳实践。

图 1 PSoC 模拟与数字模块可用于配置 CapSense 及其它功能PSoC 架构允许设计人员将多个电容式感应设计元件整合到一种应用中。

比如按钮、滑条、触摸板和接近式感应,在相同的电路中利用同一器件就可同时对这些元件提供支持。

可使用 PSoC 来扫描电容式Sensor ,并驱动 LED 、控制马达、驱动扬声器等等,如图 2 所示。

一种称为动态重构的概念使 CapSense 应用可根据需要即时进行重新配置,从而能够利用大于 100% 的系统资源。

图 2 采用 CapSense Plus 技术的应用实例:采用单个 PSoC 还可实现马达、LED 、以及扬声器等1、易于配置的电容式感应解决方案PSoC 可实施不同的 CapSense 方式(见参考书目 [1])。

所需的具体特性决定了感应的方式。

如果最需要的是电池使用寿命并且要在 2.7V 电压下工作,那么CSA 的感应方式就是最明智的选择。