IC引线框架标准

- 格式:docx

- 大小:724.77 KB

- 文档页数:2

学员作业课程名称:集成电路封装与测试作业内容:集成电路封装中的引线键合技术任课教师:张江元学员姓名:蒋涛学员学号: 511412130所在班级:集成电路工程教师评分:集成电路封装中的引线键合技术【摘要】在回顾现有的引线键合技术之后,文章主要探讨了集成电路封装中引线健合技术的发展趋势。

球形焊接工艺比楔形焊接工艺具有更多的优势,因而获得了广泛使用。

传统的前向拱丝越来越难以满足目前封装的高密度要求,反向拱丝能满足非常低的弧高的要求。

前向拱丝和反向拱丝工艺相结合,能适应复杂的多排引线健合和多芯片封装结构的要求。

并具体以球栅阵列封装为例,介绍了检测手段。

不断发展的引线健合技术使得引线健合工艺能继续满足封装日益发展的要求,为封装继续提供低成本解决方案。

【主要内容】1. 引线键合工艺1. 1 楔形焊接工艺流程1. 2 圆形焊接工艺流程1. 3 主要工艺参数介绍1.3.1 键合温度1.3.2 键合时间2. 引线键合材料2. 1 焊线工具2. 2 引线材料3. 引线键合线弧技术3. 1 前向拱丝3. 2 反向拱丝4. 键合质量的判定标准4. 1电测试4. 2 边界扫描检测4. 3 X射线测试5. 小结参考文献1. 引线键合工艺在IC封装中,芯片和引线框架(基板)的连接为电源和信号的分配提供了电路连接。

有三种方式实现内部连接:倒装焊、载带自动焊和引线键合。

虽然倒装焊的应用增长很快,但是目前90%以上的连接方式仍是引线键合。

这个主要是基于成本的考虑。

虽然倒装焊能大幅度提升封装的性能,但是过于昂贵的成本使得倒装焊仅仅用于一些高端的产品上。

事实上对于一般产品的性能要求,用引线键合已经能够达到,没有必要使用倒装焊引起额外的成本增加。

对于封装厂商来说,使用倒装焊意味着目前传统的引线键合、模塑设备的淘汰,需要引入新的倒装焊设备,这个投资是非常巨大的。

传统的封装尺寸比较大,因而引线键合所使用的线的直径比较大,线弧也比较高,一般在150m~250m之间。

IC的各种封装1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且BGA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA(butt joint pin grid array) 表面贴装型PGA 的别称(见表面贴装型PGA)。

4、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。

IC封装词条辑录1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚 BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且BGA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA(butt joint pin grid array)表面贴装型PGA 的别称(见表面贴装型PGA)。

4、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。

我国引线框架的生产情况我国内引线框架生产企业主要集中在长三角、珠三角,随着国外大封装测试厂家在中国境内投资办厂,国内引线框架的需求也将有迅速增长。

国内引线框架主要企业介绍如下:(1)先进半导体物料科技有限公司(ASM Assembly Materials Limited)ASM 于 1968 年成立,公司总部位于荷兰的比尔托芬,是一家跨国公司,拥有雄厚的技术基础,ASM 公司主要生产半导体用设备和材料,是全球 15 家顶级半导体设备制造商之一。

在美国、日本、香港、中国、新加坡、马来西亚都设有分公司。

在深圳设有分公司,生产引线框架。

(2)深圳赛格高技术投资股份有限公司(SHIC)公司与德国、荷兰柏狮(POSSEHL)电子集团合资兴办深圳赛格柏狮电子有限公司(PSE),注册资本 1104.36 万美元,主营半导体集成电路引线框架、半导体精密模具制造等业务,产品畅销海内外。

(3)铜陵丰山三佳微电子有限公司公司是由韩国丰山微电子株式会社与三佳电子集团有限责任公司共同投资2000 万美元建立的一家高科技企业,韩国丰山公司以技术、设备和资金入股,占51%的股份,三佳集团以厂房、设备和资金入股,占 49%的股份。

公司引进国际先进的技术和生产装备,生产 IC、TR 类引线框架和硬质合金级进冲模具,已建成年产 40 亿只引线框架的规模。

(4)三井高科技(上海)有限公司三井高科技(上海)有限公司、三井高科技(天津)有限公司、三井高科技电子(东莞)有限公司都是日本三井高科技股份公司在中国大陆独资开设的三家分立器件及集成电路引线框架、高精度马达转子定子叠片的专业生产厂家。

是专业生产集成电路引线框架,高精度金属模的企业,也是目前国内唯一具有 240 只脚 IC 引线框架生产能力的生产厂家,包括照相蚀刻 IC 引线框架、密冲压 IC 引线框架。

三井高科技(上海)有限公司成立于 1996 年 3 月,1998 年 6 月开始批量生产。

IC封装so、soj、sop的区别1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚BGA仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP为40mm 见方。

而且BGA不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA(butt joint pin grid array) 表面贴装型PGA的别称(见表面贴装型PGA)。

4、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。

qfn封装的引线标准

QFN封装是一种无引线封装,其引线标准主要包括以下几个

方面:

1. 引线排列方式:QFN封装的引线排列方式通常为四周引

线排列,也就是引线分布在封装的四周边缘。

2. 引线数量:QFN封装的引线数量可以根据封装的尺寸和

要求而变化,常见的引线数量有16、32、48、64等。

3. 引线间距:QFN封装的引线间距通常是指引线之间的中

心距离,常见的引线间距有0.5mm、0.65mm、0.8mm、1.0mm 等。

4. 引线宽度:QFN封装的引线宽度通常是指引线的金属部

分的宽度,常见的引线宽度有0.15mm、0.2mm、0.25mm等。

5. 引线长度:QFN封装的引线长度通常是指引线从焊盘到

封装表面的长度,常见的引线长度有0.3mm、0.4mm、0.5mm 等。

6. 引线形状:QFN封装的引线形状通常是直线形状,也有

一些封装采用了弯曲形状的引线设计。

需要注意的是,QFN封装的引线标准可能会因不同的制造商

和产品而有所差异,因此在具体应用中需要根据实际情况

选择适合的封装和引线标准。

1 引言所谓芯片尺寸封装就是CSP (Chip Size Package或Chip Scale Package)。

JEDEC(美国EIA协会联合电子器件工程委员会)的JSTK一012标准规定,LSI芯片封装面积小于或等于LSI芯片面积的120%的产品称之为CSP。

CSP技术的出现确保VLSI在高性能、高可靠性的前提下实现芯片的最小尺寸封装(接近裸芯片的尺寸),而相对成本却更低,因此符合电子产品小型化的发展潮流,是极具市场竞争力的高密度封装形式。

本文从CSP的特点、类别和制作上艺以及生产和研发等几个方面详细论述这种先进的封装技术,并对我国CSP技术的研发提出几点建议。

2 CSP的特点CSP实际上是在BGA封装小型化过程中形成的,所以有人也将CSP称之为μBGA(微型球栅阵列,现在仅将它划为CSP的一种形式),因此它自然地具有BGA封装技术的许多优点。

2.1 封装尺寸小CSP是目前体积最小的VLSI封装之一。

一般,CSP封装面积不到0.5 mm,而间距是QFP的1/10,BGA的1/3~l/10。

2.2 可容纳引脚的数最多在各种相同尺寸的芯片封装中,CSP可容纳的引脚数最多,适宜进行多引脚数封装,甚至可以应用在I/0数超过2000的高性能芯片上。

例如,引脚间距为0.5 mm,封装尺寸为40 mm×40 mm的QFP,引脚数最多为304根,若要增加引脚数,只能减小引脚间距,但在传统工艺条件下,OFP难以突破0.3 mm的技术极限;与CSP相提并论的是BGA封装,它的引脚数可达600~1000根,但值得重视的是,在引脚数相同的情况下,CSP的组装远比BGA容易。

2.3 电性能优良CSP的内部布线长度(仅为0.8~1.O mm)比QFP或BGA的布线长度短得多,寄生引线电容、引线电阻及引线电感均很小,从而使信号传输延迟大为缩短。

CSP的存取时间比QFP或BGA短1/5~1/6左右,同时CSP的抗噪能力强,开关噪声只有DIP(双列直插式封装)的1/2。

ChinalntegratedCircult1、引言随着集成电路(IC)工作频率或速度不断提高以及产品小型化的要求,封装成为高频集成电路设计的瓶颈,它在信号完整性、损耗等多方面影响电路的特性。

芯片与引线框架的互连技术是IC封装中极为关键的工艺步骤。

虽然目前已经开发了很多新的互连结构,例如互连点、凸点、按键结构、弹簧结构和柱状结构等,但是IC市场上引线键合技术因为其低成本和可靠的制造技术仍占主要地位[1][2]。

IC发展对引线键合技术的挑战日益增大,尤其是在高速电子产品和射频(RF)产品上,因此,人们越来越关心封装键合线的高频性能[3] ̄[7]。

本文主要研究了键合线的Spice模型和模型参数提取方法,建立了单个键合线的!型等效电路,给出了根据二端口S参数提取键合线等效电路模型中的R、L和C参量值的方法。

为了去除测试结构对键合线的影响,准确地获得键合线的S参数,在电路仿真和测试中使用了去嵌入(de-embedding)技术。

最后设计了一个简单的低成本的测试结构,比较验证了仿真分析结果。

东南大学集成电路学院周燕南通大学专用集成电路设计重点实验室孙玲景为平IC封装中引线键合互连特性分析*摘要:研究了芯片封装中键合线的建模和模型参数提取方法。

根据二端口网络参量,提出了单键合线的"型等效电路并提取了模型中的R、L和C参量。

最后,设计出一个简单、低成本的测试结构验证了仿真分析结果。

关键词:封装,键合线,建模,参数提取,去嵌入CharacterAnalysisofBond-WireinICPackageZHOUYan[1],SUNLing[2]JINGWeiping[2](1.SchoolofIntegratedCircuit,SoutheastUniversity,210096Nanjing,China2.JiangsuProvincialKeyLabofASICDesign,NantongUniversity,226007,China)Abstract:TheobjectiveofthispaperwastopresentapreparatoryinvestigationofmodelingofICpackagesforchip-packageco-design.Theworkwasfocusedonthemodelingandparameterextractionmethodsofbond-wires.Basedontwo-portparameters,alumped#-typeequivalentcircuitforasingle-bond-wirewaspresentedandtheR,L,andCparametersofthebond-wirewereextracted.Finally,asimpleandlowcostteststructurewasdesignedandmadeforvalidationoftheparameterizedmodel.Keywords:Package;Bond-wire;Modeling;Parameterextraction;De-embedding*基金项目:江苏省高新技术资助项目(BG2005022),南通大学自然科学基金资助项目(05Z115)55http://www.cicmag.com(总第90期)2006·11·(总第90期)http://www.cicmag.com2、键合线模型目前,全波分析方法被广泛应用在互连结构建模中。

IC封装术语(中英文对照)1、SOW (Small Outline Package(Wide—Jype))宽体SOP.部分半导体厂家采用的名称。

2、SOF(small Out—Line package)小外形封装。

表面贴装型封装之一,引脚从封装两侧引出呈海鸥翼状(L 字形)。

材料有塑料和陶瓷两种。

另外也叫SOL 和DFP。

SOP 除了用于存储器LSI 外,也广泛用于规模不太大的ASSP 等电路。

在输入输出端子不超过10~40 的领域,SOP 是普及最广的表面贴装封装.引脚中心距1。

27mm,引脚数从8~44。

另外,引脚中心距小于1。

27mm 的SOP 也称为SSOP;装配高度不到1。

27mm 的SOP 也称为TSOP (见SSOP、TSOP).还有一种带有散热片的SOP。

3、SONF(Small Out-Line Non—Fin)无散热片的SOP。

与通常的SOP 相同。

为了在功率IC 封装中表示无散热片的区别,有意增添了NF(non-fin)标记。

部分半导体厂家采用的名称(见SOP)。

4、SQL(Small Out—Line L—leaded package)按照JEDEC(美国联合电子设备工程委员会)标准对SOP 所采用的名称(见SOP)。

5、SOJ(Small Out—Line J-Leaded Package)J 形引脚小外型封装.表面贴装型封装之一。

引脚从封装两侧引出向下呈J 字形,故此得名。

通常为塑料制品,多数用于DRAM 和SRAM 等存储器LSI 电路,但绝大部分是DRAM。

用SOJ封装的DRAM 器件很多都装配在SIMM 上.引脚中心距1。

27mm,引脚数从20 至40(见SIMM)。

6、SOIC(small out-line integrated circuit)SOP 的别称(见SOP)。

国外有许多半导体厂家采用此名称。

7、SOI(small out-line I—leaded package)I 形引脚小外型封装。

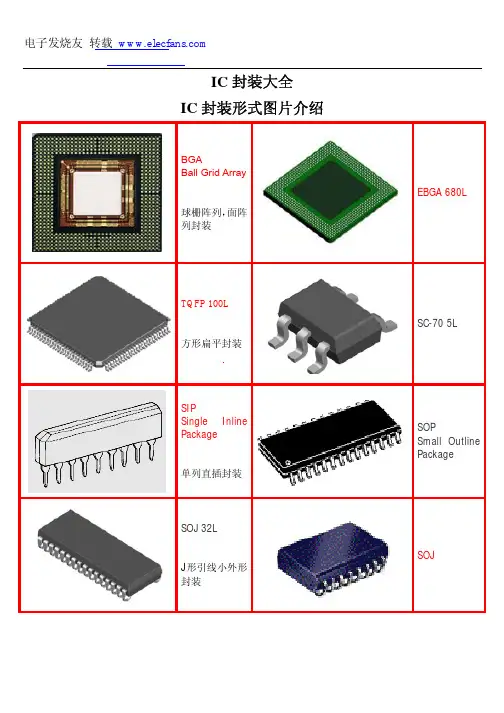

电子发烧友 转载 IC 封装大全 IC 封装形式图片介绍BGA Ball Grid Array EBGA 680L 球栅阵列, 面阵 列封装TQFP 100L SC-70 5L 方形扁平封装SIP Single Inline PackageSOP Small Outline Package单列直插封装SOJ 32L SOJ J 形引线小外形 封装转载SOP EIAJ TYPE II 14L SOT220 小外形封装T for 晶体管SSOP 16LSSOPTO-18TO-220TO-247TO-264电子发烧友 转载TO3TO52TO52TO71TO72TO78TO8TO92电子发烧友 转载TO93TO99TSOP Thin Small Outline PackageTSSOP or TSOP II Thin Shrink Outline PackageuBGA Micro Ball Grid ArrayZIP Zig-Zag Inline PackageuBGA Micro Ball Grid ArrayZIP Zig-Zag PackageInline电子发烧友 转载BQFP132C-Bend LeadCERQUAD Ceramic Quad Flat PackCeramic CaseGull LeadsWingTO263/TO268LBGA 160LPBGA 217L Plastic Ball Grid Array电子发烧友 转载SBGA 192LTSBGA 680LCLCCCPGA Ceramic Pin Grid ArrayDIP Dual Inline PackageDIP-tab Dual Inline Package with Metal Heatsink双列直插封装FBGAFDIP电子发烧友 转载FTO220Flat PackHSOP28ITO220ITO3pJLCCLCCLDCC电子发烧友 转载LGALQFPPCDIPPGA Plastic Pin Grid ArrayPLCC PQFP 有引线塑料芯 片栽体PSDIPLQFP 100L电子发烧友网 转载METAL QUAD 100LPQFP 100LQFP Quad PackageFlatSOT223SOT223SOT23SOT23/ SOT323SOT26/ SOT363电子发烧友网 转载SOT343SOT523SOT89SOT89LAMINATE TCSP 20L Chip Scale PackageTO252SO DIMM Small Outline Dual In-line Memory ModuleSIMM30 Single In-line Memory ModuleSocket 603FosterSOCKET 370 For intel 370 pin PGAPentium III &Celeron CPUPCI 64bit 3.3VPeripheralComponentInterconnect SIMM72 Single In-line Memory ModuleSOCKET462/SOCKET AFor PGA AMDAthlon &Duron CPUSOCKET 7 For intel Pentium & MMX Pentium CPUSLOT 1For intelPentium IIPentium III &Celeron CPUSLOT A For AMD Athlon CPUIC封装形式文字介绍1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

BYD BYD IC Process OverviewBYD BYD What is ICIC : Integrated Circuit通过一系列特定的加工工艺,将晶体管、二极管等有源器件和电阻、电容等无源器件,按照一定的电路互连,“集成”在一块半导体单晶片(如硅或砷化镓)上,封装在一个外壳内,执行特定电路或系统功能BYDBYD流程概述设计芯片检测单晶、外延材料掩膜版芯片制造过程封装测试系统需求总的IC 设计流程包括如下几点:线路设计(Circuit Design)晶圆制造(Wafer Fabricate)晶圆点测(Chip Probing, 简称CP)IC 封装(Assembly)成品测试(Final Testing, 简称FT)成品包裝(Packing)•集成电路的内部电路非门集成电路芯片的版图集成电路芯片内部电路的版图非门晶圆(Wafer)的形成过程BYD BYDBYD BYD 成型后晶圆BYD BYD 晶圆点测•晶圆点测的目的在于检测晶圆上晶粒的品质, 筛选出符合设计规格的晶粒PadBYD BYD 点测后的晶圆Good DieBad Die (InkedDie)BYD BYD为了电路保护,便于电力及讯号传输,利于散热,IC要进行封装IC的封装类型很多,下面只是简单的列举几种,按封装外型可分为如图片QFPTSOP BGA PBGACPGA LQFP PCDIP IC Package(IC的封装形式)BYDBYDBuild Your Dreams111.切割(Wafer Sawing)2. 粘晶(Die Attach)3. 焊线(Wire Bonding)4. 模压(Molding)5. 电镀(Plating)6. 剪切(Trimming)7. 印字(Marking)8. 成型(Forming)IC 封装步骤BYDBYDBuild Your Dreamswww .1ppt .comCompany LogoIC 结构图TOP VIEWSIDE VIEWLead Frame 引线框架Gold Wire 金线Die Pad 芯片焊盘Epoxy 银浆MoldCompound 环氧树脂BYDBYDBuild Your Dreams13成品测试成品测试的目的在于检测封装后的IC 品质, 筛选出电性符合规格以及外观良好的IC 成品。

引线框架是集成电路产品的重要组成部分,它的主要功能是为芯片提供机械支撑,并作为导电介质连接集成电路外部电路,传送电信号,以及与封装材料一起向外散发芯片工作时产生的热量。

随着大规模集成电路和超大规模集成电路的发展,集成电路正朝着高集成化、多功能化,线路的高密度化,封装的多样化和高性能化发展,其对引线框架材料要求也将越来越高。

下面就让广德均瑞电子科技为您简单解析,希望可以帮助到您!

集成电路的许多可靠性都是由封装性能决定的,引线框架为芯片提供电通路、散热通路、机械支撑等功能,IC封装要示其必须具备高强度、高导电、导热性好,以及良好的可焊性,耐蚀性、塑封性、抗氧化性等

引线框架材料经冲压法大批量生产成个系列的引线框架,因是大批量生产,在首检、中检、终检就尤其重要。

广德均瑞电子科技有限公司注册资金500万人民币,拥有不锈钢五金蚀刻加工独立法人环评资质,厂房面积2000平方米,6条不锈钢生产线,公司销售生产管理人员均超十年不锈钢蚀刻生产加工经验。

公司主要生产集成电路导线架;接地端子; 表面贴装零件(SMT)模板;精密线材布线钢板;编码器光栅;手机按键、RDIF天线、基板及金属配件;(VFD)栅网、陈列、支架;电极针(放电针);各类金属过滤网片/喇叭网片;眼镜框架;精密元器件掩模板;LCD背光模仁、钢版;显像管荫罩;电脑硬盘骨架;金属蚀刻发热片工艺等。

广德均瑞电子科技是以补强钢片为主打产品的蚀刻厂,ISO9001认证工厂,具有独立法人和环评资质,持有排污许可证的企业。

拥有6蚀刻加工生产线,免费提供FPC补强板工艺解决方案以及蚀刻行业资讯。