ISE入门教程更新

- 格式:pdf

- 大小:804.50 KB

- 文档页数:12

Xilinx 工具流程实验Xilinx 工具流程实验介绍本实验介绍ISE 软件结构向导管脚及区域约束编辑器和Xilinx 的工具流程目标完成此实验后你将会• • • 在ISE 的项目导航器中建立一个新的项目 利用结构向导建立一个DCM 例化 将例化置于设计之中• 利用软件的缺省选项实现一个设计• 利用PACE 工具指定管脚位置和区域位置过程注意当用Toolwire来执行实验时所有的软件程序文件和项目都在卷标 U:\ 下而不是在 C:\ 下建立一个新的项目第一步登录到ISE 项目导航器在C:\training\fund\labs\flow 子目录下建立一个名称为FlowLab 的新项目目标器件为xc2v40-4fg256设计流程可以是XST Verilog 或XST VHDL 你可以根据你的喜好选择相应的语言打开Xilinx ISE 5.1 软件从开始菜单里选择程序Programs→ Xilinx ISE5.1 →项目导航器Project Navigator在项目导航器中选择文件File →新项目New Project这时新项目窗口就会打开图 5b-1图5b-1. 新项目窗口对于项目名键入FlowLab对于项目位置使用按钮浏览到C:\training\fund\labs\flow单击 OK选择器件家族 Virtex 2选择器件为xc2v40封装为fg256速度等级为–4选择设计流程XST Verilog 或 XST VHDL单击 OK添加源文件第二步将子目录C:\training\fund\labs\flow\verilog 或C:\training\fund\labs\flow\vhdl 中所有源文件添加到FlowLab 项目中在项目导航器窗口中选择项目Project →添加源文件Add Source在添加已有源文件对话框图 5b-2中用下拉菜单浏览到C:\training\fund\labs\flow子目录然后进入 VHDL 或 Verilog子目录这取决于你在建立项目时所选择的流程选中所有文件单击第一个文件ch_fifo然后在按住Shift键的同时在添加已有源文件对话框中单击文件 pn_correlator图 5b-2. 添加已有源文件对话框点击打开Open对于VHDL 用户每个文件将出现选择源文件类型对话框对于除了ch_fifo_pack.vhd之外的的其它所有文件选择VHDL模块VHDL Module并点击OK对于ch_fifo_pack.vhd 选择VHDL封装VHDL Package并点击OK图5b-3. 选择源文件类型ISE将处理所有的文件并确定设计层次在项目导航器的右下角的进程条显示分析的进程添加的文件被分析后设计文件和层次将反映在项目窗口的源文件中用结构向导建立DCM例化 第三步用结构向导中的DCM向导创建一个名为MyDCM的新的源文件使用CLK0 CLK2X和LOCKED引脚 设定输入时钟频率为100MHz而其它选项为缺省设置在项目导航器中选择项目Project→新源文件New Source在新源文件窗口中选择结构向导(Architecture Wizard)并输入MyDCM作为文件名点击下一步 Next然后在下一个窗口中点击完成Finish在结构向导选择对话框中确定DCM向导已被选择并点击OK (图 5b-4).图 5b-4. 结构向导选择对话框注意Rocket I/O向导在此不可选这是因为我们的目标器件为Virtex-II而 Rocket I/O 能力仅在 Virtex-II PRO 器件中才有在Xilinx DCM 向导 – 通用设置窗口操作如下输入DCM例化名MyDCM_inst选中 CLK 2X输出框去除RST引脚的选择输入输入时钟频率为100 MHz然后点击下一步图 5b-5. Xilinx DCM 向导 – 通用设置窗口注意在DCM向导中指定频率的目的是让向导知道DCM是工作在高频模式还是低频模式基于输入的频率还可以计算输出的频率以确保是否在规定的频率范围之内另外如果选择CLKFX 输出的话输入频率还可以被用来计算在CLKFX上的输出频率以及计算估计的抖动在 Xilinx DCM向导中 – 时钟缓冲器窗口保持选项为缺省设置并点击完成注意一个新的文件(MyDCM.xaw)被添加到项目源文件窗口选择MyDCM.xaw文件进入当前源文件进程窗口双击查看HDL源文件并检查结构向导所产生的源代码将DCM例化置于设计(VHDL)中 第四步注意对于Verilog进入第五步将例化模板中的部件声明部分拷贝到ch_fifo.vhd中的合适位置然后将部件例化从例化模板中拷贝到ch_fifo.vhd 中的合适位置最后分配信号和修改代码以完成例化见本节的子步骤6和7将DCM例化置于设计中)保存修改好的文件在项目源文件窗口双击 ch_fifo.vhd 打开源代码选择文件MyDCM.xawMyDCM.xaw 选中后进入当前源文件进程窗口双击查看HDL例化模板在HDL 例化模板中复制部件声明这一部分 (从 COMPONENT MyDCM开始到 ENDCOMPONENT为止)并粘贴到 ch_fifo.vhd 的第四十行 (在部件fifo_2048x8之后在信号pn_lock, wr, wr_addr_srst : std_logic之前)在HDL 例化模板中复制部件例化这一部分 (从 Inst_MyDCM: MyDCM 直到文件结束为止) 并粘贴到 ch_fifo.vhd 的第五十四行在 begin之后在 pn_correlator_inst:pn_correlator之前按照如下方式完成例化MyDCM_inst: MyDCM PORT MAP(clkin_in => wr_clk_in,locked_out => lock ,clk2x_out => rd_clk,clk0_out => wr_clk);目前设计中有两个时钟信号没有用到DCM既然我们现在已使用了DCM我们需要修改和添加一些信号名以便例化能工作有三个地方需要修改a) 在ch_fifo 实体声明中将wr_clk改为wr_clk_in.b) 在 ch_fifo实体中将 rd_clk 信号删除既然该信号将要由DCM生成c) 在五十三行附近其它信号声明之后begin 行之前添加以下信号声明signal lock, rd_clk, wr_clk : std_logic;选择 文件File→ 保存Save 以保存文件将DCM置于设计(Verilog)中 第五步将部件例化从例化模板中拷贝到ch_fifo.v 中的合适位置最后分配信号和修改代码以完成例化见本节的子步骤4和5将DCM例化置于设计中)保存修改好的文件在项目源文件窗口双击 ch_fifo.vhd 打开源代码现在选择文件MyDCM.xawMyDCM.xaw 选中后进入当前源文件进程窗口双击查看HDL例化模板在HDL例化模板中复制部件声明这一部分 (从 MyDCM 开始一直到最后的 );结束 ) 并粘贴到ch_fifo.v 的第十行(在 wire [7:0] wr_data之后在pn_correlatorpn_correlator_inst之前)按照如下方式修改例化MyDCM MyDCM_inst (.CLKIN_IN(wr_clk_in),.LOCKED_OUT(lock),.CLK2X_OUT(rd_clk),.CLK0_OUT(wr_clk));目前设计中有两个时钟信号没有用到DCM既然我们现在已使用了DCM我们需要修改和添加一些信号名以便例化能工作有四个地方需要修改a) 在ch_fifo模块的端口列表中将 wr_clk 改为 wr_clk_inb) 同样在ch_fifo 模块的端口列表中, 删除 rd_clk端口c) 在 ch_fifo 的端口声明中从输入信号列表中删去 rd_clk信号因为此信号将由DCM产生d) 添加下列wire声明到第七行lock, rd_clk, wr_clk这样整个一行将变成wire pn_lock, wr, wr_addr_srst, lock, wr_clk, rd_clk;选择 文件File→保存Save以保存文件实现设计 第六步选择顶层设计文件ch_fifo.v/vhd, 实现设计.确认在项目源文件窗口中选择的是顶层的设计文件 (如图 5b-6). 顶层设计文件名为 ch_fifo.v/vhd图5b-6. 项目源文件窗口在当前源文件进程窗口如图5b-7中双击实现设计Implement Design注意工具将会执行实现设计所必需的所有进程在本实现中在进入实现之前工具将先执行综合图 5b-7. 当前源文件进程窗口实现期间的观测第七步注意进程条每一个进程旁边的状态符号和控制信息注意项目导航器窗口的右下角显示的是进程和设计实现的完成百分比如图5b-8图5b-8. 进程条在当前源文件进程窗口点击实现设计旁边的+展开实现步骤并查看进程我们称此为展开一个进程每一步完成之后在每一步旁边将出现一个符号 • • • 绿色的对号表示成功黄色的惊叹号表示有警告 红色的X 表示有错误对于这个特定的设计在每一步将会有一个黄色的惊叹号警告但这些警告无碍可以忽略当实现完成时项目导航器窗口底部的控制/信息窗口将会显示以下信息Done: completed successfully.打开PACE第八步在项目导航器中以建立一个新源文件的方式建立一个名为myucf 的UCF 文件然后从当前源文件进程窗口中打开PACE 工具用户约束User Constraints → 指定封装引脚Assign Package Pins在我们能够打开PACE 之前我们必须建立一个UCF 文件按照警告信息要建立一个UCF文件只要选择项目Project →新源文件New Source选择实现约束文件输入 myucf作为文件名点击下一步Next在下一个窗口中确定选择的是 ch_fifo点击下一步然后在最后一个窗口中点击完成如图5b-11)图 5b-11. 关联一个约束文件在当前源文件进程窗口展开用户约束然后双击指定封装管脚以打开PACE如果你不能看到这些进程确认在项目源文件窗口中选择的是ch_fifo测试PACE 第九步检查PACE中的四个窗口检测这些窗口怎样相互作用在PACE窗口中移动器件结构窗口和封装引脚窗口以使它们相邻图 5b-12. 器件结构窗口和封装引脚窗口在封装引脚窗口中点击用户I/O符号这些符号是中间为圆圈的框它们可能是不同颜色的方框圆圈后的不同颜色代表不同的I/O组注意在器件结构窗口中相应的引脚是如何被高亮的在设计层次窗口点击I/O引脚旁的的+号展开I/O引脚子目录你也可以展开全局逻辑和逻辑子目录来检查其中的内容这些名称来自于设计图 5b-13. 设计层次窗口注意设计对象列表窗口是如何跟着设计层次窗口中所选的子目录而变化的建立引脚和区域指配 第十步将所有rd_data<?>信号指定到BANK2上将DCM 元件放置在位置 DCM_X1Y1上将BRAM元件放置在块RAM 位置X1Y1上在设计层次窗口选择 I/O管脚子目录注意可以为每一个信号指配一个实际的引脚位置或为一个信号指定在特定组中的引脚范围在设计对象列表-I/O引脚窗口中将所有rd_data<?>信号指定到BANK2上可以这样操作选择一个信号在位置这一列点击框的右侧使用选择组的下拉菜单然后选择BANK 2图 5b-14. 设计部件列表 – I/O引脚窗口注意你可以在下拉菜单向下滚动时看到其它的位置选择 T, L, R, TL, TR, BL, BR,RT, RB, 等等这些词语是指组它们表示上部 组 硅片顶部的两组左部 组 硅片左部的两组左上部 组 硅片左上部的组等等这在你不了解组号但你又想将引脚指定到器件的那个区域是非常有帮助的在设计层次窗口点击全局逻辑文件夹在接下来的几步中我们将要将它们拖放到器件结构窗口中以便为这些部件指定特定的位置在设计对象列表窗口中选择DCM 元件并将其拖到器件结构窗口中将DCM 放置在右上方的DCM_X1Y1位置上如图所示图 5b-15. 指定一个位置在设计对象列表窗口中选择块RAM fifo_2048x8_inst_fifo_bram并将其拖到硅片的右上方的块RAM 位置X1Y1上图 5b-16. 指定一个位置选择文件 → 保存以保存引脚范围指配和DCM 及块RAM 布局选择 文件 → 退出以关闭PACE 工具在项目导航器的当前源文件进程窗口中在用户约束的下方双击编辑约束文本来查看通过PACE 工具在文件myucf.ucf 中所生成的约束查看文本版本的UCF 文件检查约束是否被写入文件图5b-17. 当前源文件进程窗口实现设计第十一步实现设计确保没有错误或与我们所建约束的冲突确认在项目源文件窗口中选择的是顶层的设计文件 (如图 5b-18)顶层设计文件名为 ch_fifo.v/vhd图 5b-18. 项目源文件窗口在当前源文件进程窗口如图5b-19中双击实现设计 Implement Design注意工具将会执行实现设计所必需的所有进程在本实现中在进入实现之前工具将先执行综合图5b-19. 当前源文件进程窗口结论本实验的目的是熟悉实现进程结构向导和PACE 的使用在本实验中我们在ISE 中将一个设计的主要阶段走了一遍建立项目添加源文件使用结构向导来改进和/或完成我们的代码指定管脚和区域位置实现整个设计。

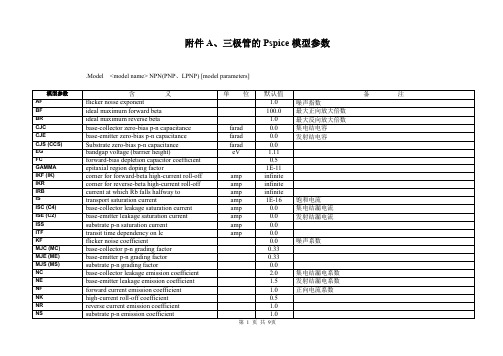

附件A、三极管的Pspice模型参数.Model <model name> NPN(PNP、LPNP) [model parameters]第 1 页共9页第 2 页共9页附件B、PSpice Goal Function第 3 页共9页附件CModeling voltage-controlled and temperature-dependent resistorsAnalog Behavioral Modeling (ABM) can be used to model a nonlinear resistor through use of Ohm抯 law and tables and expressions which describe resistance. Here are some examples.Voltage-controlled resistorIf a Resistance vs. Voltage curve is available, a look-up table can be used in the ABM expression. This table contains (Voltage, Resistance) pairs picked from points on the curve. The voltage input is nonlinearly mapped from the voltage values in the table to the resistance values. Linear interpolation is used between table values.Let抯 say that points picked from a Resistance vs. Voltage curve are:Voltage ResistanceThe ABM expression for this is shown in Figure 1.第 4 页共9页Figure 1 - Voltage controlled resistor using look-up tableTemperature-dependent resistorA temperature-dependent resistor (or thermistor) can be modeled with a look-up table, or an expression can be used to describe how the resistance varies with temperature. The denominator in the expression in Figure 2 is used to describe common thermistors. The TEMP variable in the expression is the simulation temperature, in Celsius. This is then converted to Kelvin by adding 273.15. This step is necessary to avoid a divide by zero problem in the denominator, when T=0 C.NOTE: TEMP can only be used in ABM expressions (E, G devices).Figure 3 shows the results of a DC sweep of temperature from -40 to 60 C. The y-axis shows the resistance or V(I1:-)/1A.Figure 2 - Temperature controlled resistor第 5 页共9页Figure 3 - PSpice plot of Resistance vs. Temperature (current=1A)Variable Q RLC networkIn most circuits the value of a resistor is fixed during a simulation. While the value can be made to change for a set of simulations by using a Parametric Sweep to move through a fixed sequence of values, a voltage-controlled resistor can be made to change dynamically during a simulation. This is illustrated by the circuit shown in Figure 5, which employs a voltage-controlled resistor.第 6 页共9页Figure 4 - Parameter sweep of control voltageThis circuit employs an external reference component that is sensed. The output impedance equals the value of the control voltage times the reference. Here, we will use Rref, a 50 ohm resistor as our reference. As a result, the output impedance is seen by the circuit as a floating resistor equal to the value of V(Control) times the resistance value of Rref. In our circuit, the control voltage value is stepped from 0.5 volt to 2 volts in 0.5 volt steps, therefore, the resistance between nodes 3 and 0 varies from 25 ohms to 100 ohms in 25 ohm-steps.第7 页共9页Figure 5 - Variable Q RLC circuitA transient analysis of this circuit using a 0.5 ms wide pulse will show how the ringing differs as the Q is varied.Using Probe, we can observe how the ringing varies as the resistance changes. Figure 6 shows the input pulse and the voltage across the capacitor C1. Comparing the four output waveforms, we can see the most pronounced ringing occurs when the resistor has the lowest value and the Q is greatest. Any signal source can be used to drive the voltage-controlled resistance. If we had used a sinusoidal control source instead of a staircase, the resistance would have varied dynamically during the simulation.第8 页共9页Figure 6 - Output waveforms of variable Q RLC circuit第9 页共9页。

打开XILINX的ISE,右键点击选择NEW SOURCENEW SOURCE中选择IP,写好NAME,点击下一步。

在下图中选择你要的IP核。

第一个是Block Memory生成设置向导;第二个是分布式 Memory生成设置向导;第四个是双口BLOCK RAM;是使用分布式ROM-如果你的ROM不是很大的话,而且内部BLOCK RAM 资源有限的情况下,使用分布式ROM可以为你节约不少BLOCK RAM,但是它会占用一些逻辑资源。

. 第五个是单口BLOCK RAM.选择你想要使用的IP核,(以选择向导为例)点击NEXT选择使用的Memory类型:如图设置Memory位宽和深度这里比较关键,要导入ROM的值。

这个文件就是你要放在ROM中的数据,文件的后缀名是.COE。

你可以自己建一个空的文本文件,然后把后缀名该为.COE即可。

文件内容的格式如下:MEMORY_INITIALIZATION_RADIX=10;MEMORY_INITIALIZATION_VECTOR=32767,32766,32766,32765,32764,32763,32761,32759,32757,……32754;注意:第一行定义文件中的数据采用什么进制。

可以使用10进制,2进制,16进制,数据大小不能超过你定义的数据宽度。

第二行照抄。

第三行开始就是数据了,每个数据用逗号","隔开,可以不分行,建议分行写,便于统计个数。

最后一个数据后用分号";"结束。

数据的个数必须和你定义的数据深度相同,否则会出错。

写好这个文件后,保存。

导入.coe文件后,如果没有错误,可以点击旁边的show查看数据。

点击next,最后查看设置的信息现在,可以点击finishi,产生IP。

产生的代码中有个.MIF文件,就是ROM的数据的二进制文件。

其中的.V 文件或.VHD就是生成的可综合的代码。

如上图的ROM_COS.XCO,选择它,双击VIEW HDL FUNCTIONAL MODEL就可查看Verilog代码。

10ISE14.7和modelsim10.5关联编译库今天准备在ISE14.7中调⽤PLL的IP核,搞⼀下时钟的分频和倍频。

可在我做好pll的IP核后,我直接⽤ise⽣成了⼀个仿真⽂件,只需要修改下例化模块名和加⼀个时钟就⾏勒。

问题:但怎么在ISE14.7中调⽤Modelsim勒?百度找了很多资料发现,要想调⽤:⾸先得先对ISE编译库进⾏编译。

然后就是关联ISE 和modelsim。

⽹上的很多教程都是⽼版本的,没有找到10.5版本,同时在很多细节上也和实际操作不⼀样,怕⼤家⼊坑折磨⾃⼰⼀段时间。

所以我就⾃⼰原创⼀篇教程,能够帮⼤家解决问题,同时记录下我的学习过程哈。

我是最新的10.7,所以我⼜安装勒10.5版本的modelsim。

⾄于怎么破解modelsim,可以看看我的另⼀篇博客,有详细的介绍及问题汇总解决哈。

还有在操作中发现存在很多细节不⼀样,我成功⼊了很多坑,折腾了好⼏遍,看不同的教程尝试解决办法,成功真不容易哈。

下⾯上详细的关联教程:第⼀步在开始菜单中,找到Xilinx design tools的任⼀⽂件,选择打开⽂件位置后如下图:第⼆步,就到了设置modelsim的安装包位置和32位或64位选择,⼤家根据⾃⼰的软件位置和电脑来选,我选中的如红⾊标注,在next。

如下图所⽰:第三步,选择仿真语⾔,两种语⾔⼤家都选哈,就下⼀步第四步,如下图所⽰:选择芯⽚的型号,这个看⼤家的需要和开发板芯⽚型号,我的型号是Spartan6,其他都⽤不到呀:第五步,选择编译库和时序仿真,去掉了EDK,如下图第六步,选择编译库路径,默认就⾏,如下图第七步:编译库后,没有错误,且出现了下⾯的⼏个库,说明编译库成功了哈第⼋步:点击finish即可。

第九步:从上⼀步,我们编译库成功了,接着就是对ISE14.7和modelsim10.5的ini⽂件操作勒!先是ISE14.7如下图所⽰第⼗步:如下图,⽤notepad++打开上⼀步的ISE14.7的inti⽂件后,复制下⾯的部分第⼗⼀步:直接把上⼀步ise14.7的复制的部分粘贴到下⾯位置,再保存退出就⾏第⼗⼆步:设置仿真软件的版本,如下图所⽰第⼗三步:按照下图的操作,在ISE14.7中调出来Modelsim10.5。

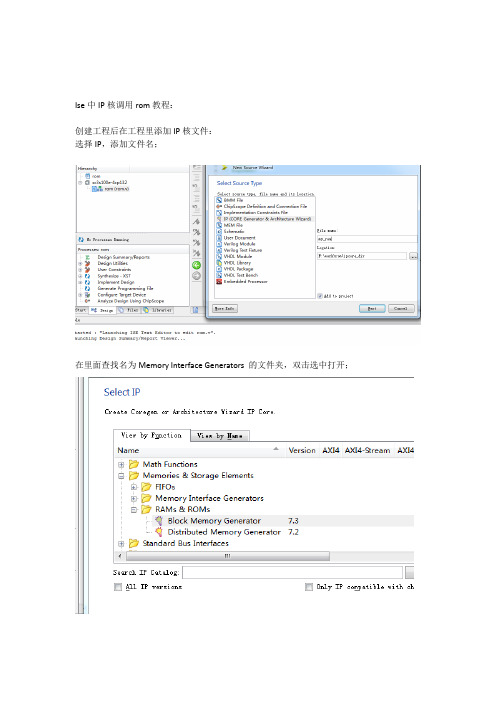

Ise中IP核调用rom教程:

创建工程后在工程里添加IP核文件:

选择IP,添加文件名;

在里面查找名为Memory Interface Generators 的文件夹,双击选中打开;

打开的界面如下:

在上边的Memory Type 里面选择single Port ROM

点击next;

输入rom的大小

在图中选择LOad Init File,添加rom的coe文件

点击Generate 生成IP核;

将生成的IP核打开,将生成的文件在设计module中实例化就可以使用,读出rom中的数据就行。

Coe文件内部:

Coe文件的制作方法:

一般的算法相关的coe可以通过matlab 生成,但是对于一些照片的话,网上有相关的类似的制作mif文件的软件,所谓mif文件和coe文件的本质是相同的,具体差别有兴趣的可

以自己在网上了解,将制作的mif文件的内容提取出来,做成coe,

还有一个方法生成mif文件就是在quartus 软件里面创建然后手动输入内容,但是工作量比较大,考虑到工作效率,不建议采用。

Mif文件:

通过Excel表格提取数据,将;转化为,但是最后一位是;前边的修改下即可;这样一个coe就做好了,大家可以动手试试,这里只是讲了一个大概流程,自己动手做了印象才深刻,尽情的显示大家喜爱的图片吧。

TotoiseSVN(中文名:小乌龟)使用教程第一部分TotoiseSVN介绍TortoiseSVN是Subversion(简称:SVN)版本控制系统的一个免费开源客户端,可以超越时间的管理文件和目录。

文件保存在中央版本库,除了能记住文件和目录的每次修改以外,版本库非常像普通的文件服务器。

你可以将文件恢复到过去的版本,并且可以通过检查历史知道数据做了哪些修改,谁做的修改。

这就是为什么许多人将Subversion和版本控制系统看作一种“时间机器”。

第二部分TotoiseSVN下载下载地址:https:///downloads.html推荐从官网下载,软件分为32位和64位版本,下载时请根据自己的系统位数进行下载;图2.1也可以在下载页面选择合适的语言版本下载。

第三部分TotoiseSVN安装安装过程:1、下载软件后,双击程序进行安装,点击“Next”;2、在许可证协议页面,选择“I Accept the terms in the License Agreement”,点击“Next”;图3.13、在自定义选项页面,可以选择安装目录,也可以直接点击“Next”进行安装;4、点击“Install”开始安装;图3.25、安装完成后,点击“Finsh”;第四部分签入源代码到SVN服务器假如我们使用Visual Studio在文件夹StartKit中创建了一个项目,我们要把这个项目的源代码签入到SVN Server上的代码库中里,首先右键点击StartKit文件夹,这时候的右键菜单如下图所示:图4.1点击Import,弹出下面的窗体,其中是服务器名,svn 是代码仓库的根目录,StartKit是我们在上个教程中添加的一个代码库:说明:左下角的CheckBox,在第一次签入源代码时没有用,但是,在以后你提交代码的时候是非常有用的。

图4.2点击OK按钮,会弹出下面的窗体,要求输入凭据:图4.3在上面的窗体中输入用户名和密码,点击OK按钮:图4.4如上图所示,好了,源代码已经成功签入SVN服务器了。

ISE DDR3 IP核创建及使用文档关键字:ISE DDR3 IP核DDR目录IP核创建 (2)1.打开CORE Generator (2)2.新建一个IP CORE Generator Project (2)1.新建project (2)2.输入一个project name (3)3.配置project options: (3)4.配置Generation (4)5.点击“OK”完成IP CORE generator project 的创建 (4)3.创建一个DDR3 IP核 (4)1.选择我们需要创建的IP核,有两种方法 (4)2.观察关于ip核的文档 (6)3.选择version3.9版本的ip核进行创建 (6)4.修改IP核里面的文件 (11)1.在ip core generator project所在的文件夹里找到mig_39(新建IP核的名字)文件夹 (11)2.打开example_design->rtl (12)3.适用ML605的IP核文件做了如下修改 (12)4.修改完之后的IP核就可以按照所给文档的说明正确使用了! (13)IP核的使用 (13)1.基本使用方法 (13)2.注意事项 (13)IP核创建1.打开CORE Generator如下图:2.新建一个IP CORE Generator Project 1.新建project2.输入一个project name命名随意,此处以mig命名3.配置project options:此处以ML605开发板为例配置,具体配置根据使用环境配置。

此处的配置很重要,并不是所有的IP核创建之后都可以在所有的板子跑,有些板子是不支持某些IP核的。

4.配置Generation此处需要配置两个地方:·design entry:本文配置verilog·vendor:本文配置ISE5.点击“OK”完成IP CORE generator project 的创建3.创建一个DDR3 IP核1.选择我们需要创建的IP核,有两种方法·方法一,选择View by function,如下图:·方法二,选择view by name,如下图:·输入MIG后,就过滤掉其他的ip核,找到你想要的ip核·也可以看到本软件上面包含有两个IP核,一个是适用V6和S6系列的,另外一个是使用V7系列的,由于我们project配置的是V6芯片,所以只有version3.9的可用2.观察关于ip核的文档这些文档有助于你对这个IP核的理解,包括它适用的芯片,设计的文档等等。

SVN客户端使用教程一、TotoiseSVN的基本使用方法1、签入源代码到SVN服务器假如我们使用Visual Studio在文件夹StartKit中创建了一个项目,我们要把这个项目的源代码签入到SVN Server上的代码库中里,首先右键点击StartKit 文件夹,这时候的右键菜单如下图所示:点击Import,弹出下面的窗体,其中/是服务器名,本环境中在内网的访问地址为https://172.16.1.159:8443/svn/或https://ncse-5042:8443/svn/外网访问地址为https://210.76.109.99:8443/svn。

svn是代码仓库的根目录,StartKit是我们在上个教程中添加的一个代码库:说明:左下角的CheckBox,在第一次签入源代码时没有用,但是,在以后你提交代码的时候是非常有用的。

点击OK按钮,会弹出下面的窗体,要求输入凭据:在上面的窗体中输入用户名和密码,点击OK按钮:如上图所示,好了,源代码已经成功签入SVN服务器了。

这时候团队成员就可以迁出SVN服务器上的源代码到自己的机器了。

2、签出源代码到本机在本机创建文件夹StartKit,右键点击Checkout,弹出如下图的窗体:在上图中URL of Repository:下的文本框中输入svn server中的代码库的地址,其他默认,点击OK按钮,就开始签出源代码了。

说明:上图中的Checkout Depth,有4个选项,分别是迁出全部、只签出下一级子目录和文件、只签出文件、只签出空项目,默认的是第一项。

上面的例子中,我们也可以使用web的方式访问代码库,在浏览器中输入/svn/StartKit/(本环境为https://210.76.109.99:8443/svn/xx/)这时候也会弹出对话框,要求输入用户名和密码,通过验证后即可浏览代码库中的内容。

搞定!源代码已经成功签出到刚才新建的StartKit目录中。

ISE整体开发流程:建工程→编写工程代码→检查语法错误→行为仿真→综合→

管脚约束→实现→时序仿真→生成bit流文件→下载到板子上调试;

实验是用ISE10.1做的,与ISE9.1不同的地方在文中也有相关说明。

一:建工程

1. 工程命名

file→new projiect(如下图所示:在工程名处填:jishuqi 资源类型选:HDL)

2. 器件类型选择及仿真综合工具、硬件描述语言设置

点击Next,出现如下图所示界面:

图中设置的有:Family:virtex2P; Device :XC2VP30;Package:FF896;Speed:-7

(这个是根据VIRTEX2P开发板设置的数据,不同的开发板设置的数据不一样)。

3.完成工程的建立

.一直点击next,出现如下图界面后,点Finish完成工程的建立:

二.编写HDL代码(工程此部分是在Implementation下完成的)

1.在Sources区域点击右键选择new source,出现如下图所示的界面,按照如下

图设置,然后一直点Next,一直到Finish完成代码文件界面:

3. 接下来开始HDL代码编写,这里是一个简单的十进制计数器的编写:

代码编写好后,点击保存,然后检查看编写代码是否有错误,如上图所示,Check

Syntax 点击检查后是绿色的勾,则代码没有语法错误,可以进行下一步功能仿

真;

module jishuqi(clk,rst,q);

input clk,rst;

output[3:0] q;

reg[3:0] q;

always@(posedge clk)

begin

if(rst==0)

q<=4'b0;

else

begin

if(q==4'b1010)

q<=0;

else

q<=q+1;

end

end

endmodule

三、行为(功能)仿真

1.同样在Sources 区域右键添加New Source 如下图所示,添加图形仿真文件:

2.一直点Next,最后finish掉到如下图所示的,时钟设置界面:

如上图所示:1.选择 Rising Edge 时钟上升沿有效;2.选择对应设计的时钟信号;

3.设置clk的频率,高低电平持续时间;4.设置仿真时间为1000ns;

3.点Finish进入波形编辑界面,如下图所示:(rst是要编辑的波形)

编辑之后波形如下所示:

点击保存;

3.如下图选择:在Sources for 选择 Behavioral Simulations

4.依次点击1,2,然后双击,待运行后,最后出现如下图的仿真结果:

到此时完成了行为仿真。

四、综合

先单击1,然后双击2,待运行正确后,再双击运行3则可以看到右边用HDL

描述出来的RTL电路,如下图所示:

五、管脚约束

先点击1,之后双击2,再在3区域设置Viertex2P开发板对应的时钟管脚设置(clk

设置为aj15),设置完成后保存!

下面是ISE9.1的界面:

六、实现

实现是把设计的电路映射到FPGA中,生成相应的工程文件;其包括三个步

骤:翻译、映射、布局布线。

操作:先单击1,然后双击Implement Design,出现如下图中2处1则正确!

七、时序仿真

时序仿真是看设计的时序是否符合要求:

操作:现在1处选择后仿真,然后单击2,再双击3,待运行后出现了右边的仿

真结果:

如上图所示,可以分析时序仿真与行为仿真的不同:时序仿真有延时t,还有

4处的毛刺!

八、生成比特流文件(配置FPGA文件)

双击2处,生成编程文件:

九、配置FPGA

双击红线处,进行相应的IMPACT配置,并连接好开发板后才能配置到FPGA

中。

NOTE:

文中第九节配置FPGA具体怎么配置没有提到,其涉及到其他软件的使用,此

次主要是熟悉ISE软件;这个将在大家后续进一步学习中会用到!

此为我以我的理解写的一个简单的教程,主要目的是让刚入门的同学熟悉用ISE

开发FPGA的一个整体流程,所以比较具体但不深入,还有很多细节的东西,希

望大家在学习的时候注意,多查下资料和书本,这方面的资料很多!