逐次逼近式AD转换原理

- 格式:docx

- 大小:47.51 KB

- 文档页数:2

STC12C5A60S2中的AD转换逐次逼近原理AD 里面包含da,当输入电压Vin时,da的最高位是1,即为0.5Vref与输入信号比较,如果输入大于0.5Vref则比较器输出为1,同时da的最高位为1,反之DA最高位则为0,通过8次比较后得到8个01数据即完成ad转换。

现在说下程序中用到stc12单片机两个寄存器ADC_CONTR;主要用来配置ad启动的工作模式;还有个result的寄存器程序中的注意点:配置完ADC_CONTR后要延时4个时钟周期先把程序附上#include "stc12.h"#include "intrins.h"#include "ad.h"uint ad;#define ADC_POWER 0X80 //ADC最高位给adc部分供电,类似于片选#define ADC_START 0X08 //模数转换启动控制位#define ADC_FLAG 0x10 //ad转换需要时间,这个是转换完成标志位#define ADC_SPEEDLL 0X00 //540 clock#define ADC_SPEEDL 0X20 //360 clock#define ADC_SPEEDH 0X40 //180 clock#define ADC_SPEEDHH 0X60 //90 clockuchar ADCresult(uchar aa) //这里的参数是哪个口来ad转换{P1ASF=0X01; //这里的选择和用哪一个P1口作为ad采样ADC_CONTR=ADC_POWER|ADC_SPEEDLL|ADC_START|aa;//ADC_CONTR=0X88|aa;_nop_();_nop_();_nop_();_nop_();//设置ADC_CONTR寄存器后需加4个CPU时钟周期的延时,才能保证值被写入ADC_CONTR寄存器while (!(ADC_CONTR & ADC_FLAG)); //等待ADC_CONTR,这里的ADC_FLAG相当于一个常数,不是寄存器里面的某个位//while(!ADC_FLAG);//ADC_FLAG=0;ADC_CONTR &= ~ADC_FLAG; //Close ADC 将标志位清零等待下次硬件置1ad=(ADC_RES<<2)+ADC_RESL; //打开10位AD采集功能如果用8位AD 屏掉这句把下一句改为Vo=(float)(ADC_RESL)*500/256; 即可//ADC_RES结果寄存器的高2位;ADC_RES结果寄存器的低8位ad=(float)(ad)*5*100/1024; //Return ADCresult(为显示整数,这里将电压值扩大了十倍)//10位AD采集即2的10次方满值为1024 这里用1024表示5伏的电压//那么用采集到的数量值除以1024 在乘以5 得到的值就是采集的电压数值//这里又*100 是为了扩大100倍显示小数位//ADC_RES*(5/256)为采集的电压值然后扩大10倍便于计算return ad;}这里只是个ad.c源文件,这里有几个问题想说一下1.怎么知道是10位还是8位的ad结果;你可以在ADCresult(uchar aa)最前面加一条AUXR1&=0x04;什么意思呢,转换结果的低2位放在ADC_RES,高8位ADC_RESL 中2为什么不用//while(!ADC_FLAG);//ADC_FLAG=0;这两条因为ADC_FLAG相当于常量前面用宏定义而头文件里只有ADC_CONTR的地址映射;但是如果在头文件中用sbit ADC_FLAG=ADC_CONTR^4会出现错误,具体原因还不清楚先说到这吧。

逐次逼近式AD转换原理逐次逼近式AD转换原理是一种常见的模拟信号转换为数字信号的方法,被广泛应用于数字信号处理、通信、仪器仪表和控制系统等领域。

该方法通过将模拟信号与一系列逐步增加或递减的参考电压进行比较,最终输出与模拟信号相对应的数字码。

下面将详细介绍逐次逼近式AD转换原理。

首先,模拟信号经过输入电路进入比较器。

比较器将模拟信号与DAC 输出的数字信号进行比较,判断两者的大小关系。

如果模拟信号大于DAC 输出的数字信号,则比较器输出高电平,否则输出低电平。

接下来,将比较器输出的电平信号进入一组逻辑电路,该逻辑电路根据比较器输出的高低电平信号,控制DAC输出电压的大小。

此时,DAC的输出电压与参考电压比较接近,但还不完全相等。

然后,将DAC输出的数字信号转换为模拟信号,通过反馈回路与模拟信号进行比较。

如果DAC输出的数字信号过小,则逻辑电路增加DAC的输入。

反之,如果DAC输出的数字信号过大,则逻辑电路减小DAC的输入。

通过逐步调整,DAC的输出电压逐渐逼近模拟信号大小。

最后,当DAC输出的数字信号与模拟信号足够接近时,逻辑电路停止对DAC输入的调整,DAC的输出被强制锁定。

此时,输出寄存器将DAC输出的数字码存储,即完成了模拟信号到数字信号的转换。

逐次逼近式AD转换器的工作原理是通过多次逼近逼近模拟信号的大小,以获取更高的转换精度。

其中,逼近的过程是通过比较器和逻辑电路的协同工作来实现的。

比较器用于比较模拟信号与DAC输出的数字信号的大小,并反馈给逻辑电路。

逻辑电路则根据比较器输出的高低电平信号,调整DAC的输入以逼近模拟信号。

然而,逐次逼近式AD转换器也存在一些缺点。

首先,由于需要多次逼近,转换速率相对较慢。

其次,由于逼近过程依赖于模拟信号的性质,因此对于非线性或非稳定信号,该转换器的精度可能受到影响。

此外,逐次逼近式AD转换器的精度也受限于比较器和DAC的性能。

总结起来,逐次逼近式AD转换原理是一种将模拟信号转换为数字信号的常见方法,通过比较器和逻辑电路的协同工作,逐步逼近模拟信号的大小,以获取更高的转换精度。

模数转换器其本质就是一个编码的过程,由于传输到数模转换器的自然信号随着时间的变化而变化。

为了实现对模拟信号的处理和储存,我们必须对信号进行编码,为此,我们选择了最基本,也是最实用的编码——2进制编码。

首先,模拟信号通过滤波器,过滤掉高频信号,得到我们需要的信号。

然后经过采样和保持电路采集模拟信号当中某一段时间的信号值,这一段时间一方面决定了采样频率的大小,另外一方面也是后面的电路结构所消耗掉的总的时间。

这段时间内得到的采样值传输到比较器当中,比较器的另外一个输入信号由数模转换器和寄存器共同作用来给出。

比如我们这次的电源电压是2V,比较器的输入电压范围是0~2V,因此采样与保持电路的电压输入范围也是0~2V。

我们的比较精度是10位,也就是比较器要在一个采样周期内进行10次比较。

最开始的时候,寄存器将这10位的2进制数字信号都置0。

然后进行第一位,也就是最高位的比较,这时数模转换器将输入电压范围的中值,也就是1V,传输给比较器的一个输入端口,比较器的另外一个输入端口来自采样与保持电路。

当采样电压高于中值1V时,寄存器的最高位由0变为1,同时逻辑控制单元控制数模转换器的下一个输入到比较器端口的电压为1V到2V的中值处,也就是1.5V,将1.5V传入到比较器的输入端口,和采样信号进行比较,输出第二位的数字信号。

以此类推,可以得到10位的数字信号。

当采样电压低于中值电压1V时,寄存器的最高位仍然为0,同时逻辑控制单元控制数模转换器的下一个输入到比较器端口的电压为0~1V的中值处,也就是0.5V,将0.5V穿入到比较器的输入端口,和采样信号进行比较,输出第二位的数字信号。

以此类推,进行10次这样的比较便可以得到10位编译模拟信号的数字信号。

A/D转换器A/D转换器是用来通过一定的电路将模拟量转变为数字量。

模拟量可以是电压、电流等电信号,也可以是压力、温度、湿度、位移、声音等非电信号。

但在A/D转换前,输入到A/D 转换器的输入信号必须经各种传感器把各种物理量转换成电压信号。

A/D转换后,输出数字信号可以有8位、10位、12位和16位等。

AD转换器的工作原理主要介绍3种:逐次逼近法双积分法电压频率转化法1 逐次逼近法:逐次逼近式A/D是比较常见的一种A/D转换电路,转换的时间为微秒级。

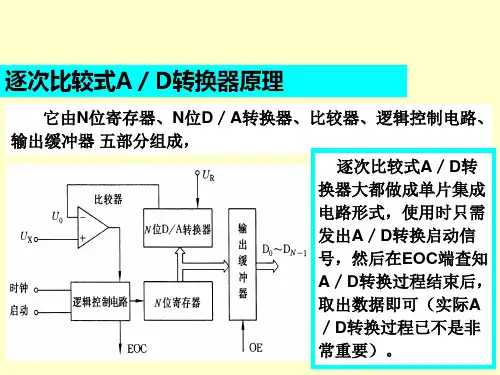

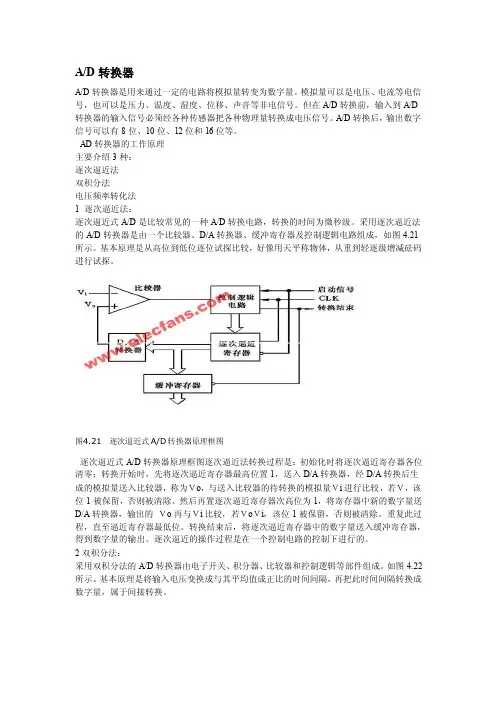

采用逐次逼近法的A/D转换器是由一个比较器、D/A转换器、缓冲寄存器及控制逻辑电路组成,如图4.21所示。

基本原理是从高位到低位逐位试探比较,好像用天平称物体,从重到轻逐级增减砝码进行试探。

图4.21 逐次逼近式A/D转换器原理框图逐次逼近式A/D转换器原理框图逐次逼近法转换过程是:初始化时将逐次逼近寄存器各位清零;转换开始时,先将逐次逼近寄存器最高位置1,送入D/A转换器,经D/A转换后生成的模拟量送入比较器,称为Vo,与送入比较器的待转换的模拟量Vi进行比较,若V,该位1被保留,否则被清除。

然后再置逐次逼近寄存器次高位为1,将寄存器中新的数字量送D/A转换器,输出的Vo再与Vi比较,若VoVi,该位1被保留,否则被清除。

重复此过程,直至逼近寄存器最低位。

转换结束后,将逐次逼近寄存器中的数字量送入缓冲寄存器,得到数字量的输出。

逐次逼近的操作过程是在一个控制电路的控制下进行的。

2双积分法:采用双积分法的A/D转换器由电子开关、积分器、比较器和控制逻辑等部件组成。

如图4.22所示。

基本原理是将输入电压变换成与其平均值成正比的时间间隔,再把此时间间隔转换成数字量,属于间接转换。

图4.22 双积分式A/D转换的原理框图双积分法A/D转换的过程是:先将开关接通待转换的模拟量Vi,Vi采样输入到积分器,积分器从零开始进行固定时间T的正向积分,时间T到后,开关再接通与Vi极性相反的基准电压VREF,将VREF输入到积分器,进行反向积分,直到输出为0V时停止积分。

一、逐次逼近式AD转换器与计数式A/D转换类似,只是数字量由“逐次逼近寄存器SAR”产生。

SAR使用“对分搜索法”产生数字量,以8位数字量为例,SAR首先产生8位数字量的一半,即10000000B,试探模拟量Vi的大小,若Vo>Vi,清除最高位,若Vo<Vi,保留最高位。

在最高位确定后,SAR又以对分搜索法确定次高位,即以低7位的一半y1000000B(y为已确定位) 试探模拟量Vi的大小。

在bit6确定后,SAR以对分搜索法确定bit5位,即以低6位的一半yy100000B(y为已确定位) 试探模拟量的大小。

重复这一过程,直到最低位bit0被确定,转换结束。

转换过程:(1)首先发出“启动信号”信号S。

当S由高变低时,“逐次逼近寄存器SAR”清0,DAC输出Vo=0,“比较器”输出1。

当S变为高电平时,“控制电路”使SAR开始工作。

(2)SAR首先产生8位数字量的一半,即10000000B,试探模拟量的Vi大小,若Vo>Vi,“控制电路”清除最高位,若Vo<Vi,保留最高位。

(3)在最高位确定后,SAR又以对分搜索法确定次高位,即以低7位的一半y1000000B(y 为已确定位) 试探模拟量Vi的大小。

在bit6确定后,SAR以对分搜索法确定bit5位,即以低6位的一半yy100000B(y为已确定位) 试探模拟量Vi的大小。

重复这一过程,直到最低位bit0被确定。

(4)在最低位bit0确定后,转换结束,“控制电路”发出“转换结束”信号EOC。

该信号的下降沿把SAR的输出锁存在“缓冲寄存器”里,从而得到数字量输出。

从转换过程可以看出:启动信号为负脉冲有效。

转换结束信号为低电平。

我觉得,这有点像数学中的二分法,如给一个数a,先用8'b1000000(设为b)与a相比较,如果a大于b,则保留最高位1,即原来的范围变成了0-7'b1111111(第8位已确认)。

一、逐次逼近式AD转换器与计数式A/D转换类似,只是数字量由“逐次逼近寄存器SAR”产生。

SAR使用“对分搜索法”产生数字量,以8位数字量为例,SAR首先产生8位数字量的一半,即B,试探模拟量Vi的大小,若Vo>Vi,清除最高位,若Vo<Vi,保留最高位。

在最高位确定后,SAR又以对分搜索法确定次高位,即以低7位的一半y1000000B(y为已确定位) 试探模拟量Vi的大小。

在bit6确定后,SAR以对分搜索法确定bit5位,即以低6位的一半yy100000B(y为已确定位) 试探模拟量的大小。

重复这一过程,直到最低位bit0被确定,转换结束。

转换过程:

(1)首先发出“启动信号”信号S。

当S由高变低时,“逐次逼近寄存器SAR”清0,DAC输出Vo=0,“比较器”输出1。

当S变为高电平时,“控制电路”使SAR开始工作。

(2)SAR首先产生8位数字量的一半,即B,试探模拟量的Vi大小,若Vo>Vi,“控制电路”清除最高位,若Vo<Vi,保留最高位。

(3)在最高位确定后,SAR又以对分搜索法确定次高位,即以低7位的一半y1000000B(y为已确定位) 试探模拟量Vi的大小。

在bit6确定后,SAR以对分搜索法确定bit5位,即以低6位的一半yy100000B(y为已确定位) 试探模拟量Vi的大小。

重复这一过程,直到最低位bit0被确定。

(4)在最低位bit0确定后,转换结束,“控制电路”发出“转换结束”信号EOC。

该信号的下降沿把SAR的输出锁存在“缓冲寄存器”里,从而得到数字量输出。

从转换过程可以看出:启动信号为负脉冲有效。

转换结束信号为低电平。

?

?

我觉得,这有点像数学中的二分法,如给一个数a,先用8'b1000000(设为b)与a相比较,如果a大于b,则保留最高位1,即原来的范围变成了0-7'b1111111(第8位已确认)。

之后的过程都是这样,重复执行就可以了。

根据以上理论,举个例子,例如满量程应该是5V,所以,第一次DA输出,输入电压与比较,输入电压大,故而取之间,即最高位保留1。

然后在新的范围内取中间电压,即,依此类推。