最新0004:DSP原理及应用——第2章DSP芯片的硬件结构21—23节讲稿

- 格式:ppt

- 大小:402.00 KB

- 文档页数:41

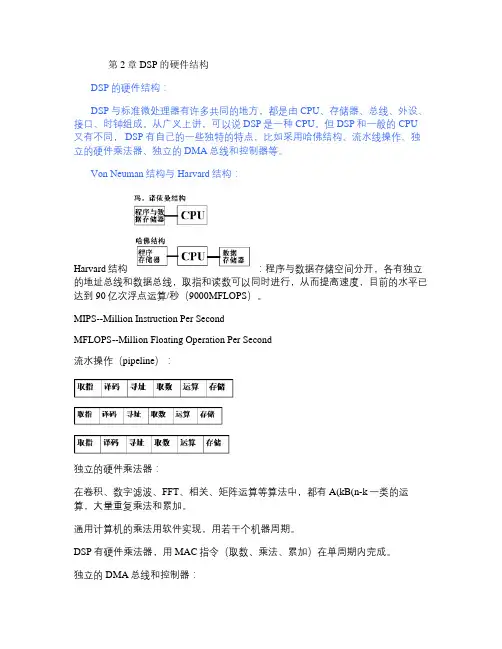

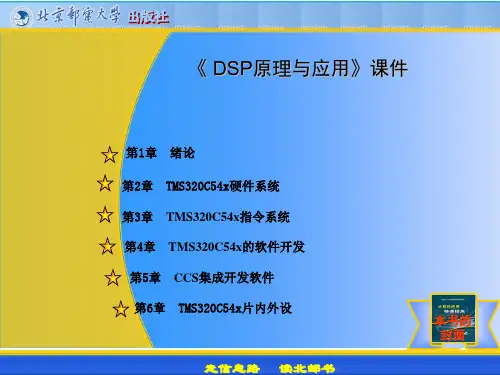

第2章DSP的硬件结构DSP的硬件结构:DSP与标准微处理器有许多共同的地方,都是由CPU、存储器、总线、外设、接口、时钟组成。

从广义上讲,可以说DSP是一种CPU。

但DSP和一般的CPU 又有不同, DSP有自己的一些独特的特点,比如采用哈佛结构、流水线操作、独立的硬件乘法器、独立的DMA总线和控制器等。

Von Neuman结构与Harvard结构:Harvard结构:程序与数据存储空间分开,各有独立的地址总线和数据总线,取指和读数可以同时进行,从而提高速度,目前的水平已达到90亿次浮点运算/秒(9000MFLOPS)。

MIPS--Million Instruction Per SecondMFLOPS--Million Floating Operation Per Second流水操作(pipeline):独立的硬件乘法器:在卷积、数字滤波、FFT、相关、矩阵运算等算法中,都有A(kB(n-k一类的运算,大量重复乘法和累加。

通用计算机的乘法用软件实现,用若干个机器周期。

DSP有硬件乘法器,用MAC指令(取数、乘法、累加)在单周期内完成。

独立的DMA总线和控制器:有一组或多组独立的DMA总线,与CPU的程序、数据总线并行工作,数据的传递和处理可以独立进行,DMA内部总线与系统总线完全分开,避开了总线使用上的瓶颈。

在不影响CPU工作的条件下,DMA速度已达800Mbyte/s。

CPU:通用微处理器的CPU由ALU和CU组成,其算术运算和逻辑运算通过软件来实现,如加法需要10个机器周期,乘法是一系列的移位和加法,需要数十个机器周期。

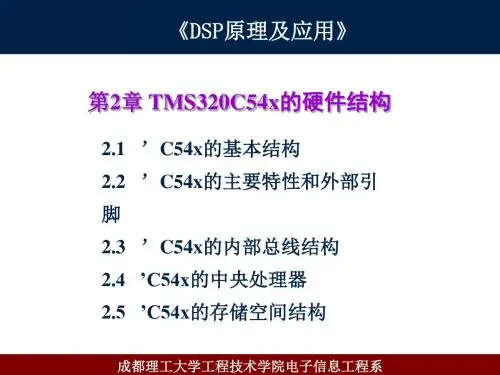

DSP的CPU设置硬件乘法器,可以在单周期内完成乘法和累加.移位:通用微处理器的移位,每调用一次移位指令移动1-bitDSP可以在一个机器周期内左移或右移多个bit,可以用来对数字定标,使之放大或缩小,以保证精度和防止溢出;还可以用来作定点数和浮点数之间的转换.溢出:通用CPU中,溢出发生后,设置溢出标志,不带符号位时回绕,带符号位时反相,带来很大的误差DSP把移位输出的最高位(MSB)存放在一个位检测状态寄存器中,检测到MSB=1时,就通知下一次会发生溢出,可以采取措施防止.数据地址发生器(DAG):在通用CPU中,数据地址的产生和数据的处理都由ALU来完成在DSP中,设置了专门的数据地址发生器(实际上是专门的ALU),来产生所需要的数据地址,节省公共ALU的时间.外设(peripherals):时钟发生器(振荡器与PLL)定时器(Timer)软件可编程等待状态发生器通用I/O同步串口(SSP)与异步串口(ASP)JTAG扫描逻辑电路(IEEE 1149.1标准便于对DSP作片上的在线仿真和多DSP条件下的调试’C54x的内部结构:中央处理器CPU 、内部总线控制、特殊功能寄存器、数据存储器RAM 、程序存储器ROM、I/O功能扩展接口、串行口、、主机通信接口HPI、定时系统、中断系统。

DSP原理及应用第二章DSP的硬件结构总结(精)【例2.4.1】累加器A=FF01234567H,执行带移位的STH 和STL指令后,求暂存器T和A的内容。

2.4.3桶形移位寄存器:TMS320C54x的40位桶形移位寄存器主要用于累加器或数据区操作数的定标。

它能将输入数据进行0~31位的左移和0~16位的右移。

所移动的位数可由ST1中的ASM或被指定的暂存器T决定。

1.组成框图①多路选择器MUX:用来选择输入数据。

②符号控制SC:用于对输入数据进行符号位扩展。

③移位寄存器:用来对输入的数据进行定标和移位④写选择电路:用来选择最高有效字和最低有效字。

2.桶形移位寄存器的输入通过多路选择器MUX来选择输入信号。

①取自DB数据总线的16位输入数据;②取自DB和CB扩展数据总线的32位输入数据;③来自累加器A或B的40位输入数据。

3.桶形移位寄存器的输出①输出至ALU的一个输入端;②经写MSW/LSW选择电路输出至EB总线。

4.桶形移位寄存器的功能主要用于格式化操作,为输入的数据定标。

①在进行ALU运算之前,对输入数据进行数据定标;②对累加器进行算术或逻辑移位;③对累加器进行归一化处理;④在累加器的内容存入数据存储器之前,对存储数据进行定标。

2.4.5比较、选择和存储单元CSSUCSSU单元主要完成累加器的高阶位与低阶位之间最大值的比较,即选择累加器中较大的字,并存储在数据存储器中。

工作过程:①比较电路COMP将累加器A或B的高阶位与低阶位进行比较;②比较结果分别送入TRN和TC中,记录比较结果以便程序调试;③比较结果输出至写选择电路,选择较大的数据;④将选择的数据通过总线EB存入指定的存储单元。

例如,CMPS指令可以对累加器的高阶位和低阶位进行比较,并选择较大的数存放在指令所指定的存储单元中。

指令格式:CMPSA,*AR1功能:对累加器A的高16位字(AH)和低16位字(AL)进行比较,若AH>AL,则AH→*AR1,TRN左移1位,0→TRN(0,0→TC;若AH,则AL→*AR1,TRN 左移1位,1→TRN(0,1→TC。

第2章DSP芯片的基本结构和特征2.1 引言可编程DSP芯片是一种具有特殊结构的微处理器,为了达到快速进行数字信号处理的目的,DSP芯片一般都具有程序和数据分开的总线结构、流水线操作功能、单周期完成乘法的硬件乘法器以及一套适合数字信号处理的指令集。

本章将首先介绍DSP芯片的基本结构,然后介绍TI公司的各种DSP芯片的特征,最后简要介绍其他公司的DSP芯片的特点。

2.2 DSP芯片的基本结构为了快速地实现数字信号处理运算,DSP芯片一般都采用特殊的软硬件结构。

下面以TMS320系列为例介绍DSP芯片的基本结构。

TMS320系列DSP芯片的基本结构包括:(1)哈佛结构;(2)流水线操作;(3)专用的硬件乘法器;(4)特殊的DSP指令;(5)快速的指令周期。

这些特点使得TMS320系列DSP芯片可以实现快速的DSP运算,并使大部分运算(例如乘法)能够在一个指令周期内完成。

由于TMS320系列DSP芯片是软件可编程器件,因此具有通用微处理器具有的方便灵活的特点。

下面分别介绍这些特点是如何在TMS320系列DSP芯片中应用并使得芯片的功能得到加强的。

2.2.1 哈佛结构哈佛结构是不同于传统的冯·诺曼(V on Neuman)结构的并行体系结构,其主要特点是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址,独立访问。

与两个存储器相对应的是系统中设置了程序总线和数据总线两条总线,从而使数据的吞吐率提高了一倍。

而冯·诺曼结构则是将指令、数据、地址存储在同一存储器中,统一编址,依靠指令计数器提供的地址来区分是指令、数据还是地址。

取指令和取数据都访问同一存储器,数据吞吐率低。

在哈佛结构中,由于程序和数据存储器在两个分开的空间中,因此取指和执行能完全重叠运行。

为了进一步提高运行速度和灵活性,TMS320系列DSP芯片在基本哈佛结构的基础上作了改进,一是允许数据存放在程序存储器中,并被算术运算指令直接使用,增强了芯片的灵活性;二是指令存储在高速缓冲器(Cache)中,当执行此指令时,不需要再从存储器中读取指令,节约了一个指令周期的时间。

DSP芯片的原理与开发应用课件1. 什么是DSP芯片DSP芯片(Digital Signal Processing Chip)是一种专门用于数字信号处理的集成电路芯片。

它具有强大的计算能力和高速处理速度,广泛应用于音频信号处理、图像处理、通信系统、雷达信号处理等领域。

2. DSP芯片的工作原理DSP芯片通过高效的算法和硬件加速器,对输入的数字信号进行采样、压缩、编码、滤波、频谱分析、解调、解码等处理,得到所需的输出信号。

其工作原理大致如下:1.信号采样:DSP芯片将输入的连续模拟信号通过采样电路转换为离散数字信号。

2.数字信号处理:DSP芯片使用内置的运算器和指令集,对采样到的数字信号进行各种算法处理,如滤波、频域变换、时域变换等。

3.运算加速:为了提高处理速度,DSP芯片通常配备专门的硬件加速器,如DSP协处理器、FPGA等,来协助完成复杂的计算任务。

4.输出处理:处理后的数字信号经过解码、解调等步骤后,再通过解调电路将其还原为模拟信号,输出到外部设备或其他系统中。

3. DSP芯片的开发应用3.1 音频信号处理DSP芯片在音频领域的应用非常广泛,可以用于音频编解码、音效处理、语音识别等。

通过采用各种数字算法,DSP芯片可以实现高质量音频信号处理和实时音效增强,提升用户体验。

在音频编解码方面,DSP芯片支持各种音频格式的解码和编码,如MP3、AAC、WAV等。

通过对音频信号进行压缩和解压缩,可以有效减小音频文件的大小,提高存储和传输效率。

3.2 图像处理DSP芯片在图像处理领域的应用日益重要。

利用DSP芯片的高速计算能力和并行处理能力,可以实现图像的滤波、边缘检测、图像增强、图像压缩等功能。

图像处理算法包括傅里叶变换、离散余弦变换、边缘检测、图像分割等。

这些算法可以在DSP芯片上进行高效的实现,帮助用户快速获得满足各种图像处理需求的结果。

3.3 通信系统DSP芯片在通信系统中起到了关键作用。

通信系统中需要对信号进行调制、解调、滤波、编解码等处理。

第2章DSP的硬件结构DSP的硬件结构:DSP与标准微处理器有许多共同的地方,都是由CPU、存储器、总线、外设、接口、时钟组成。

从广义上讲,可以说DSP是一种CPU。

但DSP和一般的CPU 又有不同, DSP有自己的一些独特的特点,比如采用哈佛结构、流水线操作、独立的硬件乘法器、独立的DMA总线和控制器等。

Von Neuman结构与Harvard结构:Harvard结构:程序与数据存储空间分开,各有独立的地址总线和数据总线,取指和读数可以同时进行,从而提高速度,目前的水平已达到90亿次浮点运算/秒(9000MFLOPS)。

MIPS—-Million Instruction Per SecondMFLOPS--Million Floating Operation Per Second流水操作(pipeline):独立的硬件乘法器:在卷积、数字滤波、FFT、相关、矩阵运算等算法中,都有A(kB(n-k一类的运算,大量重复乘法和累加.通用计算机的乘法用软件实现,用若干个机器周期。

DSP有硬件乘法器,用MAC指令(取数、乘法、累加)在单周期内完成。

独立的DMA总线和控制器:有一组或多组独立的DMA总线,与CPU的程序、数据总线并行工作,数据的传递和处理可以独立进行,DMA内部总线与系统总线完全分开,避开了总线使用上的瓶颈。

在不影响CPU工作的条件下,DMA速度已达800Mbyte/s。

CPU:通用微处理器的CPU由ALU和CU组成,其算术运算和逻辑运算通过软件来实现,如加法需要10个机器周期,乘法是一系列的移位和加法,需要数十个机器周期.DSP的CPU设置硬件乘法器,可以在单周期内完成乘法和累加。

移位:通用微处理器的移位,每调用一次移位指令移动1—bitDSP可以在一个机器周期内左移或右移多个bit,可以用来对数字定标,使之放大或缩小,以保证精度和防止溢出;还可以用来作定点数和浮点数之间的转换。

溢出:通用CPU中,溢出发生后,设置溢出标志,不带符号位时回绕,带符号位时反相,带来很大的误差DSP把移位输出的最高位(MSB)存放在一个位检测状态寄存器中,检测到MSB=1时,就通知下一次会发生溢出,可以采取措施防止。