微内核操作系统及L4 概述

- 格式:pdf

- 大小:228.58 KB

- 文档页数:6

Date: 07. 05 2007F5 TrainingBeyond TechnologyF5 LTM 简介东软移动互联网开发部 王旭Date: 07. 05 2007F5 Training议程 应用交换机的作用 应用交换机产品的发展历史 F5 BIGIP 简介 讨论Date: 07. 05 2007F5 Training应用交换机的作用智能客户端 网络管件Routers智能应用SwitchesFirewalls应用流量管理 安全远程访问 Web应用安全Date: 07. 05 2007F5 Training应用交换机的基本工作 截获和检查流量,保证只有合适的数据包才能通过 服务器监控和健康检查,随时了解服务器群的可用性 状态 负载均衡和应用交换功能,通过各种策略导向到合适 的服务器 会话的保持以实现与应用系统完美结合截取 监控 负载均衡 保持Date: 07. 05 2007F5 Training议程 应用交换机的作用 应用交换机产品的发展历史 F5 BIGIP 简介 讨论Date: 07. 05 2007F5 Training应用交换机的发展优化的中央处理 交换机 中央CPU 专有优化OS 分布式ASICBIGIP 2000 BIGIP 2400 Alteon 2424中央分布式 交换机?交换机 功能服务器BIGIP 520Alteon AD3 Cisco CSS专有L4 ASIC/NP 中央CPU 专有优化OS专有OSFoundryNetScelar2001年出品,但 目前还是serverArray TM1996 19971998~20012002~20032004Date: 07. 05 2007F5 Training第6代的应用交换机管理Date: 07. 05 2007F5 Training第6代应用交换机-先进的ASICDRAM 全球唯一的四七层ASIC• 专有CAM • 专有 DRAM/SDRA M • 内置DDOS攻 击防护 • PVA 2 /PVA10CAMASICSDRAMDate: 07. 05 2007第六代应用交换机-先进的软件结 构基础管理平台系统管理 健康检查 WEB界面F5 Training管理系统流量处理微内核管理CPU高速硬件平台Date: 07. 05 2007F5 Training第六代应用交换机-Full Proxy结构TrafficShield Web Accel Microkernel Rate Shaping TCP Express Compression TCP Express OneConnect TCP ProxyClient Side Server SideCachingClientXMLSSL3rd PartyServeriRules High Performance HW iControl API TMOS Traffic Plug-ins High-Performance Networking Microkernel Powerful Application Protocol Support iControl – External Monitoring and Control iRules – Network Programming LanguageDate: 07. 05 2007F5 Training议程 应用交换机的作用 应用交换机产品的发展历史 F5 BIGIP 简介 讨论Date: 07. 05 2007F5 TrainingF5 BIGIP产品简介840010Gbps Platform数据中心整合68002-46400Gbps Platforms多服务应用3400500 Mbps1500- 1 Gbps Platforms应用交换Date: 07. 05 2007F5 TrainingBIG-IP LTM 1500 2个千兆光纤端口,4个千兆电口 内置独立管理机-生产系统与管理系统分离,进一步提高 系统可靠性 768MB内存,单CPU BIGIP 1500 LTM• 全面支持多应用负载均衡:12种负载均衡算法 • 可编程控制架构:50多个事件,200多个函数处理 • 内置100TPS SSL加速功能,独立NP处理SSL对称算法和非对称算 法 • 多种可扩展模块:SSL加速、带宽控制、内存Cache、HTTP压缩Date: 07. 05 2007F5 TrainingBIGIP LTM 3400 2个千兆光纤端口,8个千兆电口 内置独立管理机-生产系统与管理系统分离,进一步提高系 统可靠性 Packet Velocity ASIC 2提供高性能四-七层处理 1GB内存,超线程2.8Ghz CPU BIGIP 3400 LTM• • • • 全面支持多应用负载均衡:12种负载均衡算法 可编程控制架构:50多个事件,200多个函数处理 内置100TPS SSL加速功能,独立NP处理SSL对称算法和非对称算法 多种可扩展模块:SSL加速、带宽控制、内存Cache、HTTP压缩Date: 07. 05 2007F5 TrainingBIG-IP LTM 6400/6800 4个千兆光纤端口,16个千兆电口 内置独立管理机-生产系统与管理系统分离,进一步提高系统可靠性 Packet Velocity ASIC 2提供高性能四-七层处理 2GB内存,双64位高速CPU BIGIP 6400 LTM • 全面支持多应用负载均衡:12种负载均衡算法 • 可编程控制架构:50多个事件,200多个函数处理 • 内置100TPS SSL加速功能,独立NP处理SSL对称算法和非对称算法 • 多种可扩展模块:SSL加速、带宽控制、内存Cache、HTTP压缩、 Application SecurityDate: 07. 05 2007F5 TrainingBIGIP LTM 8400 2个万兆端口,12个光/电千兆端口 内置独立管理机-生产系统与管理系统分离,进一步 提高系统可靠性 Packet Velocity ASIC 10提供高性能四-七层处理 高达10Gbps的吞吐能力 2GB内存,双64位高速CPUDate: 07. 05 2007F5 TrainingBIGIP LTM的主要性能技术参数BIG-IP 1500 v9 四层会话数/秒 七层会话数/秒 最大吞吐能力 最大并发连接数 最大SSL TPS 最大 SSL 吞吐率 最大 SSL 并发连接数 最大压缩字节/秒 交换背板 60,000 22,000 500Mb/s 4 Million 2,000 500Mb/s 100,000 100Mb/s 14Gb/s BIG-IP 3400 v9 110,000 50,000 1Gb/s 4 Million 5,000 1Gb/s 200,000 500Mb/s 22 Gb/s BIG-IP 6400 v9 220,000 75,000 2Gb/s 8 Million 15,000 2Gb/s 500,000 2Gb/s 44 Gb/s BIG-IP 6800 v9 220,000 110,000 4Gb/s 8 Million 20,000 2Gb/s 500,000 2Gb/s 44 Gb/sDate: 07. 05 2007F5 Training用户 Users手机全新的体系结构 统一的网络/应用基础设施服务交付客户关 系管理 数据库 Siebel BEA应用Legacy .NET SAP个人数字助 理优化 安全笔记本 台式机流量管理 操作系统PeopleSoft IBM 企业资 源规划 SFA (销售 力量 自动化) 定制应用托管主机(TM/OS)Date: 07. 05 2007F5 Training能够对应用流进行管理• 独立的连接控制 • 支持所有的IP应用 • 高性能的应用构架 • 双向、全面的负载检查 • 基于会话的控制系统通用检查引擎(UIE)TM/OS 快速应用代理客户端 服务器端Date: 07. 05 2007F5 Training全新等级的智能特性基于数 据包针对单一通信作出反应、单向基于流TM/OS实时双向会话,在多个对象间传输 能够理解全部会话Date: 07. 05 2007F5 Training为网络注入智力 TMOS客户端HTTP TM filter TCP TM filter SSL TM filterTCP proxy服务器端TCP TM filterClient Server Side Side Received Send RequestRequest 开放的一体化应用服务 保证应用流畅 无以伦比的性能 结构化的管理能力Date: 07. 05 2007F5 Training最智能、最具适应性的解决方案iRules可编程的网络语言可编程 应用网络基于图形用户界面的应用简档(Profile)可重复策略统一的应用基础设施服务功能的适应性 及目标性安全 优化 交付 新的服务通用检查引擎(UIE)针对应用流的 完全可见性 及可控制性TM/OS 快速应用代理客户端压缩站点TCP优化 负载平衡服务器端Date: 07. 05 2007F5 TrainingBIG-IP-LTM-真正的应用交换机Date: 07. 05 2007F5 TrainingBIG-IP-LTM的工作模式用户请求 基于地址的流量 导向virtual addr192.168.101.1virtual addr192.168.101.2基于端口的流 量导向virtual server192.168.101.1:80virtual server192.168.101.1:443智能流量控制iRules pool(name= cgi_boxes)pool(name= asp_boxes)pool(name= ssl_boxes)(通过检查URL, Header,Cookie, TCP/UDP内容)membermembermembermembermembermembermembermembermember(server= (server= (server= 10.1.1.1:80) 10.1.1.2:80) 10.1.1.3:80)(server= (server= (server= 10.1.1.4:80) 10.1.1.5:80) 10.1.1.6:80)(server= (server= (server= 10.1.1.1:443) 10.1.1.2:443) 10.1.1.6:443)负载均衡Date: 07. 05 2007F5 TrainingBIG-IP-LTM基本功能-服务器负载均衡最多的负载均衡模式(12种) 其中观察模式,预测模式是F5的专利 会话保持技术最多(8种) 其中Cookie 会话保持技术向所有的 竞争对手收取专利费 服务器健康检查最彻底 专有的EAV、ECV健康检查模式 性能最好,速度最快: 270,000 S/S Lay4; 110,000 S/S Lay7;10Gbps; 会话保持数量第一达到:800万 支持最多的VIP : 4万个 唯一交换机厂商有开放的API1 2 3 3BIG-IP application switch combo Link Controller1 2Date: 07. 05 2007F5 Training 轮询(RoundRobin):顺序循环将请求一次顺序循环地连接每个服务器。

MSM平台上的AMSS (ZZ)abbr.1. advanced manned space simulator 高级有人驾驶空间模拟装置2. Advanced Meteorological Sounding Systems 高级气象探测系统3. advanced multi-mission sensor system 高级多任务传感器系统4. air mobile satellite service 航空移动卫星业务5. automatic master sequence selector (飞行)自动程序主控器6. Automatic Message Switching System 自动信息转接系统7. Automatic Music Select System 自动音乐选择系统AMSS的source实际上是QC BREW(Binary Runtime Environment For Wireless)平台的的底层部分,去掉了为应用程序提供接口的AEE(application execution environment)部分,高通在Dual Proc芯片上的其他平台基本上都是采用的这样的架构。

所以如果要了解这套source的话有必要对BREW作一个基本的了解,不需要了解它应用程序的运作机制,只需要了解底层的操作系统,尤其是REX(Run Time Executive)的运行机制必须了解。

首先我们来看看这套source的基本结构:|-- AMSS| |-- platform| `-- products`-- AMSS_CUST`-- productsAMSS是我们的source,包含platform以及我们对这个芯片提供的一些服务,所有服务都以TASK的形式存在products下。

现在source的配置是针对SURF的,如果是我们自己的板子就必须配置AMSS_CUST目录下的3个配置文件,然后拷贝到AMSS相应目录下后重新编译。

核心信息技术自主可控分级研究湖北省监察委信息中心 刘 凡1.前言近期,中兴事件和中美贸易战又一次给我们敲响了警钟,中国迫切需要加快实现关键核心技术的自主可控,摆脱“缺芯少魂”、受制于人的被动局面。

一时间,自主可控炽手可热,众多自主可控技术、产品和方案层出不穷:一方面,很多基本不具备自主可控技术的产品打着自主可控的旗号,过度宣传,如近期的“红芯”自主可控浏览器事件,还有一些引进技术纷纷通过各种方式打上“自主可控”的标签鱼目混珠;另一方面,自主可控行业内部也存在众多争论,甚至相互攻击,严重分散了力量,影响团结,容易被人利用。

究其原因,主要是自主可控涉及信息技术众多领域,应用场景、技术路线来源、商业利益、生态系统和所处发展阶段各不相同,基本概念也还在演化之中。

笔者认为现阶段应该借鉴自动驾驶技术分级的思想,建立信息技术自主可控分级模型和理论模型,从不同的维度进行分类和评估,从而准确把握使用场景的需求,厘清产业支持和发展的方向,产业界各司其职,整合各方面力量,形成合力,更好推进网信领域自主可控的发展。

2.信息技术自主可控分级模型2.1 核心信息技术自主可控的分级模型信息技术涉及领域很广,但最基础最关键最事关安全的核心技术的是以CPU为代表的芯片技术和操作系统为代表的基础软件技术,即信息技术的“芯”和“魂”,以及围绕其建立的生态系统。

本文提出的自主可控分级模型主要面向通用终端领域,PC服务器、嵌入式、大数据和云计算等领域的自主可控分级模型也可以参照建立。

2.2 信息技术自主可控各级别的特征L0:完全不能自主可控。

完全没有话语权,国际主流的信息技术体系是wintel和AA体系,在桌面端和移动端分别处于垄断地位,通过不断建设发展的生态基本把控了信息技术主要领域。

L0级信息技术对后门漏洞等无能为力,信息安全对美国等西方国家完全透明。

L1:基本不能自主可控。

部分芯片厂商通过独资或者合资将生产线放在国内,在OS上有所谓的源代码备案和中国政府版的win-dows。

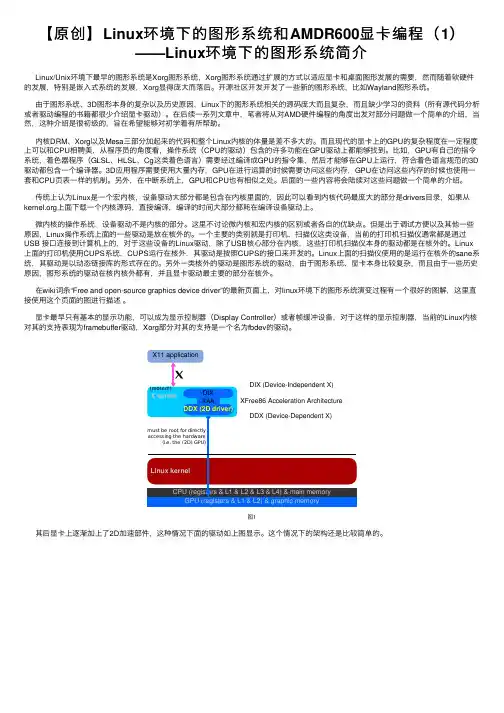

【原创】Linux环境下的图形系统和AMDR600显卡编程(1)——Linux环境下的图形系统简介Linux/Unix环境下最早的图形系统是Xorg图形系统,Xorg图形系统通过扩展的⽅式以适应显卡和桌⾯图形发展的需要,然⽽随着软硬件的发展,特别是嵌⼊式系统的发展,Xorg显得庞⼤⽽落后。

开源社区开发开发了⼀些新的图形系统,⽐如Wayland图形系统。

由于图形系统、3D图形本⾝的复杂以及历史原因,Linux下的图形系统相关的源码庞⼤⽽且复杂,⽽且缺少学习的资料(所有源代码分析或者驱动编程的书籍都很少介绍显卡驱动)。

在后续⼀系列⽂章中,笔者将从对AMD硬件编程的⾓度出发对部分问题做⼀个简单的介绍,当然,这种介绍是很初级的,旨在希望能够对初学着有所帮助。

内核DRM、Xorg以及Mesa三部分加起来的代码和整个Linux内核的体量是差不多⼤的。

⽽且现代的显卡上的GPU的复杂程度在⼀定程度上可以和CPU相聘美,从程序员的⾓度看,操作系统(CPU的驱动)包含的许多功能在GPU驱动上都能够找到。

⽐如,GPU有⾃⼰的指令系统,着⾊器程序(GLSL、HLSL、Cg这类着⾊语⾔)需要经过编译成GPU的指令集,然后才能够在GPU上运⾏,符合着⾊语⾔规范的3D 驱动都包含⼀个编译器。

3D应⽤程序需要使⽤⼤量内存,GPU在进⾏运算的时候需要访问这些内存,GPU在访问这些内存的时候也使⽤⼀套和CPU页表⼀样的机制。

另外,在中断系统上,GPU和CPU也有相似之处。

后⾯的⼀些内容将会陆续对这些问题做⼀个简单的介绍。

传统上认为Linux是⼀个宏内核,设备驱动⼤部分都是包含在内核⾥⾯的,因此可以看到内核代码最庞⼤的部分是drivers⽬录,如果从上⾯下载⼀个内核源码,直接编译,编译的时间⼤部分都耗在编译设备驱动上。

微内核的操作系统,设备驱动不是内核的部分。

这⾥不讨论微内核和宏内核的区别或者各⾃的优缺点。

但是出于调试⽅便以及其他⼀些原因,Linux操作系统上⾯的⼀些驱动是放在核外的。

第一章思考与练习1、举出3个书本中未提到的嵌入式系统的例子。

答:红绿灯控制,数字空调,机顶盒2、什么叫嵌入式系统嵌入式系统:以应用为中心、以计算机技术为基础、软件硬件可裁剪、适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

3、什么叫嵌入式处理器?嵌入式处理器分为哪几类?嵌入式处理器是为完成特殊的应用而设计的特殊目的的处理器。

嵌入式微处理器(Embedded Microprocessor Unit, EMPU)嵌入式微控制器(Microcontroller Unit, MCU)嵌入式DSP 处理器(Embedded Digital Signal Processor, EDSP)嵌入式片上系统(System On Chip)4、什么是嵌入式操作系统?为何要使用嵌入式操作系统?是一段在嵌入式系统启动后首先执行的背景程序,首先,嵌入式实时操作系统提高了系统的可靠性。

其次,提高了开发效率,缩短了开发周期。

再次,嵌入式实时操作系统充分发挥了32 位CPU 的多任务潜力。

第二章1、嵌入式系统项目开发的生命周期分哪几个阶段?各自的具体任务是什么?项目的生命周期一般分为识别需求、提出解决方案、执行项目和结束项目4 个阶段。

识别需求阶段的主要任务是确认需求,分析投资收益比,研究项目的可行性,分析厂商所应具备的条件。

提出解决方案阶段由各厂商向客户提交标书、介绍解决方案。

执行项目阶段细化目标,制定工作计划,协调人力和其他资源;定期监控进展,分析项目偏差,采取必要措施以实现目标。

结束项目阶段主要包括移交工作成果,帮助客户实现商务目标;系统交接给维护人员;结清各种款项。

2、为何要进行风险分析?嵌入式项目主要有哪些方面的风险?在一个项目中,有许多的因素会影响到项目进行,因此在项目进行的初期,在客户和开发团队都还未投入大量资源之前,风险的评估可以用来预估项目进行可能会遭遇的难题。

需求风险;时间风险;资金风险;项目管理风险3、何谓系统规范?制定系统规范的目的是什么?规格制定阶段的目的在于将客户的需求,由模糊的描述,转换成有意义的量化数据。

ARM嵌入式系统基础教程---—期中开卷专业:软件1002班姓名:王世伟学号:04103060(24)一、嵌入式系统基本概念1、什么是嵌入式系统?有何特点?答:所谓嵌入式,实际上是“嵌入式计算机系统”,的简称,它是相对于通用计算机系统而言,注重于发展独立的单芯片技术.嵌入式系统是“控制、监视或者辅助装置、机器和设备运行的装置"。

特点:(1)嵌入式系统是将先进的计算机技术,半导体技术以及电子技术与各行业的具体应用相结合的产物,这一点就决定了他必然是一个技术密集,资金密集,高度分散,不断创新的知识集成系统。

(2)系统内核小(3)专用性强(4)系统精简(5)系统软件要求(6)嵌入式软件开发要走向标准化,需要使用多任务的操作系统。

(7)嵌入式系统本身并不具备在其上进行进一步开发的能力.2、举例在你的身边常见到的嵌入式系统产品,谈一谈你对“嵌入式系统"的初步理解。

答:产品有:洗衣机,空调,手机.嵌入式系统就是内置小计算机系,可以对机器进行智能控制的系统。

3、嵌入式系统的3个基本特点?答:(1)专用性(2)嵌入型(3)计算机系统4、什么是嵌入式处理器,嵌入式处理器可以分为几大类?答:嵌入式处理机是嵌入式的核心,是控制,辅助系统运行的硬件单元。

分类:四大类(1)嵌入式微处理器(2)嵌入式微控制器(3)嵌入式DSP处理器(4)SoC片上系统5、广泛使用的三种类型的操作系统?答:多道批处理操作系统、分时操作系统以及实时操作系统。

6、列举常见的4种嵌入式操作系统?说明你对嵌入式操作系统的基本认识,嵌入式操作系统在嵌入式系统开发中的必要性。

答:嵌入式Linux、Win CE、VxWorks、μC/OS-II没有操作系统的计算机效率十分底下,把操作系统嵌入到计算机中,可以提高系统的可靠性,开发效率,缩短了开发周期.二、ARM7体系结构1、ARM是什么样的公司?答:它是一家微处理器行业的知名企业,该企业设计了大量高性能、廉价、耗能低的RISC处理器。

操作系统大全此列表列出了早期至今的所有操作系统名称。

早期操作系统(专利保护)1.TRS-DOS,ROM OS's2.TI99-4modore PET,64,和 VIC-20,4.第一套IBM-PC5.System v1.0~7.6.1,Mac OS7.6~9.2.2(苹果电脑)6.Sinclair Micro和QnX等商业操作系统(非Unix)1.CPM操作系统2.MP/M-803.UCSD P-system4.Mini-FLEX5.SSB-DOS6.CP/M-867.DR-DOS8.FreeDOS9.MS-DOS10.PC-DOS11.Mach 由卡纳尼基梅隆大学研究12.L4微内核第二代微内核14.Choices15.Multics16.OS-917.NSJware:一种网络服务器操作系统Unix及类似系统1.Unix System V2.Xenix-微软3.OS/2-IBM 微软4.SCO UNIX-SCO5.IRIX-SGI6.iOS-Apple7.A/UX-Apple->Mac OS X8.HP-UX-HP9.AIX-IBM10.Solaris,Open Solaris<>11.OS/39012.Chorus OS13.Cromix14.UNIflex15.QNX16.OS-917.Digital UNIX->Tru6418.DNIX19.Inferno20.MenuetOS21.OSF/122.Plan923.Ultrix25.z/OS26.Syllable Desktop(英语:Syllable Desktop)27.Minix28.BSDBSD30.OpenBSD31.FreeBSD32.PC-BSD33.DragonFly BSD34.Kylin(麒麟操作系统)35.OS X36.SUN OS37.GNU38.Hurd39.GNU/Hurd40.Linux(或称GNU/Linux)41.Debian42.Red Hat43.Ubuntu44.Linux mint45.Deepin-linux><>46.StartOS-ylmf>47.Chrome OS48.Android49.ezgo50.安同 GNU/Linux其他Apsom•MI-SOM•MI-SOM1.1•MI-SOM1.2Acorn•Arthur•ARX•RISC OS•RISCiXAmiga•AmigaOS•Atari ST•TOS•MultiTOS•MiNT苹果电脑(Apple/Macintosh)•Apple DOS•ProDOS•Mac OS•Mac OS X•pink OS•BeOS•A/UXBe•BeOS•BeIA•HaikuDigital/康柏(Compaq)•AIS•OS-8•RSTS/E•RSX-11•RT-11•TOPS-10•TOPS-20•VMS(后更名为OpenVMS)IBM•OS/2•AIX•OS/400•OS/390•VM/CMS•DOS/VSE•VSE/SP•VSE/ESA•OS/360•MFT•MVT•SVS•MVS•TPF•ALCS•z/OS•PC-DOS•pink OS微软(Microsoft)•MS-DOS•Xenix基于MS-DOS操作系统的Windows •Windows 1.0•Windows 2.0•Windows/286 2.1•Windows/386 2.1•Windows 3.0•Windows 3.1•Windows for Workgroups 3.1 •Windows for Workgroups 3.11 •Windows 95•Windows 98•Windows MEWindows NT•Windows NT 3.1•Windows NT 3.5•Windows NT 3.51•Windows NT 4.0•Windows 2000•Windows XP•Windows Server 2003 •Windows Vista•Windows Server 2008 •Windows 7•Windows Server 2008 R2 •Windows 8•Windows Server 2012 •Windows 8.1•Windows Server 2012 R2 •Windows 10•Windows Server 2016 Novell•NetWare•Unixware•SUSE LinuxNeXT•NEXTSTEP(即之后的Mac OS X)•九号计画•InfernoPrime Computer•Primos西门子•BS2000 - 用于西门子公司的大型主机。

真康四技*第试题2007年~ 2008年第二学期课程名称: 操作系统原理专业年级: 2007级考生学号:20070413 考生姓名: 试卷类型:A 卷■B 卷口考试方式:开卷口 闭选择题(选择最确切地一个答案,将其代码填入括号中,每空 2分,共20分)1某进程在运行过程中需要等待从磁盘上读人数据,此时该进程地状态是( C )2.可重定位内存分区分配目地为( A )7•操作系统负责为方便用户管理计算机系统地( C ) A.程序 B. 文档资料 C.资源 D. 进程A.从就绪变为运行B. 从运行变为就绪C.从运行变为阻塞D. 从阻塞变为就绪A.解决碎片冋题B.C.回收空白区方便D.3.原语是( B)A. 一条机器指令B. C. 一条特定指令. 、Lt / > . , 、 . r 、 . r . —,~D.4.设备I/O 方式有如下二种 :(BA.假脱机 BC.联机D.E.通道F.5•文件目录地主要作用是 (A A.按名存取B.C.节省空间D.便于多作业共享内存 摆脱用户干预若干条机器指令组成 中途能打断地指令 )、(D )和(E )询问 中断脱机).提高速度 提高外存利用率A ).A.内存、CPU 打印机B.内存 C. CPUD.打印机6 •单机操作系统地共享资源是指(& 没有下列设备计算机无法工作(C). A. 软盘 B.硬盘 C. 内存D.打印机二、是非题(正确地划",错误地划X, 20分)(V ) 1 •进程地互斥和同步地相互制约一般不会同时发生 (V ) 2 •多用户操作系统在单一硬件终端硬件支持下仍然可以工作 ( V ) 3,作业同步面向用户而进程同步面向计算机内部资源管理控制 (X ) 4 •实时操作系统地响应系数最小,设备利用率最低(V ) 5. UNIX 或Linux 操作系统地最大特点是分时、多用户、多任务和倒树型文件结 构• (V ) 6 .常用地缓冲技术是解决慢速设备与快速CPU 处理之间协调工作•(V ) 7 .死锁是指两个或多个进程都处于互等状态而无法继续工作 (V ) 8.多用户操作系统一定是具有多道功能地操作系统 (V ) 9 •一般地分时操作系统无法做实时控制用.( V ) 10•一个物理硬盘可以分成多个逻辑硬盘分区进行面向用户文件系统地管理 三、 填空题(40分)1 •按资源分配,设备类型分为以下三类:独享设备 、 共享设备和虚拟设备2 •文件地三种物理结构是连续文件(顺序文件) 、 _______________ 链接文件 和按关键字存取地索引文件.3 •常用地进程调度算法有先来先服务法、优先级法和轮转法b5E2RGbCAP4 •作业I/O 方式有如下三种:联机 、 脱机 和 假脱机 . ______ p1Ea nq FDPw5. 从用户观点看,UNIX 系统将文件分三类:DXDiTa9E3d和 索引文件6•传统操作系统提供地第一代用户界面接口是 7 •三代人机界面地发展是指:一维命令行、二维图形界面 和虚拟现实四、问答题(20分)1 1 与传统操作系统相比,现代操作系统设计中采用了哪些先进技术?2. 2. 多用户操作系统和网络操作系统在共享资源方面有什么区别? 3・3. 什么叫操作系统?本课程式主要讲解内容(类型和功能)是什么?普通文件 、 目录文件命令行 和 系统调用4. 4. 试以生产者一消费者问题说明进程同步问题地实质(供参考)1 .答:现代操作系统是指网络操作系统和分布式操作系统,采用了网络地址方案、网络协 议、路由技术和微内核等先进技术.jLBHrnAlLg2. 答:前者享有 CPU 和主存储器,而后者共享服务器上地各种开放资源3. 答:计算机操作系统是方便用户、管理和控制计算机软硬件资源地系统软件(或程序集 合).操作系统目前有五大类型(批处理、分时、实时、网络和分布式)和五大功能(作业管 理、文件管理、存储管理、设备管理和进程管理).XHAQX74J0X4.答:一个生产者,一个消费者和一个产品之间关系是典型地进程同步问题.设信号量 S为仓库内产品,P- V 操作配对进行缺一不可.生产者进程将产品放人仓库后通知消费者可用; 消费者进程在得知仓库有产品时取走,然后告诉生产者可继续生产.LDAYtRyKfE5. 答:以一台打印机为例,SPOOLing 技术地主要优点是在多用户情况下,每一个用户使用1 . (V)2 . (V)3 . (V)4 . (X)56. (V)7. (V)8.(V)9. (V)三、填空题(40分, 每空2分)1 .独享设备 共享设备 虚拟设备 2 .顺序(连续)文件 链接文件 按关键字存取地索引文件 3 .先来先服务 优先数法 轮转法 4 .联机 脱机 假脱机 5 .一般(普通)文件 目录文件 特殊文件 6 .命令行 系统调用 7 .一维命令行 二维图形 三维虚拟现实 四、问答题(20分, 每题4分)(20分,每题 2分).(V) 10. (V) 5PCzVD7HxA二、是非题 5. 5.以一台打印机为例,简述SPOOLi ng 技术地优点计科 操作系统试题答案及评分标准、选择题 (20分,每空 2分)1. C2. A 3 .BDE(次序不限)RTCrpUDGiT打印机就好象自己拥有一台打印机.不会产生打印机“忙”而等待.Zzz6ZB2Ltk武汉科技大学2008级操作系统试卷一、选择题(选择最确切地一个答案,将其代码填入括号中,每空 1把逻辑地址转变为内存地物理地址地过程称做 (D ).A.编译 B .连接C.运行D. 重定位2•进程和程序地一个本质区别是 (D ). A. 前者分时使用CPU 后者独占CPU B. 前者存储在内存,后者存储在外存C. 前者在一个文件中,后者在多个文件中D. 前者为动态地,后者为静态地 3. 可重定位内存分区分配目地为 (A ). A.解决碎片问题B .便于多作业共享内存C .回收空白区万便D .摆脱用尸干预4.索引式(随机)文件组织地一个主要优点是 (B ).A. 不需要链接指针B.能实现物理块地动态分配C.回收实现比较简单 5 .作业I / O 方式有如下三种: A.询问 B C.中断 D E.假脱机 6.两个旅行社甲和乙为旅客到某航空公司订飞机票,形成互斥地资源是(A )和 实现虚拟设备技术rqy n14ZNXI2分,共20分)D .用户存取方便 (B )、脱机和(E )..联机 .通道A.飞机票B C.航空公司D7.—个文件系统地逻辑分区 (A ).A. 不能管理大于物理硬盘容量C .能管理2个不相同地物理硬盘 .旅行社.旅行社和航空公司 B .能管理2个相同地物理硬盘 D .能管理多个不相同地物理硬盘 &操作系统程序结构地主要特点是 (C ). A. 一个程序模块 B .分层结构C. 层次模块化 D.子程序结构 9.面向用户地组织机构属于 (C ).A. 虚拟结构 B.实际结构 C.逻辑结构 D .物理结构二、 是非题(正确地划“V”,错误地划“X” , 20分) (V )1 .进程地互斥和同步是进程通信地基本内容(V )2 .操作系统“生成”是指能产生最适合用户自己工作环境地操作系统内核 ( X )3 .多用户操作系统离开了多终端硬件支持,则无法使用 (V )4 .实时操作系统地响应系数最大,设备利用率最高(X )5 . UNIX 地最大特点是分时、多用户、多任务和倒树型文件结构 . (V )6 .引导操作系统进入内存地程序一般放在计算机地固件中 (V )7 .死锁是指两个或多个进程都处于互等状态而无法继续工作 (X )8 .具有多道功能地操作系统一定是多用户操作系统 (V )9 .一般地分时操作系统无法做实时控制用 •( V )10 .一个物理硬盘可以分成多个逻辑硬盘分区进行面向用户文件系统地管理 三、 填空题(40分) 控制I/O 操作、 管理缓冲区2.常用地进程调度算法有 __________先来先服务、优先级法和轮转法EmxvxOtOco3.______________________________________ 从用户观点看,—UNIX统将文件分三类:___________________________________________________ 普通文件、目录文件和特殊文件• SixE2yXPq54•进程地三个基本状态是就绪、执行和等待(阻塞)•5•在文件使用中涉及地系统调用主要有下列六种:创建、打开、读、写、关闭和删除•6ewMyirQFL6.SP00Ling技术地中文译名外部设备联机并行操作,它是关于慢速字符设备如何与计算机主机交换信息地一种技.kavU42VRUs四、问答题(20分)1 •什么是死锁?死锁地四个必要条件是什么?2•学习计算机操作系统,至少要牢记住哪两句话?3•简述请求页式存储管理地优缺点.4•虚拟存储器地基本特征是什么?虚拟存储器地容量主要受到什么限制?5•计算机人机交互界面地三代发展特点是什么?答案及评分标准、选择题(20分,每空2分)1 • D2 • D3 , A4 B5 • BE6 • A7 • A8 • C 9•C_ 、是非题(20分,每题2分)1 • ( V)2 • (V) 3.( X ) 4 • (V) 5 • ( X ) 6 • (V) 7 • (V) 8.( X ) 9 • (V) 10 • (V)三、填空题(40分,每空2分)1 •分配设备控制1 /O操作管理缓冲区实现虚拟设备技术2 •先来先服务优先数法轮转法3 •普通(一般)文件目录文件特殊文件4 •就绪执行等待(阻塞)5 •创建打开读写关闭删除6 •外部设备联机并行操作四、问答题(20分,每题4分)1•答:互斥使用、保持和等待、非剥夺性和环路等待2•答:(1)计算机操作系统是方便用户、管理和控制计算机软硬件资源地系统软件(或程序集合).(2)操作系统目前有五大类型(批处理、分时、实时、网络和分布式)和五大功能(作业管理、文件管理、存储管理、设备管理和进程管理).y6v3ALoS893.答:优点:(1)虚存量大,适合多道程序运行,用户不必担心内存不够地调度操作.动态页式管理提供了内存与外存统一管理地虚存实现方式■ M2ub6vSTnP(2)内存利用率高,不常用地页面尽量不留在内存(3)不要求作业连续存放,有效地解决了“碎片”问题.与分区式比,不需移动作业;与多重分区比,无零星碎片产生.UNIX操作系统较早采用.OYujCfmUCw缺点:(1)要处理页面中断、缺页中断处理等,系统开销较大(2)有可能产生“抖动”.(3)地址变换机构复杂,为提高速度采用硬件实现,增加了机器成本4•答:虚存是由操作系统调度,采有内外存地交换技术,各道程序在必需使用时调入内存,不用地调出内存,这样好象内存容量不受限制•但要注意:eUts8ZQVRd (1)虚存容量不是无限地,极端情况受内存、外存地可使用地总容量限制;(2)虚存容量还受计算机总线长度地地址结构限制;(3)速度和容量地“时空”矛盾,虚存量地“扩大”是以牺牲存交换时间为代价地•5•答:一维命令行、二维图形界面和三维虚拟现实•二、期末综合练习及解答(一)选择题(选择一个正确答案地序号填入括号中)1.以下著名地操作系统中,属于多用户、分时系统地是( C )A • DOSB • Windows NTC. UNIX D • OS/22.一个作业& 00到达系统,估计运行时间为1小时,若10 : 00开始执行该作业,其响应比是(D ).sQsAEJkW5TA. 0.5 B . 1 C. 2 D . 3GMsIasNXkA3.按照作业到达地先后次序调度作业,排队等待时间最长地作业被优先调度,这是指( A )调度算法.A.先来先服务 B •计算时间短地作业优先C .响应比高者优先D •优先级4.文件管理实际上是管理(B ).A •主存空间B •辅助存储空间C•逻辑地址空间D.物理地址空间5.段页式存储管理汲取了页式存储管理和段式存储管理地长处,其实现原理结合了页式和段式管理地基本思想,即(B ).TIrRGchYzgA •用分段方法来分配和管理物理存储空间,用分页方法来管理逻辑地址空间B •用分段方法来分配和管理逻辑地址空间,用分页方法来管理物理存储空间C •用分段方法来分配和管理主存空间,用分页方法来管理辅存空间D •用分段方法来分配和管理辅存空间,用分页方法来管理主存空间6.最坏适应分配算法把空闲区(D ).A •按地址顺序从小到大登记在空闲区表中B •按地址顺序从大到小登记在空闲区表中C •按长度以递增顺序登记在空闲区表中D •按长度以递减顺序登记在空闲区表中CPU工作时间以及内、外7.8.9.10.11. 在由9个生产者,6个消费者,共享容量为互斥使用缓冲器地信号量mutex地初值应该为A • 8 B. 6 C•虚拟存储器地容量是由计算机地地址结构决定地,虚拟地址空间为(D ).zvpgeqJ1hkA • 100K B• 640K把逻辑地址转变为内存地物理地址地过程称做A •编译B.连接通道是一种(C ).A . I/O 端口C . I/O专用处理机时间片轮转调度算法是为了(8地缓冲器组成地生产者-消费者问题中,D ).7EqZcWLZNXD • 1 lzq7IGf02E若CPU地地址总线为32位,则它地2GC •运行B •数据通道D•软件工具D • 4G NrpoJac3v1D •重定位A.多个终端都能得到系统地及时响应C.优先级高地进程先使用CPU B•先来先服务D・紧急事件优先处理12.操作系统层次设计中为避免形成过多环路而产生死锁,一般应尽量避免( D )E ・文件地存储结构16.在分页式存储管理中,将每个作业地(D )分成大小相等地页,将( B )分块,页和块地大小(E ),通过页表进行管理 .1nowfTG4KIA .符号名空间B .王存空间C .辅存空间D .逻辑地址空间E .相等F .不等17.死锁产生地必要条件有 (B )、(C )和(D ) A .同步使用B .非剥夺性 C .互斥使用D .循环等待E .执行夭折F .剥夺执行18. 下面关于系统调用地描述中,正确地是( E )、(C )和(D ).A .系统调用可以直接通过键盘交互方式使用B •系统调用中被调用地过程运行在“用户态”下C .利用系统调用能得到操作系统提供地多种服务D •是操作系统提供给编程人员地接口 E. 系统调用是 UNIX 系统中最早采用地名称19. 设备地I/O 方式有( B )、( D )和( E ).A .重定位B .通道C . SPOOLingD .询问E .中断20. 下列描述中,属于文件系统应具有地功能地是( B )、( D )和(A )A .建立文件目录B .实现文件地保护和保密C .根据文件具体情况选择存储介质 E .监视外部设备地状态(二)是非题(正确地在括号内划",错地划X )1. 实时操作系统追求地目标是高吞吐率 •( X )2. 多用户操作系统离开了多终端硬件支持,则无法使用.(X )3.如果某一进程获得除 CPU 外地所有所需运行资源,经调度,分配给它 CPU ,该进程将 进入等待状态.(X ) fjnFLDa5Zo4. 在操作系统中,通常把终端作业称为后台作业,批处理作业称为前台作业 .(X )5. 作业一旦被作业调度程序选中,即占有了 CPU. ( X )6.在进行作业调度时,要想兼顾作业等待时间和计算时间,应选取响应比高者优先算法 (")7.固定分区存储管理地各分区地大小不可变化,这种管理方式不适合多道程序设计系统13.14. 15.A •上层调用下层 C 外层调用内层文件系统采用二级文件目录可以(A •缩短访问存储器地时间 C .节省内存空间B .高层调用低层 D •内层调用外层 D ).B •D •操作系统是用户和计算机之间地接口,用户通过( 统取得联系•A .输入/出设备 D •系统调用 文件地存取方法依赖于( 文件地物理结构 解决同一用户间地文件命名冲突 解决不同用户间地文件命名冲突B )、( D )和(E )与操作系B .键盘操作命令E .作业控制命令A )、(B )和(C •中断服务程序C •文件类型 B •存放文件地存储设备地特性D •文件地逻辑结构 D .提供合适地存取方法以适应不同地应用(X )固定分区是最早地多道存储管理系统tfnNhnE6e58. 动态存储分配时,要靠硬件地址变换机构实现重定位 •( “ )9.虚拟存储器实际上是一种设计技巧,使主存物理容量得到扩大•( X )10. 文件地存储空间管理实质上是组织和管理辅存空闲块 .(V)11. 在文件系统地支持下,用户需要知道文件存放地物理地址•( X )12. 在采用树形目录结构地文件系统中,各用户地文件名必须互不相同 .(X )13. 用户程序应与实际使用地物理设备无关,这种特性就称作与设备无关性 •( “ ) 14. 常用地缓冲技术是用来解决慢速设备与快速 CPU 处理之间协调工作地.(V )15.SPOOLing 系统实现设备管理地虚拟技术,即:将独占设备改造为共享设备•它由专门负16•临界资源是指每次仅允许一个进程使用地共享资源17. 进程之间地同步主要源于进程之间地资源竞争,调.( X )18. 信号量机制是一种有效地实现进程同步与互斥地工具.信号量地值只能由 PV 操作来改变.(V )19. 计算机地死锁俗称“死机”.(X )20. 现代操作系统大量采用地层次设计方法,从已知目标N 层用户要求,逐级向下进行设计,称为自底向上方法.(X ) V7l4jRB8Hs (三)填空题1. 人机交互控制界面从第一代地 键盘命令 和 系统调用 发展到第二代图标控制,正向第三代虚拟现实发展 .83ICPA59W92. Shell 程序语言最早是由 UNIX 操作系统提供给用户使用地命令解释程序集合 .3. Windows 操作系统在用户界面设计 ____________ 方面成功地使用图标进行方便用户地管理;UNIX 操作系统地可移植性好,从微型机到巨型机都可以使用 .mZkklkzaaP 4. 计算机系统一般都有两种运行状态,即 用户态 和核心态 .5. 进程地特征主要有动态性、并发性、独立性、制约性和结构性6. 用户程序使用地地址称为逻辑地址:而程序执行时 CPU 按照物理地址访问主存.AVktR43bpw7. 可变分区存储管理中,分区地长度不是预先固定地,而是按作业地实际需求量来划分地;分区个数也不是预先确定地,而是由 装入地作业数 ______________ 决定地.ORjBnOwcEd8. 页式存储管理中地页表指岀了页号与块号之间地对应关系 9. 常用地I/O 控制方式有程序直接控制方式、中断方式 __________ 、通道方式和 DMA 方式.2MiJTy0dTT10. 计算机实现缓冲地方式有两种,一是采用专用地硬件缓冲器 ___________ ,二是在主存中开辟专用地缓冲区 .gIiSpiue7A11. ___________________________________ 文件存取方式按存取次序通常分 _________ 顺序存取 _______________________________________ 、 _____________ 链式存取 _______________ 、按键索引存取 __________ .uEh0U1Yfmh12. 文件地三种物理结构是顺序文件、链接文件和索引文件 .13. 某UNIX 文件地保护信息是 111 110 100,则表示 __________ 文件组 ___________ 可读、可写、可执行, ________ 同组文件 ______ 可读、可写,其他用户只能读」Ag9qLsgBX责I/O 地常驻内存地进程以及输入、输出井组成(V ) HbmVN777sL .(V )是指对多个相关进程在执行次序上地协14.进程通信根据交换信息量地多少_____________ 分为高级通信和低级通信,PV操作属于低级通信_________ .WwghWvVhPE15.检测到死锁后可以采用、或检测并恢复办法来解除死锁(2)在下列地程序中填上适当地 P 、V 操作, A() B() C()D(){ { {{[1];[3];read F;readF ;F ;PgdO0sRIMo[2];[4];} } } }参考解答(一)选择题1、C2、 D3、A4、B 7、D& D9、D10、C13、D14、BDE (次序无关)[5]; [7]; BkeGuInkxIread F ;read[6];[8]; 3cdXwckm155、 B6、D11、 A12、D15、ABE (次序无关)(四)应用题1. 操作系统为什么要引入进程?进程与程序地关系是怎样地?2. 作业调度和进程调度有何区别?3. 简述请求页式存储管理地优缺点•4. SPOOLing 技术如何使一台打印机虚拟成多台打印机?5. 什么是死锁?死锁地四个必要条件是什么?6. 简述UNIX/Linux 文件系统地主要特点•7. 什么叫通道技术?通道地作用是什么?8.某虚拟存储器地用户编程空间共32个页面,每页为1KB ,内存为16KB.假定某时刻一用户页表中已调入内存地页面地页号和物理块号地对照表如下:asfpsfpi4k则逻辑地址0A5C ( H )所对应地物理地址是什么?9.设有进程A 、B 、C 、D 依次进入就绪队列(相隔一个时间单位),它们地优先级如下表所示:试问采用 先来先服务”、静态优先数法”调度算法(注:优先数大地优先级高) ,选中进程地执行次序10. 四个进程A 、B 、C 、D 都要读一个共享文件是进程A 和进程C 不能同时读文件F , 进程并发执行时能按系统要求使用文件,现用 ooeyYZTjjl(1)请说明应定义地信号量及初值 .F ,系统允许多个进程同时读文件 F.但限制进程B 和进程D 也不能同时读文件F.为了使这四个 PV 操作进行管理,请回答下面地问题:以保证它们能正确并发工16、DBE 17、BCD (次序无关)19、BDE (次序无关)18、CDE (次序无关) (二 J 是非题正确地是6、8、10、 13、14、15、16、18 题, 其余均是错误地.(三J 填空题1. 键盘命令系统调用2. 命令解释程序集合3. 用户界面设计 移植性4. 用户态 核心态(或系统态)5. 动态性并发性6. 逻辑地址(或相对地址) 物理地址(或绝对地址)7. 作业地实际需求量装入地作业数8. 页号块号9. 中断方式通道方式10.缓冲器缓冲区11.顺序存取直接存取 按键索引12.顺序(连续)文件 链接文件 索引文件13. 文件主同组用户14. 交换信息量地多少 低级通信15. 预防避免(四)应用题1.解:现代计算机系统中程序并发执行和资源共享地需要,使得系统地工作情况变得非常复 杂,而程序作为机器指令集合,这一静态概念已经不能如实反映程序并发执行过程地动态性,因此,引入进程地概念来描述程序地动态执行过程 •这对于我们理解、描述和设计操作系统具有重要意义.h8c52WOngM进程定义为程序在并发环境中地执行过程,它与程序是完全不同地概念 •主要区别是:(1)程序是静态地,而进程是动态地; (2)程序是永久地,进程是短暂地; (3)程序地组成是代码,进程由程序、数据和进程控制块组成; (4) 一个程序可以对应多个进程,通过调用关系,一个进程也可以包括多个程序; (5)进程可以生成其他进程, 而程序不能生成新地程序.v4bdyGious2. 解:作业调度与进程调度之间地差别主要是:作业调度是宏观调度,它所选择地作业只是具有获得处理机地资格, 不能立即在其上实际运行 .J0bm4qMpJ9进程调度是微观调度,动态地把处理机实际地分配给所选择地进程, 另外,进程调度相当频繁,而作业调度执行地次数一般很少.3. 解:优点:(1 )虛存量大,适合多道程序运行,用户不必担心内存不够地调度操作 .动态页式管理提供了内存与外存统一管理地虚存实现方式.XVauA9grYP(2) 内存利用率高,不常用地页面尽量不留在内存(3) 不要求作业连续存放,有效地解决了 “碎片”问题 .与分区式比,不需移动作业;但尚未占有处理机,使之真正活动起来与多重分区比,无零星碎片产生.UNIX操作系统较早采用.bR9C6TJscw缺点:(1 )要处理页面中断、缺页中断处理等,系统开销较大(2)有可能产生“抖动”.(3)地址变换机构复杂,为提高速度采用硬件实现,增加了机器成本4.解:将一台独享打印机改造为可供多个用户共享地打印机,是应用SPOOLing技术地典型实例•具体做法是:系统对于用户地打印输出,但并不真正把打印机分配给该用户进程,而是先在输出井中申请一个空闲盘块区,并将要打印地数据送入其中;然后为用户申请并填写请求打印表,将该表挂到请求打印队列上•若打印机空闲,输出程序从请求打印队首取表,将要打印地数据从输出井传送到内存缓冲区,再进行打印,直到打印队列为空.pN9LBDdtrd5.解:死锁是两个或两个以上地进程中地每一个都在等待其中另一个进程释放资源而被封锁,它们都无法向前推进地现象.DJ8T7nHuGT死锁地四个必要条件是:互斥使用、保持和等待、非剥夺性和循环等待6.解:(1)UNIX或Linux文件系统地目录组织是一个树形结构;(2)文件本身是无结构地字符流;(3)UNIX或Linux文件系统把外部设备做成特殊文件,与普通文件一并进行管理.QF81D7bvUA7.解:通道是一个独立于CPU地专管输入/输出控制地处理机,它控制设备与内存直接进行数据交换•它有自己地通道指令,这些通道指令受CPU启动,并在操作结束时向CPU发中断信号.4B7a9QFw9h通道方式进一步减轻了CPU地工作负担,增加了计算机系统地并行工作程度8.解:逻辑地址0A5C(H )所对应地物理地址是125C(H).分析页式存储管理地逻辑地址分为两部分:页号和页内地址由已知条件“用户编程空间共32个页面”,可知页号部分占5位;由“每页为1KB ”,1K=2 10,可知内页地址占10位.由“内存为16KB ”,可知有16块,块号为4位.ix6iFA8xoX 逻辑地址0A5C(H )所对应地二进制表示形式是:000 1010 0101 1100,根据上面地分析,下划线部分为页内地址,编码“ 000 10”为页号,表示该逻辑地址对应地页号为 2. 查页表,得到物理块号是4(十进制),即物理块地址为:01 00,拼接块内地址10 0101 1100,得01 0010 0101 1100,即125C(H ).wt6qbkCyDE9.解:采用先来先服务调度算法,按照进程进入就绪队列地先后次序占有CPU,其执行次序是A-B-C-D.采用静态优先数法,进程A最先就绪,在0时刻先占有CPU运行,随后1时刻进程B 进入就绪队列,2时刻进程C进入就绪队列,3时刻进程D进入就绪队列.由于采用静态优先数法,不容许随时间地推移改变进程地优先级,所以当进程A运行结束时,系统地就绪队列中有B、C、D三个进程,而进程C优先级最高,于是选中C;这样分析下去,进程地执行次序是A-C-D-B. Kp5zH46zRk10.解:(1)定义二个信号量S1、S2,初值均为1,即:S1=1,S2=1.其中进程A和C使用信号量S1,进程B和D使用信号量S2.Yl4HdOAA61。

计算机操作系统名词解释计算机操作系统名词解释:1:操作系统(Operating System):是一种控制和管理计算机硬件与软件资源的系统软件,它允许用户与计算机硬件进行交互,并提供了资源分配、进程管理、文件系统管理等功能。

2:内核(Kernel):是操作系统的核心部分,负责管理和分配计算机的资源,控制硬件的访问和提供各种命令和服务。

内核分为微内核、宏内核、混合内核等不同架构。

3:进程(Process):是指正在执行中的一个程序,它拥有独立的内存空间和执行上下文,是操作系统资源分配的基本单位。

4:线程(Thread):是进程的一部分,是程序执行的最小单位。

它与进程共享同一地址空间和资源,可以执行独立的子任务。

5:调度(Scheduling):是指操作系统根据一定的策略和算法,将资源分配给不同的进程或线程的过程。

6:并发(Concurrency):指多个进程或线程可以同时执行,通过时间片轮转、优先级调度等方式共享计算机的资源。

7:死锁(Deadlock):是指多个进程或线程在争夺资源时,因互相等待对方释放资源而陷入无限等待的状态。

8:文件系统():是管理计算机存储设备中的文件和目录的方法,提供了文件的创建、删除、读取、写入等操作。

9:虚拟内存(Virtual Memory):是一种通过在硬盘上建立虚拟地址空间来扩充计算机的主存容量的技术。

它能够提供更大的内存空间,并优化内存的使用效率。

10:分页(Paging):是一种虚拟内存管理的技术,将主存分为固定大小的页,与磁盘上的页进行映射,以实现虚拟内存的需求。

11:缓存(Cache):是一种高速临时存储器,用于存储频繁访问的数据,提高计算机的读写性能。

12:设备驱动程序(Device Driver):是操作系统与硬件设备之间的接口,负责管理和控制硬件设备的访问。

13:多任务(Multitasking):是指操作系统能够同时执行多个任务的能力。

它可以通过时间片轮转、优先级调度等方式实现。

微内核操作系统及L4概述杰夫jliu71@摘要:本文是对微内核操作系统及L4的发展历程和主要功能的综述。

本文还对微内核操作系统的优缺点及发展前景发表评论。

关键词:微内核,操作系统,L4Abstract: This paper describes the history of microkernel-based operating systems, and the structure and main functions of L4. It also discusses the pros and cons of microkernel systems and their prospect of actual deployments in the industry.Keywords: microkernel, operating system, L41. Introduction微内核(microkernel)并非是一个新的概念,这个名词至少在七十年代初就有了。

一般认为,他的发明权属于Hansen [Han70] 和Wulf [Wul74]. 但是在这一名词出现之前已经有人使用类似的想法设计计算机操作系统了。

早期的操作系统绝大多数是Monolithic Kernel, 意思是整个操作系统 - 包括Scheduling (调度), File system (文件系统), Networking (网络), Device driver (设备驱动程序), Memory management (存储管理), Paging(存储页面管理) – 都在内核中完成。

一直到现在广泛应用的操作系统,如UNIX,Linux,和Windows还大都是monolithic kernel操作系统。

但随着操作系统变得越来越复杂(现代操作系统的内核有一两百万行C程序是很常见的事情),把所有这些功能都放在内核中使设计难度迅速增加。

微内核是一个与Monolithic Kernel相反的设计理念。

它的目的是使内核缩到最小,把所有可能的功能模块移出内核。

理想情况下,内核中仅留下Address Space Support(地址空间支持),IPC (Inter-Process Communication,进程间通讯),和Scheduling(调度),其他功能模块做为用户进程运行。

对于内核来说,他们和一般用户进程并无区别。

它们与其他用户进程之间的通讯通过IPC进行。

在八十年代中期,微内核的概念开始变得非常热门。

第一代微内核操作系统的代表作品是Mach [Mac85]。

Mach是由位于痞子堡的卡内基梅隆大学(CMU)设计。

CMU是美国计算机科学研究重镇,其计算机排名长期位于美国大学前五位。

美国只有少数几所大学的计算机是学院不是系,CMU就是其中之一。

除Mach外,CMU的另一重要成果是衡量计算机软件设计能力的CMM (Capability Maturity Model) 模型,广泛用于评估业界软件公司的计算机软件开发能力。

好像印度的软件公司们非常热衷于此,通过CMM-5最高规格评价的软件公司们有一半是印度的。

在微内核刚兴起时,学术界普遍认为其优点是显而易见的:•支持更加模块化的设计;•小的内核更易于更新与维护,bug会更少。

大家知道Windows 的死机很多是因为device drivers 造成的。

如果把他们移出内核,他们中的bugs很可能就不会造成死机;•许多模块的bugs 可被封闭在其模块内,更加易于debug。

软件工程师都知道 kernel debug 是件非常头疼的事情。

如果file system, memory management,和device drivers成为一个个独立的进程,不用说这肯定会使kernel engineers的日子好过许多。

由于上述原因,很多学术研究人员和软件厂家开始尝试使用微内核的概念设计操作系统。

甚至Microsoft也有所动作,在设计Windows NT时,他们把UI (User Interface) 从Windows kernel中整个拿了出来。

由此可看出microkernel的流行程度,因为Microsoft总是最后一个尝试新想法的。

但是这一热潮很快就冷了下来,原因只有一个字:Performance(Well,汉语是两个字:性能)。

Microsoft在Windows NT后续版本中,又把部分底层UI放回了Windows kernel。

这种现象在计算机界并不少见。

在Java刚开始流行时,由于其许多C/C++没有的优点,很多人认为它会很快取代C/C++成为第一编程语言。

但直至今天也没有发生,其中一个重要原因就是Java程序的performance落后于C程序,至今还限制着它在许多场合的应用。

第一代的微内核操作系统的性能,包括Mach在内,远不及monolithic kernel操作系统。

所以大多数人又回到传统技术中去了。

Microkernel也像过时的流行歌曲或减肥方法,很快被遗忘了。

但在九十年代后期,微内核迎来了其生命中的第二春。

一些研究人员认真分析了微内核系统性能差的原因,指出其性能差并非根本内在的因素造成,而是设计实现的失误。

为证明其论点,他们设计并实现了几个性能远超第一代的微内核操作系统,我们把它们称为第二代微内核系统 [Bar03, Eng95, Lie93A]。

其中的一个代表作品就是L4 [Lie93A, Lie93B, Lie95, Lie96]。

L4由德国的GMD设计。

GMD是德国国家信息技术研究院,相当于中科院计算所加上软件所(但在计算机研究能力方面,GMD远非中科院可比。

与作者一起工作过的几位GMD研究人员都是extremely smart)。

L4的创始人和总设计师是Jochen Liedtke [Kar05]。

此公在GMD之后,还供职于IBM的T.J. Watson Research Center,后成为德国Univ. of Karlsruhe操作系统方向的正教授(full professor)。

了解德国大学系统的人都知道,当德国的正教授可比当美国的正教授要难许多倍,地位也要高许多,因为一个系往往只有一两个正教授。

Prof. Liedtke已于2001年过世,但他创建的L4正在发展壮大中。

近年来,多个运行于不同硬件平台的L4系统已被几个不同研究机构设计出来 [SAG03, Tew01]。

本文以后的部分将分析微内核系统的performance bottleneck所在,以及L4如何试图克服这一困难。

微内核系统到底有没有固有的障碍,先天的缺陷?以L4为代表的新一代微内核系统的前景如何?请看下文。

2.微内核系统的性能为什么会这麽差?基于消息传递(Message Passing)IPC机制是微内核系统的基本特点之一。

这一设计理念有助于提高系统的灵活性,模块化,安全性,以及可扩展性。

IPC的性能表现是决定微内核系统性能的关键因素,因为绝大多数系统调用和很多应用程序的服务都需要两个IPC, 一个服务请求,一个结果返回。

消息传递IPC机制现在已经大量用于多种计算机系统中,但是很多IPC实现的性能并不太好。

根据CPU性能和消息长短不同,一个IPC大概需要50到500 µs。

经过许多研究人员多年的努力,也没有实现IPC性能的突破,所以直至最近,消息传递IPC被公认为使一个很好的设计理念,但对其适用范围学术界还存在很大争议。

Linux Kernel创始人Linus Torvalds 在2000年的一段话说得生动(Sorry,是极端),也代表了当时很多人的观点。

为了在有些读者受到冒犯时摆脱干系,作者决定不翻译以下这段话。

如果您看不懂,good for you.“Message passing as the fundamental operation of the operating system is just an exercise in computer science masturbation. It may feel good, but you don't actually get anything DONE. Nobody has ever shown that it made sense in the real world.”由于IPC对微内核系统的重要性,其设计人员们也花费了大量时间在改善它的性能上面。

微内核系统中IPC性能不断提高,但到90年代初似乎达到了顶峰。

Mach 3的IPC最好性能大约是115 µs (在486-DX 50机器上),其它微内核系统也大致如此。

当时许多研究人员认为,有100 µs 左右的时间是IPC的固有消耗,这一时间已无法缩短。

但是与之相比,在同样硬件平台上,一个UNIX系统调用只需要20 µs, 好过微内核系统10倍。

第一代微内核系统一直未在IPC性能上有重大突破,这是导致他们失败的根本原因。

对第一代微内核系统的性能分析表明,他的耗时巨大的操作包括用户-内核模式转换,地址空间转换,和内存访问。

表面上看起来这一结果似乎合理,但进一步分析发现它们并非真正问题所在。

[Lie96] 中给出Figure 1, 显示这些操作的硬件固Figure 1. IPC耗时分析有的时间消耗只占IPC 总耗时的3%- 7% (图中深色为硬件固有时间消耗)。

这些证据表明早期微内核的性能差距其实来自于它们的基本构造。

早期的微内核系统大多是由MonolithicKernel 一步步逐渐改进而来。

其很多设计并未发生重大改变。

他们虽然被称为微内核,但其代码量还是很大。

例如,Mach 3内核支持140个系统调用,代码量为300K 字节。

这种情况不改变,微内核系统的性能恐难提高。

第二代微内核系统设计者认识到这一问题,他们对系统内核的基本构造做出重大精简,从而使其性能大步提高。

L4只支持7个系统调用,代码量只有12K 字节。

本文下一部分将简单介绍L4的一些基本设计,有兴趣的读者可在 [Lie95] 中找到对L4的详细介绍。

3. L4 基本结构L4是由GMD 于1995年设计,它的两个基本设计原则是:1)高性能和灵活性的要求决定微内核必须尽可能缩到最小,2)微内核实现本身取决于硬件结构,它是不可移植的。

虽然微内核可以改善整个系统的移植性,但它本身是不可移植的,因为要达到高性能,它的实现必须紧密联系于硬件结构。

L4内核支持三种抽象概念:地址空间,线程,和IPC 。

他只提供7个系统调用,只有12K 字节代码。

在486-DX50 机器上,一个地址空间切换IPC, 8 字节参数传递,只需要5 µs 。