98C64A写入时序

- 格式:doc

- 大小:34.00 KB

- 文档页数:1

64 Kb I2C CMOS Serial EEPROMCAT24C64DescriptionThe CAT24C64 is a 64 Kb CMOS Serial EEPROM device, internally organized as 8192 words of 8 bits each.It features a 32−byte page write buffer and supports the Standard (100 kHz), Fast (400 kHz) and Fast−Plus (1 MHz) I2C protocol. External address pins make it possible to address up to eight CAT24C64 devices on the same bus.Features•Supports Standard, Fast and Fast−Plus I2C Protocol•1.7 V to 5.5 V Supply V oltage Range•32−Byte Page Write Buffer•Hardware Write Protection for Entire Memory•Schmitt Triggers and Noise Suppression Filters on I2C Bus Inputs (SCL and SDA)•Low Power CMOS Technology•1,000,000 Program/Erase Cycles•100 Year Data Retention•Industrial and Extended Temperature Range•SOIC, TSSOP, UDFN 8−pad and Ultra−thin WLCSP 4−bump Packages•This Device is Pb−Free, Halogen Free/BFR Free, and RoHS CompliantFigure 1. Functional Symbol SDASCL WPV CC SSA2, A1, APIN CONFIGURATIONS (Top Views)See detailed ordering and shipping information in the package dimensions section on page 8 of this data sheet.ORDERING INFORMATIONSOIC−8W SUFFIXCASE 751BDSOIC (W), TSSOP (Y),UDFN (HU4)Y SUFFIXCASE 948ALDevice AddressA0, A1, A2Serial DataSDASerial ClockSCLWrite ProtectWPPower SupplyV CCGroundV SSFunctionPin NamePIN FUNCTIONFor the location of Pin 1, please consult thecorresponding package drawing.UDFN−8HU4 SUFFIXCASE 517AZWLCSP−4C4C SUFFIXCASE 567JYSDAWPV CCV SSA2A1A01SCLWLCSPA1A2B1B2SDAV SSSCLV CC1X= Specific Device Code(see ordering information)Y= Production Year (Last Digit)M= Production Month (1−9, O, N, D)W= Production Week CodeMARKINGDIAGRAMS(WLCSP−4)WLCSP−4C4U SUFFIXCASE 567PBXYM(C4C)For serial EEPROM in a US8 package, pleaseTable 1. ABSOLUTE MAXIMUM RATINGSParameters Ratings Units Storage Temperature–65 to +150°C Voltage on Any Pin with Respect to Ground (Note 1)–0.5 to +6.5V Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.1.The DC input voltage on any pin should not be lower than −0.5 V or higher than V CC + 0.5 V. During transitions, the voltage on any pin mayundershoot to no less than −1.5 V or overshoot to no more than V CC + 1.5 V, for periods of less than 20 ns.Table 2. RELIABILITY CHARACTERISTICS (Note 2)Symbol Parameter Min UnitsN END (Note 3)Endurance1,000,000Program/Erase Cycles T DR Data Retention100Years2.These parameters are tested initially and after a design or process change that affects the parameter according to appropriate AEC−Q100and JEDEC test methods.3.Page Mode, V CC = 5 V, 25°C.Table 3. D.C. OPERATING CHARACTERISTICS(V CC = 1.8 V to 5.5 V, T A = −40°C to +125°C and V CC = 1.7 V to 5.5 V, T A = −40°C to +85°C, unless otherwise specified.)Symbol Parameter Test Conditions Min Max UnitsI CCR Read Current Read, f SCL = 400 kHz1mAI CCW Write Current Write, f SCL = 400 kHz2mAI SB Standby Current All I/O Pins at GND or V CC T A = −40°C to +85°CV CC≤ 3.3 V1m AT A = −40°C to +85°CV CC > 3.3 V3T A = −40°C to +125°C5I L I/O Pin Leakage Pin at GND or V CC2m AV IL Input Low Voltage−0.5V CC x 0.3V V IH Input High Voltage V CC x 0.7V CC + 0.5V V OL1Output Low Voltage V CC≥ 2.5 V, I OL = 3.0 mA0.4V V OL2Output Low Voltage V CC < 2.5 V, I OL = 1.0 mA0.2V Table 4. PIN IMPEDANCE CHARACTERISTICS(V CC = 1.8 V to 5.5 V, T A = −40°C to +125°C and V CC = 1.7 V to 5.5 V, T A = −40°C to +85°C, unless otherwise specified.) Symbol Parameter Conditions Max UnitsC IN (Note 4)SDA I/O Pin Capacitance V IN = 0 V8pFC IN (Note 4)Input Capacitance (other pins)V IN = 0 V6pFI WP (Note 5)WP Input Current V IN < V IH, V CC = 5.5 V130m AV IN < V IH, V CC = 3.3 V120V IN < V IH, V CC = 1.8 V80V IN> V IH2I A (Note 5)Address Input Current(A0, A1, A2)Product Rev F V IN < V IH, V CC = 5.5 V50m A V IN < V IH, V CC = 3.3 V35V IN < V IH, V CC = 1.8 V25V IN> V IH24.These parameters are tested initially and after a design or process change that affects the parameter according to appropriate AEC−Q100and JEDEC test methods.5.When not driven, the WP, A0, A1 and A2 pins are pulled down to GND internally. For improved noise immunity, the internal pull−down is relativelystrong; therefore the external driver must be able to supply the pull−down current when attempting to drive the input HIGH. T o conserve power, as the input level exceeds the trip point of the CMOS input buffer (~ 0.5 x V CC), the strong pull−down reverts to a weak current source.Table 5. A.C. CHARACTERISTICS(V CC = 1.8 V to 5.5 V, T A = −40°C to +125°C and V CC = 1.7 V to 5.5 V, T A = −40°C to +85°C.) (Note 6)Symbol ParameterStandardV CC = 1.7 V − 5.5 VFastV CC = 1.7 V − 5.5 VFast−PlusV CC = 1.7 V − 5.5 VT A = −405C to +855CUnits Min Max Min Max Min MaxF SCL Clock Frequency1004001,000kHzt HD:STA START Condition Hold Time40.60.25m s t LOW Low Period of SCL Clock 4.7 1.30.45m s t HIGH High Period of SCL Clock40.60.40m s t SU:STA START Condition Setup Time 4.70.60.25m s t HD:DAT Data In Hold Time000m s t SU:DAT Data In Setup Time25010050ns t R (Note 7)SDA and SCL Rise Time1,000300100ns t F (Note 7)SDA and SCL Fall Time300300100ns t SU:STO STOP Condition Setup Time40.60.25m s t BUF Bus Free Time BetweenSTOP and START4.7 1.30.5m st AA SCL Low to Data Out Valid 3.50.90.40m s t DH Data Out Hold Time10010050ns T i (Note 7)Noise Pulse Filtered at SCLand SDA Inputs100100100ns t SU:WP WP Setup Time000m s t HD:WP WP Hold Time 2.5 2.51m s t WR Write Cycle Time555mst PU (Notes 7, 8)Power−up to Ready Mode110.11ms Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.6.Test conditions according to “A.C. Test Conditions” table.7.Tested initially and after a design or process change that affects this parameter.8.t PU is the delay between the time V CC is stable and the device is ready to accept commands.Table 6. A.C. TEST CONDITIONSInput Levels0.2 x V CC to 0.8 x V CCInput Rise and Fall Times≤ 50 nsInput Reference Levels0.3 x V CC, 0.7 x V CCOutput Reference Levels0.5 x V CCOutput Load Current Source: I OL = 3 mA (V CC≥ 2.5 V); I OL = 1 mA (V CC< 2.5 V); C L = 100 pFPower −On Reset (POR)Each CAT24C64 incorporates Power −On Reset (POR)circuitry which protects the internal logic against powering up in the wrong state. The device will power up into Standby mode after V CC exceeds the POR trigger level and will power down into Reset mode when V CC drops below the POR trigger level. This bi −directional POR behavior protects the device against ‘brown −out’ failure following a temporary loss of power.Pin DescriptionSCL: The Serial Clock input pin accepts the clock signal generated by the Master.SDA: The Serial Data I/O pin accepts input data and delivers output data. In transmit mode, this pin is open drain. Data is acquired on the positive edge, and is delivered on the negative edge of SCL.A 0, A 1 and A 2: The Address inputs set the device address that must be matched by the corresponding Slave address bits. The Address inputs are hard −wired HIGH or LOW allowing for up to eight devices to be used (cascaded) on the same bus. When left floating, these pins are pulled LOW internally. The Address inputs are not available for use with WLCSP 4−bumps.WP: When pulled HIGH, the Write Protect input pin inhibits all write operations. When left floating, this pin is pulled LOW internally. The WP input is not available for the WLCSP 4−bumps, therefore all write operations are allowed for the device in this package.Functional DescriptionThe CAT24C64 supports the Inter −Integrated Circuit (I 2C) Bus protocol. The protocol relies on the use of a Master device, which provides the clock and directs bus traffic, and Slave devices which execute requests. The CAT24C64operates as a Slave device. Both Master and Slave cantransmit or receive, but only the Master can assign those roles.I 2C Bus ProtocolThe 2−wire I 2C bus consists of two lines, SCL and SDA,connected to the V CC supply via pull −up resistors. The Master provides the clock to the SCL line, and either the Master or the Slaves drive the SDA line. A ‘0’ is transmitted by pulling a line LOW and a ‘1’ by letting it stay HIGH. Data transfer may be initiated only when the bus is not busy (see A.C. Characteristics). During data transfer, SDA must remain stable while SCL is HIGH.START/STOP Condition An SDA transition while SCL is HIGH creates a START or STOP condition (Figure 2). The START consists of a HIGH to LOW SDA transition, while SCL is HIGH. Absent the START, a Slave will not respond to the Master. The STOP completes all commands, and consists of a LOW to HIGH SDA transition, while SCL is HIGH.Device AddressingThe Master addresses a Slave by creating a START condition and then broadcasting an 8−bit Slave address. For the CA T24C64, the first four bits of the Slave address are set to 1010 (Ah); the next three bits, A 2, A 1 and A 0, must match the logic state of the similarly named input pins. The devices in WLCSP 4−bumps respond only to the Slave Address with A2 A1 A0 = 000 (CA T24C64C4xTR). The R/W bit tells the Slave whether the Master intends to read (1) or write (0) data (Figure 3).AcknowledgeDuring the 9th clock cycle following every byte sent to the bus, the transmitter releases the SDA line, allowing the receiver to respond. The receiver then either acknowledges (ACK) by pulling SDA LOW, or does not acknowledge (NoACK) by letting SDA stay HIGH (Figure 4). Bus timing is illustrated in Figure 5.START CONDITIONSTOP CONDITIONSDASCLFigure 2. Start/Stop TimingFigure 3. Slave Address BitsDEVICE ADDRESS** The devices in WLCSP 4−bumps respond only to the Slave Address with: A2 A1 A0 = 000, CAT24C64C4xTRFigure 4. Acknowledge TimingSCL FROM MASTERDATA OUTPUTFROM TRANSMITTERDATA OUTPUT FROM RECEIVER≥ t SU:DAT )Figure 5. Bus TimingSCLSDA INSDA OUTWRITE OPERATIONSByte WriteTo write data to memory, the Master creates a START condition on the bus and then broadcasts a Slave address with the R/W bit set to ‘0’. The Master then sends two address bytes and a data byte and concludes the session by creating a STOP condition on the bus. The Slave responds with ACK after every byte sent by the Master (Figure 6). The STOP starts the internal Write cycle, and while this operation is in progress (t WR ), the SDA output is tri −stated and the Slave does not acknowledge the Master (Figure 7).Page WriteThe Byte Write operation can be expanded to Page Write,by sending more than one data byte to the Slave before issuing the STOP condition (Figure 8). Up to 32 distinct data bytes can be loaded into the internal Page Write Buffer starting at the address provided by the Master. The page address is latched, and as long as the Master keeps sending data, the internal byte address is incremented up to the end of page, where it then wraps around (within the page). New data can therefore replace data loaded earlier. Following the STOP, data loaded during the Page Write session will be written to memory in a single internal Write cycle (t WR ).Acknowledge PollingAs soon (and as long) as internal Write is in progress, the Slave will not acknowledge the Master. This feature enables the Master to immediately follow −up with a new Read or Write request, rather than wait for the maximum specified Write time (t WR ) to elapse. Upon receiving a NoACK response from the Slave, the Master simply repeats the request until the Slave responds with ACK.Hardware Write ProtectionWith the WP pin held HIGH, the entire memory is protected against Write operations. If the WP pin is left floating or is grounded, it has no impact on the Write operation. The state of the WP pin is strobed on the last falling edge of SCL immediately preceding the 1st data byte (Figure 9). If the WP pin is HIGH during the strobe interval,the Slave will not acknowledge the data byte and the Write request will be rejected.Delivery StateThe CAT24C64 is shipped erased, i.e., all bytes are FFh.SLAVE ADDRESSSA ***C KA C KA C KS T O P PST ARTA CKBUS ACTIVITY:MASTER SLAVEADDRESS BYTE ADDRESS BYTE DAT A BYTE Figure 6. Byte Write Sequence*a 15 − a 13 are don’t care bits.a 15 − a 8a 7 − a 0d 7 − d 0Figure 7. Write Cycle TimingSTOPCONDITIONSTARTCONDITIONADDRESSSCLSDASLAVE ADDRESSSA C K A C K C K ST ARTC K S T O C KC K C K BUSACTIVITY:MASTER SLAVEADDRESS BYTE ADDRESS BYTEDATA BYTE DATA BYTE DATA BYTE Figure 8. Page Write SequenceFigure 9. WP TimingADDRESS BYTE DATA BYTESCLSDA WPREAD OPERATIONSImmediate ReadTo read data from memory, the Master creates a START condition on the bus and then broadcasts a Slave address with the R/W bit set to ‘1’. The Slave responds with ACK and starts shifting out data residing at the current address.After receiving the data, the Master responds with NoACK and terminates the session by creating a STOP condition on the bus (Figure 10). The Slave then returns to Standby mode.Selective ReadTo read data residing at a speci fic address, the selected address must first be loaded into the internal address register.This is done by starting a Byte Write sequence, whereby the Master creates a START condition, then broadcasts a Slave address with the R/W bit set to ‘0’ and then sends two address bytes to the Slave. Rather than completing the ByteWrite sequence by sending data, the Master then creates a START condition and broadcasts a Slave address with the R/W bit set to ‘1’. The Slave responds with ACK after every byte sent by the Master and then sends out data residing at the selected address. After receiving the data, the Master responds with NoACK and then terminates the session by creating a STOP condition on the bus (Figure 11).Sequential ReadIf, after receiving data sent by the Slave, the Master responds with ACK, then the Slave will continue transmitting until the Master responds with NoACK followed by STOP (Figure 12). During Sequential Read the internal byte address is automatically incremented up to the end of memory, where it then wraps around to the beginning of memory.Figure 10. Immediate Read Sequence and TimingSCL SDA 8th Bit STOPNO ACKDATA OUT89SLAVE ADDRESSSA C KDATA BYTEN OA C K S T O P PST ARTBUS ACTIVITY:MASTER SLAVEFigure 11. Selective Read SequenceSLAVE ADDRESS SA C KA C KA C K ST ARTSLAVE SA C KS T A R T PS T O P ADDRESS BYTE ADDRESS BYTE ADDRESSN O A C KDATA BYTEBUS ACTIVITY:MASTER SLAVEFigure 12. Sequential Read SequenceS T O SLAVE C KA C A C N O A C A C BYTE n BYTE n+1BYTE n+2BYTE n+xBUS ACTIVITY:MASTERSLAVEORDERING INFORMATIONDevice Order Number SpecificDeviceMarking Package Type Temperature Range Lead Finish ShippingCAT24C64WI−GT324C64F SOIC−8, JEDEC I = Industrial(−40°C to +85°C)NiPdAu Tape & Reel,3,000 Units / ReelCAT24C64YI−GT3C64F TSSOP−8I = Industrial(−40°C to +85°C)NiPdAu Tape & Reel,3,000 Units / ReelCAT24C64HU4I−GT3C6U UDFN−8I = Industrial(−40°C to +85°C)NiPdAu Tape & Reel,3,000 Units / ReelCAT24C64C4CTR A WLCSP−4with Die CoatIndustrial(−40°C to +85°C)N/A Tape & Reel,5,000 Units / ReelCAT24C64C4UTR A WLCSP−4with Die CoatIndustrial(−40°C to +85°C)N/A Tape & Reel,5,000 Units / Reel9.All packages are RoHS−compliant (Lead−free, Halogen−free).10.The standard lead finish is NiPdAu.11.For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel PackagingSpecifications Brochure, BRD8011/D.12.Caution: The EEPROM devices delivered in WLCSP must never be exposed to ultra violet light. When exposed to ultra violet lightthe EEPROM cells lose their stored data.UDFN8, 2x3 EXTENDED PADCASE 517AZ ISSUE ADATE 23 MAR 2015SCALE 2:1NOTES:1.DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.DIMENSION b APPLIES TO PLATEDTERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.25MM FROM THE TERMINAL TIP .4.COPLANARITY APPLIES TO THE EXPOSEDPAD AS WELL AS THE TERMINALS.DIM MIN MAX MILLIMETERS A 0.450.55A10.000.05b 0.200.30D 2.00 BSC D2 1.35 1.45E 3.00 BSC E2 1.25 1.35e 0.50 BSC L 0.250.35*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*DIMENSIONS: MILLIMETERSDETAIL AA30.13 REF L1DETAIL ALALTERNATE CONSTRUCTIONSLL1−−−0.15RECOMMENDEDGENERICMARKING DIAGRAM*XXXXX = Specific Device Code A = Assembly Location WL = Wafer Lot Y = YearW = Work WeekG= Pb −Free Package*This information is generic. Please refer to device data sheet for actual part marking.Pb −Free indicator, “G” or microdot “ G ”,may or may not be present.XXXXX AWLYW G18XDETAIL BALTERNATE CONSTRUCTIONSWLCSP4, 0.77x0.77CASE 567JY ISSUE CDATE 07 MAR 2017PIN A1REFERENCESCALE 4:1TOP VIEWBOTTOM VIEWDIMENSIONS: MILLIMETERS*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*RECOMMENDEDNOTES:1.DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.DATUM C, THE SEATING PLANE, IS DEFINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.4.COPLANARITY APPLIES TO SPHERICAL CROWNS OF THE SOLDER BALLS.5.DIMENSION b IS MEASURED AT THE MAXIMUMCONTACT BALL DIAMETER PARALLEL TO DATUM C.6.BACKSIDE COATING IS OPTIONAL.DIM A MIN NOM −−−MILLIMETERS A1D E b 0.150.155e0.40 BSC−−−0.040.06A20.23 REF A30.025 REF 0.750.770.750.77MAX 0.160.350.080.790.79DETAIL ANOTE 6X = Specific Device Code Y = YearW= Work Week*This information is generic. Please refer to device data sheet for actual part marking.Pb −Free indicator, “G” or microdot “ G ”,may or may not be present.GENERICMARKING DIAGRAM*X YWWLCSP4, 0.77x0.77CASE 567PBISSUE ADATE 09 NOV 2016PIN A1REFERENCESCALE 4:1TOP VIEWBOTTOM VIEWDIMENSIONS: MILLIMETERS*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering andMounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*RECOMMENDEDNOTES:1.DIMENSIONING AND TOLERANCING PER ASMEY14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.DATUM C, THE SEATING PLANE, IS DEFINED BY THESPHERICAL CROWNS OF THE SOLDER BALLS.4.COPLANARITY APPLIES TO SPHERICAL CROWNS OFTHE SOLDER BALLS.5.DIMENSION b IS MEASURED AT THE MAXIMUMCONTACT BALL DIAMETER PARALLEL TO DATUM C.6.BACKSIDE COATING IS OPTIONAL.DIMAMIN NOM−−−MILLIMETERSA1DEb0.150.155e0.40 BSC−−−0.040.055A20.19 REFA30.025 REF0.750.770.750.77MAX0.160.300.070.790.79DETAIL ANOTE 6X= Specific Device CodeY= YearW= Work Week*This information is generic. Please refer todevice data sheet for actual part marking.Pb−Free indicator, “G” or microdot “ G”,may or may not be present.GENERICMARKING DIAGRAM*XYWSOIC −8, 150 mils CASE 751BD ISSUE ODATE 19 DEC 2008IDENTIFICATIONTOP VIEWSIDE VIEWEND VIEWNotes:(1) All dimensions are in millimeters. Angles in degrees.(2) Complies with JEDEC MS-012.SYMBOLMIN NOM MAX θA A1b cD E E1e h 0º8º0.100.330.190.254.805.803.801.27 BSC1.750.250.510.250.505.006.204.00L0.401.271.35TSSOP8, 4.4x3.0, 0.65PCASE 948AL ISSUE ADATE 20 MAY 2022qXXX = Specific Device Code Y = YearWW = Work WeekA = Assembly Location G= Pb −Free Package*This information is generic. Please refer to device data sheet for actual part marking.Pb −Free indicator, “G” or microdot “G ”, may or may not be present. Some products may not follow the Generic Marking.GENERICMARKING DIAGRAM*XXX YWW A GPUBLICATION ORDERING INFORMATIONTECHNICAL SUPPORTLITERATURE FULFILLMENT:。

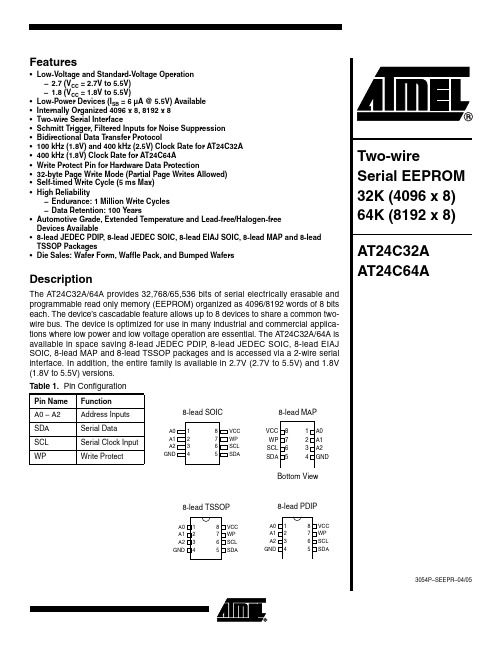

1Features•Low-Voltage and Standard-Voltage Operation –2.7 (V CC = 2.7V to 5.5V)–1.8 (V CC = 1.8V to 5.5V)•Low-Power Devices (I SB = 6 µA @ 5.5V) Available •Internally Organized 4096 x 8, 8192 x 8•Two-wire Serial Interface•Schmitt Trigger, Filtered Inputs for Noise Suppression •Bidirectional Data Transfer Protocol•100 kHz (1.8V) and 400 kHz (2.5V) Clock Rate for AT24C32A •400 kHz (1.8V) Clock Rate for AT24C64A•Write Protect Pin for Hardware Data Protection•32-byte Page Write Mode (Partial Page Writes Allowed)•Self-timed Write Cycle (5 ms Max)•High Reliability–Endurance: 1 Million Write Cycles–Data Retention: 100 Years•Automotive Grade, Extended Temperature and Lead-free/Halogen-free Devices Available•8-lead JEDEC PDIP , 8-lead JEDEC SOIC, 8-lead EIAJ SOIC, 8-lead MAP and 8-lead TSSOP Packages•Die Sales: Wafer Form, Waffle Pack, and Bumped WafersDescriptionThe AT24C32A/64A provides 32,768/65,536 bits of serial electrically erasable and programmable read only memory (EEPROM) organized as 4096/8192 words of 8 bits each. The device’s cascadable feature allows up to 8 devices to share a common two-wire bus. The device is optimized for use in many industrial and commercial applica-tions where low power and low voltage operation are essential. The AT24C32A/64A is available in space saving 8-lead JEDEC PDIP , 8-lead JEDEC SOIC, 8-lead EIAJ SOIC, 8-lead MAP and 8-lead TSSOP packages and is accessed via a 2-wire serial interface. In addition, the entire family is available in 2.7V (2.7V to 5.5V) and 1.8V (1.8V to 5.5V) versions.Table 1. Pin ConfigurationPin Name Function A0 – A2Address Inputs SDA Serial Data SCL Serial Clock Input WPWrite Protect8-lead PDIP8-lead SOIC8-lead TSSOP8-lead MAPBottom View2AT24C32A/64A3054P–SEEPR–04/05Figure 1. Block DiagramAbsolute Maximum Ratings*Operating T emperature..................................–55°C to +125°C *NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent dam-age to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Storage T emperature.....................................–65°C to +150°C Voltage on Any Pinwith Respect to Ground....................................–1.0V to +7.0V Maximum Operating Voltage ..........................................6.25V DC Output Current........................................................5.0 mA3AT24C32A/64A3054P–SEEPR–04/05Pin DescriptionSERIAL CLOCK (SCL): The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.SERIAL DATA (SDA): The SDA pin is bidirectional for serial data transfer. This pin is open-drain driven and may be wire-ORed with any number of other open-drain or open collector devices.DEVICE/ADDRESSES (A2, A1, A0): The A2, A1 and A0 pins are device address inputs that are hardwired or left not connected for hardware compatibility with other AT24Cxx devices. When the pins are hardwired, as many as eight 32K/64K devices may be addressed on a single bus system (device addressing is discussed in detail under the Device Addressing section). If the pins are left floating, the A2, A1 and A0 pins will be internally pulled down to GND if the capacitive coupling to the circuit board V CC plane is <3 pF. If coupling is >3 pF, Atmel recommends connecting the address pins to GND.WRITE PROTECT (WP): The write protect input, when connected to GND, allows nor-mal write operations. When WP is connected high to V CC , all write operations to the memory are inhibited. If the pin is left floating, the WP pin will be internally pulled down to GND if the capacitive coupling to the circuit board V CC plane is <3 pF. If coupling is >3pF, Atmel recommends connecting the pin to GND. Switching WP to V CC prior to a write operation creates a software write protect function.Memory OrganizationAT24C32A/64A, 32K/64K SERIAL EEPROM: The 32K/64K is internally organized as 128/256 pages of 32 bytes each. Random word addressing requires a 12/13-bit data word address.4AT24C32A/64A3054P–SEEPR–04/05Note:1.This parameter is characterized and is not 100% tested.Note:1.V IL min and V IH max are reference only and are not tested.Table 2. Pin Capacitance (1)Applicable over recommended operating range from T A = 25°C, f = 1.0 MHz, V CC = +1.8V.Symbol Test ConditionMax Units Conditions C I/O Input/Output Capacitance (SDA)8pF V I/O = 0V C IN Input Capacitance (A 0, A 1, A 2, SCL)6pFV IN = 0VTable 3. DC CharacteristicsApplicable over recommended operating range from: T AI = –40°C to +85°C, V CC = +1.8V to +5.5V, T AE = –40°C to +125°C,V CC = +1.8V to +5.5V (unless otherwise noted).Symbol Parameter Test ConditionMin TypMax Units V CC1Supply Voltage 1.8 5.5V V CC2Supply Voltage 2.5 5.5V V CC3Supply Voltage 2.7 5.5V V CC4Supply Voltage 4.55.5V I CC1Supply Current V CC = 5.0V READ at 400 kHz 0.4 1.0mA I CC2Supply Current V CC = 5.0V WRITE at 400 kHz 2.0 3.0mA I SB1Standby Current (1.8V option)V CC = 1.8V V IN = V CC or V SS 1.0µA I SB2Standby Current (2.5V option)V CC = 2.5V V IN = V CC or V SS 2.0µA I SB3Standby Current (2.7V option)V CC = 2.7V V IN = V CC or V SS 2.0µA I SB4Standby Current (5V option)V CC = 4.5 - 5.5V V IN = V CC or V SS6.0µA I LI Input Leakage CurrentV IN = V CC or V SS 0.10 3.0µA I LO Output Leakage Current V OUT = V CC or V SS0.053.0µA V IL (1)Input Low Level –0.6V CC x 0.3V V IH (1)Input High Level V CC x 0.7V CC + 0.5V V OL2Output Low Level V CC = 3.0V I OL = 2.1 mA 0.4V V OL1Output Low LevelV CC = 1.8VI OL = 0.15 mA0.2V5AT24C32A/64A3054P–SEEPR–04/05Notes:1.This parameter is characterized and is not 100% tested.2.This parameter is characterized and is not 100% tested (T A = 25°C).3.The Write Cycle Time of 5 ms only applies to the A T24C32A/64A devices bearing the process letter “A” on the package (themark is located in the lower right corner on the top side of the package).Table 4. AC CharacteristicsApplicable over recommended operating range from T AI = –40°C to +85°C, T AE = –40°C to +125°C, V CC = +1.8V to +5.5V,CL = 1 TTL Gate and100 pF (unless otherwise noted).Symbol ParameterAT24C32A AT24C64AUnits 1.8V2.5V – 5.0V 1.8V –3.6V 5.0VMinMax MinMax MinMax MinMax f SCL Clock Frequency, SCL 100400400400kHz t LOW Clock Pulse Width Low 4.7 1.3 1.3 1.2µs t HIGH Clock Pulse Width High 4.00.60.60.6µs t I Noise Suppression Time (1)1005010050ns t AA Clock Low to Data Out Valid 0.1 4.50.10.90.20.90.10.9µs t BUF Time the bus must be free before a new transmission can start (1) 4.7 1.3 1.3 1.2µs t HD.ST A Start Hold Time 4.00.60.60.6µs t SU.ST A Start Set-up Time 4.70.60.60.6µs t HD.DA T Data In Hold Time 0000µs t SU.DAT Data In Set-up Time 200100100100ns t R (1)Inputs Rise Time 1.00.30.30.3µs t F (1)Inputs Fall Time 300300300300ns t SU.STO Stop Set-up Time 4.70.60.60.6µs t DH Data Out Hold Time 1005020050ns t WRWrite Cycle Time 20 or 5(3)10 or 5(3)20 or 5(3)10 or 5(3)ms Endurance (1) 5.0V , 25°C, Page Mode1M 1M1M1MWrite Cycles6AT24C32A/64A3054P–SEEPR–04/05Device OperationCLOCK and DATA TRANSITIONS: The SDA pin is normally pulled high with an exter-nal device. Data on the SDA pin may change only during SCL low time periods (refer to Data Validity timing diagram). Data changes during SCL high periods will indicate a start or stop condition as defined below.START CONDITION: A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (see Figure 5 on page 8).STOP CONDITION: A low-to-high transition of SDA with SCL high is a stop condition.After a read sequence, the stop command will place the EEPROM in a standby power mode (see Figure 5 on page 8).ACKNOWLEDGE: All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a zero during the ninth clock cycle to acknowledge that it has received each word.STANDBY MODE: The AT24C32A/64A features a low power standby mode which is enabled: a) upon power-up and b) after the receipt of the stop bit and the completion of any internal operations.MEMORY RESET: After an interruption in protocol, power loss or system reset, any two-wire part can be reset by following these steps:(a) Clock up to 9 cycles, (b) look for SDA high in each cycle while SCL is high and then (c) create a start condition as SDA is high.7AT24C32A/64A3054P–SEEPR–04/05Figure 2. Bus TimingSCL: Serial Clock, SDA: Serial Data I/OFigure 3. Write Cycle TimingSCL: Serial Clock, SDA: Serial Data I/ONote:1.The write cycle time t WR is the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.Figure 4.Data Validity8AT24C32A/64A3054P–SEEPR–04/05Figure 5. Start and Stop DefinitionFigure 6.Output Acknowledge9AT24C32A/64A3054P–SEEPR–04/05Device AddressingThe 32K/64K EEPROM requires an 8-bit device address word following a start condition to enable the chip for a read or write operation (see Figure 7 on page 11). The device address word consists of a mandatory one, zero sequence for the first four most signifi-cant bits as shown. This is common to all 2-wire EEPROM devices.The 32K/64K uses the three device address bits A2, A1, A0 to allow as many as eight devices on the same bus. These bits must compare to their corresponding hardwired input pins. The A2, A1, and A0 pins use an internal proprietary circuit that biases them to a logic low condition if the pins are allowed to float.The eighth bit of the device address is the read/write operation select bit. A read opera-tion is initiated if this bit is high and a write operation is initiated if this bit is low.Upon a compare of the device address, the EEPROM will output a zero. If a compare is not made, the device will return to standby state.NOISE PROTECTION: Special internal circuitry placed on the SDA and SCL pins pre-vent small noise spikes from activating the device.DATA SECURITY: The AT24C32A/64A has a hardware data protection scheme that allows the user to write protect the entire memory when the WP pin is at V CC .Write OperationsBYTE WRITE: A write operation requires two 8-bit data word addresses following the device address word and acknowledgment. Upon receipt of this address, the EEPROM will again respond with a zero and then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will output a zero and the addressing device, such as a microcontroller, must terminate the write sequence with a stop condi-tion. At this time the EEPROM enters an internally-timed write cycle, t WR , to the nonvolatile memory. All inputs are disabled during this write cycle and the EEPROM will not respond until the write is complete (see Figure 8 on page 11).PAGE WRITE: The 32K/64K EEPROM is capable of 32-byte page writes.A page write is initiated the same way as a byte write, but the microcontroller does not send a stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the microcontroller can transmit up to 31more data words. The EEPROM will respond with a zero after each data word received.The microcontroller must terminate the page write sequence with a stop condition (see Figure 9 on page 11).The data word address lower five bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented, retaining the memory page row location. When the word address, internally generated, reaches the page boundary, the following byte is placed at the beginning of the same page. If more than 32 data words are transmitted to the EEPROM, the data word address will “roll over” and previous data will be overwritten.ACKNOWLEDGE POLLING: Once the internally-timed write cycle has started and the EEPROM inputs are disabled, acknowledge polling can be initiated. This involves send-ing a start condition followed by the device address word. The read/write bit is representative of the operation desired. Only if the internal write cycle has completed will the EEPROM respond with a zero, allowing the read or write sequence to continue.10AT24C32A/64A3054P–SEEPR–04/05Read OperationsRead operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to one. There are three read operations: current address read, random address read and sequential read.CURRENT ADDRESS READ: The internal data word address counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address “roll over” during read is from the last byte of the last memory page, to the first byte of the first page. The address “roll over” during write is from the last byte of the cur-rent page to the first byte of the same page.Once the device address with the read/write select bit set to one is clocked in and acknowledged by the EEPROM, the current address data word is serially clocked out.The microcontroller does not respond with an input zero but does generate a following stop condition (see Figure 10 on page 11).RANDOM READ: A random read requires a “dummy” byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another start condition. The microcontroller now initiates a current address read by sending a device address with the read/write select bit high. The EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a zero but does generate a following stop condition (see Figure 11 on page 12).SEQUENTIAL READ: Sequential reads are initiated by either a current address read or a random address read. After the microcontroller receives a data word, it responds with an acknowledge. As long as the EEPROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words. When the memory address limit is reached, the data word address will “roll over” and the sequen-tial read will continue. The sequential read operation is terminated when the microcontroller does not respond with a zero but does generate a following stop condi-tion (see Figure 12 on page 12).11AT24C32A/64A3054P–SEEPR–04/05Figure 7. Device AddressFigure 8. Byte WriteFigure 9. Page WriteNotes:1.* = DON’T CARE bits2.† = DON’T CARE bits for the 32KFigure 10.Current Address Read12AT24C32A/64A3054P–SEEPR–04/05Figure 11. Random ReadNote: 1.* = DON’T CARE bitsFigure 12.Sequential Read13AT24C32A/64A3054P–SEEPR–04/05Notes:1.For2.7V devices used in the 4.5V to 5.5V range, please refer to performance values in the AC and DC Characteristicstables.2.“U” and “Q” designate Green package and ROHS Compliance.3.Available in waffle pack and wafer form; order as SL719 for wafer form. Bumped die available upon request. Please contactSerial EEPROM Marketing.AT24C32A Ordering Information (1)Ordering Code Package Operation Range A T24C32A-10PI-2.7A T24C32AN-10SI-2.7A T24C32AW-10SI-2.7A T24C32A-10TI-2.78P38S18S28A2Industrial Temperature (–40°C to 85°C)A T24C32A-10PI-1.8A T24C32AN-10SI-1.8A T24C32AW-10SI-1.8A T24C32A-10TI-1.88P38S18S28A2Industrial Temperature (–40°C to 85°C)A T24C32A-10PU-2.7(2)A T24C32A-10PU-1.8(2)A T24C32AN-10SU-2.7(2)A T24C32AN-10SU-1.8(2)A T24C32AW-10SU-2.7(2)A T24C32AW-10SU-1.8(2)A T24C32A-10TU-2.7(2)A T24C32A-10TU-1.8(2)A T24C32AY1-10YU-1.8(2)8P38P38S18S18S28S28A28A28Y1Lead-free/Halogen-free/Industrial Temperature (–40°C to 85°C)A T24C32A-10PQ-2.7(2)A T24C32AN-10SQ-2.7(2)A T24C32A-10TQ-2.7(2)8P38S18A2Lead-free/Halogen-free/Extended T emperature (–40°C to 125°C)A T24C32A-10PE-2.7A T24C32AN-10SE-2.78P38S1Extended T emperature (–40°C to 125°C)A T24C32A-W2.7-11(3)A T24C32A-W1.8-11(3)Die Sale Die SaleIndustrial Temperature (–40°C to 85°C)Package Type8P38-lead, 0.300" Wide, Plastic Dual In-line Package (PDIP)8S18-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8S28-lead, 0.209" Body, Plastic Small Outline (EIAJ SOIC)8A28-lead, 4.4 mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)8Y18-lead, 4.90 mm x 3.00 mm Body, Dual Footprint, Non-leaded, Miniature Array Package (MAP)Options–2.7Low Voltage (2.7V to 5.5V)–1.8Low Voltage (1.8V to 5.5V)14AT24C32A/64A3054P–SEEPR–04/05Notes:1.For2.7V devices used in the 4.5V to 5.5V range, please refer to performance values in the AC and DC Characteristicstables.2.“U” and “Q” designate Green package and ROHS Compliance.3.Available in waffle pack and wafer form; order as SL719 for wafer form. Bumped die available upon request. Please contactSerial EEPROM Marketing.AT24C64A Ordering Information (1)Ordering Code Package Operation Range A T24C64A-10PI-2.7A T24C64AN-10SI-2.7A T24C64AW-10SI-2.7A T24C64A-10TI-2.78P38S18S28A2Industrial Temperature (–40°C to 85°C)A T24C64A-10PI-1.8A T24C64AN-10SI-1.8A T24C64AW-10SI-1.8A T24C64A-10TI-1.88P38S18S28A2Industrial Temperature (–40°C to 85°C)A T24C64A-10PU-2.7(2)A T24C64A-10PU-1.8(2)A T24C64AN-10SU-2.7(2)A T24C64AN-10SU-1.8(2)A T24C64AW-10SU-2.7(2)A T24C64AW-10SU-1.8(2)A T24C64A-10TU-2.7(2)A T24C64A-10TU-1.8(2)A T24C64AY1-10YU-1.8(2)8P38P38S18S18S28S28A28A28Y1Lead-free/Halogen-free/Industrial Temperature (–40°C to 85°C)A T24C64A-10PQ-2.7(2)A T24C64AN-10SQ-2.7(2)A T24C64A-10TQ-2.7(2)8P38S18A2Lead-free/Halogen-free/Extended T emperature (–40°C to 125°C)A T24C64A-10PE-2.7A T24C64AN-10SE-2.78P38S1Extended T emperature (–40°C to 125°C)A T24C64A-W2.7-11(3)A T24C64A-W1.8-11(3)Die Sale Die SaleIndustrial Temperature (–40°C to 85°C)Package Type8P38-lead, 0.300" Wide, Plastic Dual In-line Package (PDIP)8S18-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8S28-lead, 0.209" Body, Plastic Small Outline (EIAJ SOIC)8A28-lead, 4.4mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)8Y18-lead, 4.90 mm x 3.00 mm Body, Dual Footprint, Non-leaded, Miniature Array Package (MAP)Options–2.7Low Voltage (2.7V to 5.5V)–1.8Low Voltage (1.8V to 5.5V)15AT24C32A/64A3054P–SEEPR–04/05Package Drawings8P3 – PDIP16AT24C32A/64A3054P–SEEPR–04/058S1 – JEDEC SOIC17AT24C32A/64A3054P–SEEPR–04/058S2 – EIAJ SOIC18AT24C32A/64A3054P–SEEPR–04/058A2 – TSSOP19AT24C32A/64A3054P–SEEPR–04/058Y1 – MAP3054P–SEEPR–04/05Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise,to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL ’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL ’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.Atmel CorporationAtmel Operations2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 487-2600Regional HeadquartersEuropeAtmel SarlRoute des Arsenaux 41Case Postale 80CH-1705 Fribourg SwitzerlandTel: (41) 26-426-5555Fax: (41) 26-426-5500AsiaRoom 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong KongTel: (852) 2721-9778Fax: (852) 2722-1369Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Memory2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314Microcontrollers2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314La Chantrerie BP 7060244306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18Fax: (33) 2-40-18-19-60ASIC/ASSP/Smart CardsZone Industrielle13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00Fax: (33) 4-42-53-60-011150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Scottish Enterprise Technology Park Maxwell BuildingEast Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000Fax: (44) 1355-242-743RF/AutomotiveTheresienstrasse 2Postfach 353574025 Heilbronn, Germany Tel: (49) 71-31-67-0Fax: (49) 71-31-67-23401150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Biometrics/Imaging/Hi-Rel MPU/High Speed Converters/RF DatacomAvenue de Rochepleine BP 12338521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00Fax: (33) 4-76-58-34-80Literature Requests/literature© Atmel Corporation 2005. All rights reserved. Atmel ®, logo and combinations thereof, Everywhere You Are ® and others are registered trade-marks, and others are the trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.。

Features•Standard-Voltage Operation –2.7 (V CC = 2.7V to 5.5V)•Internally Organized 4096 x 8 (32K), 8192 x 8 (64K)•Automotive Temperature Range –40°C to +125°C •Two-wire Serial Interface•Schmitt Trigger, Filtered Inputs for Noise Suppression •Bidirectional Data Transfer Protocol •400 kHz Clock Rate•Write Protect Pin for Hardware Data Protection•32-byte Page Write Mode (Partial Page Writes Allowed)•Self-timed Write Cycle (5 ms Max)•High Reliability–Endurance: 1 Million Write Cycles –Data Retention: 100 Years•Lead-free/Halogen-free Devices Available•8-lead JEDEC SOIC and 8-lead TSSOP PackagesDescriptionThe AT24C32A/64A provides 32,768/65,536 bits of serial electrically erasable and programmable read only memory (EEPROM) organized as 4096/8192 words of 8 bits each. The device’s cascadable feature allows up to 8 devices to share a common two-wire bus. The device is optimized for use in many automotive applications where low power and low voltage operation are essential. The AT24C32A/64A is available in space saving 8-lead JEDEC SOIC and 8-lead TSSOP packages and is accessed via a 2-wire serial interface and is available in a 2.7V (2.7V to 5.5V) version.Table 1. Pin ConfigurationPin Name Function A0 – A2Address InputsSDA Serial Data SCL Serial Clock Input WPWrite Protect8-lead SOIC8-lead TSSOPBDTIC www.BDTIC .com/ATMEL25120D–SEEPR–6/08AT24C32A/64AFigure 1. Block DiagramAbsolute Maximum Ratings*Operating T emperature..................................–55°C to +125°C *NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent dam-age to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Storage T emperature.....................................–65°C to +150°C Voltage on Any Pinwith Respect to Ground....................................–1.0V to +7.0V Maximum Operating Voltage ..........................................6.25V DC Output Current........................................................5.0 mA35120D–SEEPR–6/08AT24C32A/64APin DescriptionSERIAL CLOCK (SCL): The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.SERIAL DATA (SDA): The SDA pin is bidirectional for serial data transfer. This pin is open-drain driven and may be wire-ORed with any number of other open-drain or open collector devices.DEVICE/ADDRESSES (A2, A1, A0): The A2, A1 and A0 pins are device address inputs that are hardwired or left not connected for hardware compatibility with other AT24Cxx devices. When the pins are hardwired, as many as eight 32K/64K devices may be addressed on a single bus system (device addressing is discussed in detail under the Device Addressing section). If the pins are left floating, the A2, A1 and A0 pins will be internally pulled down to GND if the capaci-tive coupling to the circuit board V CC plane is <3 pF. If coupling is >3 pF, Atmel recommends connecting the address pins to GND.WRITE PROTECT (WP): The write protect input, when connected to GND, allows normal write operations. When WP is connected high to V CC , all write operations to the memory are inhibited.If the pin is left floating, the WP pin will be internally pulled down to GND if the capacitive cou-pling to the circuit board V CC plane is <3 pF. If coupling is >3pF, Atmel recommends connecting the pin to GND. Switching WP to V CC prior to a write operation creates a software write protect function.Memory OrganizationAT24C32A/64A, 32K/64K SERIAL EEPROM: The 32K/64K is internally organized as 128/256pages of 32 bytes each. Random word addressing requires a 12/13-bit data word address.45120D–SEEPR–6/08AT24C32A/64ANote:1.This parameter is characterized and is not 100% tested.IL IH Table 2. Pin Capacitance (1)Applicable over recommended operating range from T A = 25°C, f = 1.0 MHz, V CC = +2.7V to +5.5VSymbol Test ConditionMax Units Conditions C I/O Input/Output Capacitance (SDA)8pF V I/O = 0V C IN Input Capacitance (A 0, A 1, A 2, SCL)6pFV IN = 0VTable 3. DC CharacteristicsApplicable over recommended operating range from: T A = –40°C to +125°C,V CC = +2.7V to +5.5V (unless otherwise noted)Symbol Parameter Test ConditionMin TypMax Units V CC3Supply Voltage 2.75.5V I CC1Supply Current V CC = 5.0V READ at 400 kHz 0.4 1.0mA I CC2Supply Current V CC = 5.0V WRITE at 400 kHz 2.0 3.0mA I SB Standby Current V CC = 2.7V V IN = V CC or V SS1.0 3.0µA V CC = 5.0V 3.0 5.0I LI Input Leakage CurrentV IN = V CC or V SS 0.10 3.0µA I LO Output Leakage Current V OUT = V CC or V SS0.05 3.0µA V IL (1)Input Low Level –0.6V CC x 0.3V V IH (1)Input High Level V CC x 0.7V CC + 0.5V V OL2Output Low LevelV CC = 3.0VI OL = 2.1 mA0.4V V OL1Output Low Level V CC = 1.8V I OL = 0.15 mA 0.2V55120D–SEEPR–6/08AT24C32A/64ANotes: 1.This parameter is ensured by characterization only.Table 4. AC CharacteristicsApplicable over recommended operating range from T A = –40°C to +125°C, V CC = +2.7V to +5.5V, CL = 1 TTL Gate and 100 pF (unless otherwise noted)Symbol ParameterAT24C32A/AT24C64AUnits 2.7V – 5.5VMinMax f SCL Clock Frequency, SCL 400kHz t LOW Clock Pulse Width Low 1.2µs t HIGH Clock Pulse Width High 0.6µs t I Noise Suppression Time (1)50ns t AA Clock Low to Data Out Valid 0.10.9µs t BUF Time the bus must be free before a new transmission can start (1) 1.2µs t HD.ST A Start Hold Time 0.6µs t SU.ST A Start Set-up Time 0.6µs t HD.DA T Data In Hold Time 0µs t SU.DAT Data In Set-up Time 100ns t R (1)Inputs Rise Time 0.3µs t F (1)Inputs Fall Time 300ns t SU.STO Stop Set-up Time 0.6µs t DH Data Out Hold Time 50ns t WRWrite Cycle Time5ms Endurance (1) 5.0V , 25⋅C, Page Mode1M Write Cycles65120D–SEEPR–6/08AT24C32A/64ADevice OperationCLOCK and DATA TRANSITIONS: The SDA pin is normally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods (refer to Data Valid-ity timing diagram). Data changes during SCL high periods will indicate a start or stop condition as defined below.START CONDITION: A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (see Figure 5 on page 8).STOP CONDITION: A low-to-high transition of SDA with SCL high is a stop condition. After a read sequence, the stop command will place the EEPROM in a standby power mode (see Fig-ure 5 on page 8).ACKNOWLEDGE: All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a zero during the ninth clock cycle to acknowl-edge that it has received each word.STANDBY MODE: The AT24C32A/64A features a low power standby mode which is enabled:a) upon power-up and b) after the receipt of the stop bit and the completion of any internal operations.MEMORY RESET: After an interruption in protocol, power loss or system reset, any two-wire part can be reset by following these steps:(a) Clock up to 9 cycles, (b) look for SDA high in each cycle while SCL is high and then (c) create a start condition as SDA is high.75120D–SEEPR–6/08AT24C32A/64AFigure 2. Bus TimingSCL: Serial Clock, SDA: Serial Data I/OFigure 3. Write Cycle TimingSCL: Serial Clock, SDA: Serial Data I/ONote:1.The write cycle time t WR is the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.Figure 4.Data Validity85120D–SEEPR–6/08AT24C32A/64AFigure 5. Start and Stop DefinitionFigure 6.Output Acknowledge95120D–SEEPR–6/08AT24C32A/64ADeviceAddressingThe 32K/64K EEPROM requires an 8-bit device address word following a start condition to enable the chip for a read or write operation (see Figure 7 on page 11). The device address word consists of a mandatory one, zero sequence for the first four most significant bits as shown. This is common to all 2-wire EEPROM devices.The 32K/64K uses the three device address bits A2, A1, A0 to allow as many as eight devices on the same bus. These bits must compare to their corresponding hardwired input pins. The A2,A1, and A0 pins use an internal proprietary circuit that biases them to a logic low condition if the pins are allowed to float.The eighth bit of the device address is the read/write operation select bit. A read operation is ini-tiated if this bit is high and a write operation is initiated if this bit is low.Upon a compare of the device address, the EEPROM will output a zero. If a compare is not made, the device will return to standby state.NOISE PROTECTION: Special internal circuitry placed on the SDA and SCL pins prevent small noise spikes from activating the device.DATA SECURITY: The AT24C32A/64A has a hardware data protection scheme that allows the user to write protect the entire memory when the WP pin is at V CC .WriteOperationsBYTE WRITE: A write operation requires two 8-bit data word addresses following the device address word and acknowledgment. Upon receipt of this address, the EEPROM will again respond with a zero and then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will output a zero and the addressing device, such as a microcontroller,must terminate the write sequence with a stop condition. At this time the EEPROM enters an internally-timed write cycle, t WR , to the nonvolatile memory. All inputs are disabled during this write cycle and the EEPROM will not respond until the write is complete (see Figure 8 on page 11).PAGE WRITE: The 32K/64K EEPROM is capable of 32-byte page writes.A page write is initiated the same way as a byte write, but the microcontroller does not send a stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the microcontroller can transmit up to 31 more data words. The EEPROM will respond with a zero after each data word received. The microcontroller must ter-minate the page write sequence with a stop condition (see Figure 9 on page 11).The data word address lower five bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented, retaining the memory page row location. When the word address, internally generated, reaches the page boundary, the fol-lowing byte is placed at the beginning of the same page. If more than 32 data words are transmitted to the EEPROM, the data word address will “roll over” and previous data will be overwritten.ACKNOWLEDGE POLLING: Once the internally-timed write cycle has started and the EEPROM inputs are disabled, acknowledge polling can be initiated. This involves sending a start condition followed by the device address word. The read/write bit is representative of the operation desired. Only if the internal write cycle has completed will the EEPROM respond with a zero, allowing the read or write sequence to continue.105120D–SEEPR–6/08AT24C32A/64AReadOperationsRead operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to one. There are three read operations:current address read, random address read and sequential read.CURRENT ADDRESS READ: The internal data word address counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address “roll over”during read is from the last byte of the last memory page, to the first byte of the first page. The address “roll over” during write is from the last byte of the current page to the first byte of the same page.Once the device address with the read/write select bit set to one is clocked in and acknowledged by the EEPROM, the current address data word is serially clocked out. The microcontroller does not respond with an input zero but does generate a following stop condition (see Figure 10 on page 11).RANDOM READ: A random read requires a “dummy” byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another start condition. The microcontroller now initiates a current address read by sending a device address with the read/write select bit high. The EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a zero but does generate a follow-ing stop condition (see Figure 11 on page 12).SEQUENTIAL READ: Sequential reads are initiated by either a current address read or a ran-dom address read. After the microcontroller receives a data word, it responds with an acknowledge. As long as the EEPROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words. When the memory address limit is reached, the data word address will “roll over” and the sequential read will continue. The sequential read operation is terminated when the microcontroller does not respond with a zero but does generate a following stop condition (see Figure 12 on page 12).115120D–SEEPR–6/08AT24C32A/64AFigure 7. Device AddressFigure 8. Byte WriteFigure 9. Page WriteNotes:1.* = DON’T CARE bits2.† = DON’T CARE bits for the 32KFigure 10.Current Address Read125120D–SEEPR–6/08AT24C32A/64AFigure 11. Random ReadNote: 1.* = DON’T CARE bitsFigure 12.Sequential Read135120D–SEEPR–6/08AT24C32A/64ANotes:1.For2.7V devices used in the 4.5V to 5.5V range, please refer to performance values in the AC and DC Characteristicstables.2.“Q” designates Green package and RoHS Compliant.AT24C32A Ordering Information (1)Ordering Code Package Operation Range A T24C32AN-10SQ-2.7(2)A T24C32A-10TQ-2.7(2)8S18A2Lead-free/Halogen-free/Automotive (–40⋅C to 125⋅C)Package Type8S18-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 4.4 mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)Options–2.7Low Voltage (2.7V to 5.5V)145120D–SEEPR–6/08AT24C32A/64ANotes:1.For2.7V devices used in the 4.5V to 5.5V range, please refer to performance values in the AC and DC Characteristicstables.2.“Q” designates Green package and RoHS Compliant.AT24C64A Ordering Information (1)Ordering Code Package Operation Range A T24C64AN-10SQ-2.7(2)A T24C64A-10TQ-2.7(2)8S18A2Lead-free/Halogen-free/Automotive (–40⋅C to 125⋅C)Package Type8S18-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 4.4mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)Options–2.7Low Voltage (2.7V to 5.5V)155120D–SEEPR–6/08AT24C32A/64APackage Drawings8S1 – JEDEC SOIC165120D–SEEPR–6/08AT24C32A/64A8A2 – TSSOP175120D–SEEPR–6/08AT24C32A/64ARevision HistoryRevision HistoryRevision Date Comments5120D6/2008Implemented revision history.。

金鹏科技有限公司Golden Palm Science Technology Co.,Ltd目录一、OCM4X8C液晶显示模块概述 (1)二、模块引脚说明 (1)1)表—1:OCM2X8C(128X32)、OCM2X10C(160X32)模块引脚说明 (1)2)表—2:OCM2X8C-2(128X32)模块引脚说明 (1)3)表—3:OCM4X8C(128X64)引脚说明 (1)4)表—4:OCM4X16A(256X64)引脚说明 (2)三、OCM4X8C液晶硬件接口 (2)1、8位并行连接时序图 (2)2、串行连接时序图 (3)3、AC电气特性(TA=25℃V CC=5V) (3)四、用户指令集 (4)五、显示坐标关系 (7)1、图形显示坐标 (7)2、汉字显示坐标 (8)3、字符表 (8)六、显示步骤 (9)七、显示示例程序 (9)1、发送子程序 (9)2、读子程序 (10)八、模块尺寸图 (12)附:汉字字符集三、OCM4X8C液晶硬件接口1、逻辑工作电压(VDD):4.5~5.5V2、电源地(GND):0V3、LCD驱动电压(V0):0~-10V4、工作温度(Ta):0~55℃(常温) / -20~70℃(宽温)保存温度(Tstg):-10~65℃(常温)5、电气特性见附图1 外部连接图(参考附图2)模块有并行和串行两种连接方法(时序如下):1、8位并行连接时序图MPU写资料到模块备注:六、显示步骤1、显示资料RAM(DDRAM)显示资料RAM提供64×2个位元组的空间,最多可以控制4行16字(64个字)的中文字型显示,当写入显示资料RAM时,可以分别显示CGROM、HCGROM与CGRAM 的字型;ST7920A可以显示三种字型,分别是半宽的HCGROM字型、CGRAM字型及中文CGROM字型,三种字型的选择,由在DDRAM中写入的编码选择,在0000H—0006 H的编码中将自动的结合下一个位元组,组成两个位元组的编码达成中文字型的编码(A140—D75F),各种字型详细编码如下:1、显示半宽字型:将8位元资料写入DDRAM中,范围为02H—7FH的编码。

高性能32位多核处理器SOC芯片S698PM用户手册(Ver:4.8)珠海欧比特宇航科技股份有限公司地址: 广东省珠海市唐家东岸白沙路1号欧比特科技园邮编: 519080 电话*************传真*************网址: 修改记录版权声明珠海欧比特宇航科技股份有限公司拥有此文件的版权,并有权将其作为保密资料处理。

本文件包含由版权法保护的专有资料,版权所有,未经珠海欧比特宇航科技股份有限公司的书面同意不得将本文件的任何部分进行照相、复制、公开、转载或以其他方式散发给第三方,否则,必将追究其法律责任。

免责声明本文档仅提供阶段性信息,所含内容可根据产品的实际情况随时更新,恕不另行通知。

如因文档使用不当造成的直接或间接损失,珠海欧比特宇航科技股份有限公司不承担任何责任。