基于FPGA控制的低频数字式相位测量仪研究

- 格式:doc

- 大小:18.50 KB

- 文档页数:5

基于FPGA控制的低频数字式相位测量仪研究胡云朋(电子信息工程学院微电子及固体电子专业 113114310)摘要:提出了一种基于Verilog开发的低频数字相位测量仪设计。

系统以FPGA为核心,构成完备的测量系统,可以对20Hz-20KHz的频率范围的信号进行频率、相位等参数的精确测量。

硬件结构简单,程序简单可读性强,与传统电路相比,具有处理速度快、稳定性高、性价比高的特点。

关键字:相位测量仪、FPGA、Verilog语言目录第一章研究背景 (3)第二章方案设计与论证 (3)一、设计指标要求 (3)二、设计方案论证 (4)第三章系统硬件设计 (6)硬件电路的设计: (6)第四章软件系统设计 (7)一、FPGA完成的任务 (7)二、FPGA芯片内部电路框图 (7)三、FPGA的Verilog程序及仿真结果 (7)第五章结束语 (11)参考文献: (11)第一章 研究背景随着科学技术的突飞猛进的发展,电子技术广泛的应用于工业、农业、交通运输、航空航天、国防建设等国民经济的诸多领域中,而电子测量技术又是电子技术中进行信息检测的重要手段,在现代科学技术中占有举足轻重的作用和地位。

相位是交流信号的重要参数。

相位差的测量是电子和电力测量中经常遇到的问题,测量两路同频信号的相位差在工程上有着重要的意义。

其测量方法可分为模拟和数字方法两种:传统依靠模拟器件的方法,如二极管鉴相法、脉冲计数法等,测量系统复杂、需专用器件、硬件成本高、而且精度不高。

随着集成电路的发展,利用大规模集成电路来完成各种高速、高精度电子仪器的设计,已经成为一种行之有效的方法。

采用这种技术制成的电子仪器电路结构简单、性能可靠、测量精确且易于调试,而且精度明显高于一般的模拟式测量。

在工业和民用场合, 为了对各种低频信号进行测量分析,常常引入相位测量仪。

低频数字式相位测试仪在工业领域中是经常用到的一般测量工具,例如在电力系统中,当电网合闸时,要求两电网电信号的相位相同,如果两路信号的相位不同,会出现很大的电网冲激电流,对供电系统产生巨大的破坏力,因此,精确测量出两个信号的相位差是非常重要的。

基于FPGA的低频相位测量系统设计李宝营;赵永生;祁建广【期刊名称】《微计算机信息》【年(卷),期】2012(000)006【摘要】基于现场可编程门阵列FPGA的特点,在EP1K100QC208内部设计两个计数器模块并定制一个ROM正弦表;通过单片机AT89S52控制闸门信号的开启和关闭来完成对标准信号和被测信号的同步测量,并对数据进行处理,将计算得到的结果在液晶屏12864上显示出来。

二者的结合实现了一个高精度的相位测量系统设计。

该系统采用多周期同步测量技术,在测量过程当中,可能存在最多±1个字的计数误差,其精度不会因被测频率的变化而受影响,其电路简单,降低了功耗和成本。

%Based on the characteristics of FPGA (field programmable gate array), the paper design two counter module and customize a ROM sine table in EPIK100QC208's internal; the single chip computer AT89S52 controls the gate signal to start and stop, then complete the measurement of the standard signal and the measured signal synchronous, finishes the data processing and displays the results of the calculation on the LCD screen 12864.The paper combined Single-chip with FPGA as the core control to complete the high-precision phase measurement system. The system adopts the multi-cycle synchronous measurement technique; in the measurement process, there maybe a word count error at most, but its accuracy of frequency will not be affected when the measured frequency changes, the Circuit is very simple, reducing power consumption and cost.【总页数】3页(P98-99,112)【作者】李宝营;赵永生;祁建广【作者单位】大连大连工业大学信息科学与工程学院,辽宁116034;大连大连海事大学信息科学与技术学院,辽宁116026;大连大连工业大学信息科学与工程学院,辽宁116034【正文语种】中文【中图分类】TP216【相关文献】1.基于AVR单片机与FPGA的低频数字式相位测量仪 [J], 井新宇2.基于单片机和FPGA的低频数字相位测量仪研究 [J], 郭贝贝;仝战营3.基于单片机和FPGA的低频数字相位测量仪研究 [J], 郭贝贝;仝战营4.基于FPGA控制的低频数字式相位测量仪研究 [J], 王振红;于磊5.基于FPGA控制的低频数字式相位测量仪研究 [J], 王振红;于磊因版权原因,仅展示原文概要,查看原文内容请购买。

摘要本系统以单片机和FPGA为核心,辅以必要的模拟电路,构成了一个基于具有高速处理能力的FPGA的低频数字式相位测量仪。

该系统由相位测量仪、数字式移相信号发生器以及移相网络组成;移相网络能够产生-45°~45°相位差的两路信号;相位测量仪能够测量出具有0°~359°的两路信号的相位差;而数字式移相信号发生器能够产生出相位差为0°~359°的且具有数字设置步进为1°的两路输出信号。

经过实验测试,以上功能均可以准确实现。

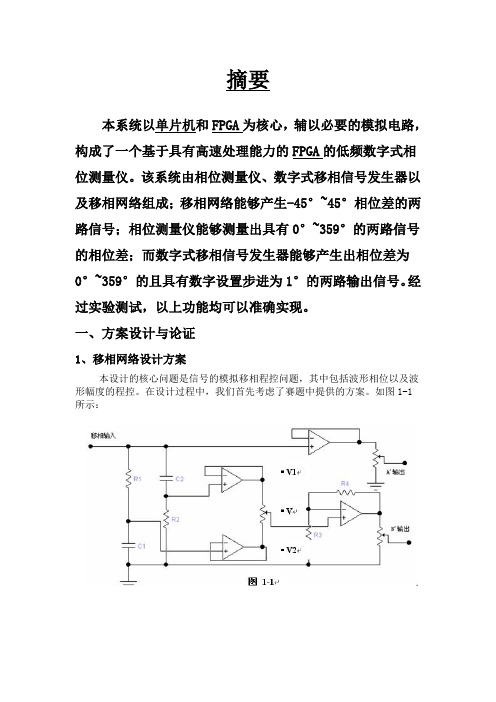

一、方案设计与论证1、移相网络设计方案本设计的核心问题是信号的模拟移相程控问题,其中包括波形相位以及波形幅度的程控。

在设计过程中,我们首先考虑了赛题中提供的方案。

如图1-1所示:该模拟电路主要采用高、低通电路的临界截止点来产生极值相位的偏移。

当高、低通电路的截止频率等于输入信号频率时,根据其幅频特性,信号波形所产生的相位分别为45°和-45°,恰好满足赛题要求的连续相移范围-45°~45°的调节。

由于高、低通电路在截止点时会产生幅度的衰减,故电路在后级加了放大电路,且采用了电压串联负反馈的方式提高了输入阻抗并降低了输出阻抗,电路最后还设计有调幅装置,能够很好地满足A、B输出的正弦信号峰—峰值可分别在0.3V—5V范围内变化。

综上所述,该移相网络能够满足赛题的所有要求,且电路设计简单、易行,故我们直接采用了这种方式来产生模拟的相移输出。

2、数字式移相信号发生器设计方案本单元设计的关键在于两个波形相位差的准确定位,在设计中我们综合考虑了两种实现方案:方案一:采点式相位确定。

利用相位范围0°~ 360°设定每个波形含有360个点,即每一点都对应一度,以保证相位的精确定位。

但当输入波形频率较高时,FPGA中的 DDFS对该波形的采点数将降低,该方法也不再适合;此外360个点的波形很难利用DDFS的地址线准确产生,由于DDFS在运行时地址是不断向下扫描的,其多余地址中的零数据也将同样会被显示输出,使得波形不再准确。

摘要低频数字相位测量仪向文芳摘要设计了一个基于现场可编程门阵列(FPGA)和AT89S51单片机相结合的低频数字相位测量仪。

本系统可分为三大基本组成部分:数据测量电路、数据运算控制电路和数据显示电路。

FPGA数据测量电路的功能就是实现将待测正弦信号的周期、相位差转变为19位的数字量。

单片机数据运算控制电路的功能就是负责读取FPGA测量到的数据,并根据这些数据计算待测正弦信号的频率及两路同频正弦信号之间的相位差,同时通过功能键切换,显示出待测信号的频率和相位差。

数据显示电路的设计采用静态显示方式,显示电路由8片1位串入8位并出的74LS164芯片组成。

本系统拟用FPGA和单片机相结合,构成整个系统的测控主体。

整个系统发挥了FPGA和单片机各自的优势,具有高速而可靠的测控能力,具有比较强的数据处理能力,键盘输入及显示控制比较灵活,系统可扩展性比较好,整个系统性能价格比比较好。

关键词FPGA,单片机,频率,相位差,相位测量仪攀枝花学院本科毕业设计(论文)ABSTRACTABSTRACTThe paper has designed a low frequency digital phase measuring instrument based on the system which communicates FPGA and the microcontroller (AT89S51). This system includes three modules: data measuring electric circuit, data operation control circuit and data display electric circuit. The function of the FPGA data measuring electric circuit is transforms the cycle, phase difference of the two input sine signals to be 19 bit of digital data. The function about microcontroller data operation control circuit is to read the data which FPGA has measured, and according to these data computations the frequency and the phase difference between two group sine signals which have same frequencies, simultaneously through the function key switch, displaying the frequency and phase difference of the two group sine signals. The data display electric circuit’s design adopting the static state display mode, the display circuit is composed by 8 pieces of 74LS164 chip (8-bit Serial-Input/Parallel-Output shift Register).This system plans with FPGA and the microcontroller, framing the phase measuri ng instrument’s dominant measurement and control system. The overall system has displayed FPGA and the microcontroller respective superiority, has high speed and the reliable measurement and control ability, and has the quite strong capacity of deal with data, the keyboard entry and the display control also quite flexible. The system’s extension is quite good. All the superiorities make the good performance price ratio of this low frequency digital phase measuring instrument.Keywords FPGA, Microcontroller, Frequency, Phase difference, Phase measurement system目录摘要 (I)ABSTRACT (II)1绪论 (1)1.1课题背景 (1)1.1.1 研究意义 (1)1.1.2 研究现状、水平及发展趋势 (1)1.2课题核心 (3)2系统设计 (4)2.1设计要求 (4)2.2总体设计思想 (4)2.3总体测量思路 (5)3设计方案 (6)3.1测量方案 (6)3.1.1频率测量 (6)3.1.2 相位差测量 (8)3.2正弦波信号发生器设计 (9)3.3信号整形电路的设计 (9)3.3.1 方案论证 (9)3.3.2 关于四电压比较器LM339 (11)3.4移相网络设计 (11)3.4.1 性能要求 (11)3.4.2 方案论证 (11)4 FPGA数据测量电路的设计 (14)4.1设计原理 (14)4.1.1 设计思路 (14)4.1.2 FPGA数据测量电路的测量原理 (14)4.1.3 精度分析 (14)4.2 FPGA概述 (15)4.3设计平台 (16)4.3.1 软件设计平台 (16)4.3.2 硬件设计平台 (17)4.4具体软件设计 (18)4.4.1 QuartusⅡ应用 (18)4.4.2 软件设计方法 (19)4.4.3 模块功能描述和系统原理图 (19)4.4.4 运行监测程序 (20)4.4.5 程序中端口及引脚定义 (20)4.5具体硬件连接 (21)4.5.1 与单片机的连接 (21)4.5.2其它连接 (22)5单片机数据运算控制电路的设计 (23)5.1设计思路 (23)5.1.1 硬件电路和原理图 (23)5.1.2 精度分析 (24)5.2 AT89S51概述 (24)5.2.1 AT89S51单片机 (24)5.2.2 AT89S51特性 (24)5.2.3 引脚排列 (25)5.2.4 引脚功能 (26)5.2.5 低功耗运行模式 (28)5.3设计平台 (29)5.3.1 软件设计平台 (29)5.3.2 硬件设计平台 (29)5.4软件设计思路 (29)5.4.1 主程序设计 (29)5.4.2 数据读取模块 (30)5.4.3 频率计算模块 (30)5.4.4 相位差计算模块 (31)5.4.5 显示模块 (31)6数据显示部分 (33)6.1显示电路的设计 (33)6.1.1 设计思路 (33)6.1.2 LED显示器接口原理 (33)6.1.3 显示电路图 (34)6.2关于74LS164 (34)6.2.1 74LS164概述 (34)6.2.2 连接说明 (34)6.2.3 数码管的编码 (35)7系统仿真和硬件验证 (36)7.1系统的仿真 (36)7.1.1 系统调试的方法 (36)7.1.2 系统调试的软/硬件 (36)7.1.3 系统的有关仿真 (36)7.1.4 仿真分析 (37)7.2系统的硬件验证 (39)7.2.1 单元电路的调试 (39)7.2.2 系统的联合调试 (40)7.2.3 系统的硬件验证 (40)7.3数据测试 (40)7.3.1 数据记录 (40)7.3.2 数据分析 (41)结论 (42)附录A:本设计FPGA的VHDL源代码 (45)附录B:单片机的汇编语言源程序清单 (51)附录C:适合于QuartusⅡ的部分器件引脚对照表 (67)附录D:系统总图 (67)参考文献 (70)致谢 (71)1 绪论1.1 课题背景1.1.1 研究意义在电子测量技术中,频率测量是最基本的测量之一。

基于FPGA的数字显示相位差测量仪[摘要] 本文主要介绍了数字显示相位差测试仪的设计方案和硬件部分。

针对FPGA的特点,在数字相位差测量系统的设计思想上,给出了一种用FPGA 芯片EP1K10TC144-3实现相位差智能化测量仪的方案。

该测量仪只需少量的外围电路,有效将测量信号正弦波,方波、三角波信号移相放大,整形为所需要的方波信号,且不失真,测量这些信号的相位差,硬件电路简单,实现了输入阻抗大,误差小,精度高,抗干扰强。

[关键词] FPGA 相位差测量晶振1.基于该题目数字显示相位差测量仪,我们在方案设计上采用了三种不同的方案,各方案各有优缺点,在综合考虑了几种方案后,我们选定了基于FPGA的数字显示相位差测量仪,因为FPGA是在可编程专用集成电路(ASIC)的设计基础上发展起来的。

由于它们集成度高、可重复编程,并能实现系统级编程(ISP),在近10年内得到迅速发展。

FPGA的集成度、工作速度不断提高,包含的资源越来越丰富,可实现功能越来越强大,具有静态可重复编程或在线动态重构的特性,使得硬件功能可以像软件一样通过编程来修改,不仅使设计修改变得十分容易,而且大大提高了电子系统的灵活性和通用能力,已成为当今实现电子系统集成化的重要手段。

该测量仪只需少量的外围电路,有效将测量信号正弦波,方波、三角波信号移相放大,整形为所需要的方波信号,且不失真,测量这些信号的相位差,硬件电路简单,实现了输入阻抗大,误差小,精度高。

2.系统设计思想2.1系统设计整个测量我们分为两个部分,一部分是测量输入的信号A的频率,在这一部分中,将一个78125的晶振经一个计数分频得到频率为0.5HZ的信号(0.5HZ 信号的周期为T=2),当原信号A与0.5HZ的信号与非的时候,其低电平半周期时(也就是T=1S时),会有一段脉冲个数,将此脉冲个数送入计数器计数输出,输出的值即为原信号的频率值;另一部分则是测量输入的两个同频异相信号A 和B的相位差,而我们输入的都是单个的模拟信号,所以在测试相位差的时候首先应产生两个同频异相的信号。

1引言关于低频数字相位测量系统的设计与实现方法,提出了以单片机最小系统和复杂可编程逻辑芯片为核心的电路设计模型。

相位的数字测量方法基本分为硬件电路测量与A/D采样后利用软件计算两种。

硬件法测量由于电路结构比较复杂,易受外界干扰影响以及准确度较差的缺点,限制了其作用进一步发挥。

近年来,随着计算机硬件及其外围设备的日益发展,以数字信号处理为核心的软件法测量技术在相位差的测量中得到了越来越多关注,并且得到了较快发展。

同频率正弦信号间的相位差测量在电工技术、工业自动化、智能控制及通讯、电子等许多领域都有广泛的应用,如电工领域中的电机功角测试,介质材料的损耗角的确定等。

因此相位差测量有着广泛的实用价值。

本系统由数据采集电路、数据运算控制电路和数据显示电路三大部份构成,其系统功能主要是进行相位差测量及频率测量。

该系统采用单片机和FPGA作为低频数字相位测量仪的核心部分。

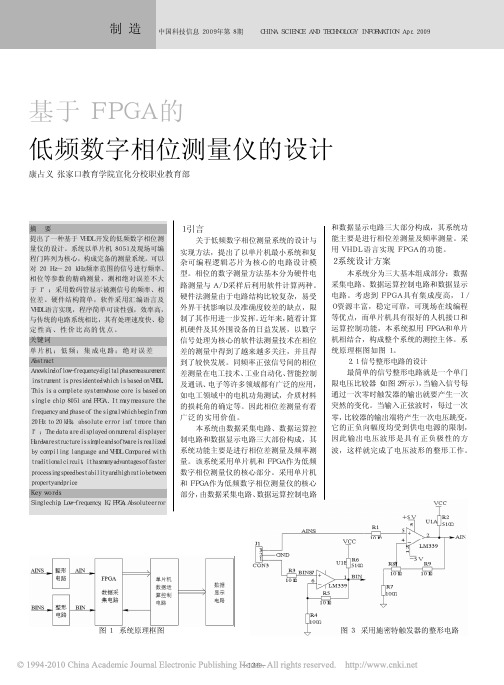

采用单片机和FPGA作为低频数字相位测量仪的核心部分,由数据采集电路、数据运算控制电路基于FPGA的低频数字相位测量仪的设计康占义 张家口教育学院宣化分校职业教育部图1 系统原理框图图3 采用施密特触发器的整形电路和数据显示电路三大部分构成,其系统功能主要是进行相位差测量及频率测量。

采用VHDL语言实现FPGA的功能。

2系统设计方案本系统分为三大基本组成部分:数据采集电路、数据运算控制电路和数据显示电路。

考虑到FPGA具有集成度高,I/O资源丰富,稳定可靠,可现场在线编程等优点,而单片机具有很好的人机接口和运算控制功能,本系统拟用FPGA和单片机相结合,构成整个系统的测控主体。

系统原理框图如图1。

2.1 信号整形电路的设计最简单的信号整形电路就是一个单门限电压比较器(如图2所示),当输入信号每通过一次零时触发器的输出就要产生一次突然的变化。

当输入正弦波时,每过一次零,比较器的输出端将产生一次电压跳变,它的正负向幅度均受到供电电源的限制,因此输出电压波形是具有正负极性的方波,这样就完成了电压波形的整形工作。

设计(论文)题目:基于FPGA与单片机控制技术结合的低频数字相位测量仪设计一、基本任务及要求一)基本任务1)硬件设计:输入信号整形电路、单片机外围电路、显示电路;2)软件设计:数据采集模块的VHDL硬件描述语言实现、单片机控制程序。

二)要求1)本设计本分为三大基本组成部分:数据采集电路、数据运算控制电路和数据显示电路。

其功能为对两路输入正弦信号(1~5 V范围内变化)进行频率和相位测量(相位测量绝对误差≤2)及数字显示(相位读数为0~359.9,分辨力为0.1),其频率测量范围:20 Hz~20 kHz。

2)通过该项目设计,完成各单元模块的硬件设计,给出其设计过程和电路图;对数据采集、单片机控制模块分别给出VHDL硬件描述语言实现的源程序和控制程序,并进行程序调试及电路的仿真、给出仿真结果。

二、进度安排及完成时间:目录摘要 (IV)Abstract (V)第1章绪论.......................................................... - 1 -1.1 课题研究的背景................................................ - 1 -1.2 本课题的主要研究工作.......................................... - 3 - 第2章主要理论及技术................................................ - 4 -2.1 频率测量...................................................... - 4 -2.2 相位测量...................................................... - 5 -2.3 单门限电压比较器原理.......................................... - 6 -2.3.1 LM339介绍............................................... - 6 -2.4 FPGA可编程控制技术............................................ - 7 -2.4.1 FPGA 器件的设计开发流程.................................. - 7 -2.4.2 FPGA工作原理............................................ - 8 -2.4.3 VHDL语言介绍........................................... - 8 -2.4.4 Quartus II软件介绍...................................... - 9 -2.5 AT80C51单片机介绍............................................ - 10 - 第3章系统设计思路................................................. - 11 -3.1 系统总体设计思路............................................. - 11 -3.2 设计方案..................................................... - 11 - 第4章硬件设计...................................................... - 13 -4.1 信号整形电路的设计........................................... - 13 -4.2 FPGA数据采集电路的设计....................................... - 14 -4.3 单片机数据运算控制电路的设计................................. - 15 -4.4 数据显示电路的设计........................................... - 16 -4.4.1 LCD12864介绍........................................... - 16 -4.4.2 基本特性................................................ - 16 -4.4.3管脚说明................................................ - 16 -4.4.4 基本用途................................................ - 17 -4.4.5数据显示电路............................................ - 17 - 第5章软件设计...................................................... - 18 -5.1 FPGA数据测量电路............................................. - 18 -5.2 分频器模块................................................... - 19 -5.3 控制信号模块................................................. - 20 -5.4 数据检测模块................................................. - 22 -5.5 数据锁存模块................................................. - 23 -5.6 数据选择模块................................................. - 24 -5.7 FPGA数据测量模块总体设计..................................... - 26 -5.7 单片机数据运算控制电路....................................... - 27 - 结束语............................................................... - 30 - 参考文献............................................................. - 31 - 致谢............................................................... - 32 - 附录............................................................... - 33 - FPGA数据采集程序................................................. - 33 - 数据显示程序..................................................... - 36 - 硬件总电路图..................................................... - 40 -低频数字式相位测量仪的设计摘要:基于过零检测法原理,以单片机89C51和可编程逻辑器件CPLD为核心,从数据采集﹑数据运算控制、显示等电路功能电路设计,实现了一个低频数字式相位测量仪系统。

《基于FPGA的低频数字相位测量仪设计》开题报告一、课题的目的和意义1.研究目的随着数字电子技术的发展,由数字逻辑电路组成的控制系统逐渐成为现代检测技术中的主流,数字测量系统也在工业中越来越受到人们的重视。

在实际工作中,常常需要测量两列频率相同的信号之间的相位差,来解决实践中出现的种种问题。

例如,电力系统中电网合闸时,要求两电网的电信号之间的相位相同,这时需要精确测量两列工频信号之间的相位差。

如果两列信号之间的相位差达不到相同,会出现很大的电网冲激电流,对供电系统产生巨大的破坏力,所以必须精确地测量出两列信号之间的相位差。

数字式仪器采用数码管显示相位差,精确度高,稳定性能好,读数方便且不需要经常调试,所以数字式测量仪逐渐代替了原来的模拟式仪器。

本系统可分为三大基本组成部分:数据采集电路、数据运算控制电路和数据显示电路。

其中数据采集电路用FPGA 实现,其功能就是实现将待测正弦信号的周期、相位差转变为19位的数字量。

2.研究意义随着相位测量技术广泛应用于国防、科研、生产等各个领域,对相位测量的要求也逐步向高精度、高智能化方向发展,在低频范围内,相位测量在电力、机械等部门有着尤其重要的意义,对于低频相位的测量,用传统的模拟指针式仪表显然不能够满足所需的精度要求,随着电子技术以及微机技术的发展,数字式仪表因其高精度的测量分辨率以及高度的智能化、直观化的特点得到越来越广泛的应用。

基于这些要求,我们设计并制作了基于FPGA为核心的低频数字式相位测量系统。

二、文献综述本设计给出了以FPGA为核心的数字式相位测量的基本原理与实现方案。

该系统由数据采集电路、数据运算控制电路和数据显示电路组成。

其中数据采集电路用FPGA 实现,其功能就是实现将待测正弦信号的周期、相位差转变为19位的数字量。

同频率正弦信号间的相位差测量在电工技术、工业自动化、智能控制及通讯、电子等许多领域都有着广泛的应用,如电工领域中的电机功角测试,介质材料损耗角的确定等。

基于FPGA控制的低频数字式相位测量仪研究

作者:王振红于磊

来源:《数字技术与应用》2010年第01期

摘要:低频数字相位测量仪在工业领域中是经常用到的一般测量工具,主要应用于同频率正弦信号间的相位差的测量显示。

本系统采用复杂可编程逻辑器件EP1K100QC208-3作为数据处理及控制核心,由移相网络,信号处理电路,数据采集电路,数据运算电路以及显示电路组成。

该系统硬件电路简单,整个设计采用VHDL(超高速硬件描述语言)语言作为系统内部硬件结构的描述手段,在Altera的maxplusⅡ的软件支持下完成。

该系统可以对200Hz~20kHz频率范围内的信号进行高频采样处理,并把收集到的数据送入FPGA进行相位差测量运算并送显示电路显示,测相绝对误差不大于±0.5°。

本系统充分利用FPGA对数据的高速处理能力,使得系统设计高效,可靠。

与传统相位测量仪相比, 该系统具有处理速度快、稳定性高、性价比高,易于实现的优点。

该系统具有较强的实用价值和良好的工程应用前景。

关键词:复杂可编程逻辑器件低频相位测量仪 FPGA VHDL语言

中图分类号: 文献标识码:A文章编号:1007-9416(2010)01-0000-00

1 绪论

随着科学技术的突飞猛进的发展,电子技术广泛的应用于工业、农业、交通运输、航空航天、国防建设等国民经济的诸多领域中,而电子测量技术又是电子技术中进行信息检测的重要手段,在现代科学技术中占有举足轻重的作用和地位。

相位是交流信号的重要参数。

相位差的测量是电子和电力测量中经常遇到的问题,测量两路同频信号的相位差在工程上有着重要的意义。

其测量方法可分为模拟和数字方法两种:传统依靠模拟器件的方法,如二极管鉴相法、脉冲计数法等,测量系统复杂、需专用器件、硬件成本高、而且精度不高。

随着集成电路的发展,利用大规模集成电路来完成各种高速、高精度电子仪器的设计,已经成为一种行之有效的方法。

采用这种技术制成的电子仪器电路结构简单、性能可靠、测量精确且易于调试,而且精度明显高于一般的模拟式测量。

在工业和民用场合,为了对各种低频信号进行测量分析,常常引入相位测量仪。

低频数字式相位测试仪在工业领域中是经常用到的一般测量工具,例如在电力系统中,当电网合闸时,要求两电网电信号的相位相同,如果两路信号的相位不同,会出现很大的电网冲激电流,对供电系统产生巨大的破坏力,因此,精确测量出两个信号的相位差是非常重要的。

同频信号间相位差的测量在电力系统、工业自动化、智能控制及通信、电子、地球物理勘探等许多领域都有着广泛的应用。

尤其在工业领域中,相位不仅是衡量安全的重要依据,还可以为节约能源提供参考。

因此,研究和设计低频数字式相位测量仪,将会为国民经济的发展起到推动和促进作用。

本课题主要研究基于FPGA控制的低频数字式相位测量仪,对200Hz~20kHz频率范围内的信号进行相位差的显示,误差控制在±0.5°之内。

2 系统测量原理

2.1相位差测量方案论证

相位差测量的基本原理主要有三种:对信号波形的变换和比较,对傅氏级数的运算及对三角函数的运算。

可采用脉冲填充计数法,相位/时间(频率)法等方案,最终选择相位/时间(频率)法,如图2.1所示,如图2.1(a)所示波形是经过移相网络后输出的两路待测同频正弦信号u1和u2,其中T1为延时时间,T为待测信号的周期,由公式(2.1)可以计算出u1 和u2的相位差。

图2.1(b)所示的为经过信号处理电路放大整形的两路方波信号。

2.2移相网络原理

在本系统设计中,我们采用基于阻容移相原理的模拟移相网络。

其原理图如图2.2所示: 如图2.2所示的相位关系中,要实现输出相移在

-45.0°~+45.0°范围内变化,R,C的理论值可以根据

公式(2.2)计算出。

2.3信号处理电路原理

信号处理电路由阻抗变换和放大、限幅、电平转换、整形电路组成。

其中阻抗变换和放大以及限幅部分均用NE5532搭建,电平转换用LM311搭建过零比较器得到方波信号,再经过由NE555搭建的施密特触发器组成的脉冲整形电路得到严格的上升沿或下降沿的方波信号。

3 系统的组成及功能指标

3.1系统组成与框图

本系统以Altera公司的EP1K100QC208-3作为数据处理及控制核心,由移相网络,信号处理电路,数据采集电路,数据运算电路以及LED数码管显示电路组成。

我们输入一路正弦信号,经

过移相网络后得到两路同频不同相的正弦信号,在经过信号处理电路将移相网络的两路输出信号处理为两路同频不同相的方波,将定义的信号超前端和信号滞后端两路信号送入

EP1K100QC208-3内,经过VHDL语言编写生成的数据采集以及数据运算模块,将数据送入LED 数码管显示电路显示出经过移相网络后的两路同频信号的相位差。

系统框图如图3.1所示。

图3.1 系统方框图

3.2 系统功能指标

3.2.1 移相网络

该移相网络适用于200Hz~20kHz的正弦信号,经过网络后产生两路同频不同相的正弦信号,理论移相范围是-45°~+45°,两路输出的正弦信号峰-峰值可通过电路中的电位器调节分别在

0.3V~5V范围内变化。

3.2.2 信号处理电路

该电路适用于200Hz~20kHz的正弦信号,输入阻抗≥100kΩ,允许两路输入正弦信号峰-峰值可分别在1~5V范围内变化。

移相网络的两路输出正弦信号经过该电路后产生两路同频不同

相的方波信号,该方波信号有着较陡的上升沿或者下降沿,易于FPGA检测得到。

3.2.3 LED数码管显示模块

该模块负责接收FPGA处理后运算后的数据,适时显示出变化的两路同频不同相信号的相位差,相位读数的理论值为-45.0°~+45.0°,分辨率为0.1。

3.2.4 供电电源模块

该系统采用220伏市电经过变压器和电源稳压电路得出所需+5V和±12V电源电压。

4 系统的设计与实现

4.1 移相网络的硬件设计

图4.1所示为移相网络硬件电路图,电位器W1接的是电压跟随器,调节电位器W1可以使B 输出在-45.0°~+45.0°范围内输出。

调节电位器W2、W3可以调节A输出和B输出的正弦信号峰-峰值在0.3V~5V范围内变化。

将W调为27.5k,W′调为1k,这样可以使频率为1KHz的输出相移在-45.0°~+45.0°范围内变化。

采用NE5532运算放大器是为了减少输出对RC网络的影响。

NE5532运算放大器有10MHz的带宽,能使输出信号真实地反映RC网络相移情况。

4.2 信号处理电路的硬件设计

如图4.2所示的信号处理电路,经相位超前输出端、相位滞后输出端将处理过的信号传输给可编程器件。

4.3 数码管显示电路设计

在本电路设计中,使用了一个八段数码显示管和一个CL5461AS四位共阴数码管,前者负责显示待测两路信号的相位差的正负,后者显示相位差的大小。

它们的管脚图分别如图4.3,图4.4所示:

4.4 相位测量的设计思想

测量两个信号之间的相位差通过计算实现。

由公式(4.1)和公式(4.2)我们可以计算出待测两路信号的相位其中: —两个信号之间的时间差

—两个信号之间的计数器的计算值

—计数器的时钟周期

—两个信号之间的相位差

—被测信号的周期

—计数器的时钟频率

—被测信号的频率

其设计思想具体的说就是当FPGA检测到规定的超前信号的下降沿时,开始计数,当FPGA 检测到规定的滞后信号的下降沿时,停止计数得到正相位差的计数N1并且得到相位差的正负状态;当FPGA检测到规定的滞后信号的下降沿时,开始计数,当FPGA检测到规定的超前信号的下

降沿时,停止计数得到负相位差的计数N2并且得到相位差的正负状态,然后将计数N1和N2通过或运算得到相位差的计数,FPGA根据相位差计数值,通过公式进行计算,最后通过LED数码管显示电路显示出计算结果。

5 结语

本设计完成了预期设计的目标任务,成功地设计出了基于FPGA控制的低频数字式相位测量仪。

本设计以ALTERA公司的复杂可编程逻辑器件(Altera Cyclone Ⅱ系列

FPGA)EP1K100QC208-3为核心,在FPGA内通过VHDL语言编写的相位测量电路,极大的简化了外围逻辑电路,提高了系统的可靠性,最终将软件计算得到的相位差通过LED数码管显示出来,读数方便。

该系统硬件电路简单,适用于200Hz~20kHz频率范围内的信号。

本系统充分利用FPGA对数据的高速处理能力,使得系统设计高效,可靠。