基于FPGA的面阵CCD图像采集系统

- 格式:pdf

- 大小:1.02 MB

- 文档页数:5

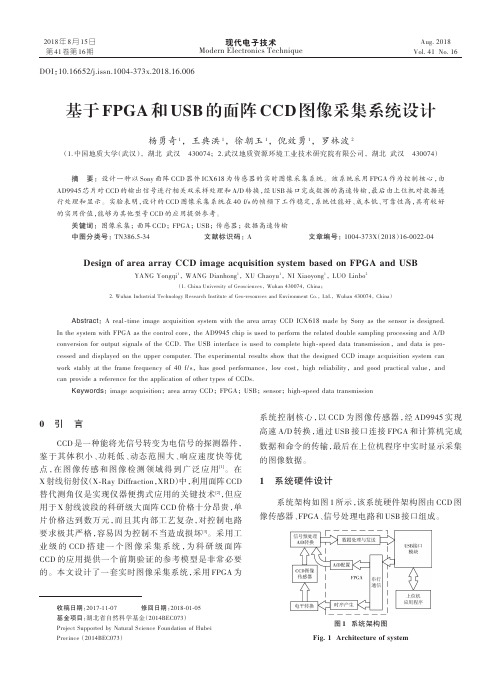

基于FPGA的图像采集处理系统在现代科技领域,特别是计算机视觉和机器学习领域,图像采集和处理已经成为一项至关重要的任务。

在许多应用中,需要快速、准确地对图像进行处理,这推动了图像采集和处理系统的研究和发展。

现场可编程门阵列(FPGA)作为一种可编程逻辑器件,具有并行处理能力强、功耗低、可重构等优点,使其成为构建高性能图像采集处理系统的理想选择。

FPGA是一种可通过编程来配置其硬件资源的集成电路,它由大量的可配置逻辑块、内存块和输入/输出块组成。

这些逻辑块和内存块可以在FPGA上被重新配置,以实现不同的逻辑功能和算法。

输入/输出块可以用于与外部设备进行通信。

基于FPGA的图像采集处理系统通常包括图像采集、预处理、传输、主处理和输出等几个主要环节。

这个阶段主要通过相机等设备获取图像数据。

相机与FPGA之间的接口可以是并行的,也可以是串行的。

并行接口通常传输速度更快,但需要更多的线缆;串行接口则使用更少的线缆,但传输速度可能较慢。

这个阶段主要是对采集到的原始图像数据进行初步处理,如去噪、灰度化、彩色化等。

这些处理任务可以在FPGA上并行进行,以提高处理速度。

经过预处理的图像数据需要通过接口或总线传输到主处理单元(通常是CPU或GPU)进行处理。

在传输过程中,可以使用DMA(直接内存访问)技术,以减少CPU的负载。

在这个阶段,主处理单元(通常是CPU或GPU)会对传输过来的图像数据进行复杂处理,如特征提取、目标检测、图像识别等。

这些处理任务需要大量的计算资源和算法支持。

处理后的图像数据可以通过接口或总线传输到显示设备或用于进一步的处理。

基于FPGA的图像采集处理系统具有处理速度快、可重构性强、功耗低等优点,使其在许多领域都有广泛的应用前景。

特别是在需要实时图像处理的场景中,如无人驾驶、机器视觉等,基于FPGA的图像采集处理系统将具有更高的性能和效率。

随着FPGA技术和相关算法的发展,我们可以预见,基于FPGA的图像采集处理系统将在未来得到更广泛的应用和推广。

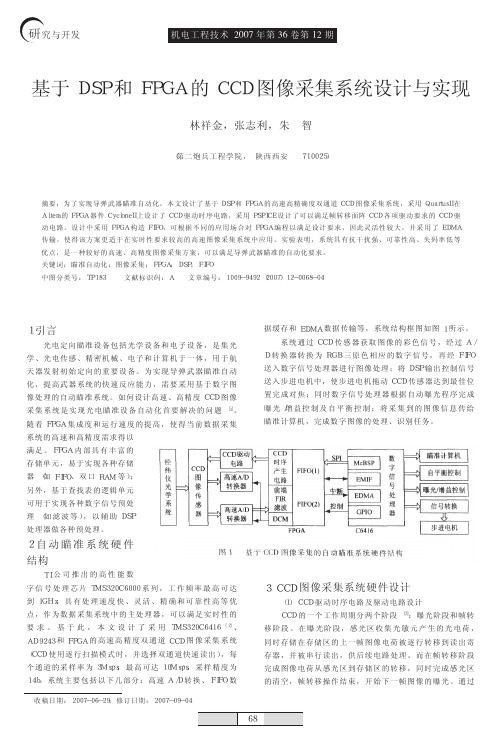

路选用独立脉冲源。

由晶体振荡器构成的时钟发生电路,输出频率为4MHz的时钟脉冲,经四分频器得到频率为lMHz的时钟脉冲。

再经脉宽调制器合成占空比为1:3的复位脉冲机,时钟脉冲牵。

为0.5MHz,由脉冲信号八分频得到,咖:由咖。

反相产生。

洲0=二二巫[=;;==矗10.。

n。

3=葛盆磊景兰兰莹三高刺广1n§nnn“nnnJ]n∞几九n几n几nn广一。

21j九n几n九几九nn栩几nn九n几几‘。

n堡.RnnH1nflIIInnnn哪nnnnn蚰月唧nnnnnnnnnn岫nMnnnn虚谩13单+元‰嚣元旧N"q.z4Nmr4像,vz元lq}州1虚嚣元一‰鏊雾图2TCDl206SUP驱动时序波形图3脉冲发生框图1爪虚设单元1.2.1分频器的实现该设计需要对4MHz的时钟脉冲分别进行四分频和八分频,在FPGA的设计中,分频器可采用图形输入设计,运用触发器或计数器来实现不同制式的分频;也可运用VHDL代码输入通过不同的算法来实现设计。

1.2.2脉宽调制器的实现脉宽调制器主要是实现脉冲信号的占空比,由图2可以得CCD的复位脉冲RS的频率为lMHZ,占空比为1:3。

实现1:3调制方法很多,可以采用VHDL有限状态机(FSM)进行设计,设定S0、Sl、s2三种不同的状态,有效脉到达时,状态机由S0依次转换到s2。

在S2状态时,状态机输出为高电平(1),其他状态输出低电平(O),从而实现占空比l:3调制。

在本系统的设计中,采用QuartusⅡ的图形输入设计方式。

运用两输入信号相异或来实现。

1.2.3脉冲信号发生器、反相器的实现脉冲信号发生器由晶体振荡器构成,输出频率为4MHz的时钟脉冲,作为FPGA的外部时钟,而反相器则可以用一非门电路就可以实现。

把上述各部分所生的symbol用QuanusⅡ提供的GraphicEditor编辑连接起来,进行整体模块仿真,其结果如图4。

从仿真的结果看,达到了设计要求。

图4CCD驱动时序仿真图612AD574与FPGA接口电路及程序设计AD574是美国模拟数字公司(Analog)推出的单片高速12位逐次比较型A/D转换器,内置双极性电路构成的混合集成转换显片,具有外接元件少,功耗低,精度高等特点,并且具有自动校零和自动极性转换功能,只需外接少量的阻容件即可构成一个完整的A/D转换器,其逻辑控制真值表如表1t表1AD574逻辑控制真值表由表1可得,采用状态机可实现模数转换过程,可将AD574的转换过程分为5个不同的工作状态:S幻一对AD574初始化;stl一启动12位转换;st2一等待转换;St3一12并行输出有效;St4—锁存数据。

基于FPGA的视频图像采集处理系统的设计与实现基于FPGA的视频图像采集处理系统的设计与实现摘要:本文针对传统视频图像采集系统在处理速度和资源利用率方面的不足,设计了一种基于FPGA的视频图像采集处理系统。

该系统通过使用FPGA作为硬件平台,结合图像预处理、图像编码和图像解码等核心模块,实现了快速高效的视频图像采集与处理。

实验结果表明,该系统在视频图像采集和处理的功能上具有较好的性能,能够广泛应用于图像处理领域。

1. 引言随着科技的不断发展,视频图像采集与处理在许多领域中得到了广泛应用,如监控系统、医疗影像等。

传统的视频图像采集处理系统通常使用软件实现,但由于软件的运行效率较低,无法满足实时处理的需求。

因此,基于FPGA的硬件实现方案成为了改进的方向。

2. 系统设计基于FPGA的视频图像采集处理系统主要由以下几个模块组成:图像采集模块、图像预处理模块、图像编码模块、图像解码模块和图像显示模块。

图像采集模块主要负责采集外部图像信号,并将其输入到FPGA中。

图像预处理模块对输入的图像进行处理,如去噪、增强等,以提高图像质量。

图像编码模块将处理后的图像进行编码,压缩数据量,并减少传输带宽。

图像解码模块将接收到的编码数据解码成原始图像数据。

图像显示模块将解码后的图像数据进行显示,以供用户观看。

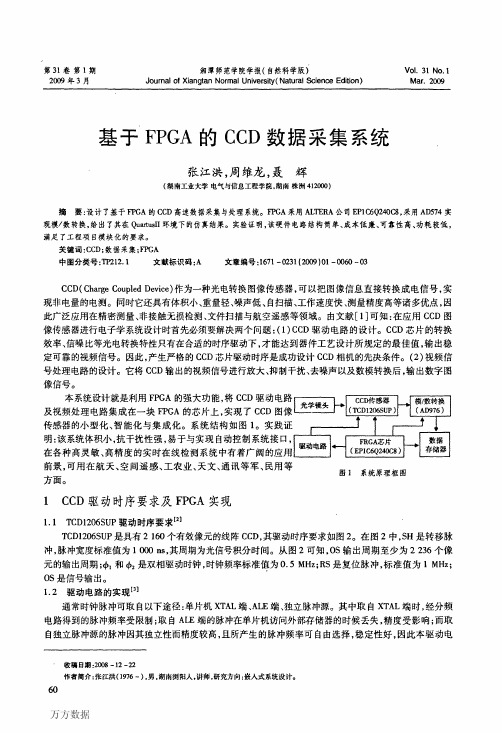

3. 系统实现在系统实现方面,首先需要选择适合的FPGA芯片作为硬件平台。

然后,利用Verilog来描述各个模块的功能,并进行相应的逻辑设计。

最后,通过将Verilog代码综合、布局和布线,生成FPGA配置文件,并烧录到FPGA芯片中。

4. 系统性能评估与实验结果分析为了评估系统的性能,进行了一系列实验。

实验结果表明,该系统在图像采集和处理的速度上优于传统的软件实现方法。

此外,该系统的资源利用效率也较高,能够满足实时处理的需求。

5. 系统应用展望基于FPGA的视频图像采集处理系统具有广泛的应用前景。

不仅可以应用于监控系统,还可以应用于医疗影像、工业检测等领域。

基于FPGA的图像采集系统设计与实现的开题报告一、研究背景与意义随着数字图像处理技术的广泛应用,图像采集技术也变得越来越重要。

图像采集系统是将现实世界中的信息转换为数字信号的设备,它通常包括图像采集器、模数转换器、数字信号处理器和存储器等。

其中,图像采集器是系统中最重要的部分,它能够将光学图像转换为数字信号。

图像采集器的性能,直接决定了整个图像采集系统的质量。

传统的图像采集系统通常使用CPLD或者DSP等芯片实现。

然而,由于CPLD的资源有限,DSP的算法处理能力不足等原因,这些方案存在一定的局限性。

而基于FPGA(Field Programmable Gate Array)的图像采集系统具有资源丰富、可重构性强、并行性好等优点,已经被广泛应用于高清视频采集、医学图像处理等领域。

本项目旨在设计和实现一种基于FPGA的图像采集系统,通过深入研究图像采集器的原理和方法,实现图像的高速、高质量采集,并将其应用到虚拟现实、机器视觉、数字医学等领域中。

二、研究内容和方法1. 研究图像采集器的原理和方法本研究将深入分析传感器传感器、ADC(Analog-to-Digital Converter)、PLL(Phase-Locked Loop)等图像采集器的基本原理和方法,研究图像采集系统中各个组件的作用,以及它们之间的相互作用关系,从而为后续的系统设计提供理论支持。

2. 设计FPGA图像采集器模块基于VHDL语言,设计FPGA图像采集器模块,并进行仿真验证。

重点研究采集器的硬件控制逻辑实现,解决同步时序、速率转换等问题。

利用FPGA的可重构性优势,优化数据处理流程,实现高速数据的运算和处理。

3. 设计采集器控制与接口电路设计采集器的各个接口电路,包括传感器电路、ADC电路、传输控制器与扩展接口等。

考虑和硬件的协作,使得系统更加完善。

4. 系统调试和实验验证通过基于硬件和仿真环境下的实验来验证采集器的性能和有效性。