IEEE754标准的32位低功耗浮点乘法器设计

- 格式:doc

- 大小:2.45 MB

- 文档页数:80

32位单精度浮点乘法器的FPGA实现摘要: 采用Verilog HDL语言, 在FPGA上实现了32位单精度浮点乘法器的设计, 通过采用改进型Booth编码,和Wallace 树结构, 提高了乘法器的速度。

本文使用Altera Quartus II 4.1仿真软件, 采用的器件是EPF10K100EQ 240 -1, 对乘法器进行了波形仿真, 并采用0.5CMOS工艺进行逻辑综...摘要: 采用Verilog HDL语言, 在FPGA上实现了32位单精度浮点乘法器的设计, 通过采用改进型Booth编码,和Wallace 树结构, 提高了乘法器的速度。

本文使用Altera Quartus II 4.1仿真软件, 采用的器件是EPF10K100EQ 240 -1, 对乘法器进行了波形仿真, 并采用0.5CMOS工艺进行逻辑综合。

关键词: 浮点乘法器; Boo th 算法; W allace 树; 波形仿真随着计算机和信息技术的快速发展, 人们对微处理器的性能要求越来越高。

乘法器完成一次乘法操作的周期基本上决定了微处理器的主频, 因此高性能的乘法器是现代微处理器中的重要部件。

本文介绍了32 位浮点阵列乘法器的设计, 采用了改进的Booth 编码, 和Wallace树结构, 在减少部分积的同时, 使系统具有高速度, 低功耗的特点, 并且结构规则, 易于VLSI的实现。

1 乘法计算公式32 位乘法器的逻辑设计可分为: Booth编码与部分积的产生, 保留进位加法器的逻辑, 乘法阵列的结构。

1.1 Booth编码与部分积的逻辑设计尾数的乘法部分,本文采用的是基4 Booth编码方式, 如表1。

首先规定A m和B m 表示数据A和B的实际尾数,P 表示尾数的乘积, PP n表示尾数的部分积。

浮点32 位数, 尾数是带隐含位1 的规格化数, 即: A m=1×a22a21….a0和B m = 1×b22b21.…b0, 由于尾数全由原码表示,相当于无符号数相乘, 24 × 24 位尾数乘积P 的公式为:1.2 乘法器的阵列结构本文采用的是3 -2 加法器, 输入3 个1 位数据: a, b,ci; 输出2 个1 位数据: s, Co。

按IEEE 754标准用单精度浮点数格式写出下列数值所对应的机器数(用十六进制表IEEE 754标准是一种定义了浮点数编码标准的标准。

按照这个标准,浮点数由三部分组成:符号位、指数和尾数。

具体而言,单精度浮点数格式使用32位二进制数表示,其中1位是符号位、8位是指数位和23位是尾数位。

本文将通过分步骤演示,按照IEEE 754标准用单精度浮点数格式写出下列数值所对应的机器数,其中0代表正数,1代表负数。

1. 3.14首先,将3.14转换为二进制数。

整数部分转换为二进制数就是3的二进制数为11,小数部分使用乘2取整法,即乘以2再取整,直到小数部分为0或达到精度要求。

具体地,0.14*2=0.28,小数部分为0.28,整数部分为00.28*2=0.56,小数部分为0.56,整数部分为00.56*2=1.12,小数部分为0.12,整数部分为10.12*2=0.24,小数部分为0.24,整数部分为00.24*2=0.48,小数部分为0.48,整数部分为00.48*2=0.96,小数部分为0.96,整数部分为00.96*2=1.92,小数部分为0.92,整数部分为10.92*2=1.84,小数部分为0.84,整数部分为10.84*2=1.68,小数部分为0.68,整数部分为10.68*2=1.36,小数部分为0.36,整数部分为10.36*2=0.72,小数部分为0.72,整数部分为00.72*2=1.44,小数部分为0.44,整数部分为00.44*2=0.88,小数部分为0.88,整数部分为00.88*2=1.76,小数部分为0.76,整数部分为10.76*2=1.52,小数部分为0.52,整数部分为10.52*2=1.04,小数部分为0.04,整数部分为10.04*2=0.08,小数部分为0.08,整数部分为00.08*2=0.16,小数部分为0.16,整数部分为00.16*2=0.32,小数部分为0.32,整数部分为00.32*2=0.64,小数部分为0.64,整数部分为00.64*2=1.28,小数部分为0.28,整数部分为10.28*2=0.56,小数部分为0.56,整数部分为00.56*2=1.12,小数部分为0.12,整数部分为10.12*2=0.24,小数部分为0.24,整数部分为00.24*2=0.48,小数部分为0.48,整数部分为00.48*2=0.96,小数部分为0.96,整数部分为00.96*2=1.92,小数部分为0.92,整数部分为1将上述的整数部分拼接起来,得到的二进制数为:11.00100011110101110000101根据IEEE 754标准,将该二进制数表示成单精度浮点数格式,具体步骤如下:1.确定符号位由于3.14是正数,因此符号位为0。

第27 卷第9 期合肥工业大学学报(自然科学版)V o l. 27 N o. 9 2004 年9 月JOU RNA L O F H EF E I UN IV ER S IT Y O F T ECHNOLO GY Sep. 200432 位快速乘法器的设计詹文法, 汪国林, 杨羽, 张珍(合肥工业大学电气与自动化工程学院, 安徽合肥230009)摘要: 高性能乘法器是现代微处理器中的重要部件, 乘法器完成一次乘法操作的周期基本上决定了微处理器的主频。

传统的乘法器的设计, 在最终的乘积项求和时, 常采用阵列相加或叠代相加的方法, 不适用中小规模的微处理器的设计。

该文提出的32 位乘法器, 采用了Boo th 编码、422 压缩器、W allace 树算法以及超前进位加法器等多种算法和技术, 在节约面积的同时, 获得了高速度的性能。

关键词: 乘法器; Boo th 编码; 超前进位加法器; W allace 树算法中图分类号: T P 342. 21 文献标识码: A文章编号: 100325060 (2004) 0921 099204D es ign of 32-b it m ul t ipl ier w ith good speed performan ceZHAN W en2fa, W A N G Guo 2lin, YA N G Yu, ZHAN G Zhen(Schoo l of E lectri c Engineeri ng and A utom at ion, H efei U niversity of T echno logy, H ef ei 230009, Ch ina)Abstract: A m u lt i p lier w ith good speed perfo rm ance is a very im po rtan t un it in the m odern m icrop ro2 cesso rs becau s e the cycle that a m u lt i p lier com p letes one m u lt i p lica t i o n operat i o n dete r m ines the m ain frequency of the m icrop rocesso r. In summ ing of the last p roduct in the t radit i o nal m u lt i p lier des ign, the array o r iterat i o n summ ing m ethod is u sed, w h ich is no t su itab le to the des ign of sm all o r m iddle scale in t egrat i o n circu i t. A 322b i t m u lt i p lier is p resen t ed in w h ich m any m ethods, such as Boo th algo2 rithm , 422 com p resso rs, W allace t ree algo rithm , and carry2loo kahead adder, are app lied, w h ich re2 su lt s in h igh speed perfo rm ance.Key words: m u lt i p lier; Boo th algo rithm ; carry2loo kahead adder; W allace t ree algo rithm高性能乘法器是现代微处理器中的重要部件, 乘法器完成一次乘法操作的周期基本上决定了微处理器的主频。

ieee754标准的32位浮点规格化数IEEE 754标准的32位浮点规格化数1. 介绍IEEE 754标准是一种针对二进制浮点数的数值表示方法,用于在计算机中表示和处理浮点数。

这个标准定义了浮点数的表示方法、运算规则和舍入模式,并被广泛应用于计算机硬件和软件系统中。

本文将重点介绍IEEE 754标准中的32位浮点规格化数,包括其表示方法、特点和应用场景。

2. 32位浮点规格化数的表示方法IEEE 754标准中的32位浮点规格化数由三个部分组成:符号位、指数位和尾数位。

其中符号位决定了数值的正负,指数位决定了数值的大小,尾数位则决定了数值的精度。

具体而言,这32位二进制数的第1位是符号位,接下来的8位是指数位,剩下的23位是尾数位。

符号位为0表示正数,为1表示负数;指数位采用偏移码表示,用来表示数值大小的量级;尾数位则存储数值的小数部分,决定数值的精确度。

此外,IEEE 754标准规定了特殊值的表示方法,如正负无穷大、NaN(不是一个数字)等。

3. 32位浮点规格化数的特点32位浮点规格化数具有以下几个特点:3.1 范围广由于指数位的长度是8位,可以表示的指数范围为-126至127,因此32位浮点规格化数可以表示非常大和非常小的数值。

同时,指数位中的偏移码使得指数值可以被表示为有符号数。

3.2 精度限制由于尾数位只有23位,这意味着32位浮点规格化数的精度有限。

这是因为尾数位的长度限制了小数部分的位数,从而限制了数值的精度。

因此,在进行浮点数的运算时,可能会出现精度丢失的问题。

3.3 舍入误差在进行浮点数运算时,由于尾数位的限制,可能会出现舍入误差。

舍入误差是由于将无限精度的实数转换为有限精度的浮点数引起的,这可以导致计算结果与实际结果之间的差异。

4. 32位浮点规格化数的应用场景32位浮点规格化数广泛应用于计算机硬件和软件系统中,特别是在科学计算、工程设计和图形处理等领域。

4.1 科学计算科学计算中的很多数值问题需要使用浮点数进行表示和计算,而32位浮点规格化数能够提供较高的数值范围和精度,满足科学计算的基本需求。

32位浮点乘法器的设计与仿真代码一、引言随着计算机科学和技术的不断发展,浮点乘法器在科学计算、图像处理、人工智能等领域中扮演着重要的角色。

本文将详细讨论32位浮点乘法器的设计与仿真代码,并深入探讨其原理和实现方法。

二、浮点数表示在开始设计32位浮点乘法器之前,我们首先需要了解浮点数的表示方法。

浮点数由符号位、阶码和尾数组成,其中符号位表示数的正负,阶码确定数的大小范围,尾数表示数的精度。

三、浮点乘法器的原理浮点乘法器的原理基于乘法运算的基本原理,即将两个数的尾数相乘,并将阶码相加得到结果的阶码。

同时需要考虑符号位的处理和对阶的操作。

下面是32位浮点乘法器的基本原理:1.获取输入的两个浮点数A和B,分别提取出符号位、阶码和尾数。

2.将A和B的尾数相乘,得到乘积P。

3.将A和B的阶码相加,得到结果的阶码。

4.对乘积P进行规格化,即将小数点左移或右移,使其满足规定的位数。

5.对结果的阶码进行溢出判断,若溢出则进行相应的处理。

6.将符号位与结果的阶码和尾数合并,得到最终的浮点乘积。

四、浮点乘法器的设计根据浮点乘法器的原理,我们可以开始进行浮点乘法器的设计。

设计的关键是确定乘法器中各个部件的功能和连接方式。

下面是浮点乘法器的设计要点:1.输入模块:负责接收用户输入的两个浮点数,并提取出符号位、阶码和尾数。

2.乘法模块:负责将两个浮点数的尾数相乘,得到乘积P。

3.加法模块:负责将两个浮点数的阶码相加,得到结果的阶码。

4.规格化模块:负责对乘积P进行规格化操作,使其满足规定的位数。

5.溢出判断模块:负责判断结果的阶码是否溢出,并进行相应的处理。

6.输出模块:负责将符号位、阶码和尾数合并,得到最终的浮点乘积。

五、浮点乘法器的仿真代码为了验证浮点乘法器的设计是否正确,我们需要进行仿真测试。

下面是一段简单的浮点乘法器的仿真代码:module floating_point_multiplier(input wire [31:0] a,input wire [31:0] b,output wire [31:0] result);wire [31:0] mantissa;wire [7:0] exponent;wire sign;// 提取符号位assign sign = a[31] ^ b[31];// 提取阶码assign exponent = a[30:23] + b[30:23];// 尾数相乘assign mantissa = a[22:0] * b[22:0];// 规格化assign {result[30:23], result[22:0]} = {exponent, mantissa};// 处理溢出always @(*)beginif (exponent > 255)result = 32'b0; // 结果溢出为0else if (exponent < 0)result = 32'b0; // 结果溢出为0elseresult[31] = sign;endendmodule六、浮点乘法器的应用浮点乘法器在科学计算、图像处理、人工智能等领域中有着广泛的应用。

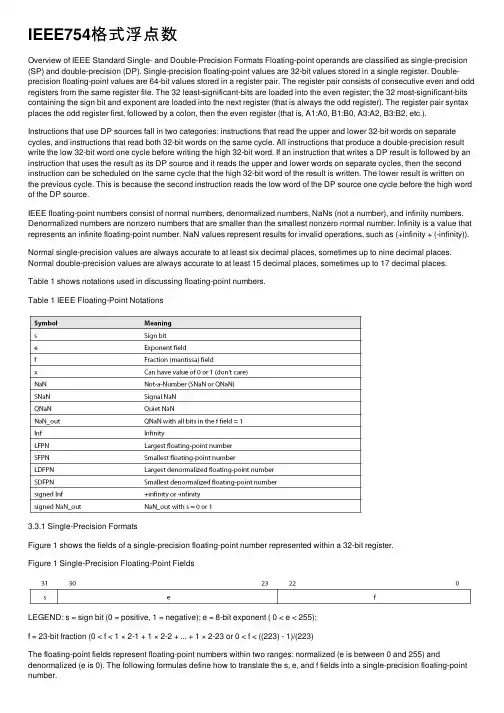

IEEE754格式浮点数Overview of IEEE Standard Single- and Double-Precision Formats Floating-point operands are classified as single-precision (SP) and double-precision (DP). Single-precision floating-point values are 32-bit values stored in a single register. Double-precision floating-point values are 64-bit values stored in a register pair. The register pair consists of consecutive even and odd registers from the same register file. The 32 least-significant-bits are loaded into the even register; the 32 most-significant-bits containing the sign bit and exponent are loaded into the next register (that is always the odd register). The register pair syntax places the odd register first, followed by a colon, then the even register (that is, A1:A0, B1:B0, A3:A2, B3:B2, etc.).Instructions that use DP sources fall in two categories: instructions that read the upper and lower 32-bit words on separate cycles, and instructions that read both 32-bit words on the same cycle. All instructions that produce a double-precision result write the low 32-bit word one cycle before writing the high 32-bit word. If an instruction that writes a DP result is followed by an instruction that uses the result as its DP source and it reads the upper and lower words on separate cycles, then the second instruction can be scheduled on the same cycle that the high 32-bit word of the result is written. The lower result is written on the previous cycle. This is because the second instruction reads the low word of the DP source one cycle before the high word of the DP source.IEEE floating-point numbers consist of normal numbers, denormalized numbers, NaNs (not a number), and infinity numbers. Denormalized numbers are nonzero numbers that are smaller than the smallest nonzero normal number. Infinity is a value that represents an infinite floating-point number. NaN values represent results for invalid operations, such as (+infinity + (-infinity)).Normal single-precision values are always accurate to at least six decimal places, sometimes up to nine decimal places. Normal double-precision values are always accurate to at least 15 decimal places, sometimes up to 17 decimal places.Table 1 shows notations used in discussing floating-point numbers.Table 1 IEEE Floating-Point Notations3.3.1 Single-Precision FormatsFigure 1 shows the fields of a single-precision floating-point number represented within a 32-bit register.Figure 1 Single-Precision Floating-Point FieldsLEGEND: s = sign bit (0 = positive, 1 = negative); e = 8-bit exponent ( 0 < e < 255);f = 23-bit fraction (0 < f < 1 × 2-1 + 1 × 2-2 + ... + 1 × 2-23 or 0 < f < ((223) - 1)/(223)The floating-point fields represent floating-point numbers within two ranges: normalized (e is between 0 and 255) and denormalized (e is 0). The following formulas define how to translate the s, e, and f fields into a single-precision floating-point number.Normalized: -1s × 2(e - 127) × 1.f 0 < e < 255Denormalized (Subnormal): -1s × 2-126 × 0.f e = 0; f is nonzeroTable 2 shows the s, e, and f values for special single-precision floating-point numbers.Table 2 Special Single-Precision ValuesTable 3 shows hexadecimal and decimal values for some single-precision floating-point numbers. Table 3 Hexadecimal and Decimal Representation for Selected Single-Precision Values3.3.2 Double-Precision FormatsFigure 2 shows the fields of a double-precision floating-point number represented within a pair of 32-bit registers.Figure 2 Double-Precision Floating-Point FieldsThe floating-point fields represent floating-point numbers within two ranges: normalized (e is between 0 and 2047) and denormalized (e is 0). The following formulas define how to translate the s, e, and f fields into a double-precision floating-point number.Normalized: -1s × 2(e - 1023) × 1.f 0 < e < 2047 Denormalized (Subnormal): -1s × 2-1022 × 0.f e = 0; f is nonzeroTable 4 shows the s, e, and f values for special double-precision floating-point numbers.Table 4 Special Double-Precision ValuesTable 5 shows hexadecimal and decimal values for some double-precision floating-point numbers. Table 5 Hexadecimal and Decimal Representation for Selected Double-Precision ValuesSymbol Hex Value Decimal ValueNaN_out 7FFFFFFFFFFFFFFF QNaN0 0000000000000000 0.0-0 8000000000000000 -0.01 3FF0000000000000 1.02 4000000000000000 2.0LFPN 7FEFFFFFFFFFFFFF 1.7976931348623157e+308SFPN 0010000000000000 2.2250738585072014e-308LDFPN 000FFFFFFFFFFFFF 2.2250738585072009e-308SDFPN 0000000000000001 4.9406564584124654e-324。

IEEE-75432位单精度浮点数计算VB源码VB IEEE-754 32位单精度浮点数计算源码Option ExplicitPrivate Function GetData(TmpHex As String) As StringDim TmpBin As StringDim TmpMi As IntegerOn Error Resume NextTmpBin = HexT oBin(TmpHex)Label1.Caption = TmpBin & " 长度" & Len(TmpBin) & "位,第1位1为负数,0为正数"TmpMi = BinT oOct(Mid(TmpBin, 2, 8)) - 127GetData = Round(BinT oOct("1." & Mid(TmpBin, 10, 23)) * (2 ^ TmpMi), 6)If Left(TmpBin, 1) = "1" Then GetData = "-" & GetDataEnd FunctionPrivate Function HexToBin(TmpHex As String) As StringDim n As IntegerDim I As IntegerDim TmpBin As StringOn Error Resume NextFor n = 1 To Len(TmpHex)I = Val("&H" & Mid(TmpHex, n, 1))TmpBin = ""While I > 0TmpBin = CStr(I Mod 2) & TmpBinI = I \ 2WendHexToBin = HexToBin & Right("0000" & TmpBin, 4)Next nEnd FunctionPrivate Function BinToOct(TmpBin As String) As DoubleDim n As IntegerDim TmpS() As StringOn Error Resume NextTmpS = Split(TmpBin, ".")For n = 1 To Len(TmpS(0))If Mid(TmpS(0), n, 1) = "1" Then BinT oOct = BinToOct + (2 ^ (Len(TmpS(0)) - n)) Next nIf UBound(TmpS) = 1 ThenFor n = 1 To Len(TmpS(1))If Mid(TmpS(1), n, 1) = "1" Then BinT oOct = BinToOct + (2 ^ (-1 * n)) Next nEnd IfEnd Function。

ieee754标准32位浮点数

IEEE 754标准定义的32位浮点数,通常称为单精度浮点数,其结构如下:

符号位(Sign bit): 占用1位,位于最左边。

用于表示数值的正负,0代表正数,1代表负数。

指数位(Exponent): 占用8位,用于表示数值的指数部分。

这8位按照偏移量(bias)计算实际的指数值。

对于32位浮点数,偏移量是127。

也就是说,存储的指数值等于实际指数加上127。

尾数位(Mantissa)或有效数字位(Fraction): 占用剩下的23位。

这部分用于表示数值的有效数字。

在标准化的浮点数表示中,有效数字的最高位总是1,因此在存储时通常省略这一位,以提高精度。

例如,一个32位浮点数的二进制表示为11000001010100000000000000000000,可以这样解析:

符号位:1(表示负数)

指数位:10000010(表示130,实际指数为130 - 127 = 3)

尾数位:10100000000000000000000(表示有效数字1.101)

因此,该浮点数的值为-1.101 \times 2^3,转换为十进制为-1.625 \times 8 = -13.0。

基于FPGA的高速流水线浮点乘法器设计与实现

摘要:设计了一种支持IEEE754浮点标准的32位高速流水线结构浮点乘法器。

该乘法器采用新型的基4布思算法,改进的4:2压缩结构和部分积求和电路,完成Carry Save形式的部分积压缩,再由Carry Look-ahead加法器求得乘积。

时序仿真结果表明该乘法器可稳定运行在80M的频率上,并已成功运用在浮点FFT处理器中。

1 引言

在数字化飞速发展的今天,人们对微处理器的性能要求也越来越高。

作为衡量微处理器性能的主要标准,主频和乘法器运行一次乘法的周期息息相关。

因此,为了进一步提高微处理器性能,开发高速高精度的乘法器势在必行。

同时由于基于IEEE754 标准的浮点运算具有动态范围大,可实现高精度,运算规律较定点运算更为简捷等特点,浮点运算单元的设计研究已获得广泛的重视。

本文介绍了32 位浮点乘法器的设计,采用了基4 布思算法,改进的4:2 压缩器及布思编码算法,并结合FPGA 自身特点,使用流水线设计技术,在实现高速浮点乘法的同时,也使是系统具有了高稳定性、规则的结构、易于FPGA 实现及ASIC 的HardCopy 等特点。

32位浮点加法器设计一、基本原理浮点数加法运算是在指数和尾数两个部分进行的。

浮点数一般采用IEEE754标准表示,其中尾数部分采用规格化表示。

浮点加法的基本原理是将两个浮点数的尾数对齐并进行加法运算,再进行规格化处理。

在加法运算过程中,还需考虑符号位、指数溢出、尾数对齐等特殊情况。

二、设计方案1. 硬件实现方案:采用组合逻辑电路实现浮点加法器,以保证运算速度和实时性。

采用Kogge-Stone并行加法器、冒泡排序等技术,提高运算效率。

2.数据输入:设计32位浮点加法器,需要提供两个浮点数的输入端口,包括符号位、指数位和尾数位。

3.数据输出:设计32位浮点加法器的输出端口,输出相加后的结果,包括符号位、指数位和尾数位。

4.控制信号:设计合适的控制信号,用于实现指数对齐、尾数对齐、规格化等操作。

5.流程控制:设计合理的流程控制,对各个部分进行并行和串行处理,提高加法器的效率。

三、关键技术1. Kogge-Stone并行加法器:采用Kogge-Stone并行加法器可以实现多位数的并行加法运算,提高运算效率。

2.浮点数尾数对齐:设计浮点加法器需要考虑浮点数尾数的对齐问题,根据指数大小进行右移或左移操作。

3.溢出判断和处理:浮点加法器需要判断浮点数的指数是否溢出,若溢出需要进行调整和规格化。

4.符号位处理:设计浮点加法器需要考虑符号位的处理,确定加法结果的符号。

四、性能评价性能评价是衡量浮点加法器设计好坏的重要指标。

主要从以下几个方面进行评价:1.精度:通过与软件仿真结果进行比较,评估加法器的运算精度,误差较小的加法器意味着更高的性能。

2.速度:评估加法器的运行速度,主要考虑延迟和吞吐量。

延迟越低,意味着加法器能够更快地输出结果;吞吐量越高,意味着加法器能够更快地处理多个浮点加法运算。

3.功耗:评估加法器的功耗情况,低功耗设计有助于提高整个系统的能效。

4.面积:评估加法器的硬件资源占用情况,面积越小意味着设计更紧凑,可用于片上集成、嵌入式系统等场景。

基于改进型选择进位加法器的32位浮点乘法器设计作者:刘容赵洪深李晓今来源:《现代电子技术》2013年第16期摘要:在修正型Booth算法和Wallace树结构以及选择进位加法器的基础上,提出了一种新型32位单精度浮点乘法器结构。

该新型结构通过截断选择进位加法器进位链,缩短了关键路径延时。

传统选择进位加法器每一级加法器的进位选择来自上级的进位输出。

提出的结构可以提前计算出尾数第16位的结果,它与Wallace树输出的相关位比较就可得出来自前一位的进位情况进而快速得到进位选择。

在Altera的EP2C70F896C6器件上,基于该结构实现了一个支持IEEE754 浮点标准的4级流水线浮点乘法器,时序仿真表明,该方法将传统浮点乘法器结构关键路径延时由6.4 ns减小到5.9 ns。

关键词:修正Booth算法; Wallace树结构;选择进位加法器;浮点乘法器中图分类号: TN702⁃34 文献标识码: A 文章编号: 1004⁃373X(2013)16⁃0133⁃04浮点乘法器是数字处理器的重要组成单元,它的性能直接关系到整个数字系统的性能。

所以浮点乘法器一直以来是人们研究的热点。

而乘法器的设计主要是对速度、面积、功耗等因素的优化与折中。

Booth 算法大大缩小了部分积数量;Wallace tree、dadda tree等压缩树结构实现部分积的并行求和提高了乘法器的速度,进位保留加法器(Carry Save Adder,CSA)则实现最终两个部分积的快速求和。

文献[1]基于乘法器各级核心器件是加法器的思想,通过优化加法器减小了乘法器的延时。

文献[2]设计了一种改进的基4 Booth编码和华莱士树的24位符号定点乘法器,在功耗和面积降低的同时,延时也得到了减小,做到了芯片性能和设计复杂度之间的良好折中。

文献[3]提出了一种适用于FPGA结构的改进型Wallace tree架构乘法器,实现了资源和性能的合理平衡。

西安邮电大学毕业设计(论文)题目:32位低功耗浮点乘法器设计学院:电子工程学院专业:集成电路设计与集成设计班级:电路1303学生姓名:白进宝学号:05136073导师姓名:邢立冬职称:高级工程师起止时间:2017年3月6日至2017年6月11日毕业设计(论文)声明书本人所提交的毕业论文《32位低功耗浮点乘法器设计》是本人在指导教师指导下独立研究、写作的成果,论文中所引用他人的文献、数据、图件、资料均已明确标注;对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式注明并表示感谢。

本人完全理解《西安邮电大学本科毕业设计(论文)管理办法》的各项规定并自愿遵守。

本人深知本声明书的法律责任,违规后果由本人承担。

论文作者签名:日期:年月日西安邮电大学本科毕业设计(论文)选题审批表西安邮电大学本科毕业设计(论文)开题报告西安邮电大学毕业设计 (论文)成绩评定表摘要乘法器是高性能数字信号处理芯片的关键部件,也是实时、高速数字信号处理器的核心。

乘法单元具有面积大、延时长、结构复杂的特点,如何设计出高速、低功耗、结构简单的乘法单元是近些年来的一大难题。

本文比较各种乘法器设计的算法与结构,分析它们的面积、速度与功耗。

最终找出最优的设计方案,完成32位浮点乘法器的电路设计。

本文首先介绍IEEE-754浮点数标准和浮点操作,对IEEE-754浮点运算标准的浮点表示格式、精度、范围、规格化进行分析,并对决定乘法器性能的实现算法与实现结构进行深入研究。

其中实现浮点乘法的重点是实现整数的乘法。

其主要实现途径有移位相加结构和华莱士树型结构。

移位相加乘法结构简单,但是延时较长;华莱士树型乘法延时较短,但是结构比较复杂。

为了进一步提高运算速度,将乘法器改为流水线结构,达到时间上的并行。

最后应用低功耗设计方法对电路进行优化设计以降低系统功耗。

关键词:IEEE-754;乘法器;移位相加;华莱士树;流水线;低功耗ABSTRACTMultiplier is the key component of high performance digital signal processing chip, and also the core of real-time and high-speed digital signal processor. The multiplication unit has the characteristics of large area, long delay and complex structure. How to design a multiplication unit with high speed, low power consumption and simple structure is a difficult problem in recent years.In this paper, the algorithms and structures of various multipliers are compared, and their area, speed and power consumption are analyzed. Finally, the optimal design scheme is found, and the circuit design of 32 bit floating point multiplier is completed.This paper first introduces the IEEE-754 floating point standard and floating point operations on floating-point IEEE-754 floating-point standard expression analysis format, accuracy, scope, standard, and implementation of the decision performance of multiplier algorithm in-depth research and implementation of structure. Among them, the key point of floating point multiplication is to achieve the multiplication of integers. The main implementation methods include shift adding structure and Wallace tree structure. The shift addition and multiplication structure is simple, but the time delay is long; the Wallace tree type multiplication delay is shorter, but the structure is complex. In order to further improve the speed of operation, the multiplier is changed into pipelined structure to achieve parallel time. Finally, the low power design method is applied to optimize the circuit to reduce system power consumption.Key words: IEEE-754;Multiplier;Shift addition;Wallace tree;Assembly line;low power consumption目录第一章绪论 (1)1.1 研究意义 (1)1.2 研究的主要内容 (1)1.3 论文结构安排 (1)第二章设计原理概述 (3)2.1 浮点数格式 (3)2.2 IEEE-754浮点数标准 (3)2.3 浮点乘法运算原理 (5)第三章浮点乘法器电路设计 (7)3.1 无符号数一位乘法 (7)3.2 超前进位加法器设计 (8)3.3 移位相加乘法结构 (9)3.4 华莱士树结构 (10)3.5 尾数的舍入与规格化 (17)3.6 阶码的处理 (19)3.7 符号位处理 (20)3.8 浮点乘法器总体结构 (20)3.9 流水线结构 (21)3.9.1 流水线技术简介 (21)3.9.2 流水线浮点乘法器设计 (21)3.10 低功耗设计 (22)3.10.1 低功耗设计背景 (22)3.10.2 低功耗设计方法 (22)3.10.3 浮点乘法器的低功耗设计 (24)3.11 本章小结 (25)第四章仿真验证与逻辑综合 (26)4.1 功能仿真 (26)4.1.1 尾数运算功能仿真 (26)4.1.2 浮点乘法器功能仿真 (27)4.1.3 流水线结构浮点乘法器功能仿真 (28)4.2 浮点乘法器逻辑综合 (29)4.3 浮点乘法器时序仿真 (30)4.4 功耗分析 (30)结束语 (32)致谢 (33)参考文献 (34)附录 (35)第一章绪论1.1 研究意义进入21世纪以,来大数据、互联网+、人工智能等新兴技术正在逐步进入到我们的生活当中。

基于RISC指令系统的32位浮点加减法运算器设计摘要:浮点运算部件一直是限制微处理器性能的一个关键因素。

在分析了浮点运算器的结构和算法,提出了一种支持IEEE-754标准的浮点加减法运算器的实现方案,并详细介绍了该运算器的结构和算法。

方案采用了四级流水线的结构,即:0操作数检查、对阶、尾数运算、结果规格化及舍入处理。

每个步骤可以单独作为一个模块,在每个模块之间增加了寄存器,利用这些寄存器可以为下一个操作准备正确的数据。

关键词:流水线,IEEE-754标准,警戒位,舍入法32 bit Floating-Point Addition and Subtraction ALU Design Based onRISC StructureABSTRACT:Floating-Point arithmetic unit is always key factor of restricting microprocessor performance.This paper analyses structure and algorithm of Floating-Point ALU and brings forward a scenario about Floating-Point addition and subtraction ALU which supports IEEE-754 standard. The scenario adopts 4-Level pipelining structure: 0 operation numbers check、match exponent、fraction arithmetic、result normalization and rounding. Each step can be act as a single module. Among these modules, there are some registers which can prepare correct data for next operation.Keywords: pipelining, IEEE-754 Standard, Guard Digit, Rounding Method1 引言随着SOC技术、IP技术以及集成电路技术的发展,RISC软核处理器的研究与开发设计开始受到了人们的重视。

上溢、下溢与除以零等异常情况在大多数系统中是经常发生的。

以双精度浮点数为例,如果只考虑格式化数,则它的溢出有四种情况:(1)正数大于(1-532-)×21024的情况为正上溢;(2)正数小于0.5×21023的;(3)负数小于-(1-253-)×21024的情况为负上溢; (4)负数大于0.5×21023-的情况为负下溢。

在浮点运算过程中一个很重要的步骤是舍入。

舍入的目的是使得有效数据的位数保持在固定位数范围内。

IEEE754标准规定了四种舍入模式:(1)就近舍入(偶数):目标是使舍入结果尽可能接近实际值。

最大误差为±21LSB(Least Significant Bit)。

(2)零舍入RZ :通过截断实际值的多余位来实现。

最大误差为土LSB 。

(3)+∞舍入:结果向正无穷大方向舍入。

所有值被舍入到下一个可能值,负数的舍入结果将截去多余位,正数的舍入结果为下一个较大的有效值。

(4)-∞舍入:结果向负无穷大方向舍入。

负数的舍入结果将为下一个较小的有效值,正数的舍入结果将截去多余位。

下表给出了不同的舍入方法下的舍入结果,以8位值舍入为4位值为例。

不同舍入方法的舍入值数值 就近舍入 零舍入 +∞舍入 -∞舍入 .01101001 .0111 .0110 .0111 .0110 -.01101001 -.0111 -.0110 -.0110 -.0111 .10000111 .1000 .1000 .1001 .1000 -10000111 -.1000 -.1000 -.1000 -.1001 .10000000 .1000.1000.1000.1000浮点运算单元源代码:module alu(flout_a,flout_b,clk,en,rst,flout_c,yichu); //浮点运算单元模块 input[31:0] flout_a; //输入的被乘数 input[31:0] flout_b; //输入的乘数 input clk; //时钟信号 input en; //使能信号 input rst; //复位信号 output[31:0] flout_c; //输出运算结果 output[1:0] yichu; //输出溢出标志 reg[31:0] flout_c; reg[1:0] yichu; reg[1:0] overflow; reg s3;reg s1,s2; //符号reg[7:0] exp1,exp2,exp3; //阶码reg[22:0] man1,man2,man3; //尾数reg n;reg[7:0] temp1;reg[7:0] temp2;reg[8:0] temp3;reg[23:0] temp;reg[45:0] comeout;reg[23:0] all; //小数部分reg[1:0] zheng; //整数部分always@(posedge clk) //提取flout_a的符号,阶码,尾数beginif(!rst)begins1<=1'b0;exp1<=8'b00000000;man1<=23'b0;endelse if(en)begins1<=flout_a[31];exp1<=flout_a[30:23];man1<=flout_a[22:0];endendalways @(posedge clk) //提取flout_b的符号,阶码,尾数beginif(!rst)begins2<=1'b0;exp2<=8'b00000000;man2<=23'b0;endelse if(en)begins2<=flout_b[31];exp2<=flout_b[30:23];man2<=flout_b[22:0];endendalways@(posedge clk) //尾数相乘beginif(man1==23'b0000000000_0000000000000)beginman3=man1;n=1'b0;endelse if(man2==23'b0000000000_0000000000000)beginman3=man2;n=1'b0;end //处理特殊值elsebegincomeout=man1*man2;temp=man1+man2; //1.m*1.n=1+(0.m+0.n)+(0.m*0.n) all=temp[22:0]+comeout[45:23];zheng=1'b1+temp[23];zheng=zheng+all[23]; //整数if(zheng[1]==1) //整数小于4而大于1beginn=1'b1; //左归阶码应加1if(zheng[0]==1)man3[22:0]={2'b1,all[22:1]}; //零舍入elseman3[22:0]={2'b0,all[22:1]};endelsebeginn=1'b0;man3=all[22:0];endendendalways@(posedge clk) //阶码相加beginif(exp1[7]==1)temp1={1'b0,exp1[6:0]};else temp1={1'b1,exp1[6:0]};if(exp2[7]==1)temp2={1'b0,exp2[6:0]};else temp2={1'b1,exp2[6:0]}; //把阶码的移码形式变为补码形式temp3=temp1+temp2;temp3=temp3+n;if(temp3[8:7]==2'b01)overflow=2'b01; //阶码上溢elsebeginif(temp3[8:7]==2'b10)overflow=2'b10; //阶码下溢else overflow=2'b00;endcase(temp3[8:7])2'b00:exp3={1'b1,temp3[6:0]};2'b01:exp3=temp3[7:0];2'b11:exp3={1'b0,temp3[6:0]};2'b10:exp3=temp3[7:0];endcaseendalways@(posedge clk) //输出结果begins3=s1^s2;yichu= overflow;if(man3==0)beginflout_c=32'b0;yichu=2’b00;endelse flout_c={s3,exp3[7:0],man3[22:0]};endendmodule。

32位单精度浮点乘法器的FPGA 实现胡侨娟,仲顺安,陈越洋,党 华(北京理工大学 北京 100081)摘 要:采用V erilog HDL 语言,在FPGA 上实现了32位单精度浮点乘法器的设计,通过采用改进型Boo th 算法和W allace 树结构,提高了乘法器的速度。

本文使用A ltera Q uartus II 411仿真软件,采用的器件是EPF 10K 100EQ 2401,对乘法器进行了波形仿真,并采用015C M O S 工艺进行逻辑综合。

关键词:浮点乘法器;Boo th 算法;W allace 树;波形仿真中图分类号:T P 33212+2 文献标识码:B 文章编号:1004373X (2005)2402302I m plem en ta tion of 32b it Si ngle Prec ision Floa ti ng Po i n tM ultipl ier Ba sed on FPGAHU Q iao juan ,ZHON G Shunan ,CH EN Yueyang ,DAN G H ua(Beijing Institute of T echno l ogy,Beijing,100081,Ch ina )Abs tra c t :U sing V erilog HDL ,a design of 32b single p recisi on floating po int m ulti p lier based on FPGA is p resented 1By using astructure of W allace trees and Boo th algo rithm ,the speed of m ulti p lier has been i m p roved 1T he softw are of A ltera Q uartus II 411is used fo r perfo r m ing the w ave si m ulati on of the m ulti p lier w ith EPF 10K 100EQ 2401device 1T he m ulti p lier is synthesized w ith 015C M O S techno logy 1Ke yw o rds :floating po int m ulti p lier ;Boo th algo rithm ;W allace trees ;w ave si m ulati on收稿日期:20050813 随着计算机和信息技术的快速发展,人们对微处理器的性能要求越来越高。

邮电大学毕业设计(论文)题目:32位低功耗浮点乘法器设计学院:电子工程学院专业:集成电路设计与集成设计班级:电路1303学生:白进宝学号:05136073导师:邢立冬职称:高级工程师起止时间:2017年3月6日至2017年6月11日毕业设计(论文)声明书本人所提交的毕业论文《32位低功耗浮点乘法器设计》是本人在指导教师指导下独立研究、写作的成果,论文中所引用他人的文献、数据、图件、资料均已明确标注;对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式注明并表示感。

本人完全理解《邮电大学本科毕业设计(论文)管理办法》的各项规定并自愿遵守。

本人深知本声明书的法律责任,违规后果由本人承担。

论文作者签名:日期:年月日邮电大学本科毕业设计(论文)开题报告邮电大学毕业设计(论文)成绩评定表摘要乘法器是高性能数字信号处理芯片的关键部件,也是实时、高速数字信号处理器的核心。

乘法单元具有面积大、延时长、结构复杂的特点,如何设计出高速、低功耗、结构简单的乘法单元是近些年来的一大难题。

本文比较各种乘法器设计的算法与结构,分析它们的面积、速度与功耗。

最终找出最优的设计方案,完成32位浮点乘法器的电路设计。

本文首先介绍IEEE-754浮点数标准和浮点操作,对IEEE-754浮点运算标准的浮点表示格式、精度、围、规格化进行分析,并对决定乘法器性能的实现算法与实现结构进行深入研究。

其中实现浮点乘法的重点是实现整数的乘法。

其主要实现途径有移位相加结构和华莱士树型结构。

移位相加乘法结构简单,但是延时较长;华莱士树型乘法延时较短,但是结构比较复杂。

为了进一步提高运算速度,将乘法器改为流水线结构,达到时间上的并行。

最后应用低功耗设计方法对电路进行优化设计以降低系统功耗。

关键词:IEEE-754;乘法器;移位相加;华莱士树;流水线;低功耗ABSTRACTMultiplier is the key component of high performance digital signal processing chip, and also the core of real-time and high-speed digital signal processor. The multiplication unit has the characteristics of large area, long delay and complex structure. How to design a multiplication unit with high speed, low power consumption and simple structure is a difficult problem in recent years.In this paper, the algorithms and structures of various multipliers are compared, and their area, speed and power consumption are analyzed. Finally, the optimal design scheme is found, and the circuit design of 32 bit floating point multiplier is completed.This paper first introduces the IEEE-754 floating point standard and floating point operations on floating-point IEEE-754 floating-point standard expression analysis format, accuracy, scope, standard, and implementation of the decision performance of multiplier algorithm in-depth research and implementation of structure. Among them, the key point of floating point multiplication is to achieve the multiplication of integers. The main implementation methods include shift adding structure and Wallace tree structure. The shift addition and multiplication structure is simple, but the time delay is long; the Wallace tree type multiplication delay is shorter, but the structure is complex. In order to further improve the speed of operation, the multiplier is changed into pipelined structure to achieve parallel time. Finally, the low power design method is applied to optimize the circuit to reduce system power consumption.Key words: IEEE-754;Multiplier;Shift addition;Wallace tree;Assembly line;low power consumption目录第一章绪论 (1)1.1 研究意义 (1)1.2 研究的主要容 (1)1.3 论文结构安排 (2)第二章设计原理概述 (3)2.1 浮点数格式 (3)2.2 IEEE-754浮点数标准 (4)2.3 浮点乘法运算原理 (6)第三章浮点乘法器电路设计 (9)3.1 无符号数一位乘法 (9)3.2 超前进位加法器设计 (10)3.3 移位相加乘法结构 (12)3.4 华莱士树结构 (13)3.5 尾数的舍入与规格化 (21)3.6 阶码的处理 (23)3.7 符号位处理 (24)3.8 浮点乘法器总体结构 (25)3.9 流水线结构 (25)3.9.1 流水线技术简介 (25)3.9.2 流水线浮点乘法器设计 (26)3.10 低功耗设计 (26)3.10.1 低功耗设计背景 (26)3.10.2 低功耗设计方法 (27)3.10.3 浮点乘法器的低功耗设计 (29)3.11 本章小结 (30)第四章仿真验证与逻辑综合 (32)4.1 功能仿真 (32)4.1.1 尾数运算功能仿真 (32)4.1.2 浮点乘法器功能仿真 (33)4.1.3 流水线结构浮点乘法器功能仿真 (34)4.2 浮点乘法器逻辑综合 (35)4.3 浮点乘法器时序仿真 (36)4.4 功耗分析 (37)结束语 (39)致 (40)参考文献 (41)附录 (42)第一章绪论1.1 研究意义进入21世纪以,来大数据、互联网+、人工智能等新兴技术正在逐步进入到我们的生活当中。

集成电路产业是电子信息产业的核心对我国的经济政治和国防安全有着重大影响[1]。

为此我国把集成电路产业定为重点战略产业,制定了一系列的相关政策确保我国经济建和国防安全。

目前包括微处理器在的集成电路的发展一直严格遵循摩尔定律。

处理器中的浮点乘法单元是整个电路设计中需要着重考虑的对象。

在某些领域中需要很高精度的浮点运算,而功耗大、面积大是高精度浮点运算部件的固有特性[2]。

因此浮点乘法器性能的优劣关乎到信号处理的能力。

正因为高性能的浮点乘法器的广泛应用,故近几十年来其一直是研究的热点。

1.2 研究的主要容本论文的主要的研究容是设计出性能符合要求的32位低功耗浮点乘法器,要求在高可靠性的基础上,工作速度达到50MHz。

依据性能的要求,乘法器每次乘法运算的时间应在20ns以。

首先介绍浮点数标准及其运算,深入研究32位低功耗浮点乘法器设计当中的常见的电路结构和算法确定乘法单元的结构。

浮点乘法器的设计重点是尾数乘法器的设计,其性能优劣决定了整个设计是否能够达到要求[3]。

对比移位相乘结构和华莱士树结构的优劣,深入研究Wallace树形结构,在Wallace树形结构的基础上改进为流水线浮点乘法器。

由于近些年来移动设备的普及,本次浮点乘法器的设计适当加入了低功耗的容。

通过功能仿真来验证设计的原理是否正确。

再通过逻辑综合和时序仿真看其性能是否达到要求。

在满足性能的要求上,选取合理的设计结构和器件。

1.3 论文结构安排第一章绪论。

介绍论文研究的意义、研究的主要容、论文结构安排。

第二章设计原理概述。

主要介绍浮点数的表示格式,浮点数的规格化,IEEE-754浮点数标准,简要介绍浮点乘法运算的基本原理。

第三章浮点乘法器电路设计。

对实现尾数相乘运算的两种结构进行比较分析。

移位相加乘法结构是最简单的乘法算法结构,结构简单,便于设计,但是延时较长,只能在工作频率较低的系统中工作;华莱士树乘法结构利用并行计算的思想,能够极大的降低延时,但同时带来的是面积与功耗的增加。

最后介绍尾数的舍入与规格化、阶码的处理和符号位处理。

将浮点乘法器改为流水线结构进一步提高运算速度。

在功能正确的基础上适当加入低功耗设计容把系统的功耗降低。

第四章仿真验证与逻辑综合。

通过功能仿真、逻辑综合和时序仿真观察运算结果,分析性能是否达到要求。

第五章结论。

总结32位低功耗浮点乘法器的完成情况,并分析本次设计存在的问题为进一步研究提供方向。

第二章设计原理概述2.1 浮点数格式计算机中的浮点数是用一个定点的尾数再乘以一个基为2的阶数得到。

计算机部用定点数表示数值数据的围比浮点数小很多。

例如,对于n位带符号整数,其表示围为-2n-1~(2 n-1-1),运算结果很容易溢出,此外,用定点数也不能表示出大量的带有小数点的实数。

因此,计算机部会专门定义浮点数格式用以表示更大围的实数。

对于任意一个实数X,都可以表示为:(2-1) 其中,S取值为0或1,用来决定X的正负,通常情况下0表示正数,1表示负数;M是定点小数用来表示实数X的尾数;E是一个二进制定点整数,称为X的阶码或指数;R是基数,可以约定为2、4、8等。

要确定一个实数的值,只需要在约定的基数R下,确定符号S、尾数M和阶码E就可以了。

因此,浮点数格式只需要规定S、M和E各自所用的位数、编码方式和所在的位置,而基数R 与定点小数的位置一样,是默认的,不需要明显的表示出来。