Cadence16.6 下机械孔设置

- 格式:doc

- 大小:230.00 KB

- 文档页数:1

在电子工程中,过孔是一种非常重要的元件,在PCB(Printed Circuit Board,印制电路板)上起到了连接不同层次电路的作用。

而在设计和制造PCB的过程中,cadence高亮一种孔径的过孔是一个极为重要的步骤。

今天我们将从多个角度来深入探讨这个主题,以便更好地理解它的重要性和应用。

1. 过孔的作用和种类在PCB设计中,过孔可以分为通孔和盲孔,它们的作用是连接不同层次的电路。

通孔贯穿整个PCB板,连接不同的层,而盲孔只从一面到另一面,连接内部层次的电路。

而cadence高亮一种孔径的过孔,主要是为了在设计过程中突出某个特定孔径的过孔,便于后续的制造和检查。

2. Cadence高亮过孔的方法和工具在Cadence软件中,高亮一种孔径的过孔通常是通过设置钻孔层的显示属性来实现的。

在PCB设计过程中,设计师可以根据实际需求选择特定的过孔孔径,并通过Cadence软件来进行高亮处理。

这样做的好处是,在设计过程中能够更清晰地看到特定孔径的过孔,在后期的设计优化和制造检查中也能更方便地进行操作。

3. 过孔设计的考量因素在设计PCB过孔时,需要考虑很多因素,如电气特性、机械强度、制造成本等。

而高亮一种孔径的过孔,也需要考虑到这些因素。

在设置高亮时,需要确保选择的孔径是符合设计要求的,并且在制造和检查中能够清晰地显示出来。

这需要设计师对材料、制造工艺等方面有一定的了解和经验。

4. 个人观点和总结作为一名电子工程师,我深知过孔在PCB设计中的重要性。

而Cadence软件的高亮一种孔径的过孔功能,对于提高设计效率和准确性有着很大的帮助。

通过对这个功能的深入了解,我对PCB设计和制造有了更深入的认识,也使我的工作更加顺利和高效。

这种功能的应用能够带来更好的产品质量和用户体验。

通过以上内容的探讨,我们对cadence高亮一种孔径的过孔有了更深入的了解,也认识到了其在PCB设计和制造中的重要性。

希望本文的内容能够对大家有所帮助,也能够激发出更多关于PCB设计的讨论和研究。

Cadence_SPB16.5、16.6的安装、破解、打补丁图⽂教程SPB16.5/6基于pubkey1.30的安装及破解注意:我的电脑是win7旗舰版,破解成功,请关闭防⽕墙和杀毒软件,16.5和16.6均破解成功了⾸先,安装license manager,步骤如下:点击LicenseManager。

选择接受许可,点击Next选择LicenseManager安装⽬录,根据个⼈习惯修改吧。

选择要安装的模块,点击Next。

到这⾥要刹车,直接Cancel。

最后完成安装,点击Finish接下来,要安装Cadence的主要⼯具:Product Installation。

安装Product Installation,⼀路Next到下图。

注:选择customs和anyone who……选择安装⽬录,路径如上图所⽰,点击Next。

预览安装信息,不满意的点击Back修改,感觉ok的点击Next。

点击Install开始安装。

耐⼼等待。

⼀般安装到最后,出现要寻找firewall的允许项添加什么的,需要等很长⼀会,⼀开始以为软件装的不动了,不想⼀会⼜开始装了。

这⾥不⽤管,直接Next。

要查看产品信息了就在选中该项,不需要了直接点击Finsh,就完成了安装⼯作。

⼀、破解步骤。

1、在任务管理器中确认⼀下是否有这两个进程,有就结束掉,即cdsNameServer.exe和cdsMsgServer.exe,没有就算了。

说明:看来没有。

2、把安装⽬录下的SPB_16.5/tools/pspice⽬录下的orSimSetup.dll剪切出来找个地⽅先放着不理(待完成破解后再拷回原来的地⽅,如果不⽤仿真部分删掉也⽆所谓)。

按照这个说的做吧。

3、解压本⽂档第⼀页中的pubkey.rar⽂件,把pubkey、pubkey1.3.exe和lLicenseManagerPubkey.bat放到Cadence\LicenseManager⽬录下并运⾏LicenseManagerPubkey.bat。

1 原理图笔记 (1)2 PCB笔记 (6)1 :原理图画完处理:1:检查连接性(眼睛看)2 重新编号,tool--->anotate3 DRC检查, tool---->Design rules check4 tools--->create netlist--->allegro(破解的不完全,有时候需要自己创建一个allgero文件夹。

2:PCB完成后处理事项:1 看连接线是否都铺完,tools->quick reqorts->unconnected pinsshape dynamic stateshape no netshape islandsDRC2 tools-->database check3 display-->state(保证全为绿色)4丝印层显示准备(把需要生成丝印的东西提取到丝印层):(显示stack-up(选pin/via/drc)/geometry(选outline/assemble_top/bottom/pin_number)/manufacturing(选autosilk_top/bottom))先把所有电气层关掉,stach-up-->所有etch关掉略去:5 生成丝印层---->manufacture-->silkscreen-->layer(选both)/elements(选both)/classes and subclasses(把那些东西提取出来放到丝印层,改package geometry和reference designator为silk 其余为none-->执行silkscreen6:提取之后,调整丝印信息,例如器件编号位置。

7 添加文字说明:add-->text-->manufacturing-->autosilk_top-->点击要添加文字的位置,输入文字就可以了8 设置钻孔文件数据参数——>manufacture-->nc-->nc parameters-->点击closed就自动把参数文件放置到设置好的目录下。

第一章 User Interface本章的主要内容介绍allegro 操作接口,透过本章学习可以对Allegro 的工作接口有了大致的了解,同时也能体验出Allegro PCB Layout 时的强大功能。

A. 程序的启动点选除了以上Allegro 主程序,我们还会常用到以下几个常用工具:• Padstack DesignerPadstack Designer 的作用是建立和修改Pad ,具体会在下面章节中讲到。

• DB doctorDB doctor 的作用有三个:1.板子Data-base 的检查2.板子Data-base 的修复3.更新板子上的DRC支持的文件种类为: .brd .mcm .mdd .psm .dra .pad and . sav databases.B. Cadence SPB ToolsPCB Designer 在 V16.5 分成2个基本等级,用户可以根据自己的需求购买不同等级的Tool 及搭配的option (Onlyfor Allegro),主要功能差别见下表:在开启 Allegro 时,系统会先跳出如下图的对话框,让您选取要使用的软件等级。

123窗口中所列出的软件项目是依据系统所能选取的 License 功能來决定 以下也列出几个常用的Option 来介绍:PCB High-Speed option :针对高速设计能提供更多的功能 Miniaturization option :针对HDI 设计能提供更多的功能如果在使用过程中想更改产品,可以在点选下拉菜单File 项目下面的Change Edit ,就会出现如上图所示的对话框时,选择所需产品。

C. Allegro 常用档类型的介绍D. Allegro的目录结构Allegro的文件目录可以分为三部分:安装路径、工作路径和用户环境路径。

安装路径:系统默认的安装路径为:C:\Cadence\SPB_16.6,在安装时使用者可以根据自己随意更改安装路径。

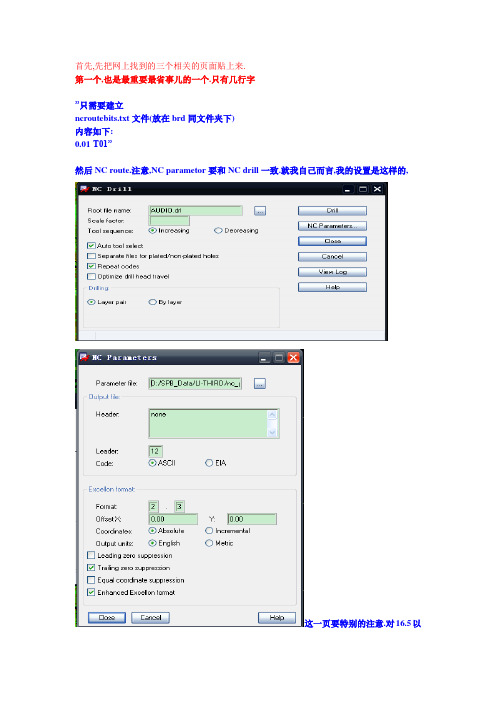

首先,先把网上找到的三个相关的页面贴上来.第一个,也是最重要最省事儿的一个.只有几行字”只需要建立ncroutebits.txt文件(放在brd同文件夹下)内容如下:0.01T01”然后NC route.注意,NC parametor要和NC drill一致.就我自己而言,我的设置是这样的,这一页要特别的注意.对16.5以前的版本的庆,在OffsetX里要写上MANUFACTURING->PHOTOPLOT_OUTLINE框的左下标的反相值.但是16.5里修正了这一点.所以16.5里不用填.还有一点.打开*.rou文件,把里边的以”;”(分号)开头的那几行注释删除掉.不然在导入CAM 的时候会报错.另16.5生成的artwork导入CAM时可能TOP.BOTTOM会变成多层的.这时要设置一下CAM350,方法如下:File->Setup->Photoplotter, RS274X 点击setup option, convert composite to single layer打钩第二个(此页不知为何无图.)Allegro椭圆孔攻略以下内容多是网上各位大侠的总结,再加自己的些许实践,如有不当之处还望指出。

candence版本16.3,据说candence在15.2已经支持椭圆孔和方形孔。

在candence的pad designer工具中,可以自动生成椭圆孔和方形孔。

很多大侠都是先做热风焊盘再做孔。

由于本人用的机械孔省去此步。

过程如下1. 制作椭圆孔< xmlnamespace prefix ="v" ns ="urn:schemas-microsoft-com:vml" />2. Allegro中导出椭圆孔1> 首先,要在板子上画一个route path的边框(台湾映阳公司的allegro资料中没有此步操作,本人做了简单测试,其效果图如下)。

CadenceAllegro16.6⽣成Gerber步骤⼀,⽣成钻孔⽂件1,maufacture-nc-nc parameters 按默认设置,output units ,如果是使⽤mils,就选english,如果是cm就选择metrix,点击close后⽣成nc_param.txt2.执⾏Manufacture→NC→NCDrill,如果有盲孔或埋孔,则Drilling中选择ByLayer,否则默认,点Drill⽣成*.drl⽂件,点击Viewlog可以查看⽇志信息。

3.不规则孔的钻孔⽂件⽣成:执⾏Manufacture→NC→NCRoute,默认设置,点击Route⽣成*.rou⽂件,点击Viewlog可以查看⽇志信息。

4.钻孔表及钻孔图的⽣成:执⾏Manufacture→NC→DrillLegend,如果有盲孔或埋孔,则Drilling中选择ByLayer,否则默认(单位为mil),点击OK⽣成*.dlt⽂件。

此时跟随⿏标会⽣成⼀个表格,将它放在PCB旁边;⼆,⽣成gerber⽂件1.设置Gerber⽂件参数2.切换到FilmControl选项卡,设置要输出的Gerber⽂件。

3.设置每个Gerber层的参数逐个选中每个Gerber,设置未定义线宽为6mil(0.1524mm),两层板输出都为正⽚Positive(多层板如果在层叠结构中若电源地设置了负⽚则对应层设置输出负⽚Negative),点击Selectall,选中所有要输出的Gerber层,再勾选Checkdatabasebeforeartwork选项,最后点击CreateArtwork,输出Gerber⽂件。

4.最终⽣成的Gerber⽂件在PCB⼯程⽂件夹⾥的gerber⽂件夹中Allegro中为Gerber⽂件设置独⽴的⽂件夹在Allegro软件中,⽣成的Gerber⽂件,数量较多,⽽且都保存在和PCB⼀样的⽂件夹中,不⼩⼼就会造成漏选、错选,很不⽅便。

在Cadence软件中,过孔参数主要包括以下几个方面:

1. 过孔类型:根据实际需求选择不同的过孔类型,如盲埋孔、通孔等。

2. 过孔大小:根据设计需求和线宽线距规则设置过孔的大小,一般为8/8mil、6/6mil、4/4mil等。

3. 过孔间距:根据设计需求和线宽线距规则设置过孔的间距,包括线到孔、线到线、线到焊盘、线到过孔、孔到盘等元素之间的间距。

4. 过孔高度和深度:根据实际需求设置过孔的高度和深度,以满足不同设计要求。

5. 金属层和导电层:根据实际需求选择过孔的金属层和导电层,以满足信号传输和电流导通的要求。

6. 阻焊层和焊盘:根据实际需求设置过孔的阻焊层和焊盘,以满足焊接和电路板制作的要求。

在Cadence软件中,可以通过PCB Editor等工具进行过孔参数的设置和调整,以满足不同设计需求。

同时,还需要注意过孔的电气性能和可靠性等方面的问题,以确保设计的可靠性和稳定性。

前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。

目录:一、基本约束规则设置 1、线间距设置2、线宽设置3、设置过孔4、区域约束规则设置5、设置阻抗6、设置走线的长度范围置详解(图文并茂)则设约束规.616o r g Alle (为了不侵犯别人的成果,所以在这里做了特殊说明,以示敬意)首先感谢詹书庭编写这篇文章,为我们学习交流Cadence allegro 苦用心!俗话说的好,社会在发展,技术在进步,技术的进步在于不断的学习交流和实践。

所以为了方便大家学习交流,为大家提供一个良好 QQ )!学习交流 Cadence allegro 请加QQ 群:一起来学AllegRo 【2】.群号:331730476 .以下是正文这篇文章写得很好,操作步骤详细,截图一目了然,通俗易懂,唯一的缺点就是部分截图不是很清晰,我对个别图片做了调整和替换,不易替换的不清晰图片,仔细看下也能明白其中的意思。

此文章由丹心静居整理---2014.10.13 加入。

对原文作者表示歉意的交流平台,在这里留下我们的群原文作者的群拒绝任何人(QQ 软件提供了丰富的知识和方法。

请大家认真学习,不要辜负作者的良2014-10-13 第 1 页,共 83 页二、高级约束规则设置11、单个网络长度约束12、a+b 类长度约束 13、a+b-c 类长度约束14、a+b-c 在最大和最小传播延迟中的应用y a l e D n i P 、10约束分差设置、.29分对差创建、.19设置则分规差、 9属性用置通设、 8等长型T 、.37等长NET X 阻的过电、.27等长NET 阻的电不过、.17置等长设、 71、线间距设置(1)、设置默认间距规则点击CM图标,如下图所示,打开约束管理器。

单击Spacing,再点击All Layers,如下图所示。

右边有一个DEFAULT就是默认规则,我们可以修改其值。

入一个值,这样就都修改了,如下图所示点选Default按鼠标右键,执行Create-Spacing CSet加入新规则。