实验4 扫描显示驱动电路

- 格式:doc

- 大小:85.50 KB

- 文档页数:5

内蒙古工业大学信息工程学院实验报告课程名称: CPLD/FPGA应用开发技术实验名称:扫描驱动显示电路设计实验类型:验证性□ 综合性□设计性■实验室名称:班级:学号:姓名:组别:同组人:成绩:实验日期: 2012-5-9月日预习报告一、实验目的:1.了解实验箱中8位七段数码管显示模块的工作原理。

2.熟悉VHDL 硬件描述语言及设计专用数字集成电路的自顶向下的设计思想。

3.掌握利用CPLD/FPGA设计8位七段数码管扫描显示驱动电路的方法。

二、实验设备:1.计算机(配置为:P4 CPU 128M内存);2. MAX+plusⅡ开发工具软件;3. EL教学实验箱;4.万用表;5. DS 5022M型双踪数字示波器;三、实验内容:本实验要求在给定子模块程序的基础上,画出设计原理图。

自行编写顶层模块程序,完成扫描显示驱动电路的设计,实现在8个数码管上轮流显示字符0-F的功能。

四、设计要求1.要求在Max+plusⅡ平台上用VHDL语言编写顶层模块程序,调试、仿真成功后,下载至ALTER EPM7128SLC84-15 芯片,再利用外接电路实现以上设计功能。

2.扫描驱动显示电路有 2 个输入端(clk,reset),14 个输出端(a,b,c,d,e,f,g)和(y0,y1,y2,y3,y4,y5,y6,y7),全部为TTL 电平,管脚分配任意,如下图所示。

3.根据芯片特点,管脚分配时将时钟信号分配给83 脚,复位信号分配给1 脚,使能信号分配给84 脚。

月日实验报告一、实验内容:本实验要求在给定子模块程序的基础上,画出设计原理图。

自行编写顶层模块程序,完成扫描显示驱动电路的设计,实现在8 个数码管上轮流显示字符0-F 的功能。

二、实验程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY XS ISPORT(CLK,RESET: IN STD_LOGIC;A,B,C,D,E,F,G: OUT STD_LOGIC;Y: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END XS;ARCHITECTURE BEHA OF XS ISCOMPONENT COUNTER16PORT(CLK,CLR: IN STD_LOGIC;COUNT: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;COMPONENT DECDISPPORT(DATAIN: IN STD_LOGIC_VECTOR(3 DOWNTO 0);A,B,C,D,E,F,G: OUT STD_LOGIC);END COMPONENT;COMPONENT YIMA3PORT(X: IN STD_LOGIC_VECTOR(2 DOWNTO 0);Y: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END COMPONENT;SIGNAL CONT: STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL SEL3: STD_LOGIC_VECTOR(2 DOWNTO 0);BEGIND1:COUNTER16 PORT MAP(CLK=>CLK,CLR=>RESET,COUNT=>CONT);D2:DECDISP PORT MAP(DATAIN=>CONT,A=>A,B=>B,C=>C,D=>D,E=>E,F=>F,G=>G);D3:YIMA3 PORT MAP(X=>CONT(2 DOWNTO 0),Y=>Y);END BEHA;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY YIMA3 ISPORT( X: IN STD_LOGIC_VECTOR(2 DOWNTO 0);Y: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END YIMA3 ;ARCHITECTURE BEHA OF YIMA3 ISBEGINY<=X;END BEHA;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DECDISP ISPORT(DATAIN: IN STD_LOGIC_VECTOR(3 DOWNTO 0);A,B,C,D,E,F,G: OUT STD_LOGIC);END DECDISP;ARCHITECTURE BEHA OF DECDISP ISSIGNAL DATAOUT: STD_LOGIC_VECTOR(6 DOWNTO 0);BEGINA<=DATAOUT(6);B<=DATAOUT(5);C<=DATAOUT(4);D<=DATAOUT(3);E<=DATAOUT(2);F<=DATAOUT(1);G<=DATAOUT(0);PROCESS(DATAIN)BEGINCASE DATAIN ISWHEN "0000"=> DATAOUT<="1111110"; WHEN "0001"=> DATAOUT<="0110000"; WHEN "0010"=> DATAOUT<="1101101"; WHEN "0011"=> DATAOUT<="1111001"; WHEN "0100"=> DATAOUT<="0110011"; WHEN "0101"=> DATAOUT<="1011011"; WHEN "0110"=> DATAOUT<="1011111"; WHEN "0111"=> DATAOUT<="1110000"; WHEN "1000"=> DATAOUT<="1111111"; WHEN "1001"=> DATAOUT<="1111011"; WHEN "1010"=> DATAOUT<="1110111"; WHEN "1011"=> DATAOUT<="0011111"; WHEN "1100"=> DATAOUT<="1001110"; WHEN "1101"=> DATAOUT<="0111101"; WHEN "1110"=> DATAOUT<="1001111"; WHEN "1111"=> DATAOUT<="1000111"; WHEN OTHERS=> DATAOUT<="XXXXXXX"; END CASE;END PROCESS;END BEHA;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY COUNTER16 ISPORT(CLK,CLR: IN STD_LOGIC;COUNT: OUT STD_LOGIC_VECTOR(3 DOWNTO 0); SEL: OUT STD_LOGIC_VECTOR(2 DOWNTO 0)); END COUNTER16;ARCHITECTURE BEHA OF COUNTER16 ISSIGNAL CNT: STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINPROCESS(CLK,CLR)BEGINIF CLR='0'THENCNT<="0000";ELSIF CLK='1' AND CLK'EVENT THENCNT<=CNT+'1';END IF;COUNT<=CNT;SEL<=CNT(2 DOWNTO 0);END PROCESS;三、仿真结果:四、管脚分配:。

实验一 maxplusII 软件的初步使用(图形的设计)一、实验目的:1、初步掌握Max+PlusII 软件的基本操作与应用。

2、初步了解可编程器件的设计全过程。

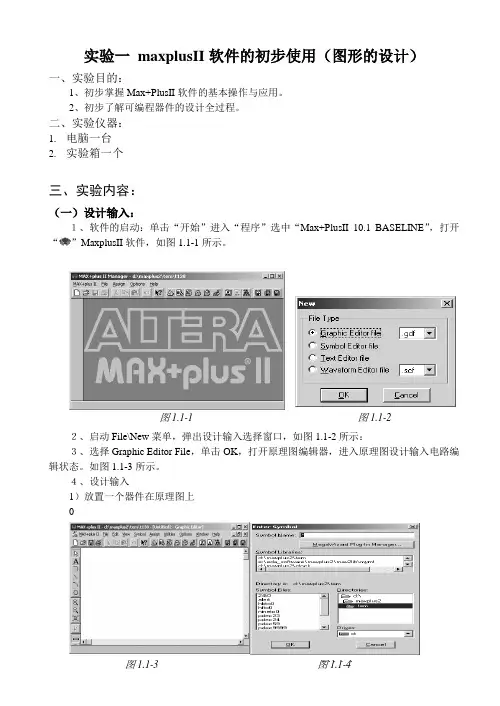

二、实验仪器: 1. 电脑一台 2. 实验箱一个三、实验内容:(一)设计输入:1、软件的启动:单击“开始”进入“程序”选中“Max+PlusII 10.1 BASELINE ”,打开“”MaxplusII 软件,如图1.1-1所示。

2、启动File\New 菜单,弹出设计输入选择窗口,如图1.1-2所示:3、选择Graphic Editor File ,单击OK ,打开原理图编辑器,进入原理图设计输入电路编辑状态。

如图1.1-3所示。

4、设计输入1)放置一个器件在原理图上 01.1-4图1.1-1图1.1-2图1.1-3 图1.1-4b 、在光标处输入元件名称(如:input ,output ,and2,and3,nand2,or2,not ,xor ,dff 等)或用鼠标点击库元件,按下OK 即可。

c 、如果安放相同的元件,只要按住Ctrl 键,同时用鼠标按左键拖动该元件复制即可。

d 、一个完整的电路包括:输入端口input 、电路元件集合、输出端口output 。

e 、图1.1-5为3-8译码器元件安放结果。

2)添加连线到器件的引脚上:把鼠标移到元件引脚附近,则鼠标自动由箭头变为十字,按住鼠标左键拖动,即可画出连线。

3-8译码器原理图连线后如图1.1-6所示。

3)标记输入/输出端口属性分别双击输入端口的“PINNAME ”,当变成黑色时,即可输入标记符并回车确认;输出端口标记方法类似。

本译码器的三输入端分别标记为:A 、B 、C ;其八输出端分别为:D0、D1、D2、D3、D4、D5、D6、D7。

如图1.1-7所示。

4)保存原理图单击保存按钮图表,对于新建文件,出现类似文件管理器图框,请选择保存路径/文件名称保存原理图,原理图的扩展名为.gdf ,本实验中取名为test1.gdf 。

实验二:计数器动态扫描实验一实验目的熟悉译码扫描动态显示的工作原理、设计过程和实现方法。

二实验内容与要求学习用VHDL设计译码扫描动态显示电路,完成编译、综合、适配、仿真和实验箱上的硬件测试。

三实验平台(1)硬件:计算机、GX-SOC/SOPC-DEVLABCycloneII EP2C35F672C8核心扳(2)软件:Quartus II四实验原理通过动态扫描一组4BIT 的输入,有控制开关控制数据的流向,即在哪个数码管上显示,在允许的条件产生后,扫描记录响应位置上的输入数据(开关选择),将结果动态地显示在共阴数码管上。

在能满足人眼要求的一定的扫描频率下,对数据进行动态显示。

五程序--显示电路--显示电路整合--ledscan.vhd 4 digit bcd-to-7 segment scan displaylibrary ieee ;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity ledscan isport(clk : in std_logic; --synchronousenable : in std_logic; --scan clockdata_bcd :in std_logic_vector(3 downto 0);--input bcdctrl : in std_logic_vector(2 downto 0);---ctrl the order of inputi.e. bcd_dataledseg : out std_logic_vector(6 downto 0);--output to 7 segmentledcom : out std_logic_vector(5 downto 0));--7 segment enableend ledscan;architecture behavior of ledscan issignal com_clk : std_logic_vector(2 downto 0);signal bcd_led : std_logic_vector(3 downto 0);signal data2show : std_logic_vector(23 downto 0);component comcounport(clk : in std_logic;--synchronouse clockenable : in std_logic;--scan clockcomclk : out std_logic_vector(2 downto 0));--output count end component;component com_encodeport(com_clk : in std_logic_vector(2 downto 0);--input countledcom : out std_logic_vector(5 downto 0));--output encodeend component;component bcd_muxport(com_clk : in std_logic_vector(2 downto 0);--input countbcd_data : in std_logic_vector(23 downto 0);--input display databcd_led : out std_logic_vector(3 downto 0));--output to 7 segment end component;component bcd_7segport(bcd_led : in std_logic_vector(3 downto 0);--input bcdledseg : out std_logic_vector(6 downto 0));--output to 7 segment end component;begininput_control:process(clk)beginif (clk'event and clk='1') thenif ctrl="000" thendata2show(3 downto 0)<=data_bcd;-- first value to showelsif ctrl="001" thendata2show(7 downto 4)<=data_bcd;-- 2nd value to showelsif ctrl="010" thendata2show(11 downto 8)<=data_bcd;-- 3rd value to showelsif ctrl="011" thendata2show(15 downto 12)<=data_bcd;-- 4th value to showelsif ctrl="100" thendata2show(19 downto 16)<=data_bcd;-- 5th value to showelsif ctrl="101" thendata2show(23 downto 20)<=data_bcd;-- 6th value to showelsedata2show<="000000000000000000000000";end if;end if;end process ;u0: comcoun port map (clk=>clk,enable=>enable,comclk=>com_clk);-- 7 segment com scan counteru1: com_encode port map(com_clk=>com_clk,ledcom=>ledcom);-- 7 segment com scan counter--u1: com_encode port map (com_clk,ledcom); --7 segment com encode u2: bcd_mux port map (com_clk=>com_clk,bcd_data=>data2show,bcd_led=>bcd_led);--multiplexeru3: bcd_7seg port map (bcd_led=>bcd_led,ledseg=>ledseg); --bcd to7 segment encoderend behavior;--七段显示扫描电路--comcoun.vhd 7 segment com scan counterlibrary ieee ;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity comcoun isport(clk : in std_logic;--synchronouse clockenable : in std_logic;--scan clockcomclk : out std_logic_vector(2 downto 0));--output countend comcoun;architecture behavior of comcoun issignal q : std_logic_vector(2 downto 0);--internal counted signal beginfscan:process(clk)beginif (clk'event and clk='1') thenif (enable='1') thenif q>=6 thenq<="000";--initial counterelseq<=q+1;--countingend if;end if;end if;end process fscan;comclk<=q; --output internal countend behavior;--计数译码电路 -- 6 共阴--com_encode.vhd 7 segment com encoderlibrary ieee ;use ieee.std_logic_1164.all;entity com_encode isport(com_clk :in std_logic_vector(2 downto 0);--input countledcom :out std_logic_vector(5 downto 0));--output encodeend com_encode;architecture behavior of com_encode isbeginledcom<="000001" when com_clk="001" else"000010" when com_clk="010" else"000100" when com_clk="011" else"001000"when com_clk="100" else"010000"when com_clk="101" else"100000";end behavior;--bcd_mux.vhd multiplexer of bcd-selectionlibrary ieee ;use ieee.std_logic_1164.all;entity bcd_mux isport(com_clk : in std_logic_vector(2 downto 0);--input countbcd_data :in std_logic_vector(23 downto 0);--input display data bcd_led : out std_logic_vector(3 downto 0));--output to 7 segment end bcd_mux;architecture behavior of bcd_mux isbeginbcd_led<=bcd_data(3 downto 0) when com_clk="001" elsebcd_data(7 downto 4) when com_clk="010" elsebcd_data(11 downto 8) when com_clk="011" elsebcd_data(15 downto 12)when com_clk="100" elsebcd_data(19 downto 16)when com_clk="101" elsebcd_data(23 downto 20)when com_clk="110" else"----";end behavior;--bcd对应七段显示器编码电路--bcd_7seg.vhd bcd to 7 segment encoderlibrary ieee ;use ieee.std_logic_1164.all;entity bcd_7seg isport(bcd_led :in std_logic_vector(3 downto 0);--input bcdledseg : out std_logic_vector(6 downto 0));--output to 7 segment end bcd_7seg;architecture behavior of bcd_7seg isbeginwith bcd_led selectledseg<="0111111" when "0000",--0"0000110" when "0001",--1"1011011" when "0010",--2"1001111" when "0011",--3"1100110" when "0100",--4"1101101" when "0101",--5"1111101" when "0110",--6"0100111" when "0111",--7"1111111" when "1000",--8"1101111" when "1001",--9"1110111" when "1010",--A"1111100"when "1011",--b"0111001"when "1100",--c"1011110" when "1101",--d"1111001"when "1110",--E"1110001" when "1111",--F"0000000" when others;end behavior;六引脚定义及代码图2-1引脚定义代码:# Copyright (C) 1991-2008 Altera Corporation# Your use of Altera Corporation's design tools, logic functions # and other software and tools, and its AMPP partner logic# functions, and any output files from any of the foregoing# (including device programming or simulation files), and any# associated documentation or information are expressly subject # to the terms and conditions of the Altera Program License# Subscription Agreement, Altera MegaCore Function License# Agreement, or other applicable license agreement, including,# without limitation, that your use is for the sole purpose of# programming logic devices manufactured by Altera and sold by# Altera or its authorized distributors. Please refer to the# applicable agreement for further details.# Quartus II: Generate Tcl File for Project# File: ACOUNT10.tcl# Generated on: Tue Nov 03 11:40:42 2009# Load Quartus II Tcl Project packagepackage require ::quartus::projectset need_to_close_project 0set make_assignments 1# Check that the right project is openif {[is_project_open]} {if {[string compare $quartus(project) "ACOUNT10"]} {puts "Project ACOUNT10 is not open"set make_assignments 0}} else {# Only open if not already openif {[project_exists ACOUNT10]} {project_open -revision ACOUNT10 ACOUNT10} else {project_new -revision ACOUNT10 ACOUNT10}set need_to_close_project 1}# Make assignmentsif {$make_assignments} {set_global_assignment -name FAMILY "Cyclone II"set_global_assignment -name DEVICE EP2C35F672C8set_global_assignment -name ORIGINAL_QUARTUS_VERSION 8.0set_global_assignment -name PROJECT_CREATION_TIME_DATE "11:03:58 NOVEMBER 03, 2009"set_global_assignment -name LAST_QUARTUS_VERSION 8.0set_global_assignment -name USE_GENERATED_PHYSICAL_CONSTRAINTS OFF -section_id eda_palaceset_global_assignment -name DEVICE_FILTER_PACKAGE FBGAset_global_assignment -name DEVICE_FILTER_PIN_COUNT 672set_global_assignment -name DEVICE_FILTER_SPEED_GRADE 8set_global_assignment -name MIN_CORE_JUNCTION_TEMP 0set_global_assignment -name MAX_CORE_JUNCTION_TEMP 85set_global_assignment -name VHDL_FILE com_encode.vhdset_global_assignment -name PARTITION_NETLIST_TYPE SOURCE -section_id Topset_global_assignment -name PARTITION_COLOR 14622752 -section_id Top set_global_assignment -name LL_ROOT_REGION ON -section_id "Root Region"set_global_assignment -name LL_MEMBER_STATE LOCKED -section_id "Root Region"set_global_assignment -name VHDL_FILE comcoun.vhdset_global_assignment -name VHDL_FILE COUNT10a.vhdset_global_assignment -name VHDL_FILE bcd_7seg.vhdset_global_assignment -name VHDL_FILE clkgen.vhdset_global_assignment -name VHDL_FILE ACOUNT10.vhdset_global_assignment -name VECTOR_WAVEFORM_FILE warefare.vwfset_global_assignment -name INCREMENTAL_VECTOR_INPUT_SOURCE warefare.vwfset_instance_assignment -name PARTITION_HIERARCHY root_partition -to | -section_id Topset_location_assignment PIN_P25 -to clkset_location_assignment PIN_F6 -to Clrset_location_assignment PIN_B22 -to enset_location_assignment PIN_H23 -to LEDCOM[5]set_location_assignment PIN_G26 -to LEDCOM[4]set_location_assignment PIN_G25 -to LEDCOM[3]set_location_assignment PIN_G24 -to LEDCOM[2]set_location_assignment PIN_G23 -to LEDCOM[1]set_location_assignment PIN_P18 -to LEDCOM[0]set_location_assignment PIN_F26 -to LEDSEG[6]set_location_assignment PIN_F25 -to LEDSEG[5]set_location_assignment PIN_J20 -to LEDSEG[4]set_location_assignment PIN_J21 -to LEDSEG[3]set_location_assignment PIN_F23 -to LEDSEG[2]set_location_assignment PIN_F24 -to LEDSEG[1]set_location_assignment PIN_E25 -to LEDSEG[0]set_location_assignment PIN_B21 -to EN6# Commit assignmentsexport_assignments# Close projectif {$need_to_close_project} {project_close}}七仿真图2-2 创建VHDL文件图2-3 PIN口设置图2-4 创建VERILOG文件图2-5 运行八导入程序图2-7 下载图2-8 实验结果。

4led 动态扫描显示及按键实验感想

在完成4LED动态扫描显示及按键实验后,我深深感受到了科技的实际应用与电路设计的美妙结合。

这不仅是一次对于理论知识的学习和巩固,更是一次将知识转化为实践的宝贵体验。

实验中,我们通过编程控制4个LED灯的亮灭,使其按照特定的模式进行动态扫描。

这其中涉及到了数字信号处理、逻辑门电路、微控制器等多个知识点。

每一个LED灯的亮与灭,都代表着一串代码的执行,每一次的动态扫描,都是程序在控制板上跑动的轨迹。

在实验过程中,我深刻体会到了编程的魅力。

通过编写程序,我可以精确地控制每一个LED灯的亮灭时间,甚至可以创造出复杂的扫描效果。

而按键的部分更是增添了实验的趣味性。

通过按键,我可以随时改变LED的扫描模式,每一次按键,都像是给程序注入了一个新的灵魂,使其焕发出不同的光彩。

当然,实验过程中也遇到了不少困难。

例如,如何确保4个LED 灯能够均匀地亮起与熄灭,如何处理按键抖动问题等。

但正是这些问题的存在,使得整个实验更加具有挑战性。

通过不断地尝试、调试,我最终克服了这些困难,也更加深入地理解了相关知识。

这次实验让我认识到,理论知识的学习固然重要,但只有将其应用于实践中,才能真正体会到知识的价值。

同时,实验中的每一个细节、每一个问题,都是对自身能力的锻炼与提升。

通过不断地实践与

尝试,我相信自己能够更好地掌握知识,更好地将理论知识与实践相结合。

未来,我计划进一步深入学习微控制器编程、电路设计等相关知识,希望能够为未来的科技应用做出更大的贡献。

同时,我也希望能够将这次实验的经验分享给更多的同学,共同探索科技的奥秘。

实验四数码管扫描显示控制器设计与实现2011211208班2011211055 4 于圣泽一、实验目的1.掌握VHDL语言的语法规范, 掌握时序电路描述方法;2.掌握多个数码管动态扫描显示的原理及设计方法。

二、实验原理三、多个数码管动态扫描显示, 是将所有数码管的相同段并联在一起, 通过选通信号分时控制各个数码管的公共端, 循环依次点亮多个数码管, 利用人眼的视觉暂留现象, 只要扫描的频率大于50Hz, 将看不到闪烁现象。

一个数码管要稳定显示要求显示频率大于50Hz, 那么6个数码管则需要50×6=300Hz以上才能看到持续稳定点亮的现象。

四、cat1~cat6是数码管选通控制信号, 分别对应于6个共阴极数码管的公共端, 当catn=‘0’时, 其对应的数码管被点亮。

因此, 通过控制cat1~cat6, 就可以控制6个数码管循环依次点亮。

五、实验内容1.用VHDL语言设计并实现六个数码管串行扫描电路, 要求同时显示0、1.2.3.4.5这6个不同的数字图形到6个数码管上, 仿真验证其功能, 并下载到实验板测试。

2.用VHDL语言设计并实现六个数码管滚动显示电路六、循环左滚动, 始终点亮6个数码管, 左出右进。

状态为: 012345→123450→234501→3450123→450123→501234→012345七、向左滚动, 用全灭的数码管填充右边, 直至全部变灭, 然后再依次从右边一个一个地点亮。

状态为:012345→12345X→2345XX→345XXX→45XXXX→5XXXXX→XXXXXX→XXXXX0→XXXX01→XXX012→XX0123→X01234→012345,其中‘X’表示数码管不显示。

八、设计思路和过程对50MHz时钟进行5000分频, 得到10kHZ时钟scanclk。

把scanclk作为6进制计数器的时钟, 对计数器的状态进行译码, 得到cat(5 downto 0)的选通脉冲。

4.2 扫描数码显示器实验4.2.1 实验目的1. 学习状态机的原理及使用VHDL语言设计的方法;2.学习复杂数学系统的设计方法;3.掌握动态扫描数码显示器的设计方法。

4.2.2 实验设备PC微机一台,TD-EDA试验箱一台,SOPC开发板一块。

4.2.3 实验内容状态机是一类很重要的时序电路,是许多数字电路的核心部件。

根据状态机的输出方式可以分为Mealy型和Moore型两种状态机。

输出与状态有关而与输入无关的状态机类型称为Moore型状态机。

输出与状态及输入皆有关系的状态机称为Mealy型状态机。

状态机通常包含:说明部分、主控时序进程、主控组合进程、辅助进程几个部分。

利用状态机进行设计的步骤如下:1.分析设计要求,列出状态机所有可能的状态,并对每一个状态进行状态编码;2.根据状态转移关系和输出函数画出状态转移图;3.由状态转移图,用状态机语句描述状态机。

是数码管动态扫描显示的方式主要是为了节省I/O管脚和内部逻辑资源,它利用人的视觉暂留现象,将6位数数码管分别循环选通,配合传送相应的要显示的数据,只要扫描的速度足够快,就可以使人的视觉感到好像是6位数码管的同时显示。

一般扫描频率使用1KHz 就可以了。

本实验设计一个可以使6位数码管动态刷新显示的扫描电路。

分析系统的要求可知此设计需要包括6进制计数器、BCD译码器、数据选择多路开关等多个小单元模块。

实验需要设计一个模块来为6个数码块提供要显示的数据,设计一个六位数123456从左向右移动的方式,直到最高一位移出最右边数码块后,最低位6再从最左面数码块移进,从而实现循环移动。

4.2.4 实验步骤1.运行QuartusⅡ软件,建立新工程,工程名称及顶层文件名称为SCANLED。

2.选择File→New菜单,创建图形设计文件,在图形编辑器界面中选择Block Tool工具按钮,分别新建DAT、MULX、BCD_LED子模块,完成模块的定义及模块之间的连接,完成如图4-2-1所示的数码扫描显示器顶层设计电路图。

多位L E D-显示器动态扫描驱动电路设计完整版《多位LED 显示器动态扫描驱动电路》报告(一)目的:1、了解多位LED 显示器动态扫描驱动电路的基本工作原理;2、完成多位LED 显示器动态扫描驱动电路设计并分析计算单元电路;3、绘制多位LED 显示器动态扫描驱动电路图,针对工作原理进行参数估算;4、电路功能的检测和调试;5、设计答辩,完成设计报告。

(二)结构图(三)电路总体功能概述该电路的功能是通过控制数据选择器输入端的高低电平来使四个LED显示器可以显示0-9任意一个数字,实现动态扫描功能。

由振荡电路,控制电路,四位四选一数据选择器,一位LED译码驱动电路和四位LED显示电路组成。

首先用555定时器构成频率为1000赫兹多谐振荡器产生脉冲信号,再将信号传输到74构成的二位二进制触发器,使该触发器输出00,01,10,11。

将触发器的两输出端分别接到数据选择器153的S1,S0,将四个输入D0或D1D2D3信号传输到LED显示电路,使LED显示不同数字,将触发器的两输出端接到138的A1,A0(A2接0),再将138的输出Y0,Y1,Y2,Y3接到四个LED的共阴极,控制LED的显示状态,把74ls153的输出端与cc4511的四个输入端相连,把LED显示器的a,b,c,d,e,f,g与cc4511的输出端相连,这样便可以通过555定时器产生的脉冲控制四个LED的显示顺序,同时调整153的输入端的高低电位,这样便实现了对四个LED的显示控制,可随意现实0至9的数字。

振荡电路由555定时器构成的多谐振荡电路组成,有振荡电路提供脉冲,振荡周期T=Tpl+Tph=R1*C*ln2+(R1+R2)*C*ln2=0.001s,则其振荡频率为1000Hz,多谐振荡器在接通电源后无需外接触发信号就可以产生矩形脉冲或方波。

控制电路是一片74LS74构成的两位二进制触发器,它接收到控制电路的振荡脉冲,产生00,01,10,11的输出信号。

实验-扫描显示驱动电路————————————————————————————————作者:————————————————————————————————日期:2实验4 扫描显示驱动电路一、实验目的了解教学系统中8位八段数码管显示模块的工作原理,设计标准扫描驱动电路模块,以备后面实验用。

二、硬件要求主芯片Altera EPM7128SLC84-15,时钟,8位八段数码管显示器,四位拨码开关。

三、实验内容用四位拨码开关产生8421BCD码,用CPLD分别产生字形编码电路和扫描驱动电路,然后进行仿真,观察波形,正确后编程下载实验测试。

1、编一个简单的从0~F轮换显示十六进制数的电路。

2、用计数器产生数码管扫描驱动信号,调节时钟频率,感受扫描的过程,并观察字符的亮度和显示刷新的效果。

7段数码管显示字符0~F,显示字符与7段数码管驱动线的对应关系如下:二进制数字符7段数码管(gfedcba)0000 0 0111111(3F)0001 1 0000110(06)0010 2 1011011(5B)0011 3 1001111(4F)0100 4 1100110(66)0101 5 1101101(6D)0110 6 1111101(7D)0111 7 0000111(07)1000 8 1111111(7F)1001 9 1101111(6F)1010 A 1110111(77)1011 B 1111100(7C)1100 C 0111001(39)1101 D 1011110(5E)1110 E 1111001(79)34 1111F 1110001(71)四、实验原理四位拨码开关提供8421BCD 码,经译码电路DECL7S 后连接8段数码管的字形显示驱动信号a,b,c,d,e,f,g 。

数码管扫描电路可通过片选地址SEL[2..0]控制。

由SEL[2..0]和a,b,c,d,e,f,g 决定了8位数码管中的那一位显示和显示什么字形。

电子设计自动化实验报告实验四译码扫描显示电路设计一、实验目的1.熟悉QuartusⅡ软件应用环境,了解实验流程。

2.编写简单的Verilog代码,并在QuartusⅡ中进行调试和验证,并在EDA6000中下载代码和验证。

3.用扫描方式驱动8x8显示点阵,显示预定的字符”A”。

二、实验原理本实验要实现8x8显示点阵的控制电路,采用扫描方式驱动,分为8条行线,和八条列线,其中列线经反向驱动后接显示点阵。

用一个三位2进制数进行计数,控制扫描的过程,时钟信号有效,计数加一,用case语句实现扫描行列的变换。

当某一列为高电平,此列选通,当相应行为高电平时,相交点的led灯点亮,动态扫描,由于视觉延迟最终显示设定的字符”A”。

三、实验内容1、实现8x8点阵扫描驱动的“ Verilog ”语言设计。

2、编程下载并在实验箱上进行验证四、实验步骤与结果1、新建Verilog工程项目,编写代码并保存至与模块名对应的项目文件夹。

2、编译程序,编译无误后,在【tools】里面选择RTL视图,观察电路结构。

3、将实验箱和PC合理连接起来。

打开EDA6000软件,设置好芯片类型为ACEX1K (EP1K30TC144-3),载入模式11。

4、根据EDA6000界面内管脚对应芯片的实际管脚在QUARTUSⅡ里面设定管脚号并检查无误。

5、将程序下载至FPGA试验箱内,并在EDA6000软件界面内进行验证测试。

程序源代码:module ymsm(CLK,row,col);input CLK; output [7:0]row,col;reg [7:0]row,col;reg [2:0]a;always @(posedge CLK) beginif(a<7) a=a+1;else a=0;case(a)3'b000:begin row=10000000;col=00100000;end3'b001:begin row=01000000;col=01010000;end3'b010:begin row=00100000;col=10001000;end3'b011:begin row=00010000;col=10001000;end3'b100:begin row=00001000;col=11111000;end3'b101:begin row=00000100;col=10001000;end3'b110:begin row=00000010;col=10001000;end3'b111:begin row=00000001;col=10001000;endendcaseendendmodule编译:选择processing---start compilation命令,开始编译。

实验7 4*4 键盘扫描控制器1.实验任务说明:设计并实现4*4 键盘扫描控制电路,判断哪个按键被按下,在数码管上显示键值,并通过蜂鸣器发出按键音。

要求:●键值采用16 进制编码,即16 个按键分别对应显示16 进制数0~F,按键对应关系如下:最上面一行从左至右依次为0~3,第二行从左至右依次为4~7,第三行从左至右依次为8~B,最下面一行从左至右依次为C~F,其中b、d 显示为小写,其他字母大写;●按键按下时显示当前键值并保持,直到下一按键被按下时更新显示;●只有按键被按下时蜂鸣器发出按键音,放开后蜂鸣器不发声。

●选做:每个按键对应不同的按键音。

●2.实验设计思路将本实验分为4个部分,分别是顶层,分频器(扫描时钟的分频器和为蜂鸣器提供频率的分频器),数码管译码电路,扫描信号发生电路。

顶层利用状态机实现,状态转移为s0->s1->s2->s3->s0,分别对应扫描到col[0->3->0]。

同时把row 信号转化为一个“时钟信号”clock_change,当有按键按下就输出1,没有则输出0。

并以这个时钟设计一个时序逻辑,当clock_change的上升沿到来才更新tempSegin(传递给数码管的输入信号)和choose(传递给蜂鸣器分频器的输入信号),输出sound信号时,将蜂鸣器输出的信号与clock_change信号相与,以达到按下一次键盘蜂鸣器发声,数码管显示的目的。

3.源程序:1)分频器扫描时钟的分频器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;entity divide is--divide the frequency to 1/ngeneric( n:natural:=200);port( clk: in std_logic;clk_out: out std_logic);end divide;architecture div_arch of divide is--temporary signalsignal temp: std_logic;beginprocess( clk )--count variable count from 0 to n/2-1--means every n/2 period reverse the clk variable count: integer range 0 to n/2-1;beginif (clk'event and clk='1') thenif( count = n/2-1) thentemp <= not temp;count := 0;elsecount := count + 1;end if;end if;end process;clk_out <= temp;end div_arch;为蜂鸣器提供频率的分频器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;entity divide_sound is--the origin clk is 50MHz--divide the frequency to 1/ngeneric( n0:natural:=4;n1:natural:=8;n2:natural:=12;n3:natural:=16;n4:natural:=20;n5:natural:=24;n6:natural:=28;n7:natural:=42;n8:natural:=46;n9:natural:=50;n10:natural:=54;n11:natural:=58;n12:natural:=62;n13:natural:=66;n14:natural:=70;n15:natural:=74);port( clk: in std_logic;choose: in integer range 0 to 15;sound_out: out std_logic);end divide_sound;architecture div_arch of divide_sound is --temporary signalsignal temp: std_logic;beginprocess( clk )--count variable count from 0 to n/2-1--means every n/2 period reverse the clk variable count: integer range 0 to 100;variable n:integer range 0 to 200;--count'max is over the n(max)/2 - 1begincase choose iswhen 0 =>n := n0;when 1 =>n := n1;when 2 =>n := n2;when 3 =>n := n3;when 4 =>n := n4;when 5 =>n := n5;when 6 =>n := n6;when 7 =>n := n7;when 8 =>n := n8;when 9 =>n := n9;when 10 =>n := n10;when 11 =>n := n11;when 12 =>n := n12;when 13 =>n := n13;when 14 =>n := n14;when 15 =>n := n15;when others => n:= n0;end case;if(clk'event and clk='1') thenif( count = n/2 - 1) thentemp <= not temp;count := 0;elsecount := count + 1;end if;end if;end process;sound_out <= temp;end div_arch;2)扫描信号发生电路LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;entity scan_seq is--produce the column scan signalport( clk,reset: in std_logic;col: out std_logic_vector(3 downto 0));end scan_seq;architecture arch of scan_seq isbeginprocess(clk)variable count: integer range 0 to 3;--M=4 counter,every count output the porper impulse beginif( reset ='1')thencount := 0;elsif( clk'event and clk='1' )thenif( count = 3)thencount := 0;elsecount := count +1;end if;end if;case count iswhen 0 => col<="1110";when 1 => col<="1101";when 2 => col<="1011";when 3 => col<="0111";end case;end process;end arch;3)数码管译码电路LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY seg7_1H IS --seg7 decoding PORT(a: IN STD_LOGIC_VECTOR(3 DOWNTO 0); --inputb: OUT STD_LOGIC_VECTOR(6 DOWNTO 0); --outputcat: OUT STD_LOGIC_VECTOR(7 DOWNTO 0) --selcect);END seg7_1H;ARCHITECTURE aa OF seg7_1H ISsignal temp: std_logic_vector(3 downto 0);BEGINprocess(a)beginCASE a IS --b6-0 -> abcdefg WHEN "0000" => b <= "1111110"; --0WHEN "0001" => b <= "0110000"; --1WHEN "0010" => b <= "1101101"; --2WHEN "0011" => b <= "1111001"; --3WHEN "0100" => b <= "0110011"; --4WHEN "0101" => b <= "1011011"; --5WHEN "0110" => b <= "1011111"; --6WHEN "0111" => b <= "1110000"; --7WHEN "1000" => b <= "1111111"; --8WHEN "1001" => b <= "1111011"; --9WHEN "1010" => b <= "1110111"; --AWHEN "1011" => b <= "0011111"; --bWHEN "1100" => b <= "1001110"; --CWHEN "1101" => b <= "0111101"; --dWHEN "1110" => b <= "1001111"; --EWHEN "1111" => b <= "1000111"; --FWHEN others => b <= "0000000"; --others END CASE;end process;cat <= "11111110";END aa;4)顶层LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;entity scanKeyboard is--scan the keyboard and display, sound at the same time port(clk,reset: in std_logic;row: in std_logic_vector(3 downto 0);col: out std_logic_vector(3 downto 0);sound: out std_logic;b: out std_logic_vector(6 downto 0);cat: out std_logic_vector(7 downto 0);seeclk: out std_logic);end scanKeyboard;architecture arch of scanKeyboard iscomponent divide_sound is--the origin clk is 50MHz--divide the frequency to 1/ngeneric( n0:natural:=4;n1:natural:=8;n2:natural:=12;n3:natural:=16;n4:natural:=20;n5:natural:=24;n6:natural:=28;n7:natural:=42;n8:natural:=46;n9:natural:=50;n10:natural:=54;n11:natural:=58;n12:natural:=62;n13:natural:=66;n14:natural:=70;n15:natural:=74);port( clk: in std_logic;choose: in integer range 0 to 15;sound_out: out std_logic);end component;component scan_seq is--produce the column scan signalport( clk,reset: in std_logic;col: out std_logic_vector(3 downto 0));end component;component seg7_1H IS --seg7 decoding PORT(a: IN STD_LOGIC_VECTOR(3 DOWNTO 0); --inputb: OUT STD_LOGIC_VECTOR(6 DOWNTO 0); --outputcat: OUT STD_LOGIC_VECTOR(7 DOWNTO 0) --selcect);END component;component divide is--divide the frequency to 1/ngeneric( n:natural:=200);port( clk: in std_logic;clk_out: out std_logic);end component;--clk_scan is the scan signal for column--tempSound is the output of the sound divider--tempSegin is the input of the seg7 translate part--clock_change is disgned to record the row's impulse appear--choose is the select of the keyboardsignal clk_scan: std_logic;signal tempSound:std_logic;signal tempSegin:std_logic_vector(3 downto 0);signal clock_change:std_logic;signal choose: integer range 0 to 15;type state is (s0,s1,s2,s3);signal presentstate, nextstate : state;beginu0:divide_sound port map(clk => clk,choose=>choose,sound_out=>tempSound);u1:divide port map(clk =>clk, clk_out=>clk_scan);u2:scan_seq port map(clk=>clk_scan,reset=>reset,col=>col);u3:seg7_1H port map(a=>tempSegin,b=>b,cat=>cat); --discrible the register for clk_scanp1_reg:process(clk_scan,reset)beginif(reset ='1')thenpresentstate<= s0;elsif( clk_scan'event and clk_scan='1' )thenpresentstate<= nextstate;end if;end process;--discrible the state for clk_scanp2_stateChange:process(presentstate)begincase presentstate iswhen s0 => nextstate<= s1;when s1 => nextstate<= s2;when s2 => nextstate<= s3;when s3 => nextstate<= s0;end case;end process;--discrible the outputp3_out:process(presentstate,row,clock_change)begin--behave synchronize with the clock_changeif( clock_change'event and clock_change = '1')then case presentstate is-- column[0]when s0 => case row iswhen "1110"=>choose <= 12;tempSegin <= "1100";when "1101"=>choose <= 8;tempSegin <= "1000";when "1011"=>choose <= 4;tempSegin <= "0100";when "0111"=>choose <= 0;tempSegin <= "0000";when others=>choose <= 0;tempSegin <= tempSegin;end case;-- column[1]when s1 => case row iswhen "1110"=>choose <= 13;tempSegin <= "1101";when "1101"=>choose <= 9;tempSegin <= "1001";when "1011"=>choose <= 5;tempSegin <= "0101";when "0111"=>choose <= 1;tempSegin <= "0001";when others =>choose <= 0;tempSegin <= tempSegin;end case;-- column[2]when s2 => case row iswhen "1110"=>choose <= 14;tempSegin <= "1110";when "1101"=>choose <= 10;tempSegin <= "1010";when "1011"=>choose <= 6;tempSegin <= "0110";when "0111"=>choose <= 2;tempSegin <= "0010";when others=>choose <= 0;tempSegin <= tempSegin;end case;-- column[3]when s3 => case row iswhen "1110"=>choose <= 15;tempSegin <= "1111";when "1101"=>choose <= 11;tempSegin <= "1011";when "1011"=>choose <= 7;tempSegin <= "0111";when "0111"=>choose <= 3;tempSegin <= "0011";when others=>choose <= 0;tempSegin <= tempSegin;end case;end case;end if;end process;--discrible clkchangep3_clkchange:process(row)beginif( row = "1111")thenclock_change <='0';elseclock_change<='1';end if;end process;--output the sound signalsound <= tempSound and clock_change;--to see the clock_change in waveformseeclk <= clock_change;end arch;4.仿真波形及分析1)分频器1(扫描时钟的分频器)图1-1分频器整体图1-2 分频器计数到99翻转(高翻低)图1-3 分频器计数到99翻转(低翻高)实际应采用分频比为,50k,现仿真时为方便仿真取为200分频,由图1-1可以看到整体分频的情况,由图1-2可以看到分频器在计数到99时由高电平翻为低电平,由图1-3可以看到分频器在计数到99时由低电平翻为高电平。

设计任务本实验要求在给定子模块程序的基础上,画出设计原理图。

自行编写顶层模块程序,完成扫描显示驱动电路的设计,实现在8 个数码管上轮流显示字符0-F 的功能。

library ieee;use ieee.std_logic_1164.all;entity disp isport(clk,reset: in std_logic;a,b,c,d,e,f,g: out std_logic;y: out std_logic_vector(2 downto 0));end disp;architecture beha of disp iscomponent counter16port(clk,clr: in std_logic;count: out std_logic_vector(3 downto 0));end component;component decdispport(datain: in std_logic_vector(3 downto 0);a,b,c,d,e,f,g: out std_logic);end component;component yima3port(x: in std_logic_vector(2 downto 0);y: out std_logic_vector(2 downto 0));end component;signal cont: std_logic_vector(3 downto 0);signal sel3: std_logic_vector(2 downto 0);begind1:counter16 port map(clk=>clk,clr=>reset,count=>cont);d2:decdisp port map(datain=>cont,a=>a,b=>b,c=>c,d=>d,e=>e,f=>f,g=>g);d3:yima3 port map(x=>cont(2 downto 0),y=>y);end beha;library ieee;use ieee.std_logic_1164.all;entity yima3 isport( x: in std_logic_vector(2 downto 0);y: out std_logic_vector(2 downto 0));end yima3 ;architecture beha of yima3 isbeginy<=x;end beha;library ieee;use ieee.std_logic_1164.all;entity decdisp isport(datain: in std_logic_vector(3 downto 0);a,b,c,d,e,f,g: out std_logic);end decdisp;architecture beha of decdisp issignal dataout: std_logic_vector(6 downto 0); begina<=dataout(6);b<=dataout(5);c<=dataout(4);d<=dataout(3);e<=dataout(2);f<=dataout(1);g<=dataout(0);process(datain)begincase datain iswhen "0000"=>dataout<="1111110";when "0001"=>dataout<="0110000";when "0010"=>dataout<="1101101";when "0011"=>dataout<="1111001";when "0100"=>dataout<="0110011";when "0101"=>dataout<="1011011";when "0110"=>dataout<="1011111";when "0111"=>dataout<="1110000";when "1000"=>dataout<="1111111";when "1001"=>dataout<="1111011";when "1010"=>dataout<="1110111";when "1011"=>dataout<="0011111";when "1100"=>dataout<="1001110";when "1101"=>dataout<="0111101";when "1110"=>dataout<="1001111";when "1111"=>dataout<="1000111";when others=>dataout<="XXXXXXX";end case;end process;end beha;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter16 isport(clk,clr: in std_logic;count: out std_logic_vector(3 downto 0);sel: out std_logic_vector(2 downto 0)); end counter16;architecture beha of counter16 issignal cnt: std_logic_vector(3 downto 0); beginprocess(clk,clr)beginif clr='0'thencnt<="0000";elsif clk='1' and clk'event thencnt<=cnt+'1';end if;count<=cnt;sel<=cnt(2 downto 0);end process;end beha;。

电子科技大学学生姓名:学号:指导教师:一、实验室名称:实验报告二、实验项目名称:扫描显示电路设计三、实验原理:数码显示板上一共有8 个数码管,如果按照传统的数码管驱动方式(静态扫描方式),则需要8 个七段译码器进行驱动,这样既浪费资源,有时电路工作也不可靠。

所以现在最常见的数码管驱动电路已经不用上述的静态扫描方式了,而是采用动态扫描显示的方式,这种方式只需一个译码器就可以实现电路正常、可靠的工作,这样大大节省资源。

动态数码扫描显示方式是利用了人眼的视觉暂留效应,把八个数码管按一定顺序(从左至右或从右至左)进行点亮,当点亮的频率(即扫描频率)不大时,我们看到的是数码管一个个的点亮,然而,当点亮频率足够大时,我们看到的不再是一个一个的点亮,而是全部同时显示(点亮),与传统方式得到的视觉效果完全一样。

因此我们只要给数码管这样一个扫描频率,那么就可以实现两个以上的数码管同时点亮。

而这个频率我们可以通过一个计数器来产生,只要计数频率足够大,就可以实现我们的要求。

事实上,因为数码管点亮不是瞬间就可以的,它也需要一定的时间,该时间与数码管的选择有关系。

为了折中这一对矛盾,实验中一般可将计数频率选择在100Hz左右肯定可以满足上述两个要求。

动态数码扫描显示的硬件电路设计要求是:对共阴数码管,将其公共端阴极接三八译码器的输出,三八译码器的输入为位选信号输入;将8 个(或更多)的数码管的相同段接在一起,然后引出。

原理图如下:四、实验目的:1、进一步熟悉用VHDL进行EDA设计方法;2、本实验与实验二的不同之处在八个数码管都要稳定地显示;3、进一步了解EDA实验箱的基本功能;五、实验内容:1、用VHDL设计一个扫描显示电路,使得八个数码管能同时显示(要求显示的值为自己的学号+100,如学号为1,则数码管显示101,多出的数码管全显示0),然后编译、仿真;2、下载该程序,验证程序是否正确。

3、请事先准备一个软盘或优盘,本实验程序需要保存,后面实验需要用到。

汕头大学实验报告实验三4×4键盘扫描时序逻辑电路的VHDL模型实验一、实验目的1、了解普通4×4键盘扫描的原理。

2、掌握组合逻辑电路和时序逻辑电路的混和设计。

3、进一步加深七段码管显示过程的理解。

二、硬件要求1、4×4键盘阵列。

2、FPGA主芯片。

3、可变时钟源。

4、七段码显示区。

5、LED显示模块。

三、实验原理本实验主要完成的实验是完成4×4键盘扫描的,然后获取其键值,并对其进行编码,从而进行按键的识别,并将相应的按键值进行显示。

键盘扫描的实现过程如下:对于4×4键盘,通常连接为4行、4列,因此要识别按键,只需要知道是哪一行和哪一列即可,为了完成这一识别过程,我们的思想是,首先固定输出4行为高电平,然后输出4列为低电平,在读入输出的4行的值,通常高电平会被低电平拉低,如果读入的4行均为高电平,那么肯定没有按键按下,否则,如果读入的4行有一位为低电平,那么对应的该行肯定有一个按键按下,这样便可以获取到按键的行值。

同理,获取列值也是如此,先输出4列为高电平,然后在输出4行为低电平,再读入列值,如果其中有哪一位为低电平,那么肯定对应的那一列有按键按下。

获取到行值和列值以后,组合成一个8位的数据,根据实现不同的编码在对每个按键进行匹配,找到键值后在7段码管和LED显示。

四、实验内容及步骤本实验内容是完成4×4键盘的扫描,然后将正确的键值进行显示,实验步骤如下:1、编写键盘扫描和显示的VHDL代码。

2、用MaxPlusII对其进行编译仿真。

3、在仿真确定无误后,选择芯片ACEX1K EP1K30QC208。

4、给芯片进行管脚绑定,在此进行编译。

5、根据自己绑定的管脚,在实验箱上对键盘接口、显示接口和FPGA之间进行正确连线。

6、给目标板下载代码,在4×4键盘输入键值,观看实验结果。

五、VHDL程序设计代码及结果1、4×4键盘扫描源程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY Vhdl1 ISPORT(CLK_1K : IN STD_LOGIC; --时钟输入1KHZCLK_40K : IN STD_LOGIC; --40K TimeClkKEY_LIE : IN STD_LOGIC_VECTOR(3 DOWNTO 0);-- 列输入START :OUT STD_LOGIC; --二-十进制数据输出标志KEY_HANG :OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --行输出DA TA_P : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--二-十进制数输出DISP_DA TA : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);--数码管显示译码输出DISP_SEL : OUT STD_LOGIC_VECTOR(1 downto 0));--数码管显示扫描输出END ;ARCHITECTURE RTL OF Vhdl1 ISSIGNAL INT : STD_LOGIC; --列与非信号SIGNAL CLK_SEL : STD_LOGIC;--键值控制1khz的时钟信号SIGNAL START_REG:STD_LOGIC; --数据输出标志信号SIGNAL DISP_SEL_REG:STD_LOGIC_VECTOR(1 DOWNTO 0);--数码管显示扫描信号SIGNAL DATA_L,DATA_H:STD_LOGIC_VECTOR(3 DOWNTO 0);--二-十进制低位、高位信号SIGNAL DATA_TMP:STD_LOGIC_VECTOR(3 DOWNTO 0);--二-十进制低位高位暂存信号SIGNAL KEY_HANG_TMP:STD_LOGIC_VECTOR(3 DOWNTO 0);--行输出信号SIGNAL DISP_DA TA_REG:STD_LOGIC_VECTOR(3 DOWNTO 0); --二-十进制低位、高位暂存信号(数码管用)SIGNAL KEY_CODE:STD_LOGIC_VECTOR(7 DOWNTO 0);--行列相并信号SIGNAL DATA_P_REG:STD_LOGIC_VECTOR(7 DOWNTO 0); --二-十进制数信号-------------------------------------------------------------------------------BEGINKEY_CODE<=KEY_HANG_TMP&KEY_LIE;--行、列相并DATA_P<=DATA_P_REG;START<= START_REG;KEY_HANG<=KEY_HANG_TMP;DISP_SEL<=DISP_SEL_REG;CLK_SEL<=CLK_1K AND ( NOT INT);--无键按下时有CLK-SEL时钟信号输出--------------------------------------------------PROCESS (CLK_SEL,CLK_40K , INT)V ARIABLE STA TE : INTEGER RANGE 0 TO 3 ;BEGINIF RISING_EDGE(CLK_40K) THEN --一个40K的脉冲上升沿到来输入一次列状态以判断是否有按键按下INT<= NOT (KEY_LIE(3) AND KEY_LIE(2) AND KEY_LIE(1) AND KEY_LIE(0));END IF;IF RISING_EDGE(CLK_SEL) THEN --一个1K的脉冲的上升沿到来输出一个带表行的状态CASE STATE IS--变量表示状态机,4循环WHEN 0=>KEY_HANG_TMP<="1110";STA TE :=1;WHEN 1 =>KEY_HANG_TMP<="1101";STATE :=2 ;WHEN 2 =>KEY_HANG_TMP<="1011";STATE :=3;WHEN 3 =>KEY_HANG_TMP<="0111";STATE :=0;END CASE;END IF;END PROCESS;PROCESS (CLK_40K , INT)--进程是并行的V ARIABLE STA TE :INTEGER RANGE 0 TO 3;V ARIABLE COUNTER : INTEGER RANGE 0 TO 31;BEGINIF INT='0' THENSTATE:=0;COUNTER:=0;ELSIF RISING_EDGE(CLK_40K) THENCASE STATE ISWHEN 0 =>DATA_TMP <= DATA_L;--低四位放入暂存信号内STATE:=1;WHEN 1 =>--再嵌套一个CASE语句CASE KEY_CODE IS--实现把像并数据译码十六进制的1到FWHEN "01110111" =>DA TA_L <="0001";--把1放入低四位DA TA_H <=DA TA_TMP;--把暂存信号的内容放入高四位,相相当于向左移位STA TE:=2;--跳出内嵌套CASE语句,转向外CASE语句的状态2 WHEN "01111011" =>DA TA_L <="0010";DA TA_H <=DATA_TMP;STATE:=2;WHEN "01111101" =>DA TA_L <="0011";DA TA_H <=DATA_TMP;STATE:=2;WHEN "01111110" =>DA TA_L <="0100";DA TA_H <=DATA_TMP;STATE:=2;WHEN "10110111" =>DA TA_L <="0101";DA TA_H <=DATA_TMP;STATE:=2;WHEN "10111011" =>DA TA_L <="0110";DA TA_H <=DATA_TMP;STATE:=2;WHEN "10111101" =>DA TA_L <="0111";DA TA_H <=DATA_TMP;STATE:=2;WHEN "10111110" =>DA TA_L <="1000";DA TA_H <=DATA_TMP;STATE:=2;WHEN "11010111" =>--9键DA TA_L <="1001";DA TA_H <=DATA_TMP;STATE:=2;WHEN "11011011" =>--0键DA TA_L <="0000";DA TA_H <=DATA_TMP;STATE:=2;WHEN "11011101" =>--A键,实现步进加一功能IF DA TA_H ="1001" THENIF DA TA_L="1001" THENDATA_H<="1001";DATA_L<="1001";ELSE DA TA_L<=DATA_L + 1;END IF;ELSIF DA TA_L="1001" THENDATA_L<="0000";DATA_H<=DATA_H+1;ELSEDATA_L<=DATA_L+1;DATA_H<=DATA_H;END IF;STATE:=2;WHEN "11011110" =>--B键,实现步键加十IF DA TA_H="1001" THENDA TA_H<="1001";ELSEDATA_L<=DATA_L;DATA_H<= DATA_H+1;END IF;STATE:=2;WHEN "11100111" =>--C键,实现步进减一IF DA TA_L="0000" AND DATA_H="0000" THENDATA_L<="0000";DATA_H<="0000";ELSIF DA TA_L="0000" THENDA TA_L<="1001";DA TA_H<= DATA_H-1;ELSEDATA_L <=DATA_L-1;DATA_H<=DATA_H;END IF;STA TE:=2;WHEN "11101011"=>--D键,实现步进减十IF DA TA_H="0000" THENDA TA_H<="0000";ELSEDATA_L<=DATA_L;DATA_H<=DATA_H-1;END IF;STATE:=2;WHEN "11101110" =>--E键,实现送数功能DA TA_L<=DATA_L;DA TA_H<=DATA_H;DATA_P_REG<=DATA_H&DATA_L;START_REG<='1';--数据输出标志信号置一STATE:=2;WHEN"11101101" =>--F键,实现清零功能DA TA_L<="0000";DA TA_H<="0000";STATE:=2;WHEN OTHERS =>--不可缺少STATE:=2;END CASE;WHEN 2 =>--状态2实现去抖动功能IF COUNTER=31 THEN --计数延时去抖COUNTER:=0;STA TE:=3;ELSECOUNTER:=COUNTER+1;STATE:=2;END IF;WHEN 3 =>-- 清除数据输出标志START_REG<='0';STA TE:=3;END CASE;END IF;END PROCESS;PROCESS (CLK_1K,DA TA_L,DATA_H)--数码管循环显示V ARIABLE STA TE: INTEGER RANGE 0 TO 1;BEGINIF RISING_EDGE(CLK_1K) THENCASE STATE ISWHEN 0 =>DISP_SEL_REG<="10";-- 输入10到数码管显示扫描信号DISP_DA TA_REG<=DATA_L;--二-十进制低高位暂存节点STATE:=1;WHEN 1 =>DISP_SEL_REG<="01";DISP_DA TA_REG<=DATA_H;STATE:=0;END CASE;END IF;END PROCESS;PROCESS(CLK_1K,DISP_DA TA_REG)--数码管译码BEGINIF RISING_EDGE(CLK_1K) THENCASE DISP_DA TA_REG ISWHEN "0000"=>DISP_DA TA<="1111110";--0WHEN "0001"=>DISP_DA TA<="0110000";--1WHEN "0010"=>DISP_DA TA<="1101101";WHEN "0011"=>DISP_DA TA<="1111001";WHEN "0100"=>DISP_DA TA<="0110011";WHEN "0101"=>DISP_DA TA<="1011011";WHEN "0110"=>DISP_DA TA<="1011111";WHEN "0111"=>DISP_DA TA<="1110000";WHEN "1000"=>DISP_DA TA<="1111111";WHEN "1001"=>DISP_DA TA<="1111011";WHEN OTHERS =>DISP_DA TA<="0000000";END CASE;END IF;END PROCESS;END;2、实验现象(1)38译码器六、思考题1、总结FPGA是如何识别按键的?与单片机读取键值有何不同?答:FPGA的所有I/O控制块允许每个I/O引脚单独配置为输入口,不过这种配置是系统自动完成的。

实验四扫描驱动显示电路设计(设计性实验)一、实验目的1.了解实验箱中 8 位七段数码管显示模块的工作原理。

2.熟悉 VHDL 硬件描述语言及设计专用数字集成电路的自顶向下的设计思想。

3.掌握利用 CPLD/FPGA设计 8 位七段数码管扫描显示驱动电路的方法。

二、实验设备1.计算机(配置为:P4 CPU 128M 内存);2. MAX+plusⅡ开发工具软件;3.EDA 实验箱(主芯片是ALTERA EPM7128SLC84-6);三、扫描原理为了减少8位显示信号的接口连接线,实验箱中的数码显示采用扫描显示工作模式。

即 8 位数码管的七段译码输入(a,b,c,d,e,f,g)是并联在一起的,而每一个数码管是通过一个3 位选择 sel[2..0]来选定的。

sel 与数码管之间是一 3-8 译码的关系,即sel为“000”时,选中第一个数码管,sel 为“111”时,选中第八个数码管。

四、设计任务本实验要求在给定子模块程序的基础上,画出设计原理图。

自行编写顶层模块程序,完成扫描显示驱动电路的设计,实现在 8 个数码管上轮流显示字符 0-F 的功能。

五、设计要求1.要求在 Max+plusⅡ平台上用 VHDL 语言编写顶层模块程序,调试、仿真成功后,下载至 ALTER EPM7128SLC84-15 芯片,再利用外接电路实现以上设计功能。

2.扫描驱动显示电路有 2 个输入端(clk,reset),14 个输出端(a,b,c,d,e,f,g)和(y0,y1,y2,y3,y4,y5,y6,y7),全部为 TTL 电平,管脚分配任意,如下图所示3.根据芯片特点,管脚分配时将时钟信号分配给 83 脚,复位信号分配给 1 脚,使能信号分配给 84脚。

六、程序清单:--顶层程序:library ieee;use ieee.std_logic_1164.all;entity disp isport(clk,reset: in std_logic;a,b,c,d,e,f,g: out std_logic;y: out std_logic_vector(2 downto 0));end disp;architecture beha of disp iscomponent counter16port(clk,clr: in std_logic;count: out std_logic_vector(3 downto 0));end component;component decdispport(datain: in std_logic_vector(3 downto 0);a,b,c,d,e,f,g: out std_logic);end component;component yima3port(x: in std_logic_vector(2 downto 0);y: out std_logic_vector(2 downto 0));end component;signal cont: std_logic_vector(3 downto 0);signal sel3: std_logic_vector(2 downto 0);begind1:counter16 port map(clk=>clk,clr=>reset,count=>cont);d2:decdisp port map(datain=>cont,a=>a,b=>b,c=>c,d=>d,e=>e,f=>f,g=>g);d3:yima3 port map(x=>cont(2 downto 0),y=>y); end beha;--十六进制程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter16 isport(clk,clr: in std_logic;count: out std_logic_vector(3 downto 0);sel: out std_logic_vector(2 downto 0)); end counter16;architecture beha of counter16 issignal cnt: std_logic_vector(3 downto 0);beginprocess(clk,clr)beginif clr='0'thencnt<="0000";elsif clk='1' and clk'event thencnt<=cnt+'1';end if;count<=cnt;sel<=cnt(2 downto 0);end process;end beha;--七段数码管显示程序:library ieee;use ieee.std_logic_1164.all;entity decdisp isport(datain: in std_logic_vector(3 downto 0);a,b,c,d,e,f,g: out std_logic);end decdisp;architecture beha of decdisp issignal dataout: std_logic_vector(6 downto 0); begina<=dataout(6);b<=dataout(5);c<=dataout(4);d<=dataout(3);e<=dataout(2);f<=dataout(1);g<=dataout(0);process(datain)begincase datain iswhen "0000"=> dataout<="1111110";when "0001"=> dataout<="0110000";when "0010"=> dataout<="1101101";when "0011"=> dataout<="1111001";when "0100"=>dataout<="0110011";when "0101"=> dataout<="1011011";when "0110"=> dataout<="1011111";when "0111"=> dataout<="1110000";when "1000"=> dataout<="1111111";when "1001"=> dataout<="1111011";when "1010"=> dataout<="1110111";when "1011"=> dataout<="0011111";when "1100"=> dataout<="1001110";when "1101"=> dataout<="0111101";when "1110"=> dataout<="1001111";when "1111"=> dataout<="1000111";when others=> dataout<="XXXXXXX";end case;end process;end beha;--3-8译码器实现数码管选择library ieee;use ieee.std_logic_1164.all;entity yima3 isport( x: in std_logic_vector(2 downto 0);y: out std_logic_vector(2 downto 0)); end yima3 ;architecture beha of yima3 isbeginy<=x;end beha;输出仿真波形图:disp.vhd波形:counter16.vhd波形:decdisp.vhd波形:yima3.vhd波形:七、硬件实验1、对芯片进行编程。

辽宁工业大学数字电子技术基础课程设计(论文)题目:LED显示器动态扫描驱动电路的设计院(系):电子与信息工程学院专业班级:学号:100405024学生姓名:指导教师:教师职称:副教授起止时间:2012.12.29—2013.1.11课程设计(论文)任务及评语院(系):电子与信息工程学院教研室:电子信息工程摘要随着计算机技术和电子技术的飞速发展和广泛应用,电器设备的输出显示技术也变得复杂多样。

在这些显示当中,LED数码管的显示电路较为简单,成本也较低,在功能单一的仪器仪表与机电设备中应用较广。

本文着重说明LED显示器动态扫描驱动电路的设计。

对于本设计首先用555定时器产生固定频率的信号作为节拍发生器的时钟,将此时钟连到由74LS160接成的四进制加法计数器上,由具有八个译码输出端的74LS138作为数码管的译码器。

其次,当7447引脚接到高电平时驱动共阴极七段LED数码管轮流显示对应数据。

最后利用仿真软件验证设计的正确性,当各引脚输出的高电平频率达到一定程度时,数码管呈现闪烁现象。

关键词:555定时器;计数器;译码器;七段LED数码管目录第1章绪论 (1)1.1LED显示器动态扫描驱动电路的设计意义 (1)1.2设计参数及要求 (1)1.3方案论证 (2)1.4设计总体框图 (3)第2章各单元电路的设计 (4)2.1多谐振荡器的设计 (4)2.2计数器的设计 (4)2.3译码器的设计 (5)2.4共阴极LED动态驱动电路设计 (6)2.5七段数码管的设计 (7)第3章整体电路设计 (9)3.1整体电路图及工作原理 (9)3.2电路参数计算 (10)3.3整体电路的仿真及分析 (10)第4章设计总结 (12)参考文献 (13)附录: (14)第1章绪论1.1LED显示器动态扫描驱动电路的设计意义随着计算机技术和电子技术的飞速发展和广泛应用,电器设备的输出显示技术也变得复杂多样,诸如CRT显示、LCD显示、多位LED显示及发光二极管显示等应运而生。

实验四键盘扫描及显⽰设计实验报告实验四键盘扫描及显⽰设计实验报告⼀、实验要求1. 复习⾏列矩阵式键盘的⼯作原理及编程⽅法。

2. 复习七段数码管的显⽰原理。

3. 复习单⽚机控制数码管显⽰的⽅法。

⼆、实验设备1.PC 机⼀台2.TD-NMC+教学实验系统三、实验⽬的1. 进⼀步熟悉单⽚机仿真实验软件 Keil C51 调试硬件的⽅法。

2. 了解⾏列矩阵式键盘扫描与数码管显⽰的基本原理。

3. 熟悉获取⾏列矩阵式键盘按键值的算法。

4. 掌握数码管显⽰的编码⽅法。

5. 掌握数码管动态显⽰的编程⽅法。

四、实验内容根据TD-NMC+实验平台的单元电路,构建⼀个硬件系统,并编写实验程序实现如下功能:1.扫描键盘输⼊,并将扫描结果送数码管显⽰。

2.键盘采⽤ 4×4 键盘,每个数码管显⽰值可为 0~F 共 16 个数。

实验具体内容如下:将键盘进⾏编号,记作 0~F,当按下其中⼀个按键时,将该按键对应的编号在⼀个数码管上显⽰出来,当再按下⼀个按键时,便将这个按键的编号在下⼀个数码管上显⽰出来,数码管上可以显⽰最近 4 次按下的按键编号。

五、实验单元电路及连线矩阵键盘及数码管显⽰单元图1 键盘及数码管单元电路实验连线图2实验连线图六、实验说明1. 由于机械触点的弹性作⽤,⼀个按键开关在闭合时不会马上稳定地接通,在断开时也不会⼀下⼦断开。

因⽽在闭合及断开的瞬间均伴随有⼀连串的抖动。

抖动时间的长短由按键的机械特性决定,⼀般为 5~10ms。

这是⼀个很重要的时间参数,在很多场合都要⽤到。

键抖动会引起⼀次按键被误读多次。

为了确保 CPU 对键的⼀次闭合仅做⼀次处理,必须去除键抖动。

在键闭合稳定时,读取键的状态,并且必须判别;在键释放稳定后,再作处理。

按键的抖动,可⽤硬件或软件两种⽅法消除。

2. 为了减少键盘与单⽚机接⼝时所占⽤ I/O 线的数⽬,在键数较多时,通常都将键盘排列成⾏列矩阵形式。

3. 从数码管显⽰⽅式看,数码管分为静态显⽰和动态显⽰两种⽅式。

实验四动态扫描显示一、实验目的:1、掌握数字、字符转换成显示段码的软件译码方法2、动态显示的原理和相关程序的编写二、实验设备:电脑和THGZ-1单片机.CPLD/FPGA综合开发实验装置三、实验说明:动态显示,也称扫描显示。

显示器由6 个共阴极数码管构成。

单片机的P0 口输出显示段码,由一片74LS245 驱动输出;P1 口输出位码,经74LS06 反向后输出。

单片机P0 输出段码,P1 口输出位码,输出6 个字符。

四、实验内容及步骤:1、单片机最小应用系统的P0 口接段码口a~h,P1 口接位码口S1~S6。

2、打开模块电源,实验台电源。

3、推上左侧空气开关,启动计算机,打开伟福仿真软件Keil Uvsion2,进入仿真环境。

⑴建立工程项目:点击主菜单 PROJEKT→NEW PROJECT→工程名 XXX.UV2(保存在桌面上)a、CPU选择:DEVICE → ATMEL → AT89C51COPY STANDARD 8051 STARTUP CODE……? 否⑵进行仿真器的设置:打开 View →PROJECT WINDOW 界面,右键点击TARGET1 选择 OPTION FOR TARGET TARGET1b、目标机晶振选择:TARGET → XTAL → 11.0592 MHZc、调试选项:DEBUG →⊙USE KEIL MONITOR DRIVER-51点击其旁边的”SETTING”设置串口 PORT :COM1传输波特率 BAUDRATE : 38400⑶创建程序文件:FILE→NEW FILE→在 TEXT 文本界面输入源程序输入完毕,另存 SAVE AS 文件名 XXX.ASM(保存在桌面上)⑷添加程序到工程组:点开TARGET1→SOURCE GROUP →ADD FILES TO GROUP “SOURCE GROUP1”在文件类型窗口选择: ALL FILES在文件名窗口输入要调试的程序文件名 : 桌面: XXX.ASM,点击“ADD”键,并关闭此窗口⑸查看源程序:双击 SOURCE GROUP 下的文件名(SOURCE GROUP下只允许一个文件,其他用 REMOVE FILE FROM SOURCE GROUP 删去)打开源程序,阅读、理解、分析该程序。

实验4 扫描显示驱动电路

一、实验目的

了解教学系统中8位八段数码管显示模块的工作原理,设计标准扫描驱动电路模块,以备后面实验用。

二、硬件要求

主芯片Altera EPM7128SLC84-15,时钟,8位八段数码管显示器,四位拨码开关。

三、实验内容

用四位拨码开关产生8421BCD码,用CPLD分别产生字形编码电路和扫描驱动电路,然后进行仿真,观察波形,正确后编程下载实验测试。

1、编一个简单的从0~F轮换显示十六进制数的电路。

2、用计数器产生数码管扫描驱动信号,调节时钟频率,感受扫描的过程,并观察字符的亮度和显示刷新的效果。

7

四、实验原理

四位拨码开关提供8421BCD 码,经译码电路DECL7S 后连接8段数码管的字形显示驱动信号a,b,c,d,e,f,g 。

数码管扫描电路可通过片选地址SEL[2..0]控制。

由SEL[2..0]和a,b,c,d,e,f,g 决定了8位数码管中的那一位显示和显示什么字形。

SEL[2..0]变化的快慢决定了扫描频率的快慢。

1、参考电路:如图4-1所示(时钟频率

>40Hz)

实验连线:把RESET 和rst0接高电平,CLK 接上时钟信号,可观察到第一个数码管循环显示字符0~F 。

2、参考电路:如图4-2所示

图4-1(t4-1.gdf )

图4-1’(t4-11.gdf )

图4-2(t4_2.gdf)

五、实验连线

输入信号:

D3,D2,D1,D0所对应的管脚同四位拨码开关相连;

清零信号RESET所对应的管脚同按键开关相连;

时钟CLK所对应的管脚同试验箱上的时钟源相连。

输出信号:

代表扫描片选地址信号SEL2,SEL1,SEL0的管脚同四位扫描驱动地址的低三位相连,最高位地址接“0”(也可悬空);

代表七段数码驱动信号a, b, c, d, e, f, g的管脚分别同扫描数码管的段输入a,b,c,d,e,f,g相连。

六、实验报告

1、字形编码的种类,即一个8段数码管可产生多少种字符,产生所有字符需多少根译码信号线?

2、字符显示亮度和扫描频率的关系,且让人感觉不出光烁现象的最低扫描频率是多少?

七、附录

(1) 字符译码器DECL7S的VHDL源程序

library ieee;

use ieee.std_logic_1164.all;

entity decl7s is

port(a:in std_logic_vector(3 downto 0);

led7s:out std_logic_vector(6 downto 0));

end;

architecture one of decl7s is

begin

process(a)

begin

case a is

when "0000" => led7s<="0111111";

when "0001" => led7s<="0000110";

when "0010" => led7s<="1011011";

when "0011" => led7s<="1001111";

when "0100" => led7s<="1100110";

when "0101" => led7s<="1101101";

when "0110" => led7s<="1111101";

when "0111" => led7s<="0000111";

when "1000" => led7s<="1111111";

when "1001" => led7s<="1101111";

when "1010" => led7s<="1110111";

when "1011" => led7s<="1111100";

when "1100" => led7s<="0111001";

when "1101" => led7s<="1011110";

when "1110" => led7s<="1111001";

when "1111" => led7s<="1110001";

when others => null;

end case;

end process;

end;

(2) 16进制4位计数器的VHDL源程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity cnt4b is

port(clk,rst,en : in std_logic;

cq : out std_logic_vector(3 downto 0);

cout : out std_logic );

end cnt4b;

architecture behave of cnt4b is

begin

process(clk,rst,en)

variable ci:std_logic_vector(3 downto 0);

begin

if rst='1' then ci:=(others=>'0');--计数器异步复位

elsif clk'event and clk='1' then

if en='1' then --检测是否允许计数

if ci<"1111" then ci:=ci+1; --允许计数,

else ci:=(others=>'0'); --等于15,计数值清零

end if;

end if;

cq<=ci;

end if;

if ci="1111" then cout<='1'; --输出进位信号

else cout<='0';

end if;

end process;

end behave;

※文本编辑器的使用说明

MAX+PLUSII支持AHDL,VHDL及Verilog HDL等硬件描述语言。

下面通过一个例子说明采用文本方式进行设计的步骤。

首先选择File/New,在对话框中选择Text Editor File,打开一个无标题的Text Editor窗口。

然后选择File/Save As,在File Name框内输入文件名为——实体名.vhd,保存文件。

将上面的源程序输入。

完成后,可选择File/Project/Set Project to Current File,将文件设为当前项目。

然后同图形编辑一样,进行编译通过,波形仿真。

为了能在图形编辑器中调用,可以通过File/Greate Default Symbol将这部分生成一个可调用的图形元件符号,可以通过File/Edit Symbol对生成的图形符号进行简单编辑。

注意,只有在同一个文件夹中才可直接调用。

为了在任意文件中调用,可以将编译生成的扩展名为sym的符号文件和扩展名为vhd的文本源程序文件放在同一个文件夹中,通过Option/User library命令建立自己的元件库。