基于FPGA全景视频监控的设计

- 格式:pdf

- 大小:294.93 KB

- 文档页数:3

九江东毅港口监控系统设计方案目录1。

系统概述 (3)2。

系统设计依据及设计原则 (4)2。

1系统设计规范及依据 (4)2.2设计原则及要求 (5)3。

系统组成结构 (6)3.1系统结构拓扑图 (6)3.2系统组成模块 (6)3.2。

1系统前端监控摄像头 (6)3。

2.2 传输链路 (7)3。

2.3 监控中心 (8)4. 系统设计思路及系统需求的功能 (8)4。

1.系统设计思路 (8)4。

2。

系统功能需求 (9)5。

系统详细设计 (10)5.1 监控摄像机点位设计 (10)5。

1。

1监控摄像机的要求 (10)5。

1.2监控探头的选型及参数 (12)5.2传输系统设计 (12)5。

2。

1传输方式的类型 (12)5。

2。

2电源及控制信号传输 (14)5。

3监控室里各设备设计 ....................................................错误!未定义书签。

5。

3。

1。

NVR/DVR (14)5。

3.1.1 NVR的存储特点 (14)5.3.1。

2 NVR的选型和参数 (15)5。

3.2显示系统 (15)5.4数据存储架构 (16)6.监控系统设备的使用与维护 (17)7.整个系统结构示意图 (18)1。

系统概述近几年视频监控报警系统的发展突飞猛进,它的推广和应用也在遍布各个领域,它已成为现代化管理和安全防范的重要手段。

随着IP 网络和宽带技术的不断发展,采用先进计算机通信技术及图像视频压缩技术为核心的网络化、数字化视频监控系统方案越来越得到人们的广泛使用。

视频监控系统防范于未然,用来实现较周密的外围区域及建筑物内重要的区域管理,减少管理人员的工作强度,提高管理质量及管理效率.作为现代化管理有力的辅助手段,视频监控系统将现场内各现场的视频图像传送至监控中心,管理人员在不亲临现场的情况下可客观地对各监察地区进行集中监视,发现情况统一调动,节省大量巡逻人员,还可避免许多人为因素。

FPGA在视频监控系统中的应用与设计周克良;周利锋;章祖忠【摘要】针对现有的视频监控系统具有性能低,灵活性差,不便更新,开发成本高,可靠性低的问题,设计了一种基于现场可编程门阵列FPGA的视频监控系统;该系统首先利用CMOS摄像头OV7670获取模拟视频图像,双端口SDRAM对图像数据进行缓存,然后利用FPGA对视频信号处理能力强,集成度高,灵活性强,并行处理等特点实现对视频信号的处理,进而达到最终在VGA显示器上显示的效果;与其他视频监控设备相比,该系统能够高效的实现视频监控,而且具有实时性高,成本低,可靠性强等优点.【期刊名称】《计算机测量与控制》【年(卷),期】2015(023)010【总页数】4页(P3381-3384)【关键词】FPGA;视频监控;图像处理;VGA【作者】周克良;周利锋;章祖忠【作者单位】江西理工大学电气工程与自动化学院,江西赣州 341000;江西理工大学电气工程与自动化学院,江西赣州 341000;江西理工大学电气工程与自动化学院,江西赣州 341000【正文语种】中文【中图分类】TP272视频监控系统是银行,火车站,汽车站,娱乐场所,购物中心甚至家庭保安的重要组件。

随着社会的发展,人们生活水平的不断提高,人们的安全意识也在不断增强,安全问题势必成为社会的一个重要话题[1],人们迫切希望通过监控设备达到震慑敌人,降低风险的效果,视频监控系统得到人们的青睐并开始大规模的使用。

然而,目前市场上大部分视频监控系统实时性低[2],成本高,更大程度上只是震慑别人,视频的监控效果质量很差,达不到监控的要求。

并且对已有的监控系统进行升级改造困难,代价昂贵,耗时长,这迫切需要新产品的出现。

随着嵌入式系统技术的飞速发展,设计了基于现场可编程门阵列(FPGA)的视频监控系统,采用Altera公司CycloneⅡ系列EP2C8Q208C8作为视频监控系统的核心控制,大大提高了视频监控的效果和质量,解决了现有监控系统存在的各种问题。

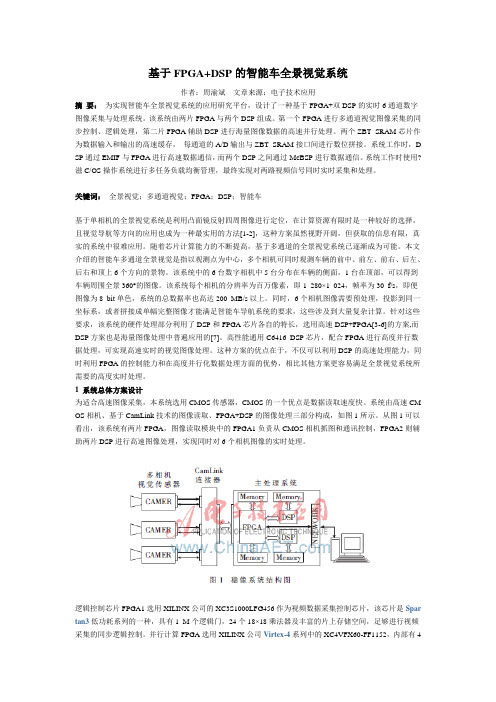

基于FPGA+DSP的智能车全景视觉系统作者:周渝斌文章来源:电子技术应用摘要:为实现智能车全景视觉系统的应用研究平台,设计了一种基于FPGA+双DSP的实时6通道数字图像采集与处理系统。

该系统由两片FPGA与两个DSP组成。

第一个FPGA进行多通道视觉图像采集的同步控制、逻辑处理,第二片FPGA辅助DSP进行海量图像数据的高速并行处理。

两个ZBT SRAM芯片作为数据输入和输出的高速缓存,每通道的A/D输出与ZBT SRAM接口间进行数位拼接。

系统工作时,D SP通过EMIF与FPGA进行高速数据通信,而两个DSP之间通过McBSP进行数据通信。

系统工作时使用?滋C/OS操作系统进行多任务负载均衡管理,最终实现对两路视频信号同时实时采集和处理。

关键词:全景视觉;多通道视觉;FPGA;DSP;智能车基于单相机的全景视觉系统是利用凸面镜反射四周图像进行定位,在计算资源有限时是一种较好的选择,且视觉导航等方向的应用也成为一种最实用的方法[1-2],这种方案虽然视野开阔,但获取的信息有限,真实的系统中很难应用。

随着芯片计算能力的不断提高,基于多通道的全景视觉系统已逐渐成为可能。

本文介绍的智能车多通道全景视觉是指以观测点为中心,多个相机可同时观测车辆的前中、前左、前右、后左、后右和顶上6个方向的景物。

该系统中的6台数字相机中5台分布在车辆的侧面,1台在顶部,可以得到车辆周围全景360°的图像。

该系统每个相机的分辨率为百万像素,即1 280×1 024,帧率为30 f/s,即便图像为8 bit单色,系统的总数据率也高达200 MB/s以上。

同时,6个相机图像需要预处理,投影到同一坐标系,或者拼接成单幅完整图像才能满足智能车导航系统的要求,这些涉及到大量复杂计算。

针对这些要求,该系统的硬件处理部分利用了DSP和FPGA芯片各自的特长,选用高速DSP+FPGA[3-6]的方案,而DSP方案也是海量图像处理中普遍应用的[7]。

技术创新博士论坛您的论文得到两院院士关注基于FPGA 全景视频监控的设计Design of Panoramic Video Monitoring System Based on FPGA(大庆石油学院)王秀芳侯振龙梁洪卫WANG Xiu-fang HOU Zhen-long LIANG Hong-wei摘要:针对现有视频监控器不能在同一时间、同一位置监控360°范围内全景图像的问题,本文利用FPGA 设计了一种可以实现在摄像头静止情况下拍摄360°全景目标的监控系统。

采用了以改进的摄像头和模数转换芯片SAA7113为采集方案,针对SAA7113芯片实现了总线配置、四路视频的VGA 显示模块的设计。

关键词:全景监控;FPGA;CCD中图分类号:TP302.1文献标识码:AAbstract:For improving the disadvantage that the current Video Monitoring System can not monitor the panoramic images at the same time 、the same location,this paper has designed a Panoramic Video Monitoring System with FPGA which could achieve the goal of monitoring 360°view.The design is adopted by the improved cameras and A/D chips.achieved the configuration of Inter IC Bus for SAA7113chip and displayed on a VGA monitor.Key words:Panoramic Video Monitoring System;FPGA;CCD文章编号:1008-0570(2010)07-2-0021-021引言目前市场上的主流摄像头产品主要是“枪机(即固定安装的摄像机)”和“球机(即带旋转云台的摄像机)”。

科技前沿1视频监控系统设计本视频监控系统主要由图像采集终端,视频转换接口,VGA 显示终端组成,传感器OV5620采集到现实景物后,将生成的RAW数据流由ITU数据输出端口发送给视频转换接口。

视频转换接口将ITU数据输入端口送来的RAW数据流转换成RGB数据流发送,通过VGA端口发送给显示终端显示。

OV5620输出图像的最大分辨率为2592×1944。

2系统硬件设计硬件电路主要包括CMOS摄像头传感器,数据采集模块,SDRAM存储模块,VGA视频输出接口模块。

在现实景物的采集与显示过程中,视频转换接口功能的实现通过以下步骤来完成:①对采集到的RAW数据流进行转换。

视频转换接口收到的是像素的RAW值,因此需要将每个像素的色彩值由RAW空间转换到RGB空间,然后再对RGB进行数据平均,输出RGB 数据,实现色彩空间的转换。

②将转换后的每个像素的RGB值写入存储器中。

由于视频的转换接口和VGA接口的视频数据流工作的时钟域是不同的,需要SDRAM来作为缓存,存储一帧图像的数据,以供VGA显示器显示。

③从存储器中读出像素的RGB值,并将其转换成VGA模拟信号值。

由于FPGA内部没有D/A转换单元,因此不能通过FPGA来直接产生模拟信号,还需要另外添加专门的图像D/A芯片(ADV7123)来完成模拟信号的产生。

系统工作时,FPGA将从SDRAM存储器中读出的RGB值送至图像DA芯片进行数模转换变成模拟信号值VGA 接口直接输出,系统就能将图像在VGA显示器上直接显示。

3系统软件设计3.1摄像头采集图像模块程序设计摄像头的采集过程和VGA的显示恰好是个相反的过程,VGA的显示是由FPGA产生行列时序,供给D/A转换器,产生驱动VGA显示器的模拟信号。

而摄像头的采集图像是摄像头自动产生行列信号,用FPGA进行采集就行。

在对摄像头进行采集之前,需要用SCCB协议给摄像头进行配置,SCCB协议兼容I2C协议,前者写数据和I2C是一样的,就是读数据的时序不一样。

DOI:10.16660/ki.1674-098X.2020.12.051基于FPGA的全景相机系统的软件设计①王玥1 付强2 姚江云1(1.广西科技大学鹿山学院 广西柳州 545616;2.柳州铁道职业技术学院 广西柳州 545616)摘 要:本文主要讨论全景相机系统的实现算法。

简单介绍如下,可以利用Matlab计算出摄像头的内部参数,利用双线性插值算法在(FPGA )上对摄像头采集的畸变图像进行校正,还可以用SIFT算法和BRIEF 算法来提取特征点和匹配特征点,利用最小二乘法计算变换矩阵。

最后将所得参数与校正后的图像数据传送到电脑端整合出坐标变换后的图像,实现图像配准与融合。

关键词:全景相机系统 特征点 畸变图像配准 图像配准与融合中图分类号:TP39 文献标识码:A 文章编号:1674-098X(2020)04(c)-0051-02①课题来源:“2019年度广西高校中青年教师科研基础能力提升项目:基于FPGA的全景相机系统研究(课题编号:2019KY1105)”的研究成果。

1 相机的标定与图像畸变校正因为不同的摄像头之间存在镜头畸变系数不同这个固有的因素,并且摄像头的畸变系数要用标定获取,通过USB2.0传输每个摄像头采集到的图像数据到上位机,用Matlab 计算得到摄像头内部参数矩阵和镜头畸变系数矩阵,依次对每个摄像头进行畸变校正。

缓存在片外存储器中的图像数据是畸变校正模块的输入数据,图像数据经过畸变校正之后通过并行的6路输出,使6个16位的图像数据在每个时钟周期同时输出,像素在图像中的位置信息和片上存储信息同时输入并用分时复用的方法保存到DDR 中。

双线性插值算法具有噪声小、消耗小等优点,运用此算法在FPGA上进行实时畸变校正并求出图像的变换矩阵,将求得的图像变换参数和畸变校正等图像数据传送到电脑端,进行图像融合和显示。

全景相机具有多个不同的摄像头,而每个摄像头所处的位置也有所不同,当进行图像采集的时候,同一个物体依据摄像头拍摄的位置不同所得到的数据肯定不同。

基于FPGA和DSP的图像拼接系统李锦明;侯天喜;高文刚;成乃朋【摘要】针对传统的在PC机上实现的图像拼接系统体积庞大、功耗高、携带不便等缺点,结合SIFT特征设计了一种基于FPGA和DSP的图像拼接系统.FPGA负责完成视频图像采集、显示的逻辑控制;DSP负责完成图像拼接算法的实现;并利用FPGA内部FIFO与DSP的EMIFA接口直接通信,实现FP-GA与DSP之间的数据交换.利用ChipScope、CCS对系统中的各个模块调试,实验结果表明基于FPGA 和DSP的图像拼接系统能够实现图像拼接功能,验证了其有效性.同时极大地增强了系统的灵活性.【期刊名称】《仪表技术与传感器》【年(卷),期】2018(000)007【总页数】4页(P46-49)【关键词】图像拼接;SIFT;FPGA;DSP;EMIFA【作者】李锦明;侯天喜;高文刚;成乃朋【作者单位】中北大学,仪器科学与动态测试教育部重点实验室,山西太原 030051;中北大学,仪器科学与动态测试教育部重点实验室,山西太原 030051;中北大学,仪器科学与动态测试教育部重点实验室,山西太原 030051;中北大学,仪器科学与动态测试教育部重点实验室,山西太原 030051【正文语种】中文【中图分类】TP2740 引言图像拼接技术[1]是计算机视觉的一个重要研究方向,拼接技术的出现和发展为获取更广视角、更高分辨率以及全景图像提供了有效的解决方案,已经广泛应用于虚拟现实、医学影像、智能监控、军事导航等领域。

目前绝大多数的图像拼接系统都是在PC机上开发运行的,但是PC机自身体积庞大、携带不便等缺点制约了它在实际工程中的应用。

鉴于此,结合SIFT特征设计了一种基于FPGA和DSP的嵌入式图像拼接系统[2-3],极大地增强了系统的灵活性和实时性。

最终实验结果表明该系统拼接效果良好,具有广阔的应用前景。

1 图像拼接算法图像拼接主要包括图像获取、图像配准、图像变换和图像融合4个过程,具体算法流程如图1所示。

摘要全景相机在水平方向视角为360°,垂直方向视角最高可达360°,可广泛应用于机器人、视频会议、监控和虚拟现实领域。

作为一种视觉传感器应用于机器人领域中,可使机器人在目标识别、路径规划和避障等方面做出最优决策。

由于处理量数据大、算法复杂度高且应满足便携性要求,因此,目前大部分全景相机无法实时获取无畸变的全景图像,使其在实时性要求高的领域中的应用受到限制,因此解决全景相机实时性问题已成为高校和社会研究的重点。

相比于其他图像处理器现场可编程门阵列具有高速、并行、低功耗、体积小的优点,应用于全景相机中在解决实时性问题同时可显著降低设备功耗和体积。

本课题开发了一款多摄像头全景相机平台,并实时计算出该平台内5幅图像间的变换矩阵,每幅图像分辨率为640×480,帧率为30帧每秒。

主要分为以下几个部分。

本文选用5个广角、手动调焦的CMOS摄像头,在满足全景相机功能的条件下,设计并制作了摄像头安装架,实现了对360°景物的采集。

选用现场可编程门阵列对图像或视频进行处理。

广角摄像头采集到的图像存在畸变在Matlab上求得每个摄像头的内部参数后,运用双线性差值算法,通过插值查找表实现现场可编程门阵列对畸变图像实时校正。

采用SIFT算法提取图像特征点,BRIEF算法生成特征点描述符并通过最小汉明距离判定方法找出匹配点对。

在算法方面,基于全景相机应用平台,将SIFT、BRIEF算法各部分优化整合。

在实现算法方面,采用数据并行,任务并行方法,利用现场可编程门阵列并行处理特性,可实时提取匹配点对。

在现场可编程门阵列端采用随机采样一致性算法提纯特征点对将迭代串行运算的随机采样一致性算法优化为并行处理,寻找出8对局内点,同时结合最小二乘法求得变换矩阵参数。

最后将变换矩阵参数与校正后的图像数据传到电脑端求解坐标变换后的图像,实现图像配准与图像融合。

关键词:现场可编程门阵列;图像畸变校正;图像特征点;随机采样一致性算法AbstractThe panoramic camera have a 360°angle of view horizontally and an almost 360° vertically, and it should have been widely used in the field of robotics, video conference, surveillance and virtual reality. With the panoramic camera, the robot can make a better decision in target recognition, path planning and obstacle avoidance. Because of processing mass data and the the complex image processing algorithm, it is necessary to meet the portability requirements. Almost all panoramas can not obtain panoramic images without distortion in real time, which limits their application. Therefore, solving the real-time problem has become the focus of universities and corporations. Compared with other image processors, FPGA has the advantages of a higher speed, parallelism, lower power consumption and smaller size. Choosing the FPGA as the core component in panoramic camera can reduce the power consumption and size of the device.In this thesis, a multi-camera panoramic camera platform has been developed and the transformation matrix between the five images in the platform could be calculated in real time. The resolution of each image is 640×480 and the frame rate is 30 frames per second. There are several main parts in this study as following. Used by five wide-angle manual focusing CMOS camera module, the platform realizes the function of panorama camera. We choose FPGA chip to processing image in real-time. The image of the wide-angle camera is distorted. We get the internal parameters of each camera with Matlab software. Using the bilinear interpolation algorithm, we correct the distorted image in real-time by the look-up table. We registrate image by image featres. We extract the image featres using the SIFT algorithm, generate feature point descriptors by BRIEF algorithm and determine the matching points by minimum Hamming distance. To extract the image features and match these points in real, we optimize the image processing algorithms using data parallel, task parallel method, basing on FPGA We remove incorrect matches by RANSAC algorithm in parallel processing and obtain the transformation matrix. Finally, the transformation matrix parameters and the image data after correcting are transferred to PC to realize the image registration and image fusion.Keywords: FPGA, distortion correction, image feature point s, RANSAC algorithm目录摘要 (I)ABSTRACT (II)第1章绪论 (1)1.1课题来源 (1)1.2研究目的及意义 (1)1.3国外研究现状 (2)1.4国内研究现状 (4)1.5本文的主要研究内容 (6)第2章全景相机系统设计 (7)2.1引言 (7)2.2全景相机硬件系统设计 (7)2.2.1 摄像头选型 (7)2.2.2 摄像头安装平台设计 (9)2.2.3 图像处理器选型 (10)2.3全景相机图像处理系统设计 (11)2.3.1 图像预处理 (11)2.3.2 图像变换矩阵求解 (13)2.4本章小结 (14)第3章全景相机图像畸变校正 (15)3.1引言 (15)3.2摄像头标定 (15)3.2.1 摄像头成像模型 (15)3.2.2 图像畸变 (18)3.2.3 摄像头标定实验 (20)3.3图像畸变校正 (20)3.3.1 图像畸变校正算法 (20)3.3.2 图像畸变校正硬件架构 (22)3.4本章小结 (25)第4章全景相机图像特征提取与匹配 (26)4.1引言 (26)4.2SIFT算法 (27)4.2.1 高斯差分尺度空间构建 (27)4.2.2 特征点检测 (29)4.2.3 特征点方向确定 (30)4.2.4 生成特征描述子 (30)4.3BRIEF算法 (31)4.4全景相机图像特征提取与匹配算法 (33)4.5算法硬件架构 (34)4.5.1 特征点提取 (35)4.5.2 特征描述向量生成 (37)4.5.3 图像特征点匹配 (38)4.6实验结果与分析 (39)4.7本章小结 (41)第5章全景相机图像变换关系求取 (42)5.1引言 (42)5.2图像变换模型 (42)5.3变换矩阵计算 (43)5.4RANSAC算法 (44)5.5RANSAC算法硬件架构 (45)5.6实验结果与分析 (46)5.7本章小结 (48)结论 (49)参考文献 (50) (54)致谢 (55)第1章绪论1.1课题来源本课题来源于深圳市孔雀团队——超高速超高清图像感知技术与装备创新团队。

技术创新博士论坛您的论文得到两院院士关注基于FPGA 全景视频监控的设计Design of Panoramic Video Monitoring System Based on FPGA(大庆石油学院)王秀芳侯振龙梁洪卫WANG Xiu-fang HOU Zhen-long LIANG Hong-wei摘要:针对现有视频监控器不能在同一时间、同一位置监控360°范围内全景图像的问题,本文利用FPGA 设计了一种可以实现在摄像头静止情况下拍摄360°全景目标的监控系统。

采用了以改进的摄像头和模数转换芯片SAA7113为采集方案,针对SAA7113芯片实现了总线配置、四路视频的VGA 显示模块的设计。

关键词:全景监控;FPGA;CCD中图分类号:TP302.1文献标识码:AAbstract:For improving the disadvantage that the current Video Monitoring System can not monitor the panoramic images at the same time 、the same location,this paper has designed a Panoramic Video Monitoring System with FPGA which could achieve the goal of monitoring 360°view.The design is adopted by the improved cameras and A/D chips.achieved the configuration of Inter IC Bus for SAA7113chip and displayed on a VGA monitor.Key words:Panoramic Video Monitoring System;FPGA;CCD文章编号:1008-0570(2010)07-2-0021-021引言目前市场上的主流摄像头产品主要是“枪机(即固定安装的摄像机)”和“球机(即带旋转云台的摄像机)”。

这些产品功能比较单一,主要存在以下缺点:视场范围小;存在监控盲区;需要安装较多摄像头;在同一时间只能监控某一角度空间。

但是在例如交通运输等必要场合,要求同一时间、同一位置持续监视360°范围内的目标。

随着先进的视频监控技术的发展,可以解决监控盲区,实现360°总体范围的宏观拍摄功能。

目前主要是少数几个海外厂家生产,售价高昂,相关设计资料更是少之又少。

解决监控盲区,常用有两套解决方案:一是在不同角度安装多个摄像机;二是安装快球系统。

但是安装多个摄像机势必会增加成本,而快球实现360°视频监控在某一时刻只能看到某一角度的画面,不可避免的还是会在监控时出现盲区。

本文在现有视频监控的基础上设计了一种新型全景监控摄像机,能够拍摄360°全景视频图像,无观察死角,不需旋转云台,并将所拍摄内容显示在同一个VGA 设备上,既降低了成本和维修费用又解决了普通球机不能同时浏览全景图像的问题。

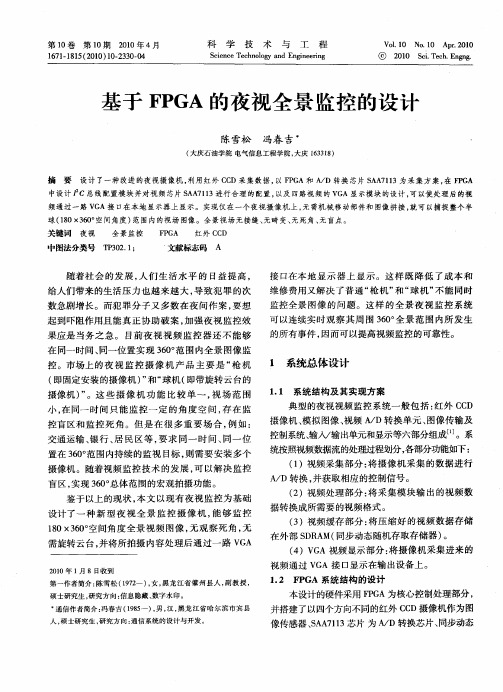

2系统总体设计2.1典型系统结构及其实现方案一个典型的视频监控系统一般包括如下几个部分:模拟图像、CCD(电荷耦合器件)摄像头、视频A/D 转换单元、图像传输及控制系统、输入/输出单元和显示部分等。

系统按照视频数据流的处理过程划分,各部分功能如下:(1)视频采集部分:将摄像头采集的数据进行A/D 转换,并获取相应的控制信号。

(2)视频处理部分:将采集模块输出的视频数据转换成需要的视频格式。

(3)视频缓存部分:将压缩好的视频数据存储在外部SDRAM 中。

(4)VGA 视频显示部分:将摄像头采集进来的视频通过VGA 接口显示在输出设备上。

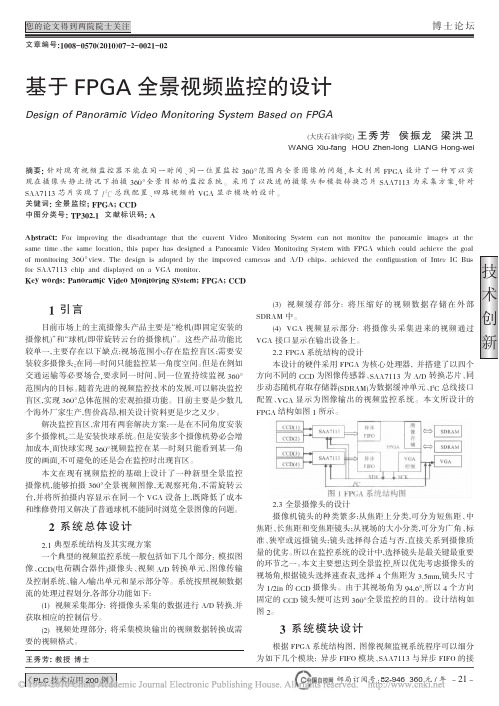

2.2FPGA 系统结构的设计本设计的硬件采用FPGA 为核心处理器,并搭建了以四个方向不同的CCD 为图像传感器、SAA7113为A/D 转换芯片、同步动态随机存取存储器(SDRAM)为数据缓冲单元、I 2C 总线接口配置、VGA 显示为图像输出的视频监控系统。

本文所设计的FPGA 结构如图1所示。

图1FPGA 系统结构图2.3全景摄像头的设计摄像机镜头的种类繁多:从焦距上分类,可分为短焦距、中焦距、长焦距和变焦距镜头;从视场的大小分类,可分为广角、标准、狭窄或远摄镜头;镜头选择得合适与否,直接关系到摄像质量的优劣。

所以在监控系统的设计中,选择镜头是最关键最重要的环节之一。

本文主要想达到全景监控,所以优先考虑摄像头的视场角,根据镜头选择速查表,选择4个焦距为3.5mm,镜头尺寸为1/2in 的CCD 摄像头。

由于其视场角为94.6°,所以4个方向固定的CCD 镜头便可达到360°全景监控的目的。

设计结构如图2。

3系统模块设计根据FPGA 系统结构图,图像视频监视系统程序可以细分为如下几个模块:异步FIFO 模块、SAA7113与异步FIFO 的接王秀芳:教授博士技术创新口模块、I2C配置接口模块和VGA显示模块。

图2监控场景图3.1FIFO模块设计FPGA与A/D转换单元的接口有SAA7113的8位视频数据线VPO和同步时钟线LCC。

FPGA在每个LCC时钟的上升沿,对SAA7113的VPO口采样接收一个8位的视频数据。

在本系统中SAA7113送过来的LLC频率为27MHz,而FP-GA系统时钟频率为48MHz。

系统在不同时钟域之间数据传递,这便产生了亚稳态问题。

解决在异步时钟域之间传输数据的方法通常有三种:在时钟同步单元中采用两次同步法;使用握手信号机制;使用异步FIFO进行数据缓冲。

本系统采用异步FIFO进行数据缓冲。

设计中采用Quar-tusII自带的参数化模型库LPM(Library of Parameterized Mod-ules)进行设计,也可以称之为软核(Soft IP Core)。

Quartus II软件中提供了五种FIFO宏模块,本设计中选用LPM_FIFO来构成异步FIFO。

选择MegaWizard Plug-In Manager栏,设置相应参数可以产生异步FIFO,如图3所示。

图3FIFO模块的设计由上图可见,异步FIFO设有8位数据输入和8位数据输出端口,宽度为8bit,深度为1024words,输入端口由写时钟(wrclk)和写使能(wrreq),读时钟(rdclk)和读使能(rdreq)控制,读写时钟在上升沿触发,读写使能信号高电平有效。

具有3固定的标识:rdempty(FIFO空标志)、wrfull(FIFO满标志)和wrusedw[9..0]。

3.2SAA7113与异步FIFO的接口设计异步FIFO缓冲来自SAA7113的数字视频数据流,因此SAA7113需要与FIFO进行接口。

不但要将SAA7113的数字视频输出总线VPO与FIFO的输入数据总线相连,SAA7ll3还要为异步FIFO提供写使能信号和写时钟信号。

SAA7113在每个同步时钟(LLC)的上升沿来到时,将数字视频数据打入VPO总线,所以LLC可以作为FIFO的写时钟信号。

SAA7113没有输出专门的写使能信号,因此,写使能信号必须经过其它变换得到。

阅读资料发现,SAA7113可以通过I2C接口配置。

这样综合考虑后,在系统中用场参考信号(VREF)和行参考信号(HREF)的逻辑与(wrreq=VREF&HREF)关系作为异步FIFO的写使能,按照此办法就可以将有效视频数据写入到异步FIFO中去。

异步FIFO读数据一端由于在FPGA内部,所以实现比较方便。

视频处理器SAA7ll3与FPGA内部实现的异步FIFO连接如图4所示。

图4SAA7113与异步FIFO连接图3.3I2C配置接口模块I2C总线(Inter IC BUS—集成电路芯片间的串行总线)是近年来在微电子通信控制领域广泛采用的一种新型总线标准,能用于替代标准的并行总线。

具有接口线少,控制方式简化,器件封装形式小,通信速率较高等优点。

在I2C总线通过数据线SDA和时钟线SCL对SAA7113芯片进行操作。

初始化之后,启动A/D转换,根据行、场时序图对VPO总线数据进行采样,便可以得到符合标准的数字视频信号。

下图是利用VHDL语言编写的I2C与SAA7113配置接口的顶层模块。

图5I2C模块图3.4VGA显示模块VGA(Video Graphic Array)接口是与显示器进行通信的唯一接口。

通过FPGA器件控制RGB信号、行同步信号、场同步信号等信号,并参照有关标准,最后可以实现对VGA显示器的控制。

设计中的四个CCD摄像头需要显示在同一个显示器上,所以,不可避免的采用了视频画面分割合成技术。

视频合成部分的原理如图6所示。

图6视频合成原理由图6可见,4路视频信号各自经过模/数转化后分别在水平和垂直方向上按2:1的比率压缩取样、存储,而后各样点在同一个时钟驱动下顺序读出,经过数/模转换后即可形成4路画面合成一路的输出信号。

4结束语本文以FPGA作为核心处理器件,设计了全景监控系统的CCD摄像头,利用Quartus II实现了主要模块的软件仿真,论证了方案的可行性。

系统结构简单,硬件流程清晰。

论文创新点:本文针对现有视频监控系统存在监控死角的问题,设计了可以实现全景监控的摄像头,并实现了各监控模块的FPGA设计。

(下转第30页)技术创新Blocks编译器将C源码编译运行生成bin文件,再利用JN5121Flash Programmer编程器将bin文件下载到JN5121-000-M00微处理器中。

2.3.3串口通信与软件模拟实现PC机RS-232C的通信,有两种方法,一种是利用API接口,另一种是使用VC++6.0中的ActiveX控件。

由于使用ActiveX空间简单易用、结构清晰,同时考虑到网络协调器对各种终端设备控制管理的软件模拟。

本文使用VC++6.0的Ac-tiveX控件实现PC机RS-232C的通信,同时使用VC++6.0编程实现环境控制系统终端设备的软件模拟。

3结束语智能化的家居生活离我们越来越近,市场上也已经出现了不少家居智能化产品,但家居智能化仍处于市场开拓阶段,具有巨大的商业前景。

基于ZigBee技术自身的特点,在实现家居智能化中具有得天独厚的优势。

本文研究了ZigBee技术在家居智能环境控制系统(没有包括全部的智能家居设备以及设备全部功能)的应用,证明了采用JN5121-000-M000模块实现的ZigBee星型网络在智能控制系统的可行性和优势,下一步的工作是将该系统连接上具体的环境控制终端设备,使其实用化。