哈工大数电自主实验 数字钟的设计

- 格式:docx

- 大小:112.14 KB

- 文档页数:6

姓名班级学号

实验日期节次教师签字成绩

实验名称简易数字钟的设计

1.实验目的

(1)用计数器相关知识设计一个简易的数字钟,分和秒为六十进制。

(2)了解中规模计数器的应用,通过独立设计和实践掌握74LS90、74LS00等芯片的功能。

(3)锻炼动手能力,通过实际操作巩固所学知识,培养学习兴趣。

2.总体设计方案或技术路线

本实验旨在以计数器为核心,设计和调试出六十进制计数器,并进行两个六十进制计数器的级联。

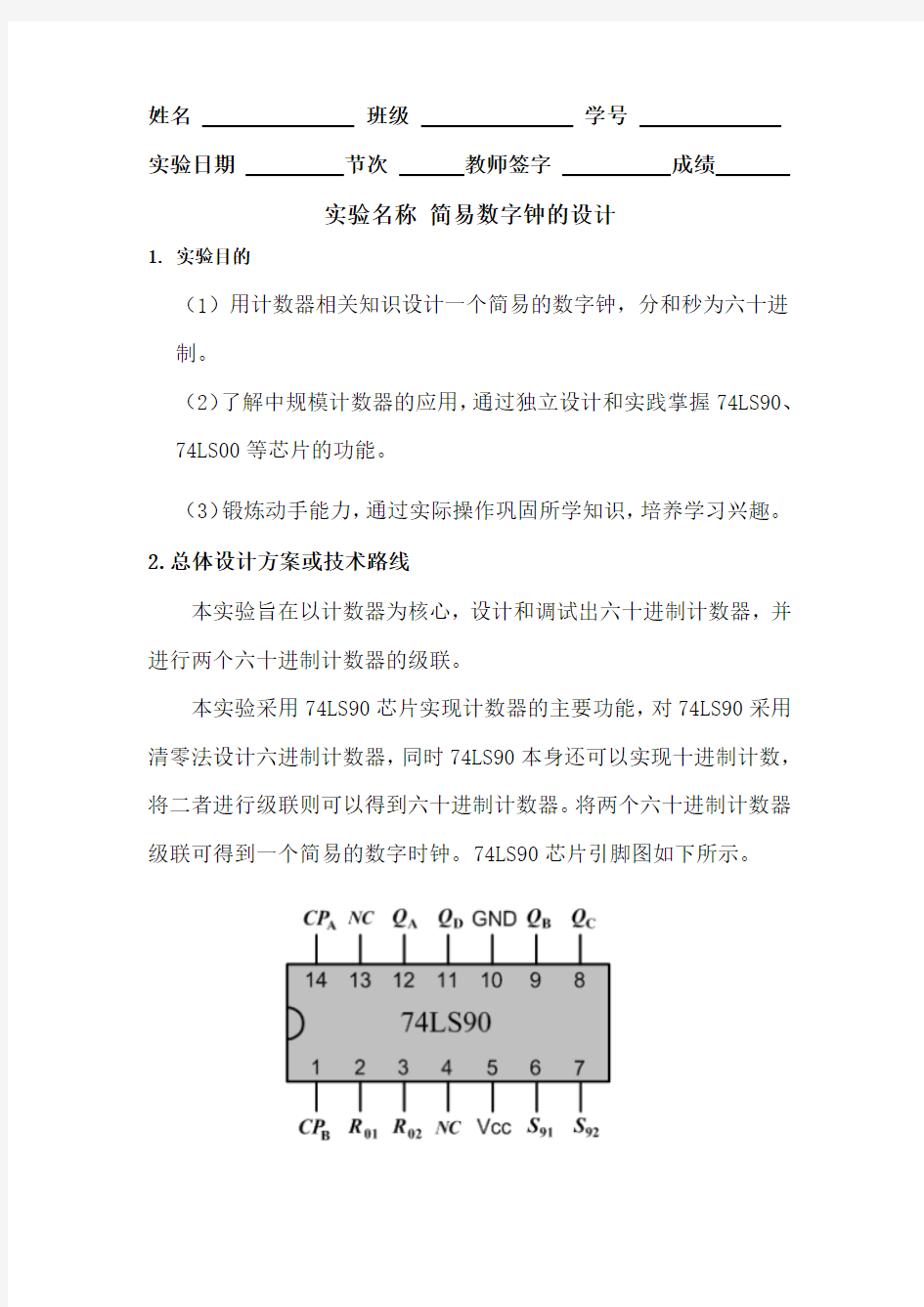

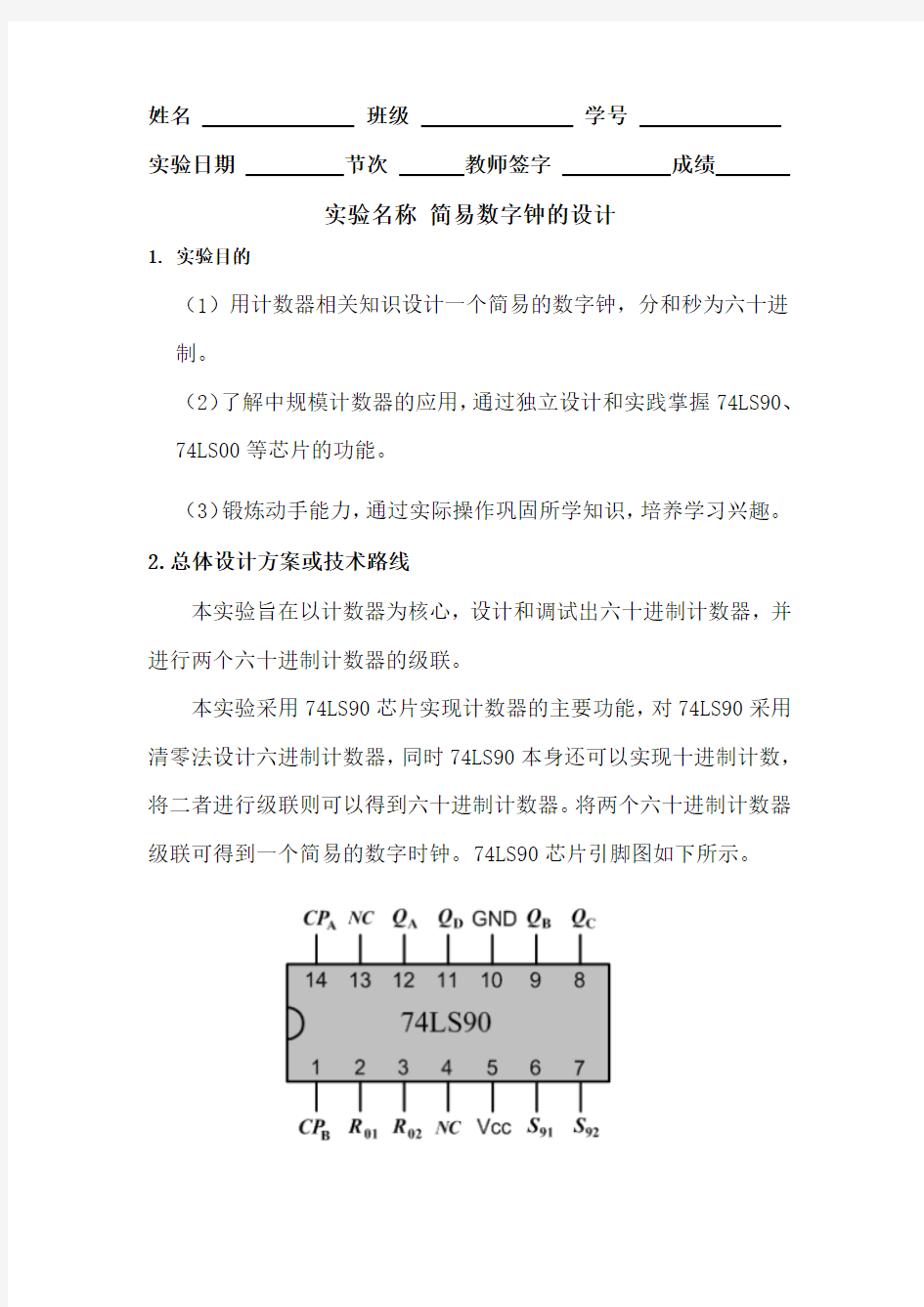

本实验采用74LS90芯片实现计数器的主要功能,对74LS90采用清零法设计六进制计数器,同时74LS90本身还可以实现十进制计数,将二者进行级联则可以得到六十进制计数器。将两个六十进制计数器级联可得到一个简易的数字时钟。74LS90芯片引脚图如下所示。

考虑到74LS90芯片的性能不够稳定,本实验需要两个六十进制计数器,我另外选用了74LS161芯片来设计一个六十进制计数器,然后和74LS90构成的六十进制计数器进行级联,得到数字时钟。

74LS161芯片为集成同步加法计数器,具有清零、置数、保持等功能,其引脚图如下:

用74LS161实现异步进位级联六十进制计数器,高位芯片的时钟端来自低位芯片的输出端Q3,低位芯片采用异步清零法实现十进制计数器,高位芯片也采用同样的方法实现六进制计数器,级联后得到六十进制计数器。

当74LS90所构成六十进制计数器的高位芯片为六进制计数器,当输出为0110时控制清零端进行清零,由0110变为0000,Q3会产生一个下降沿,将Q3端通过一个与非门连到74LS161的CP端,经过与非门后的下降沿变为上升沿,触发74LS161芯计数。

用信号发生器输出周期为1s的方波信号,加到低位74LS90芯片计数器的输入端,即可带动整个时钟开始跳动。分和秒为六十进制,循环计时。

3.实验电路图

U9

4. 仪器设备名称、型号

数字电子技术实验箱直流稳压电源数字万用表

74LS90、74LS161、74LS00芯片导线若干

5.理论分析或仿真分析结果

接通电源后,秒个位显示0到9,秒十位显示0到5,分个位显示0到9,分十位显示0到5。最大输出为59分59秒,之后回0,循环计数。

仿真结果如下图,左上为秒低位,右上为秒高位,左下为分低位,右下为分高位。

6.详细实验步骤及实验结果数据记录(包括各仪器、仪表量程及内阻的记录)

(1)检查导线是否完好

(2)按电路图所示连好电路。

(3)在秒低位的输入连入周期为1s的时钟,观察数码管的输出。是否实现了简易数字时钟的功能。如有错误,用数字万用表检查连线并改正,重新进行调试。

实验结果:

接通电源后和时钟信号输入后,秒个位显示从0到9,秒十位显示0到5,分个位显示0到9,分十位显示0到5。最大输出为59分59秒,之后回0,循环计数。

7.实验结论

用74LS90和74LS161芯片可以设计组合成一个简易数字时钟,两种芯片各自通过清零法实现六进制和十进制的计数器,然后级联为六十进制计数器,最后两个六十进制计数器间进行级联,输入为周期1s的时钟信号时,就可以得到一个简易的数字时钟。

8.实验中出现的问题及解决对策

本次实验并不是一帆风顺的,最初的设计思路是四个芯片全部采用74LS90来实现计数器的功能,后来通过在实验室的调试,发现并不能理想地实现数字钟的功能,经常出现不稳定的情况,向老师询问后得知74LS90的性能不够稳定,后来我尝试将分钟的高、低位芯片换为74LS161,两个六十进制计数器间的连接方式也进行了微调,自

主仿真后,又到实验室进行调试,得到了较为理想的结果。

9.本次实验的收获和体会、对电路实验室的意见或建议

通过本次实验,我的动手能力自主解决问题的能力得到提高,一开始的失败让我认识到探索的过程不是一帆风顺的,遇到挫折时不应气馁,而是努力通过各种方式解决问题。

10.参考文献

杨春玲王淑娟主编《数字电子技术基础》高等教育出版社

廉玉欣主编《电子技术基础实验教程》机械工业出版社