第十二章 触发器习题及答案

- 格式:doc

- 大小:66.00 KB

- 文档页数:6

1第8章 触发器和时序逻辑电路——基本习题解答8.4如果D 触发器外接一个异或门,则可把D 触发器转换成T 触发器,试画出其逻辑图。

解:Q n +1=D=T ⊕Q n 故D =T ⊕Q n 如题8.4图所示。

题8.4.图8.5试用T 触发器和门电路分别构成D 触发器和JK 触发器。

解:(1)T 触发器构成D 触发器Q n +1=D =T ⊕Q n ∴T =D ⊕Q n 如题8.5(a )图所示。

题8.5(a )图(2)T 触发器构成JK 触发器Q n +1=n n n n Q K Q J Q T Q T +=+=T ⊕Q n ∴T =n n n n n KQ Q J Q Q K Q J +=⊕+)(如题8.5(b )图所示。

题8.5(b )图8.6逻辑电路如题8.6图(a )所示,设初始状态Q 1=Q 2=0,试画出Q 1和Q 2端的输出波形。

时钟脉冲C 的波形如题8.6图(b )所示,如果时钟频率是4000Hz ,那么Q 1和Q 2波形的频率各为多少?题8.6图(a ) 题8.6图(b )解:JK 触发器构成了T ′触发器,逻辑电路为异步加法计数,Q 1和Q 2端的输出波形如题CP228.6图(c )所示。

Q 1输出波形为CP 脉冲的二分频,Q 2输出波形为CP 脉冲的四分频。

如果CP 脉冲频率为4000Hz ,则Q 1波形的频率是2000Hz ;Q 2波形的频率是1000Hz 。

题8.6图(c )8.8试列出题8.8图所示计数器的状态表,从而说明它是一个几进制计数器。

题8.8图解:F 0:J 0=21Q Q ,K 0=1F 1:J 1=Q 0,K 1=20=Q 0+Q 2 F 2:QJ 2=K 2=1假设初态均为0,分析结果如题8.8图(a )所示,Q 2Q 1Q 0经历了000-001-010-011-100-101-110七种状态,因此构成七进制异步加法计数器。

题8.8图(a )8.9试用主从型JK 触发器组成两位二进制减法计数器,即输出状态为“11”、“10”、“01”、Q Q Q3“00”。

第12章时序逻辑电路自测题一、填空题1.时序逻辑电路按状态转换情况可分为时序电路和时序电路两大类。

2.按计数进制的不同,可将计数器分为、和N进制计数器等类型。

3.用来累计和寄存输入脉冲个数的电路称为。

4.时序逻辑电路在结构方面的特点是:由具有控制作用的电路和具记忆作用电路组成。

、5.、寄存器的作用是用于、、数码指令等信息。

6.按计数过程中数值的增减来分,可将计数器分为为、和三种。

二、选择题1.如题图12.1所示电路为某寄存器的一位,该寄存器为。

A、单拍接收数码寄存器;B、双拍接收数码寄存器;C、单向移位寄存器;D、双向移位寄存器。

2.下列电路不属于时序逻辑电路的是。

A、数码寄存器;B、编码器;C、触发器;D、可逆计数器。

3.下列逻辑电路不具有记忆功能的是。

A、译码器;B、RS触发器;C、寄存器;D、计数器。

4.时序逻辑电路特点中,下列叙述正确的是。

A、电路任一时刻的输出只与当时输入信号有关;B、电路任一时刻的输出只与电路原来状态有关;C、电路任一时刻的输出与输入信号和电路原来状态均有关;D、电路任一时刻的输出与输入信号和电路原来状态均无关。

5.具有记忆功能的逻辑电路是。

A、加法器;B、显示器;C、译码器;D、计数器。

6.数码寄存器采用的输入输出方式为。

A、并行输入、并行输出;B、串行输入、串行输出;C、并行输入、串行输出;D、并行输出、串行输入。

三、判断下面说法是否正确,用“√"或“×"表示在括号1.寄存器具有存储数码和信号的功能。

( )2.构成计数电路的器件必须有记忆能力。

( )3.移位寄存器只能串行输出。

( )4.移位寄存器就是数码寄存器,它们没有区别。

( )5.同步时序电路的工作速度高于异步时序电路。

( )6.移位寄存器有接收、暂存、清除和数码移位等作用。

()思考与练习题时序逻辑电路的特点是什么?时序逻辑电路与组合电路有何区别?在图12.1电路作用下,数码寄存器的原始状态Q3Q2Q1Q0=1001,而输入数码D3D2D1D0=0110时,在CP的作用下,Q3Q2Q1Q0状态如何变化?题图12.2所示移位寄存器的初始状态为111,画出连续3个C P脉冲作用下Q2Q1Q0各端的波形和状态表。

一、判断题1、用逻辑门构成的各种触发器均属于电平异步时序逻辑电路()2、RS、JK、D和T四种触发器中,唯有RS触发器存在输入信号的约束条件()3、与非门的输入端加有低电平时,其输出端恒为高电平。

()4、数字电路可以分为组合逻辑电路和时序逻辑电路两大类。

()5、时序逻辑电路中存在反馈,其输出不仅取决于当时的输入,还与电路的上一个状态有关。

()6、组合逻辑电路的输出只与当时的输入有关,与电路的上一个状态无关,没有记忆功能。

()7、触发器是时序逻辑电路的基本单元。

()8、时序逻辑电路由组合逻辑电路和存储电路构成。

()9、触发器的反转条件是由触发输入与时钟脉冲共同决定的。

()10、组合逻辑电路任何时刻的输出不仅与该时刻的输入状态有关,还与先前的输出状态有关。

()11、译码器、比较器属于组合逻辑电路。

12、数字电路可分为组合逻辑电路和时序逻辑电路。

13、全加器是实现两个1位二进制数相加并考虑低位进位的逻辑电路。

14、实现同一逻辑功能的逻辑电路可以不同15、译码是编码的逆过程。

16、寻找组合逻辑电路输入输出关系表达式的过程和方法,是组合逻辑电路的设计过程.17、公式化简法有时不容易判断结果是否最简.18、实现同一逻辑功能的电路是唯一的.19、加法器可以有并行进位加法器.20、七段显示译码器有共阳极和共阴极显示器两种接法.21、一个班级有80个学生,现采用二进制编码器对每位学生进行编码,则编码器输出至少5位二进制数才能满足要求22、高电平有效的显示译码器可驱动共阴极接法的数码管23、低电平有效的显示译码器可驱动共阳极接法的数码管24、高电平有效的显示译码器可驱动共阳极接法的数码管25、低电平有效的显示译码器可驱动共阴极接法的数码管26、同一CP控制各触发器的计数器称为异步计数器()27、各触发器的信号来源不同的计数器称为同步计数器()28、1个触发器可以存放2个二进制数()29、D触发器只有时钟脉冲上升沿有效的品种。

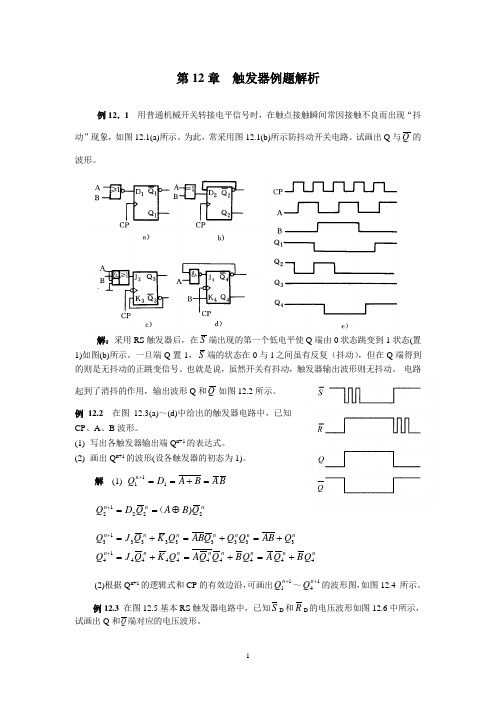

第12章 触发器例题解析例12.1 用普通机械开关转接电平信号时,在触点接触瞬间常因接触不良而出现“抖动”现象,如图12.1(a)所示。

为此,常采用图12.1(b)所示防抖动开关电路。

试画出Q 与Q 的波形。

解:采用RS 触发器后,在S 端出现的第一个低电平使Q 端由0状态跳变到1状态(置1)如图(b)所示。

一旦端Q 置1,S 端的状态在0与l 之间虽有反复(抖动),但在Q 端得到的则是无抖动的正跳变信号。

也就是说,虽然开关有抖动,触发器输出波形则无抖动。

电路起到了消抖的作用,输出波形Q 和Q 如图12.2所示。

例12.2 在图12.3(a)~(d)中给出的触发器电路中,已知CP 、A 、B 波形。

(1) 写出各触发器输出端Q n+1的表达式。

(2) 画出Q n+1的波形(设各触发器的初态为1)。

解 (1) B A B A D Q n =+==+111n n n Q B A Q D Q 22212)⊕==+(n n n n n n n n nn n n n n n QB Q A Q B Q Q A Q K Q J Q Q AB Q Q Q AB Q K Q J Q 444444444143333333313+=+=+=+=+=+=++ (2)根据Q n+1的逻辑式和CP 的有效边沿,可画出11+n Q ~14+n Q 的波形图,如图12.4 所示。

例12.3 在图12.5基本RS 触发器电路中,已知S D 和R D 的电压波形如图12.6中所示,试画出Q 和端对应的电压波形。

解:这是一个用已知的R D和S D的输入状态确定Q和Q输出状态的问题。

只要根据每个时间区间里R D和S D的状态去查触发器的特性表,即可找出Q和Q的相应状态输出,并画出它们的波形图。

另外,对较简单的电路,根据电路图逐一分析也能直接画出Q和Q端的波形图。

从12.6的波形图上可以看到,当在输入端出现R D =S D =0的状态时,如果S D(或R D)首先回到了高电平,那么触发器的次态仍然是可以确定的。

触发器练习题一、填空题1、触发器具有 个稳定状态,在输入信号消失后,它能保持 。

2、在基本RS 触发器中,输入端D R 或D R 能使触发器处于 状态,输入端D S 或D S 能使触发器处于 状态。

3、同步RS 触发器状态的改变是与 信号同步的。

4、在CP 脉冲和输入信号作用下,JK 触发器能够具有 、 、 、和 的逻辑功能。

5、对于JK 触发器,当CP 脉冲有效期间,若J=K=0时,触发器状态 ;若K J =时,触发器 或 ;若J=K=1时,触发器状态 。

6、与主从触发器相比, 触发器的抗干扰能力较强。

7、对于JK 触发器,若J=K ,则可完成 触发器的逻辑功能。

8、对于JK 触发器,若K J =,则可完成 触发器的逻辑功能。

二、判断题1、触发器有两个稳定状态,一个是现态,一个是次态。

( )2、触发器有两个稳定状态,在外界输入信号的作用下,可以从一个稳定状态转变为另一个稳定状态。

( )4、同步D 触发器的Q 端和D 端的状态在任何时刻都是相同的。

( )5、同一逻辑功能的触发器,其电路结构一定相同。

( )6、仅具有反正功能的触发器是T 触发器。

( )三、选择题1、对于触发器和组合逻辑电路,以下( )的说法是正确的。

A 、两者都有记忆能力B 、两者都无记忆能力C 、只有组合逻辑电路有记忆能力D 、只有触发器有记忆能力2、对于JK 触发器,输入J=0、K=1,CP 脉冲作用后,触发器的1+n Q 应为( )。

A 、0B 、1C 、可能是0,也可能是1D 、与n Q 有关3、JK 触发器在CP 脉冲作用下,若使n n Q Q =+1,则输入信号应为( )。

A 、1==K JB 、Q K Q J ==,C 、Q K Q J ==,D 、0==K J4、具有“置0” “置1” “保持” “翻转”功能的触发器叫( )。

A 、JK 触发器B 、基本RS 触发器C 、同步D 触发器 D 、同步RS 触发器5、边沿控制触发的触发器的触发方式为( )。

第12章习题解答12-1 已知由与非门组成的基本RS触发器和输入端D R、D S的波形如题图12-1所示,试对应地画出Q 和Q的波形,并说明状态“不定”的含义。

题图12-1解:12.2 已知可控RS触发器CP、R和S的波形如题图12-2所示,试画出输出Q的波形。

设初始状态分别为0和1两种情况。

题图12-2解:12-3 在主从结构的JK触发器中,已知CP、J、K的波形如题图12-3所示,试画出Q端的波形。

设初始状态Q=0。

题图12-3解:12-4 维持阻塞型D触发器的输入D和时钟脉冲CP的波形如题图12-4所示,试画出Q端的波形。

设初始状态Q = 0。

题图12-4解:12-5 在T触发器中,已知T和CP的波形如题图12.5所示,试画出Q端的波形。

设初始状态Q= 0。

题图12-5解:12-6 写出题图12-6所示电路的逻辑关系式,说明其逻辑功能。

题图12-6解:逻辑关系为:Q D AQ BQ==+所以其功能为JK触发器。

12-7 如题图12-7所示的电路和波形,试画出D端和Q端的波形。

设初始状态Q= 0。

题图12-7解:12-8 将主从型JK触发器转换为T'触发器有几种方案?画出外部连线图。

解:12-9 电路如题图12-9所示。

画出Q0端和Q1端在六个时钟脉冲CP作用下的波形。

设初态Q1=Q0= 0。

题图12-9解:12-10 用题图12.10(a)所给器件构成电路,并在示波器上观察到如图12.10(b)所示波形。

试问电路是如何连接的?请画出逻辑电路图。

(a) (b)题图12-10解:12-11 已知如题图12.11(a)所示电路的各输入端信号如题图12-11(b)所示。

试画出触发器输出端Q0和Q1的波形。

设触发器的初态均为0。

(a) (b)题图12-11解:12-12 已知电路和时钟脉冲CP及输入端A的波形如题图12-12所示,试画出输出端Q、1Q的波形。

假定各触发器初态为1。

(a ) (b )题图12-12解:12-13 已知题图12-13(a )所示电路中输入A 及CP 的波形如题图12-13(b )所示。

[复习提问]1.与非门的逻辑功能。

2.逻辑门电路和特点。

[新课导入]前面的课程中,我们学习了基本门电路,基本门电路的简单组成组合逻辑电路。

组合逻辑电路的工作特点是输出状态直接受输入信号控制。

输入信号消失了,相应的输出信号也就消失了。

因此,没有记忆功能。

而利用集成门电路也可以组成具有记忆功能的触发器,其电路的输出不仅与输入有关,还与电路原来状态有关。

当输入信号消失后,输出仍保持原来状态不变。

能记忆前一时刻的状态。

因此,人们称之具有记忆功能,这是集成触发器的工作特点。

[新授内容]§12.1集成触发器的基本形式一、什么叫触发器及其状态是指一种具有两种稳定状态的电路。

可分别代表寄存二进制1或0。

当外加触发信号时,触发器能从一种稳态翻转到另一种稳态,即它能按逻辑功能在1、0两数码之间变化。

二、基本RS触发器1.电路组成:将G1的输出耦合到G2的输入,而将G2的输出耦合到G1输入的两个与非门。

将两个与非门交叉耦合。

2.逻辑功能:R 、S 的不同状态组合。

Q n+1的状态。

置0端,复位端。

R 端为0,S 端1时,Q =1而Q=0故叫复位端。

记忆功能:G2输出低电平耦合到G1的输入端,即使端信号撤除,G1输出端仍维持在高电平上,从而实现了记忆功能。

置位端,置1端S触发器Q 端的状态为触发器的状态。

Q 和Q 的关系始终是互补的:当D R =D S =0时,Q=Q =1,撤除D R 、D S 信号后,两个与非门的输出端状态不能肯定。

故这种情况是不能使用的。

翻转:是指在外信号作用下触发器的状态转换的过程。

(1)触发脉冲:外加信号:D R 、D S(2) 正、负触发脉冲及其表示:有无小圆圈。

三、同步RS 触发器 1.组成:(1)时钟脉冲CP 的作用。

主控脉冲(2)G3、G4的作用。

2.钟控同步触发器的工作原理 (1)CP=0时——维持原状 (2)CP=1,R 、S 决定Q 、Q3.逻辑符号:注意:(1)R 、S 无小圆圈、说明是正脉冲触发(CP 上升沿)触发有效。

第十二章 触发器习题及答案

一、填空题

1、 触发器有_____个稳态,存储8位二进制信息要______个触发器。

2、 一个基本RS 触发器在正常工作时,它的约束条件是R + S =1,则它不允许输入S =____

且R =____的信号。

3、 触发发有两个互补的输出端Q 、Q ,定义触发器的1状态为Q=___________,0状态为

_________可见,触发器的状态指的是______端的状态。

4、 一个基本RS 触发器在正常工作时,不允许输入R=S=1的信号,因此它的约束条件是

___________。

5、 在一个CP 脉冲作用下,引起触发器两次或多次翻转的现象称为触发器的__________ ,

触发方式为__________式或_____________的触发器不会出现这种现象。

6、 触发器是一种由门电路构成并具有两个稳定状态的电路,两个稳定状态分别用来表示和

寄存二进制数码______和______。

7、按逻辑功能不同可分为_______触发器______触发器______触发器_____触发器和_____触发器等。

8、按电路结构不同,可分为______触发器,________触发器,________触发器,________触发器等。

9、描述触发器功能的方法有:__________、____________、__________、______________和________________。

10、电路在没有外加信息触发时保持某一状态不变,而这种状态叫____________。

11、防止空翻的触发器结构有_________________________。

12、触发器的基本性质有_____________________________________________。

13、从结构上看,时钟同步R-S 触发器是在R-S 触发器的基础上增加了____________构成的。

14、比结构上看主从结构的触发器是由主触发器和___________组成。

其工作时受时钟脉冲CP 控制,CP=1时,_______________CP ;=0时,_______________。

15、从CP 脉冲前沿到达时起到触发器翻转完毕的时间称为_______________

二、 选择题

1、D 触发器的特征方程是( )

A 、1n Q D +=

B 、1n n Q DQ +=

C 、1n n Q

D Q +=⊕

2、仅具有“置0”、“置1”功能的触发器叫( )

A 、JK 触发器

B 、RS 触发器

C 、

D 触发器

3、仅具有“翻转”功能的触发器叫( )

A 、JK 触发器

B 、'T 触发器

C 、

D 触发器

4、JK 触发器用作'T 触发器时,控制端J 、K 正确接法是( )

A 、n J Q = n

K Q = B 、1J K == C 、n J K Q ==

5、触发器由门电路组成,但它不同门电路的功能,主要特点是( )

A 、和门电路功能一样

B 、具有记忆功能

C 、没有记忆功能

6、TTL 型和CMOS 型触发器使用过程中方法正确的是( )

A 、电源电压一样时,可以兼容;但TTL 型不用的控制端可以悬空为“1”;CMOS 型的不用控制端不可悬空,必须通过电阻接电源为“1”

B 、只要电源电压一致可随意使用

C 、电源电压不同也可以互换使用

7、N个触发器可以构成能寄存()位十进制数码的寄存器。

A、N-1

B、N

C、N+1

D、2N

8、在下列触发器中,有约束条件的是()。

A、主从JK F/F

B、主从D F/F

C、同步RS F/F

D、边沿D F/F

9、一个触发器可记录一位二进制代码,它有()个稳态。

A、0

B、1

C、2

D、3

10、存储8位二进制信息要()个触发器。

A、2

B、4

C、6

D、8

11、对于T触发器,若原态Q n=0,欲使新态Q n+1=1,应使输入T=()。

(多选)

A、0

B、1

C、Q

D、Q

12、对于T触发器,若原态 Q n=1,欲使新态Q n+1=1,应使输入T=()。

(多选)

A、0

B、1

C、Q

D、Q

13、对于JK触发器,若J=K,则可完成()触发器的逻辑功能。

A、RS

B、D

C、T

D、T1

14、欲使D触发器按Q n+1=Q n 工作,应使输入D=()。

A、0

B、1

C、Q

D、 Q

15、下列触发器中,没有约束条件的是()。

A、基本RS触发器

B、主从RS触发器

C、同步RS触发器

D、边沿D触发器

16、边沿式D触发器是一种()稳态电路。

A、元

B、单

C、双

D、多

17、为实现将JK触发器转换为D触发器,应使()。

A、J=D,K=D

B、K=D,J=D

C、J=K=D

D、J=K=D

18、描述触发器的逻辑功能的方法有()。

(多选)

A、状态转换真值表

B、特性方程

C、状态转换图

D、状态转换卡诺图

19、下列触发器中,克服了空翻现象的有()。

(多选)

A、边沿D触发器

B、主从RS触发器

C、同步RS触发器

D、主从JK触发器

20、欲使JK触发器按Q n+1=0工作,可使JK触发器的输入端()。

(多选)

A、J=K=1

B、J=Q,K=Q

C、J=Q,K=1

D、J=0,K=1

三、判断题。

1、因为触发器具有记忆功能,所以可作寄存器。

()

2、D触发器的特性方程为Q n+1=D,与Q n无关,所以它没有记忆功能。

()

3、RS触发器的约束条件RS=0表示不允许出现R=S=1的输入。

()

4、同步触发器存在空翻现象,而边沿触发器和主从触发器克服了空翻。

()

5、主从JK触发器,边沿JK触发器和同步JK触发器的功能完全相同。

()

6、若要实现一个可暂停的一位二进制计数器,控制信号A=0计数,A=1保持,可选用T触发器,且令T=A。

()

7、由两个TTL或非门构成的基本RS触发器,当R=S=0时,触发器的状态为不定。

()

8、边沿JK触发器,在CP为高电平期间,当J=K=1时,状态翻转一次。

()

9、触发器的两个输出端Q和Q分别表示触发器的两种不同的状态。

()

10、在门电路基础上组成的触发器,输入信号对触发器状态,影响随输入信号的消失而消失。

()

四、解答题

1、图12-1a中,已知D、JK触发器都是边沿触发器,起始状态为0,且已知A、B、C波形

如图12-1b所示,试画出各触发器对应Q端的波形。

2、边沿J—KFF CT4112组成图12-2a所示电路,图12-2b为输入波形。

试画出Q1、Q2、Z 端的波形。

设Q1、Q2的初态为0。

3、图a 所示的D触发器的CP和D信号初态为1,请画出输出端Q的波形。

T

Q

答案

选择题

1 A

2 C

3 B

4 B

5 B

6 A

7 B

8 C

9 C 10 D 11B,D 12 A,D 13

C 14 C 15

D 16 C 17 A 18 A,B,C,D 19 A,B,D 20 B,C,D

填空题

1、2、8 2、0、0 3、Q=1、Q=0 、Q 4、RS=0 5、空翻、主从式、边沿式 6、

0、1 7、RS、JK、D、T、T′ 8、基本、同步、主从、维持阻塞 9、逻辑真值表、特征方程、驱动表、状态图和时序图 10、稳态 11、主从结构,维持阻塞结构12、有两个稳态、在触发信号作用下可实现状态的改变、有记忆功能 13、两个控制门

14、从触发器、接收输入信号、触发器翻转 15、传输时间t p。

三、判断题

1√ 2× 3√ 4√ 5√ 6× 7× 8× 9√ 10×

三、分析题

1、

2、

3。