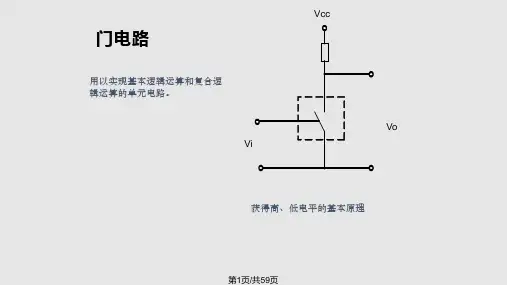

基本开关电路

• MOS管的开关特性

Vi

Vo

第4页/共59页

§3-1 集成逻辑电路的电气特性

集成电路的工艺: TTL: 晶体管-晶体管逻辑 (标准,S,LS,AS,ALS,F)

速度快、电源电压:典型值5V,一般4.5~5.5V 肖特基--提高电路工作速度的一种电路结

构的名称。 MOS:金属-氧化物-半导体逻辑

1. 输出电压与输入电压

输出低电平VOL:输出低电平时的最高电压。 输出高电平VOH:输出高电平时的最低电压。 输入高电平VIH(Von开门电平):输入高电平时的最低电压。 输入低电平VIL(VOFF关门电平):输入低电平时的最高电压。 高电平抗干扰容限VNH:VNH=VOH-VIH 低电平抗干扰容限VNL:VNH=VIL-VOL 阈值电平Vth: 粗略估算用。

第28页/共59页

§3-1-5 使用逻辑门的几个问题

1、输入脚多余: 与:多余脚接逻辑高或输入并联。 或:多余脚接逻辑低或输入并联。

2、输入脚不足: 改变逻辑或用门电路扩展。

3、扇出系数: 采用功率门电路或改电路。

F A B B C B D A B B ( C D ) A B B C A D B B CD

cd第29页共59页332常用组合逻辑模块常用组合逻辑模块321四位并行加法器322数值比较器323译码器324数据选择器325总线收发器326其他常用器件一个模块完成某个常用的特定的功能如加法器数值比较器译码器编码器及数据比较第30页共59页一4位加法器逻辑图第31页共59页图113加法器数字设计引论11数制第32页共59页逻辑图数字设计引论23逻辑图第33页共59页位加法器数字设计引论26应用实例第34页共59页二加法器的级连四位加法器级连成八位加法器第35页共59页用4位加法器构成余3码到8421码的转换器第36页共59页一位bcd码加法器第37页共59页图1231位bcd码加法器方框数字设计引论12二值编码第38页共59页4位比较器低位比较结果级连一数值比较器逻辑图一数值比较器逻辑图第39页共59页第40页共59页4位比较器组成8位比较器第41页共59页交通控制灯电路的一部分第42页共59页一变量译码器二变量译码器的扩展三变量译码器实现组合逻辑函数四变量译码器构成数据分配器五显示译码器第43页共59页一变量译码器一变量译码器24译码器38译码器38译码器功能表ststststststststen第45页共59页二变量译码器的扩展二变量译码器的扩展74138树形扩展第46页共59页三变量译码器实现组合逻辑函数三变量译码器实现组合逻辑函数cicocico例1