FPGA实现嵌入式系统

- 格式:pdf

- 大小:265.30 KB

- 文档页数:4

嵌入式系统原理与接口技术fpga

嵌入式系统原理与接口技术FPGA

嵌入式系统是嵌入在其他设备中的计算机系统,由于其小尺寸、低功耗、高可靠性和定制化等特性,被广泛应用于计算机控制、通讯、汽车、医疗、航空航天等领域。

而FPGA作为可编程逻辑器件,其重要性与广泛程度在嵌入式系统中也不言而喻。

FPGA的原理是通过可编程逻辑单元、存储单元和I/O模块等组件构成,可以实现针对特定应用的定制化逻辑电路。

与ASIC相比,FPGA 一方面具有定制化灵活、开发效率高等优点,另一方面也存在着资源消耗较高、性能等方面的局限性。

因此,在嵌入式系统中,FPGA与MCU、DSP等处理器结合使用,充分发挥各自的优势。

FPGA的接口技术也是嵌入式系统中的重要组成部分。

常见的接口技术包括SPI、I2C、UART等。

SPI是一种串行传输接口,可以实现多个设备的数据同步传输;I2C是一种串行通信总线,可以实现多个设备之间的数据传输,以及设备之间的控制与管理;UART是一种异步串行通信接口,可以实现设备之间的数据传输与控制。

在实际应用时,需要根据不同的应用场景选择合适的接口技术,以保证系统的稳定性和可靠性。

总之,嵌入式系统与FPGA的结合,为物联网、智能家居、智能交通等领域带来了更加智能化和高效化的解决方案。

未来,随着技术的不断发展和创新,嵌入式系统与FPGA的应用前景必将更加广阔。

关键字:嵌入式系统设计ARM FPGA多功能车辆总线Multifunction Vehicle Bus 在计算机、互联网和通信技术高速发展的同时,嵌入式系统开发技术也取得迅速发展,嵌入式技术应用范围的急剧扩大.本文介绍了一种基于ARM和FPGA,从软件到硬件完全自主开发多功能车辆总线(Multifunction Vehicle Bus)MVB??B嵌入式系统的设计和实现。

系统设计和实现通常来说,一个嵌入式系统的开发过程如下:1.确定嵌入式系统的需求;2.设计系统的体系结构:选择处理器和相关外部设备,操作系统,开发平台以及软硬件的分割和总体系统集成;3.详细的软硬件设计和RTL代码、软件代码开发;4.软硬件的联调和集成;5.系统的测试。

一、步骤1:确定系统的需求:嵌入式系统的典型特征是面向用户、面向产品、面向应用的,市场应用是嵌入式系统开发的导向和前提。

一个嵌入式系统的设计取决于系统的需求。

1、MVB总线简介列车通信网(Train Communication Network,简称TCN)是一个集整列列车内部测控任务和信息处理任务于一体的列车数据通讯的IEC国际标准(IEC-61375-1), 它包括两种总线类型绞线式列车总线(WTB)和多功能车厢总线(MVB)。

TCN在列车控制系统中的地位相当与CAN总线在汽车电子中的地位。

多功能车辆总线MVB是用于在列车上设备之间传送和交换数据的标准通信介质。

附加在总线上的设备可能在功能、大小、性能上互不相同,但是它们都和 MVB总线相连,通过MVB总线来交换信息,形成一个完整的通信网络.在MVB系统中,根据IEC-61375-1列车通信网标准, MVB总线有如下的一些特点:拓扑结构:MVB总线的结构遵循OSI模式,吸取了ISO的标准。

支持最多4095个设备,由一个中心总线管理器控制。

简单的传感器和智能站共存于同一总线上。

数据类型:MVB总线支持三种数据类型:a.过程数据:过程变量表示列车的状态,如速度、电机电流、操作员的命令。

FPGA设计与嵌入式硬件开发课程大纲【大纲】一、课程介绍A. 课程名称B. 课程目标C. 参考教材D. 课程安排二、FPGA基础知识A. FPGA概述1. 什么是FPGA2. FPGA的应用领域B. FPGA的工作原理1. CLB、IOB、BRAM等模块的介绍2. FPGA的内部结构C. FPGA的设计流程1. 设计准备2. RTL设计3. 综合与布局布线4. 下载与调试三、硬件描述语言A. 了解Verilog HDL1. Verilog HDL的基本语法2. 模块化设计与层次化设计3. 时钟与时序控制B. Verilog的高级特性1. 组合逻辑与时序逻辑2. 有限状态机设计3. 生成器与实例化四、FPGA开发工具A. 开发环境介绍1. FPGA开发板的选择与使用2. FPGA开发软件的选择与使用B. Xilinx Vivado的基本操作1. 工程的创建与配置2. 约束文件的编写与调试3. 综合与实现过程的掌握4. Bitstream的生成与下载五、嵌入式硬件开发A. 嵌入式硬件开发概述1. 嵌入式系统的定义与特点2. 嵌入式硬件设计的关键问题B. 嵌入式处理器的选择与配置1. ARM Cortex-M系列处理器简介2. 嵌入式处理器体系结构与指令集3. 外设与总线的配置与控制C. 嵌入式硬件设计流程1. 系统级设计与模块化设计2. 基于FPGA的SoC设计3. 硬件/软件协同开发六、实践项目A. FPGA设计项目1. 基础的组合逻辑与时序逻辑设计2. 有限状态机设计与控制器实现3. 基于FPGA的外设接口设计B. 嵌入式硬件项目1. 基于ARM Cortex-M处理器的外设控制2. 嵌入式系统级设计与调试七、考核方式与评价标准A. 课堂表现与作业质量B. 实践项目的完成情况C. 期末考试成绩八、参考资料A. 课程教材及参考书目B. 相关学术论文与期刊以上为《FPGA设计与嵌入式硬件开发课程大纲》的内容,请参考。

基于Xilinx FPGA特点的嵌入式Bootloader设计与实现Bootloader程序是指嵌入式系统在正常工作之前,配置系统运行环境,引导操作系统的一小段程序。

通过这段程序,我们可以初始化硬件设备、建立内存空间映射等,从而将系统的软硬件环境带到一个合适的环境,为系统的正常运行做好准备。

对于不使用操作系统的嵌入式系统而言,应用程序的运行同样也需要依赖一个准备好的软、硬件环境,因此从这个意义上来讲,BootLoader程序对于嵌入式系统是必需的。

BootLoader程序与硬件系统密切相关,依赖于具体的嵌入式板级硬件设备的配置。

比如板卡的硬件地址配置、微处理器的类型和其他外设的类型等。

也就是说,即使是基于相同嵌入式微处理器构建的不同嵌入式目标板,BootLoader程序也不是完全通用的,仍需要修改其源程序。

与ARM等嵌入式系统的启动过程所不同的是,FPGA必须先将内部硬件逻辑配置完成之后,才能运行程序代码。

虽然可以直接将程序代码例化到片内BRAM中,但是由于FPGA 内部的BRAM资源有限,而且硬件逻辑配置时就会占用其中的资源,因此遇到大型系统设计时(例如带有TCP/IP协议的大型程序),片内BRAM资源不够,就必须使用外部的RAM来储存程序代码和堆栈,这就需要设计Bootloader程序来完成用户程序的引导。

本文结合Xilinx FPGA的特点详细给出了Bootloader程序设计和实现过程。

本设计所实现的Bootloader程序是在FPGA硬件配置完毕之后在MicroBlaze软核处理器上运行的一段启动代码,用来把Flash中的用户程序传输至外部RAM,并引导系统从用户程序中开始运行。

一、系统硬件平台的实现本设计的实现是以Xilinx公司的Spartan-3E FPGA、STMicroelectronics公司的SPI串行Flash(M25P16)、Micron Technology公司的DDR SDRAM (MT46V32M16)为主要器件构建硬件平台。

简单的说,嵌入式是嵌入式系统的简称,所谓嵌入式系统是指嵌入到应用对象中的专用计算机系统。

这里的对象就是指产品,比如日常使用的冰箱、空调、洗衣机,或者手机、游戏机等。

这些产品中都有计算机系统,这类计算机系统就是嵌入式计算机系统。

至于单片机、ARM、FPGA、DSP等都是实现嵌入式系统的硬件平台。

根据对象体系的功能复杂性和计算处理复杂性,提供的不同选择。

对于简单的家电控制嵌入式系统,采用简单的8位单片机就足够了,价廉物美,对于手机和游戏机等,就必须采用32位的ARM和DSP等芯片了。

FPGA是一种更偏向硬件的实现方式。

所以要学习嵌入式,要从单片机开始,然后学习ARM和DSP之类我个人认为你说的刚好相反。

不是别的,FPGA就是自己构建硬件电路,而DSP有内嵌的硬件乘法模块。

单片机应该是偏软的,比如说吧, 现在基本上可以完全用高级语言(如C)来编写单片机程序,而DSP 确还是要用到汇编。

你要知道,汇编可以说就是硬件语言。

呵呵,希望对你有用————ARM、FPGA和DSP的特点和区别是什么?发布时间:2009-5-8 14:25 发布者:ARM 阅读次数:833 DSP(digital singnal processor)是一种独特的微处理器,有自己的完整指令系统,是以数字信号来处理大量信息的器件。

一个数字信号处理器在一块不大的芯片内包括有控制单元、运算单元、各种寄存器以及一定数量的存储单元等等,在其外围还可以连接若干存储器,并可以与一定数量的外部设备互相通信,有软、硬件的全面功能,本身就是一个微型计算机。

DSP采用的是哈佛设计,即数据总线和地址总线分开,使程序和数据分别存储在两个分开的空间,允许取指令和执行指令完全重叠。

也就是说在执行上一条指令的同时就可取出下一条指令,并进行译码,这大大的提高了微处理器的速度。

另外还允许在程序空间和数据空间之间进行传输,因为增加了器件的灵活性。

其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。

《基于ARM+FPGA的嵌入式安全PLC设计与实现》一、引言随着工业自动化和智能化的快速发展,可编程逻辑控制器(PLC)作为工业控制的核心设备,其安全性和可靠性显得尤为重要。

传统的PLC设计往往面临计算能力有限、扩展性不足以及安全性不够高等问题。

为了解决这些问题,本文提出了一种基于ARM+FPGA的嵌入式安全PLC设计与实现方案。

该方案结合了ARM的高性能计算能力和FPGA的并行处理能力,实现了高效率、高安全性的PLC控制。

二、系统设计1. 硬件设计本系统采用ARM+FPGA的异构计算架构。

ARM作为主控制器,负责运行操作系统和高级算法;FPGA则用于实现高速并行数据处理和接口控制。

此外,系统还包括电源模块、存储模块、通信接口等。

(1)ARM处理器选择选用高性能的ARM Cortex-A系列处理器,具有高计算能力、低功耗和良好的扩展性。

(2)FPGA选择选用适合工业应用的FPGA芯片,具有高并行处理能力、低延迟和高可靠性。

(3)存储模块设计采用高速、大容量的存储设备,如SSD或DRAM,以满足系统对数据存储和读取的需求。

2. 软件设计软件设计包括操作系统、通信协议、安全机制等。

(1)操作系统采用实时操作系统(RTOS),以保证系统的实时性和稳定性。

(2)通信协议支持多种工业通信协议,如EtherNet/IP、Modbus等,以满足不同工业应用的需求。

(3)安全机制采用加密、认证、访问控制等安全机制,保证系统的数据安全和防止未经授权的访问。

三、关键技术实现1. ARM与FPGA的协同工作通过桥接电路实现ARM与FPGA的协同工作。

ARM负责任务调度和数据处理,FPGA负责高速并行数据处理和接口控制。

两者协同工作,实现高效的数据处理和控制。

2. 数据加密与认证采用高级加密标准(AES)对数据进行加密,保证数据在传输和存储过程中的安全性。

同时,采用数字签名技术对数据进行认证,防止数据被篡改。

3. 访问控制与权限管理通过访问控制和权限管理机制,对系统资源进行保护,防止未经授权的访问和操作。

基于FPGA的嵌入式系统的研究及设计的开题报告一、研究背景及意义随着信息技术的发展,嵌入式系统在社会生产、科学技术等各个领域中得到了广泛应用,其中基于FPGA(Field-Programmable Gate Array)的嵌入式系统在高性能、低功耗、可重构性等方面具有独特的优势,日益成为研究的热点和应用的重要方向。

本课题旨在研究基于FPGA的嵌入式系统的设计及其应用,在对现有相关技术和理论进行深入分析的基础上,结合具体应用场景进行相关系统设计与实践开发,探索FPGA嵌入式系统的优化设计和功能实现,推动信息技术的发展与应用。

二、研究内容及目标本课题的主要研究内容包括以下几个方面:1、基于FPGA的嵌入式系统设计理论研究,包括FPGA基础概念、数字电路设计、EDA工具等相关理论技术的研究。

2、基于ARM处理器的FPGA嵌入式系统架构设计与优化,主要涉及ARM处理器架构、信号处理、寄存器设计等。

3、基于FPGA的嵌入式系统开发及应用实践,实现各类控制、通信、图像处理等应用场景。

本课题的主要研究目标包括以下几个方面:1、深入掌握基于FPGA的嵌入式系统的设计原理和关键技术,具备开发和应用FPGA嵌入式系统的能力。

2、基于ARM处理器的FPGA嵌入式系统架构设计与优化,在提高系统性能和功耗效率的同时,实现系统的实时控制和数据处理等功能。

3、基于FPGA的嵌入式系统开发及应用实践,实现控制、通信、图像处理等应用场景,验证系统性能和可靠性。

三、研究方法和技术路线本课题采用文献研究法、实验研究法和案例研究法相结合的方式进行研究,具体技术路线如下:1、文献研究法。

通过查阅相关文献资料和参考书籍,深入研究FPGA的基础理论、数字电路设计和ARM处理器的嵌入式系统架构等领域的最新研究成果,了解国内外相关领域的发展动态及趋势。

2、实验研究法。

基于FPGA平台,搭建实验环境并进行算法实现、实际调试和性能测试,对系统进行不断优化和完善,验证系统设计的可行性和有效性。

《基于ARM+FPGA的嵌入式安全PLC设计与实现》一、引言随着工业自动化程度的不断提高,可编程逻辑控制器(PLC)作为工业控制的核心设备,其安全性和可靠性显得尤为重要。

传统的PLC设计多采用单一处理器架构,难以满足日益增长的安全性和性能需求。

因此,本文提出了一种基于ARM+FPGA的嵌入式安全PLC设计与实现方案,旨在提高PLC的安全性和性能。

二、系统设计1. 硬件设计本设计采用ARM+FPGA的异构计算架构,其中ARM作为主处理器,负责系统的控制和数据处理;FPGA作为协处理器,负责高速信号处理和实时控制。

在硬件设计上,主要考虑了以下方面:(1)处理器选择:选用高性能的ARM处理器和FPGA芯片,以保证系统的计算能力和数据处理速度。

(2)接口设计:设计丰富的接口,包括通信接口、存储接口、电源接口等,以满足系统与外界的通信和数据存储需求。

(3)功耗控制:优化系统功耗设计,降低系统能耗,提高系统可靠性。

2. 软件设计软件设计主要包括操作系统、通信协议、安全机制等方面的设计。

本设计采用实时操作系统(RTOS)作为系统的软件平台,以支持多任务处理和实时控制。

同时,设计了自定义的通信协议,以保证数据传输的可靠性和实时性。

在安全机制方面,采用了加密、认证、访问控制等安全措施,以提高系统的安全性。

三、关键技术实现1. ARM与FPGA的协同工作ARM与FPGA的协同工作是本设计的关键技术之一。

通过设计合理的任务划分和调度算法,实现ARM与FPGA之间的协同计算和数据处理,以提高系统的整体性能。

2. 安全机制的实现安全机制的实现是保证系统安全性的重要措施。

本设计采用了加密、认证、访问控制等安全措施,对数据进行加密传输和存储,对用户进行身份认证和访问控制,以防止未经授权的访问和数据泄露。

3. 实时性保障实时性是PLC的重要性能指标之一。

本设计通过优化任务调度算法、提高数据处理速度、优化通信协议等措施,保证系统的实时性,以满足工业控制的需求。

基于FPGA的嵌入式系统设计的开题报告一、研究背景如今,高效、可靠的嵌入式系统已被广泛应用于各种应用领域,例如自动化控制、通讯、医疗、航空航天等。

而FPGA(Field-Programmable Gate Array)技术则是在嵌入式系统设计中广泛使用的一种硬件实现方式。

FPGA器件具有灵活性强、性能高、可重构性好等优点,因此在嵌入式系统中被广泛应用。

本论文的研究主要针对的是基于FPGA的嵌入式系统设计。

该系统能够实现多种功能,包括数据采集、处理、存储、显示等。

该系统可以广泛应用于各种领域,例如航空航天、汽车、医疗、通讯等。

二、研究目的和意义本论文的主要目的是设计并实现一种基于FPGA的嵌入式系统。

该系统应具有以下特点:1. 实时性:能够以高速率采集、处理和显示数据。

2. 可靠性:能够提供稳定和可靠的系统运行。

3. 灵活性:能够适应不同的应用场景和用户需求。

对于该系统的研究具有以下意义:1. 推广FPGA技术的发展。

通过开发基于FPGA的嵌入式系统,可以更好地推广FPGA技术在嵌入式系统设计中的应用。

2. 促进嵌入式系统的应用。

开发基于FPGA的嵌入式系统可以提高嵌入式系统在各种领域的应用,从而推动各领域的发展。

3. 增强学生的实践能力。

通过该论文的研究,可以促进学生对于FPGA技术的理解和实践能力的提高。

三、研究内容和方法本论文的研究内容主要包括以下三个部分:1. FPGA的基本原理和应用。

该部分主要介绍FPGA的基本原理和应用,并阐述了FPGA技术在嵌入式系统设计中的优势。

2. 基于FPGA的嵌入式系统设计。

该部分主要介绍基于FPGA的嵌入式系统的设计流程和具体实现方法,包括硬件设计和软件设计。

3. 基于FPGA的嵌入式系统实现。

该部分主要介绍基于FPGA的嵌入式系统的实现方法,包括硬件实现和软件实现。

本论文的研究方法主要包括以下几个方面:1. 理论研究。

对于FPGA技术的原理和应用,以及基于FPGA的嵌入式系统的设计和实现方法进行深入研究和理解。

FPGA实现嵌入式系统

摘要:在许多领域中广泛应用的嵌入式计算系统(简称为嵌入式系统),是在更大的电子器件中嵌入的重复完成特定功能的计算系统,它经常不被器件的使用者所识别,但在各种常用的电子器件中能够找到这些嵌入式系统。

以可编程门阵列(FPGA)来实现可配置的嵌入式系统已越来越广泛,本文主要详细介绍了以FPGA实现嵌入式系统的前景。

关键词:嵌入式;FPGA;嵌入式操作系统。

FPGA Embedded Systems

LI Bo

(College of Electrical and Electronic Engineering,Wuhan Institute of Technology,Wuhan

430200,China)

Abstract:In many embedded computing systems widely used in the field(referred to as embedded systems),is an electronic device in larger repeat embedded computing system to accomplish a specific function,it is often not recognized by the user of the device,but in a variety of conventional electronic devices can be found in these embedded systems.Programmable gate array(FPGA)to implement a configurable embedded systems has become increasingly widespread,this paper introduces the prospect to FPGA implementation of embedded systems.

Key words:Embedded;FPGA;Embedded operating system.

1引言

随着计算与通信的融合以及广泛的多媒体处理需求,嵌入式系统得到了前所未有的蓬勃发展。

嵌入式系统是以专用芯片为核心的专用系统,其特点是面向用户、面向应用、面向产品,软、硬件量体裁衣,满足行业应用个性化的要求,而这也是FPGA器件的特点。

因此基于FPGA的可配置嵌入式系统开发技术以及相应的片上可编程系统(SOPC)解决方案,不仅可融入微处理器技术、数字信号处理技术、可编程系统级芯片设计和软硬件协同设计技术,还能提供了基于嵌入式智能平台的嵌入式系统的设计方法,还降低了设计难度、缩短了研发周期,必将成为未来的主流趋势之一。

从系统对上市时间的要求、可定制特性以及集成度等方面考虑,FPGA在嵌入式系统中获得广泛应用,已经从早期的军事、通信系统等应用扩展到低成本消费电子类等产品中。

目前,FPGA在嵌入式系统中主要有3种使用方式:(1)状态机模式:无外设、无总线结构且无实时操作系统,达到最低的成本,常应用于VGA和LCD控制等,满足用户的最基本需求。

(2)单片机模式:包括一定的外设,可以利用实时操作系统和总线结构,以中等的成本,达到中等的性能,常用于控制和仪表。

(3)定制嵌入模式:高度集成扩充的外设,实时操作系统和总线结构,可达到高性能,常应用于网络和无线通信等。

2FPGA实现嵌入式系统的优势

嵌入式嵌入式系统经历了从单片计算机、工业控制计算机、集中分布式控制系统,进而发展到嵌入式智能平台的几个发展阶段。

从独立单机使用发展到联

网设备。

从以模拟电路为主发展到以数字电路为主、数模混合型,进而进入全数字时代。

总的来说,嵌入式系统向着更高性能、更小体积、更低功耗、更廉价、无处不在的方向发展。

基于FPGA的可配置嵌入式系统开发技术以及相应的片上可编程系统(SOPC)解决方案,不仅可融入微处理器技术、数字信号处理技术、可编程系统级芯片设计和软硬件协同设计技术,还能提供了基于嵌入式智能平台的嵌入式系统的设计方法,还降低了设计难度、缩短了研发周期,必将成为未来的主流趋势之一。

从系统对上市时间的要求、可编程的特性以及集成度等方面考虑,以可编程门阵列(FPGA)来实现可配置的嵌入式系统已越来越广泛。

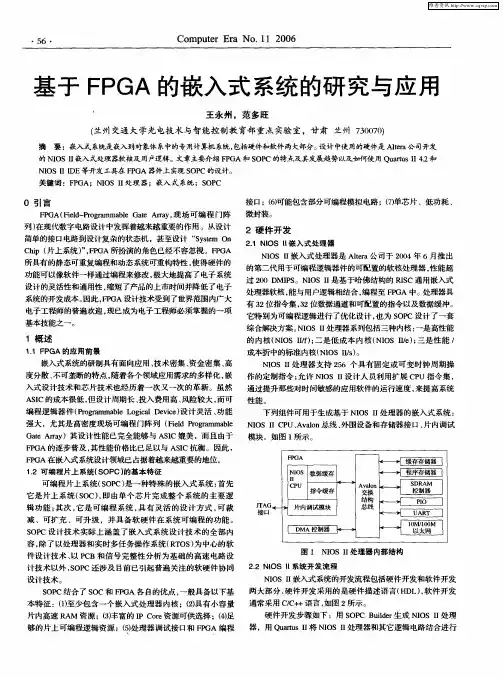

图1表示FPGA实现嵌入式系统的市场预测,估计从2002年的23亿美元,将增长到2008年的63亿美元。

图1FPGA实现嵌入式系统的市场预测

采用90纳米工艺生产FPGA器件之后,FPGA器件进一步降低成本,减少功耗和提高性能,低成本使FPGA成为中小批量生产的应用器件,应用范围从早期的军事、通信系统等扩展到低成本消费电子类等产品。

目前在实现嵌入式系统的各个领域得到广泛的应用,并进一步带来设计方法的变化。

3FPGA DSP嵌入式系统

FPGA是极高并行度的信号处理引擎,能够满足算法复杂度不断增加的应用要求,通过并行方式提供极高性能的信号处理能力。

Xilinx的XtrerneDSP模块,如图3所示,使得Virtex4/Sparten3系列厂PGA可以为高性能的数字信号处理提供理想的解决方案,达到传统上由ASIC或ASSP完成的高性能信号处理能力。

可以针对数字通信和视频图象处理等应用开发高性能的DSP引擎,也可在可编程DSP系统中作为预处理器或协处理器等。

Vir-tex4SX系列中DSP48模块最多达到512个,工作频率达到500MHz,成为算术密集应用的理想器件。

DSP48模块是一个18×18位二进制补码乘法器,跟随一个48位符号扩展的加法器/减法器/累加器,适应DSP应用中的众多的功能。

提高了操作数输入、中

间积和累加器输出的可编程流水线操作,以及48位内部总线等的吞吐量和适应性,无需一般的结构布线就可以实现前一个DSP48的输出与后一个DSP48输入的级联,增强了它的功能。

在复杂算法的数字处理系统中,系统要求的不断提高和集成规模的不断扩大,使得系统结构在设计的开始阶段是不明确的,不可能直接用RTL(寄存器转移级)设计方法进行描述,所以将系统集成到数字芯片中。

图2所示的DSP设计环境可以进行系统的数学建模,算法优化和改进,设计校验和诊断,以及日DL产生和仿真等。

涉及Xilinx的ISE硬件实现工具和嵌入系统开发包EDK,以及片内逻辑分析工具(CChipScope Pro)等。

第三方的工具包括MATLAB/SimuLink和ModeISim等,可以进行HDL协同仿真和硬件在环路的协同仿真等,一旦设计优化完成和仿真通过,可以直接利用IP核的网表文件进行硬件实现,设计的效率和可靠性大大提高。

图2DSP设计环境进行系统的数学建模

4FPGA嵌入微处理器系统

Xilinx FPGA的Virtex4和Virtexll-Pro系列嵌入7IBM PowerPC405的RISC 微处理器硬核,而Virtex和Spanten II之后的所有系列都可以嵌入MicroBlaze软核。

嵌入的PPC405硬核和MicroBlaze软核都是32位的哈佛结构微处理器。

PPC405硬核包括cache单元、存储器管理单元(MMU)、指令获取译码单元、执行单元、定时器和诊断逻辑单元等,如图3所示,指令的操作包括获取、译码、执行、写回和加载回写五级流水组成。

包括加载和存储等大多数指令都是一个时钟周期内执行。

图3指令的操作

PPC405处理器模块是与CoreConnect总线结构相兼容的,包括Xilinx IP软核在内的任何CoreConnect兼容核都可以通过这个高性能总线结构与处理器模块集成。

CoreConnect结构提供处理器局部总线(PLB)、片内外设总线(OPB)和器件控制寄存器(DCR)总线,利用这三个总线来互联处理器模块、Xilinx I 户软核、第三方IP核和定制的逻辑。

高性能外设连接到高带宽低滞后的PCB总线,较慢速的外设连接到OPB总线,可以减少PLB总线的流量,提高整个系统性能。

图4给出PPC405和MicroBlaze的总线例子。

图4给出PPC405和MicroBlaze的总线例子。

6结论

在复杂算法的嵌入式系统系统中,系统的要求不断提高,集成规模不断扩大,使得系统的结构在设计的开始阶段是不明确的,不可能直接用RTL(寄存器转移级)设计方法进行描述,也就无法将系统集成到数字芯片之中。

随着FPGA的成本不断降低,FPGA实现嵌入式系统达到嵌入式系统系统的特性和可编程的要求具有明显的优越性,市场潜力很大。

参考文献

[1]Frank Vahid,Tony Givargis.Embedded System Design:A Unified Hardware/Software

Introduction.2002

[2]FPGA在嵌入式系统中应用不断走强.电子工程专辑一嵌入系统特刊,2005,3

[3]Ken Karnofsky.Simulink Brings Model—Based Design to Embedded Signal

Processing.Xcelljournal,2004

[4]Rodriguez J,Bernet S,Wu B,et al.Multilevel voltage-source-converter topologies for

industrial medium-voltage drives[J].IEEE Trans.on Industrial Electronics,2007,54(6):2930-2945.。