数字集成电路分析与设计深亚微米工艺第三版课程设计

- 格式:docx

- 大小:16.61 KB

- 文档页数:2

亚微米和深亚微米IC中的ESD保护结构研究的开题报告1.选题背景:随着集成电路技术的发展,芯片制造技术不断变革,芯片制造工艺进一步向亚微米、深亚微米方向推进,让集成电路在制造和使用中更加可靠和高效。

然而,随着集成度和功能的提高,晶体管密度和场效应晶体管信号速度也相应增加,ESD的危害性也不断增强。

因此,在亚微米和深亚微米的IC设计和制造中,ESD保护结构的研究显得尤为重要。

2.研究目的:本研究的目的是对亚微米和深亚微米IC中的ESD保护结构进行研究。

具体目标如下:1)分析亚微米和深亚微米IC的ESD问题;2)研究不同ESD保护结构的工作原理,各自的优缺点;3)研究ESD保护结构的设计方法,重点分析干扰抑制设计的原理;4)分析ESD保护结构的正确使用方法,提高芯片的可靠性和耐久性。

3.研究内容:本研究的重点是亚微米和深亚微米IC中的ESD保护结构。

主要研究内容如下:1)亚微米和深亚微米IC的ESD问题;2)ESD保护结构的工作原理及分类;3)ESD保护结构的设计方法,包括电路设计和电磁设计两方面;4)ESD保护结构正确使用方法;5)对比分析不同ESD保护结构的优缺点。

4.研究方法:本研究采用理论分析和实验研究相结合的方法。

理论分析以文献资料和相关标准为依据,重点阐述亚微米和深亚微米IC中的ESD保护结构的工作原理、设计方法和使用方法。

实验研究部分则采用常规的ESD实验方法,对不同类型的ESD保护结构进行测试和比较分析。

5.预期成果:通过本研究,可以深入了解亚微米和深亚微米IC的ESD问题及其影响。

能够掌握ESD保护结构的工作原理、分类、设计方法和使用技巧。

分析不同ESD保护结构的优缺点,指导实际应用中的ESD保护设计工作。

促进集成电路技术的发展,提高芯片的可靠性和稳定性。

集成电路工艺课程设计报告目录1.课程设计目的与任务 (1)2.课程设计的基本内容 (1)2.1 npn双极型晶体管的设计 (1)2.2课程设计的要求与数据 (1)3.课程设计原理 (1)3.1晶体管设计的一般步骤 (2)3.2晶体管设计的基本原则 (2)4.晶体管工艺参数设计 (3)4.1晶体管的纵向结构参数设计 (3)4.1.1 集电区杂质浓度的确定 (3)4.1.2 基区及发射区杂质浓度 (3)4.1.3 各区少子迁移率及扩散系数的确定 (4) 4.1.4 各区少子扩散长度的计算 (5)4.1.5 集电区厚度的选择 (6)4.1.6 基区宽度的计算 (6)4.1.7扩散结深 (9)4.1.8杂质表面浓度 (9)4.1.9 芯片厚度和质量 (10)4.2 晶体管的横向设计 (10)4 .2 .1 晶体管横向结构参数的选择 (10)4.3 工艺参数计算 (11)4.3.1 晶体管工艺概述 (11)4.3.2基区硼预扩时间 (12)4.3.3基区硼扩散需要的氧化层厚度 (12) 4.3.4基区硼再扩散时间计算 (13)4.3.5发射区预扩散时间 (13)4.3.6发射区氧化层厚度 (14)4.3.7发射区再扩散的时间 (14)4.3.8基区氧化时间 (15)4.3.9发射级氧化层厚度 (15)4.4设计参数总结 (16)5.工艺流程图 (17)6.生产工艺流程 (17)6.1 硅片清洗 (17)6.1.1 清洗原理 (18)6.1.2硅片清洗的一般程序 (18)6.2氧化工艺 (19)6.2.1 氧化原理 (19)6.2.2基区氧化的工艺步骤 (20)6.2.3测量氧化层厚度 (20)6.3 第一次光刻工艺(光刻基区) (21)6.3.1 光刻原理 (21)6.3.2 工艺步骤 (21)6.4 基区硼扩散工艺 (22)6.4.1 硼扩散原理 (22)6.4.2 硼扩散工艺步骤 (23)6.5发射区氧化的工艺步骤 (23)6.6第二次光刻工艺(光刻发射区) (24)6.7发射区磷的扩散 (24)6.7.1 磷扩散原理 (24)6.7.2 磷扩散工艺步骤 (25)6.8引线孔氧化的工艺步骤 (25)6.9 第三次光刻(光刻引线孔) (26)6.10引线孔金属化 (27)6.10.1集成电路对金属化材料特性的要求 (27) 6.10.2金属化步骤 (27)6.11光刻金属电极 (28)7. 心得体会 (28)8. 参考文献 (29)微电子器件与工艺课程设计报告——npn双极型晶体管的设计1.课程设计目的与任务《微电子器件与工艺课程设计》是有关微电子器件和工艺知识的综合应用的课程,使我们系统的掌握半导体器件,集成电路,半导体材料及工艺的有关知识的必不可少的重要环节。

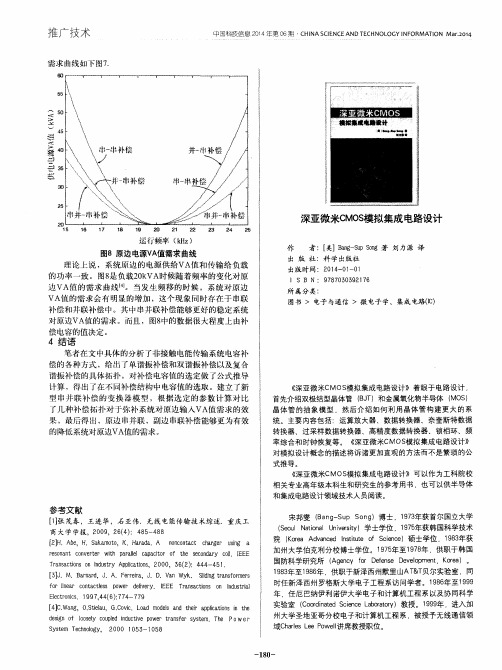

毕业设计-深亚微米电源管理类集成电路及各种数模混合集成电路的关键技术理论研究与设计斜率补偿稳定性可测性ABSTRACT A high efficiency current mode synchronous buck regulator IC is designed on the basis of the project “Theoretical research and design of key techniques for deep-submicron power management IC and mixed IC”.Thewhole simulation has been completed by using the EDA softwares, such as Cadence, Hspice, and the layout design is also finished.Atpresent, the chip is being taped out in Hynix.Beginningfrom the switching mode regulator, a high efficiency current mode synchronous buck DC/DC is designed after an in-depth systemic study on the current-mode switching regulator.Byadopting the technologies of synchronous rectification, double operation mode and low dropout operation, the efficiency of this design is up to 96%.Inorder to prevent the sub-harmonic oscillation at high duty cycles, slope compensation is used.Whatis special is that the design provides a clamp circuit that can adjust its thresholds with respect to the magnitude of the slope compensation signal so that a substantially constant maximum current limit of the regulator may be remained at greater duty cycles.Amacro model is also created to obtain the bode plots for appropriate frequency compensation.Finally,the circuits for testability are designed to shorten the test time and get more profit margins.Keyword:current-modeBuck regulatorslope compensationstability testability 目录第一章绪论1 §1.1国内外电源管理技术概述1§1.2开关型电压转换器简介2第二章XD2607系统构建8 §2.1控制模式的选取8§2.2工作模式的选取10§2.3系统设计与系统框图11§2.4效率的考虑13§2.5主要电特性指标14第三章XD2607设计中的技术关键及其解决方案16 §3.1电流环稳定性分析与斜率补偿16§3.2电压环稳定性分析与电路建模21第四章XD2607电路设计与仿真验证28 §4.1使能控制与PTAT电流偏置(ENABLE)28§4.2带隙基准源(VREF)31§4.3零温度系数电流基准(IREF)36§4.4误差放大器(EA)38§4.5振荡器模块(OSC)41§4.6斜坡产生模块(SLOPE)43§4.7电流比较器(ICOMP)45§4.8误差箝位电路(CLAMP)47§4.9自动测试电路(TEST)49§4.10控制逻辑(LOGIC)53第五章XD2607整体电路仿真验证及主要性能指标实现56 结束语错误!未定义书签。

数字集成电路分析与设计第三版课程设计一、课程设计背景数字集成电路课程是电子信息工程、计算机科学与技术专业的重要基础课程之一,涉及数字电路的设计、分析与实现。

本课程设计旨在通过实际应用的方式,深入理解数字电路的内部原理与工作机理,掌握数字电路的设计方法与技巧,提高学生的工程实践能力。

二、课程设计内容本课程设计主要包括以下两个实验项目:1.逻辑门电路设计本项目通过设计并构建逻辑门电路,学习数字电路的基本工作原理,掌握逻辑门电路的设计方法与技巧。

实验要求•设计并构建包括与门、或门、非门、异或门、与非门、或非门等基本逻辑门电路;•验证逻辑门电路的正确性,并进行优化设计;•使用逻辑门电路实现数字电路的基本运算,例如加法、减法、乘法等运算。

实验流程1.确定逻辑门电路的输入输出类型,并设计逻辑门电路的电路图;2.选择适合的逻辑门,并进行组合设计,使其能够完成所需功能;3.给出逻辑门电路的真值表,并使用仿真工具模拟验证电路的正确性;4.构建电路,并进行实验验证;5.优化电路性能,例如减小功耗、减小延迟等。

2.计数器电路设计本项目通过设计并构建计数器电路,学习数字电路的进位、借位、计数等基本原理,掌握计数器电路的设计方法与技巧。

实验要求•实现包括二进制计数器、带有预置值的二进制计数器等常用计数器电路;•验证计数器电路的正确性,并进行优化设计;•在计数器电路的基础上,设计并编写实现数字频率计算器。

实验流程1.确定计数器电路的输入输出类型,并设计计数器电路的电路图;2.选择适合的计数器类型,并进行组合设计,使其能够完成所需功能;3.给出计数器电路的真值表,并使用仿真工具模拟验证电路的正确性;4.构建电路,并进行实验验证;5.优化电路性能,例如减小功耗、减小延迟等。

三、课程设计效果评估本课程设计的效果将通过以下几个方面进行评估:•学生对数字电路基本原理和工作机理的理解程度•学生能够熟练掌握数字电路的设计方法与技巧•学生的工程实践能力是否提高•学生对课程设计的反馈和评价四、课程设计总结数字集成电路分析与设计第三版课程设计旨在通过实际应用的方式,深入理解数字电路的内部原理与工作机理,掌握数字电路的设计方法与技巧,提高学生的工程实践能力。

深亚微米工艺集成电路串扰控制技术的研究和优化设计的开题报告一、选题的背景及意义随着电子技术的飞速发展,现代集成电路以及高端芯片的技术日新月异,特别是深亚微米工艺技术的迅猛发展,芯片设计的规模和复杂度不断提高。

但是,随着工艺的进一步发展,深亚微米工艺出现了新的问题,其中之一就是串扰问题。

深亚微米工艺电路元件的尺寸过小,导致电路间距和线寻址距离变得更小,因此晶体管器件、金属线及其与相邻结构之间的相互作用,会产生电磁辐射干扰,从而导致电路串扰的问题。

这种串扰不仅仅是对芯片自身的干扰,还对其他芯片或者周边的电子设备产生相应的干扰,因此非常值得研究。

目前,针对该问题的研究主要包括两个方面:一是串扰现象的理论分析研究,二是针对某一类芯片进行专门的串扰治理和防范措施。

因此,本文致力于研究和优化设计深亚微米工艺集成电路的串扰控制技术,为当前和未来的芯片设计提供可靠的技术保障,同时提高芯片质量和性能,具有重要的实用价值与研究意义。

二、选题的研究现状及发展趋势现阶段国内外对深亚微米工艺集成电路串扰控制技术的研究还处于发展阶段,该领域的研究主要涉及到以下几个方面:1. 串扰现象模拟和计算方法2. 串扰问题的理论分析及仿真3. 串扰规律的探讨和建模4. 串扰控制技术的研究和应用5. 新型芯片结构和材料的研究未来,随着科技的不断进步和深亚微米工艺技术的日益成熟,深入研究深亚微米工艺集成电路的串扰控制技术无疑将会成为该领域的研究热点和发展趋势。

三、选题的研究内容及方法本文的研究内容主要集中在深亚微米工艺集成电路的串扰控制技术,主要包括以下研究内容:1. 深入分析深亚微米工艺集成电路的串扰现象和机理,探讨其规律和特点。

2. 分析和比较现有的串扰控制技术,针对其中存在的问题和不足,提出有效的串扰控制技术和策略。

3. 基于串扰控制技术的需求和分析,结合当前的芯片设计需求,提出一种优化的集成电路设计方法,通过改进设计方案,减小串扰干扰。

课程设计班级:姓名:学号:成绩:电子与信息工程学院电子科学系CMOS二输入与非门的设计一、概要随着微电子技术的快速发展,人们生活水平不断提高,使得科学技术已融入到社会生活中每一个方面。

而对于现代信息产业和信息社会的基础来讲,集成电路是改造和提升传统产业的核心技术。

随着全球信息化、网络化和知识经济浪潮的到来,集成电路产业的地位越来越重要,它已成为事关国民经济、国防建设、人民生活和信息安全的基础性、战略性产业。

集成电路有两种。

一种是模拟集成电路。

另一种是数字集成电路。

本论文讲的是数字集成电路版图设计的基本知识。

然而在数字集成电路中CMOS与非门的制作是非常重要的。

二、CMOS二输入与非门的设计准备工作1.CMOS二输入与非门的基本构成电路使用S-Edit绘制的CMOS与非门电路如图1。

图1 基本的CMOS二输入与非门电路2.计算相关参数所谓与非门的等效反相器设计,实际上就是根据晶体管的串并联关系,再根据等效反相器中的相应晶体管的尺寸,直接获得与非门中各晶体管的尺寸的设计方法。

具体方法是:将与非门中的VT3和VT4的串联结构等效为反相器中的NMOS 晶体管,将并联的VT 1、VT 2等效PMOS 的宽长比(W/L)n 和(W/L)p 以后,考虑到VT3和VT4是串联结构,为保持下降时间不变,VT 3和VT 4的等线电阻必须减小为一半,即他们的宽长比必须为反相器中的NMOS 的宽长比增加一倍,由此得到(W/L)VT3,VT4=2(W/L)N 。

因为考虑到二输入与非门的输入端IN A 和IN B 只要有一个为低电平,与非门输出就为高电平的实际情况,为保证在这种情况下仍能获得所需的上升时间,要求VT 1和VT 2的宽长比与反相其中的PMOS 相同,即(W/L)VT1,VT2=(W/L)P 。

至此,根据得到的等效反向器的晶体管尺寸,就可以直接获得与非门中各晶体管的尺寸。

如下图所示为t PHL 和t PLH ,分别为从高到低和从低到高的传输延时,通过反相器的输入和输出电压波形如图所示。

微电子器件第三版课程设计1.课程设计目的本课程设计旨在通过设计和实现一个集成电路,使学生能够深入了解微电子器件的原理和设计流程,并将所学知识应用于实际中。

2.课程设计内容课程设计的主要内容如下:1.通过参考文献和相关资料,研究和了解所设计的集成电路的原理和相关知识;2.选择和设计适合的电路拓扑结构,绘制集成电路的电路图;3.进行电路仿真并优化电路参数,以实现所需的设计指标; 4.设计和绘制实际的集成电路版图; 5.进行集成电路的制作和测试,对设计的电路进行验证和分析; 6.最终提交完整的课程设计报告,包括电路原理、设计过程、仿真结果和实验结果等方面的内容。

3.课程设计要求本课程设计的要求如下:1.学生需要以团队形式完成课程设计;2.每个小组提交一份完整的课程设计报告,报告中应包括电路原理、设计过程、仿真结果和实验结果等方面的内容; 3.电路设计和仿真应使用专业的EDA软件,如Cadence等; 4.课程设计完成后需进行现场演示和答辩,每个小组需向全班进行电路演示和答辩; 5.设计的集成电路应具有一定的实际应用价值,能够满足一定的设计指标; 6.课程设计报告的撰写应符合学校的相关要求和规范。

4.参考资料1.微电子器件,第三版,姚明等著,高等教育出版社,2010年;2.模拟集成电路设计,Razavi B.著,电子工业出版社,2007年;3.Cadence电路设计,张三著,机械工业出版社,2012年。

5.课程设计时间安排本课程设计的时间安排如下:第1周:课程设计介绍和规划;第2周-第3周:电路原理和EDA软件操作培训;第4周-第5周:电路拓扑结构设计和仿真;第6周-第7周:版图设计和仿真;第8周-第9周:集成电路制作与测试;第10周:报告撰写和演示准备;第11周:现场演示和答辩。

6.课程设计评分依据本课程设计的评分依据如下:1.集成电路设计的准确性、可靠性和实用性;2.电路仿真结果的正确性和优化性;3.集成电路制作的成功率和精度;4.课程设计报告的内容、格式和语言表达;5.电路演示和答辩的表现和交流能力。

数字集成电路分析与设计深亚微米工艺第三版课程设计

一、概述

本文主要介绍数字集成电路分析与设计深亚微米工艺第三版课程设计。

本设计

主要涉及数字集成电路设计的各个方面,包括数字逻辑设计、计算机组成原理、数字信号处理等。

本设计旨在深入探究数字电路和集成电路的设计和工艺细节,从而提高学生的专业技能和实践能力。

二、设计内容

本次设计主要分为以下几个部分:

1. 数字逻辑电路设计

在本部分中,学生需要根据题目要求,设计数字逻辑电路的电路图和真值表,

同时需要手动编写数字逻辑电路的代码,并利用VHDL语言进行编程实现。

本部分

要求学生熟练掌握数字逻辑电路的设计方法和VHDL语言的编程技巧。

2. 计算机组成原理

在本部分中,学生需要设计一个基于FPGA的计算机组成原理的电路图和真值表,并利用VHDL语言进行编程实现。

本部分要求学生深入理解计算机组成原理的

设计思想,并熟练掌握FPGA电路设计和VHDL编程的技巧。

3. 数字信号处理

在本部分中,学生需要设计一个数字信号处理的电路图和真值表,并利用Python语言进行编程实现。

本部分要求学生掌握数字信号处理的基本原理和算法,以及Python语言的编程技巧。

三、课程目标

通过本次课程设计,学生应该达到以下目标:

1. 掌握数字电路和集成电路的设计和工艺细节

本设计涉及数字电路和集成电路的多个方面,要求学生深入理解电路设计和工艺细节,从而能够熟练掌握数字电路和集成电路的设计方法和实现流程。

2. 提高学生的专业技能和实践能力

本设计要求学生进行实际的电路设计和编程实现,从而加深对数字电路和集成电路的理解和掌握。

通过实践,学生能够提高自己的专业技能和实践能力,为将来的工作打下坚实的基础。

3. 培养学生的团队合作和创新能力

本设计要求学生分组进行合作,通过协作和交流,提高团队合作和创新能力。

学生需要思考如何在电路设计和编程实现中,发挥个人和团队的优势,提高工作效率。

四、总结

数字集成电路分析与设计深亚微米工艺第三版课程设计,旨在提高学生的数字电路和集成电路设计能力,同时培养学生的实际操作能力和团队合作能力。

本设计涉及数字逻辑电路设计、计算机组成原理和数字信号处理等方面,要求学生深入理解电路设计和编程实现的原理和方法,从而能够掌握数字电路和集成电路设计的技能。