[讲解]半导体制造技术作业

- 格式:doc

- 大小:13.50 KB

- 文档页数:3

1.1中国半导体论坛半导体技术天地是全国最大的半导体行业网站,主要有芯片设计半导体制造芯片封装测试,中国半导体论坛是一个以电子技术交流为主的电子工程师论坛,致力于做国内电子行业用户、工程师交流的最佳电子论坛,目前开设有求职招聘、半导体整合技术、半导体封装、半导体技术天地、半导体测试、半导体制造、技术交流天地、技术天地、半导体天地、相关书籍等交流论坛。

下面讲解CMOS制造.1.2CMOS的制造流程CMOS是集成电路的最基本单元,它的制作流程可分为前段和后段,前段流程主要完成元件的制作,包括组件隔离区的形成、阱的植入、栅极的制成、LDD的植入、源极和漏极的制成。

后段流程主要完成元件之间的互连,包括第一层金属的制成、第二层金属的制成、保护层和焊垫的制成。

以0.25微米制程为例,具体分为以下步骤。

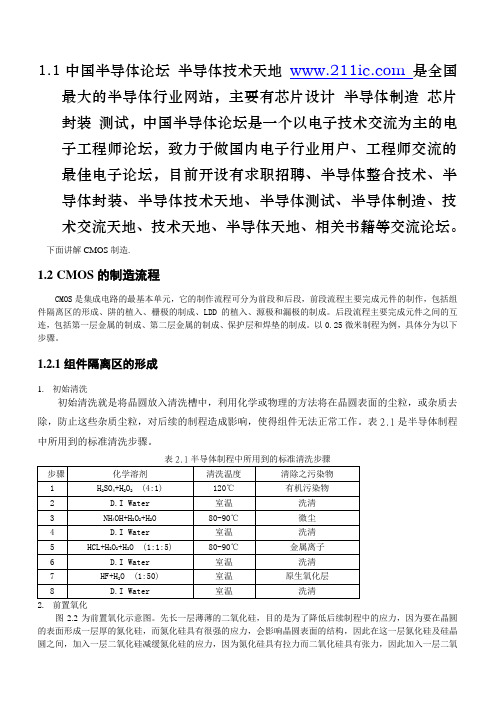

1.2.1组件隔离区的形成1.初始清洗初始清洗就是将晶圆放入清洗槽中,利用化学或物理的方法将在晶圆表面的尘粒,或杂质去除,防止这些杂质尘粒,对后续的制程造成影响,使得组件无法正常工作。

表2.1是半导体制程中所用到的标准清洗步骤。

表2.1半导体制程中所用到的标准清洗步骤步骤化学溶剂清洗温度清除之污染物1 H2SO4+H2O2 (4:1) 120℃有机污染物2 D.I Water 室温洗清3 NH4OH+H2O2+H2O 80-90℃微尘4 D.I Water 室温洗清5 HCL+H2O2+H2O (1:1:5) 80-90℃金属离子6 D.I Water 室温洗清7 HF+H2O (1:50) 室温原生氧化层8 D.I Water 室温洗清2.前置氧化图2.2为前置氧化示意图。

先长一层薄薄的二氧化硅,目的是为了降低后续制程中的应力,因为要在晶圆的表面形成一层厚的氮化硅,而氮化硅具有很强的应力,会影响晶圆表面的结构,因此在这一层氮化硅及硅晶圆之间,加入一层二氧化硅减缓氮化硅的应力,因为氮化硅具有拉力而二氧化硅具有张力,因此加入一层二氧化硅可以平衡掉硅晶圆表面的应力。

八大半导体工艺顺序剖析八大半导体工艺顺序剖析在现代科技领域中,半导体材料和器件扮演着重要的角色。

作为电子设备的基础和核心组件,半导体工艺是半导体制造过程中不可或缺的环节。

有关八大半导体工艺顺序的剖析将会有助于我们深入了解半导体制造的工作流程。

本文将从简单到复杂,逐步介绍这八大工艺的相关内容。

1. 排版工艺(Photolithography)排版工艺是半导体制造过程中的首要步骤。

它使用光刻技术,将设计好的电路图案转移到硅晶圆上。

排版工艺需要使用光刻胶、掩膜和曝光设备等工具,通过逐层叠加和显影的过程,将电路图案转移到硅晶圆上。

2. 清洗工艺(Cleaning)清洗工艺在排版工艺之后进行,用于去除光刻胶和其他污染物。

清洗工艺可以采用化学溶液或高纯度的溶剂,保证硅晶圆表面的干净和纯净。

3. 高分辨率电子束刻蚀(High-Resolution Electron BeamLithography)高分辨率电子束刻蚀是一种先进的制造技术。

它使用电子束在硅晶圆表面进行刻蚀,以高精度和高分辨率地制作微小的电路图案。

4. 电子束曝光系统(Electron Beam Exposure Systems)电子束曝光系统是用于制造高分辨率电子束刻蚀的设备。

它具有高能量电子束发射器和复杂的控制系统,能够精确控制电子束的位置和强度,实现微米级别的精细曝光。

5. 高能量离子注入(High-Energy Ion Implantation)高能量离子注入是半导体器件制造中的一项重要工艺。

通过将高能量离子注入到硅晶圆表面,可以改变硅晶圆的电学性质,实现电路中的控制和测量。

6. 薄膜制备与沉积(Film Deposition)薄膜制备与沉积是制造半导体器件的关键工艺之一。

这个工艺将薄膜材料沉积在硅晶圆表面,包括化学气相沉积、物理气相沉积和溅射等方法。

这些薄膜能够提供电介质、导电材料或阻挡层等功能。

7. 设备和工艺完善(Equipment and Process Optimization)设备和工艺完善的步骤是优化半导体制造工艺的关键。

扩散工艺前言:扩散部按车间划分主要由扩散区域及注入区域组成,其中扩散区域又分扩散老区和扩散新区。

扩散区域按工艺分,主要有热氧化、扩散、LPCVD、合金、清洗、沾污测试等六大工艺。

本文主要介绍热氧化、扩散及合金工艺。

目录第一章:扩散区域设备简介……………………………………第二章:氧化工艺第三章:扩散工艺第四章:合金工艺第一章:扩散部扩散区域工艺设备简介炉管设备外观:扩散区域的工艺、设备主要可以分为:类别主要包括按工艺分类热氧化一氧、二痒、场氧、Post氧化扩散推阱、退火/磷掺杂LPCVD TEOS、SI3N4、POL Y清洗进炉前清洗、漂洗合金合金按设备分类卧式炉A、B、C、D、F、H、I六台立式炉VTR-1、VTR-2、VTR-3 清洗机FSI-1、FSI-2炉管:负责高温作业,可分为以下几个部分:组成部分功能控制柜→对设备的运行进行统一控制;装舟台:→园片放置的区域,由控制柜控制运行炉体:→对园片进行高温作业的区域,由控制柜控制升降温源柜:→供应源、气的区域,由控制柜控制气体阀门的开关。

FSI:负责炉前清洗。

第二章:热氧化工艺热氧化法是在高温下(900℃-1200℃)使硅片表面形成二氧化硅膜的方法。

热氧化的目的是在硅片上制作出一定质量要求的二氧化硅膜,对硅片或器件起保护、钝化、绝缘、缓冲介质等作用。

硅片氧化前的清洗、热氧化的环境及过程是制备高质量二氧化硅膜的重要环节。

2. 1氧化层的作用2.1.1用于杂质选择扩散的掩蔽膜常用杂质(硼,磷,砷等)在氧化层中的扩散系数远小于在硅中的扩散系数,因此氧化层具有阻挡杂质向半导体中扩散的能力。

利用这一性质,在硅上的二氧化硅层上刻出选择扩散窗口,则在窗口区就可以向硅中扩散杂质,其它区域被二氧化硅屏蔽,没有杂质进入,实现对硅的选择性扩散。

1960年二氧化硅就已被用作晶体管选择扩散的掩蔽膜,从而导致了硅平面工艺的诞生,开创了半导体制造技术的新阶段。

同时二氧化硅也可在注入工艺中,作为选择注入的掩蔽膜。

半导体生产流程所谓的半导体,是指在某些情况下,能够导通电流,而在某些条件下,又具有绝缘体效用的物质;而至于所谓的IC,则是指在一半导体基板上,利用氧化、蚀刻、扩散等方法,将众多电子电路组成各式二极管、晶体管等电子组件,作在一微小面积上,以完成某一特定逻辑功能例如:AND、OR、NAND 等,进而达成预先设定好的电路功能.自1947年12月23日第一个晶体管在美国的贝尔实验室BellLab被发明出来,结束了真空管的时代,到1958年TI开发出全球第一颗IC成功,又意谓宣告晶体管的时代结束,IC的时代正式开始.从此开始各式IC不断被开发出来,集积度也不断提升.从小型集成电路SSI,每颗IC包含10颗晶体管的时代;一路发展MSI、LSI、VLSI、ULSI;再到今天,短短50年时间,包含千万个以上晶体管的集成电路已经被大量生产,并应用到我们的生活的各领域中来,为我们的生活带来飞速的发展.不能想象离开半导体产业我们的生活将会怎样,半导体技术的发展状况已成为一个国家的技术状况的重要指针,电子技术也成为一个国家提高国防能力的重要途径.半导产品类别目前的半导体产品可分为集成电路、分离式组件、光电半导体等三种.集成电路IC,是将一电路设计,包括线路及电子组件,做在一片硅芯片上,使其具有处理信息的功能,有体积小、处理信息功能强的特性.依功能可将IC分为四类产品:内存IC、微组件、逻辑IC、模拟IC.分离式半导体组件,指一般电路设计中与半导体有关的组件.常见的分离式半导体组件有晶体管、二极管、闸流体等.光电式半导体,指利用半导体中电子与光子的转换效应所设计出之材料与组件.主要产品包括发光组件、受光组件、复合组件和光伏特组件等.IC产品介绍IC产品可分为四个种类,这些产品可细分为许多子产品,分述如下:内存IC:顾名思义,内存IC是用来储存资料的组件,通常用在计算机、电视游乐器、电子词典上.依照其资料的持久性电源关闭后资料是否消失可再分为挥发性、非挥发性内存;挥发性内存包括DRAM、SRAM,非挥发性内存则大致分为MaskROM、EPROM、EEPROM、FlashMemory四种.微组件IC:指有特殊的资料运算处理功能的组件;有三种主要产品:微处理器指微电子计算器中的操作数件,如计算机的CPU;微控制器是计算机中主机与接口中的控制系统,如声卡、影视卡...等的控制组件;数字讯号处理IC可将模拟讯号转为数字讯号,通常用于语音及通讯系统.模拟IC:低复杂性、应用面积大、整合性低、流通性高是此类产品的特色,通常用来作为语言及音乐IC、电源管理与处理的组件.逻辑IC:为了特殊信息处理功能不同于其它IC用在某些固定的范畴而设计的IC,目前较常用在电子相机、3DGame、IC产业IC的制造可由上游至下游分为三种工业,一是与IC的制造有直接关系的工业、包括晶圆制造业、IC制造业、IC封装业;二是辅助IC制造的工业,包括IC设计、光罩制造、IC测试、化学品、导线架工业;三是提供IC制造支持的产业,如设备、仪器、计算机辅助设计工具工业...等.IC集成电路制作过程简介集成电路的生产过程极其复杂,习惯上将其分为前置作业,电路的制作,晶圆及晶粒测试和后段的封装测试等.因为IC是由很多的电路集合而成的,而这些电路组件和线路是以晶圆为基础并以层状分布的,制造过程也是一层层的建造出来的,类似于建楼房的过程.其中前置作业类似于楼房的设计和建造地基,包括电路的设计、光罩设计和晶圆的制作,电路设计即是根据使用的要求设计出各层的线路和架够,光罩设计则类似于照像底片,依靠其将设计好的电路印到芯片上,而制作硅晶圆就是将硅晶体通过加热熔化,再用一定的方法拉成晶棒,并切片、研磨成符合要求的芯片的过程.电路制作是在硅片的基础上制成一层层的电路的过程,因为线路极其细微,其制造过程也就有很高的难度,生产上是使用类似照相技术的报光,显影,蚀刻,冲洗的方法来实现的下面将做详细的介绍.晶圆及晶粒测试是对各制造流程的结果的测试,目的是对各流程有很好的控制,并能及时的发现生产中的不良产品,尽早进行修部或剔除,以减少不良成本,经过各道测试并最终生产出来的芯片才能进入到下一道封装测试的过程.封装和测试是将功能测试良好的晶粒切割开,并封装,拉出联线再进行全面测试的过程,要经过芯片切割,粘晶,焊线,封料,切割/成形,印字,电镀,及检验等过程.直到这里,一个合格的集成电路才算制造完成.IC制造业特性IC制造业中,有几个不同于其它制造业的特性,分列如下:机器的折旧占成本大部分:制造IC所用的机器设备价格高,而且汰旧快,通常采二至四年加速折旧此为实际作法;大多数股市上市说明书则宣称四至八年平均折旧,因此机器折旧的费用很高;一般说来,机器的折旧占制造成本的20%以上.良率影响产品单位成本:晶圆上可划分为许多方块,而一个IC的线路就都做在这个方块上,再送至封装厂中切割包装,就可将这些方块制成一片片的IC;而包装好经测试可使用的IC占晶圆割下IC总数的比率称为良率.IC的制造过程非常精密,只要在其中一步骤稍有不慎,就会使IC毁损,而成为不能使用的产品,不像其它制造业的产品,有制造过程的错误,大多只会成为品质不良的产品,非不能使用的产品;因此IC制造业的良率要较传统的工业制造良率来的低,而且变异大,不论是在品质管制及成本控制上都是一大问题;通常IC的制造中,影响良率的原因有两种:a晶圆的大小:在晶圆上做IC,通常边缘的部分都因晶圆的圆弧而无法做出完整的方块;晶圆的直径愈大,则其圆弧的曲度愈小,边缘要舍弃的面积占晶圆的比率也就愈小,良率就愈高;因此IC厂都在努力提升自己的制程能在更大的晶圆上做出产品.b线上的管制:集成电路制造是极精密的工业,且制造环境特殊无尘室;在制造过程中所犯的一个小过失,影响良率的程度就很大,通常可达20%以上,因此线上的管制在集成电路制造中是很重要的.制程复杂影响机器使用率:IC制造厂中,由于制程重复且步骤多,若制造排程不良,容易造成某些工作站忙线、有些站闲置,而使得机器设备无法充分利用;机器设备的折旧又是占了IC制造成本中的大部分,若机器使用率不高,那幺便会耗费大量的折旧成本;充分的利用机器,是IC制造厂管理中重要的一环.晶圆代工因为IC的生产过程复杂,从设计到生产的生产线长,而且生产过程的主要成本是机台的成本,固定成本高,且产品多样化,批量小,更新速度快,因此很少有厂家能从前到后的整条线生产自己的产品,而很多厂商都只是加工整个制程中的一段,再形成供应链式的组合,联合制造产品,以实现规模效应.晶圆代工就是基于此而产生的,这种企业只负责生产不进行设计,因此也可以说晶圆代工厂并没有自己的产品,传统上讲只是指wafer晶圆的制作过程,即是在wafer上做出一层层的电路而现在逐渐延伸出广义的晶圆代工,其除了原来晶圆制造的功能外,还包括了上游的光罩制作和下游的切割、封装、测试等过程,因此一个IC设计企业只要将自己的设计交给晶圆代工厂,便可以得到符合自己要求的IC成品,模块制程wafer生产的基本原理集成电路尽管种类不同,其制程相似;差别在不同的光罩会有不同的电路图样;CVD、离子植入时投入的材料不同,会产生不同的组件,而使制造出来的IC有所差异.IC制程中,制造作业种类通常只有十多种,但由于不断重复这些作业,使得一片IC从晶圆投入到可以切割包装,要经过百次以上的制造步骤.一个IC产品制作电路后的结构,是以芯片为基础逐层的建造起来的,上面已经提到,每一层的生产都是使用类似照相技术的报光,显影,蚀刻,冲洗的方法来实现的,因此生产过程中,每一层的制造都是几个类似的过程,而整个晶圆的制造就是这几个过程的重复循环,每个过程的生产都在特定的区域来完成,这些区域有:薄膜thin-film,黄光photo,蚀刻etch,扩散diffusion.薄膜thin-film薄膜区间是尘积介电质或金属层的地方,介电质是用于隔离开各层金属的多为玻璃层,而金属层是集成电路中的导线,多采用铝或铜或铝铜合金,因此介电质和金属沉积也是集成电路的制程中的重要制程.薄膜技术有物理气象沉积包括蒸镀既借着对被蒸镀物体加热,利用被蒸镀物在高温时所具备的饱和蒸气压,来进行薄膜的沉积.和溅镀既利用电浆所产生的离子,借着离子对被溅镀物体电极的轰击,使电浆的气相内具有被镀物的粒子,来产生沈积薄膜的.和化学气象沈积既利用化学反应的方式,在反应器内将反应物通常为气体生成固态的生成物,并沉积在芯片表面的一种薄膜沉积技术.黄光Photo微影技术是制造集成电路的重要之一,通过暴光和显影的程序它可以将光罩上设计的图案转移到晶圆表面的光阻上,其主要过程包括光阻涂抹,烘拷,对准,暴光及显影等程序,由于光学上的需要,此段制程之照明采用偏黄的可见光,因此习惯上将此区称为黄光区.在黄光区内,利用整合型的晶圆轨道机——步进机系统来完成这个过程,其利用紫外光线或深紫外光线来照射光阻,以引起化学反应,将设计的光罩上的图形印到晶圆或光阻上,这也是集成电路厂中最昂贵的工具,每台的价格都可达到数百万美元,因此也常成为生产中的瓶颈. 蚀刻Etch Etch作为IC制程中的主要环节之一,其目的是化学物质的反应来去除wafer表面多余的物质,根据各stedp的目的不同有多种具体方式,但从其基本的原来可将其分为两种,既WetEtching湿蚀刻和DryEtching干蚀刻,WetEtching是用将wafer放入化学溶液中,通过化学反应将要蚀刻掉的物质腐蚀掉,而干蚀刻是将化学气体吹到weafer表面上,与其发生反应,以实现蚀刻的目的.两者相比,后者的过程中的关键参数容易控制,用物理或化学的方法均可实现,且对图形的控制能力较强,而前者只能通过化学的方法实现,且对关键参数的控制能力较差,尤其是当线宽越来越细时,湿蚀刻将无法使用,但对于不同的蚀刻对象和环境,两者各有各自适合的范围,两种方法要根据工艺的要求不同来选择.在湿蚀刻的过程中还有一个重要的技术过程是waferdrying,因为湿的wafer是无法进入到下一道工序的,必须通过一些方法使其干燥,常用的方法有:Down-FlowSpinDryer既是利用高速旋转的方法,靠离心力的作用干燥;和IPAVaporDryer,MarangoniDryer等,其中Down-FlowSpinDryer因为力的作用,易形成watermark,且增加wafer的应力,转动过程中还会形成摩擦,而IPAVaporDryer和MarangoniDryer可防止watermark但时间较长,且化学用量多. 扩散Diffusion 扩散区间是进行加热制程的区域,这些制程可能是用来添加制程或者是用来加热制程,如在晶圆表面生成氧化层,扩散掺杂等是添加制程,而离子植入后用于恢复晶体结构的热处理是加热制程.高温炉是这区域的批量制程工具,它能够同时处理150片的wafer,可以将这些预置在硅芯片表面上的掺质,藉高温扩散的原理,把他们趋进芯片表面的材质内.。

芯片制造-半导体工艺教程Microchip Fabrication----A Practical Guide to Semicondutor Processing目录:第一章:半导体工业[1][2][3]第二章:半导体材料和工艺化学品[1][2][3][4][5]第三章:晶圆制备[1][2][3]第四章:芯片制造概述[1][2][3]第五章:污染控制[1][2][3][4][5][6]第六章:工艺良品率[1][2]第七章:氧化第八章:基本光刻工艺流程-从表面准备到曝光第九章:基本光刻工艺流程-从曝光到最终检验第十章:高级光刻工艺第十一章:掺杂第十二章:淀积第十三章:金属淀积第十四章:工艺和器件评估第十五章:晶圆加工中的商务因素第十六章:半导体器件和集成电路的形成第十七章:集成电路的类型第十八章:封装附录:术语表#1 第一章半导体工业--1芯片制造-半导体工艺教程点击查看章节目录by r53858概述本章通过历史简介,在世界经济中的重要性以及纵览重大技术的发展和其成为世界领导工业的发展趋势来介绍半导体工业。

并将按照产品类型介绍主要生产阶段和解释晶体管结构与集成度水平。

目的完成本章后您将能够:1. 描述分立器件和集成电路的区别。

2. 说明术语“固态,” “平面工艺”,““N””型和“P”型半导体材料。

3. 列举出四个主要半导体工艺步骤。

4. 解释集成度和不同集成水平电路的工艺的含义。

5. 列举出半导体制造的主要工艺和器件发展趋势。

一个工业的诞生电信号处理工业始于由Lee Deforest 在1906年发现的真空三极管。

1真空三极管使得收音机, 电视和其它消费电子产品成为可能。

它也是世界上第一台电子计算机的大脑,这台被称为电子数字集成器和计算器(ENIAC)的计算机于1947年在宾西法尼亚的摩尔工程学院进行首次演示。

这台电子计算机和现代的计算机大相径庭。

它占据约1500平方英尺,重30吨,工作时产生大量的热,并需要一个小型发电站来供电,花费了1940年时的400, 000美元。

英文回答:The LPCVD (Low Pressure Chemical Vapor Deposition) process plays a crucial role in the semiconductor manufacturing industry. It is extensively utilized for the deposition of thin films of various materials, such as silicon nitride, silicon oxide, and polysilicon, onto a silicon wafer. Operating within a vacuum chamber at low pressures, typically between 0.1 and 10 Torr, and at elevated temperatures ranging from 500 to 1100°C, this process involves the chemical reaction of precursor gases. These gases are introduced into the chamber and undergo dposition to form a solid film on the surface of the wafer. The LPCVD process is of paramount importance in the production of microelectronic and optoelectronic devices, as well as in the manufacture of thin film solar cells and other semiconductor-based products.LPCVD(低压化学蒸汽分解)工艺在半导体制造业中发挥着至关重要的作用。

[讲解]半导体制造技术作业

1. 什么叫集成电路,写出集成电路发展的五个时代及晶体管的数量,(15分)集成电路:将多个电子元件集成在一块衬底上,完成一定的电路或系统功能。

集成电路芯片/元件数产业周期无集成 1 1960年前小规模(SSI) 2到50 20世纪60年代前期

中规模(MSI) 50到5000 20世纪60年代到70年代前期

大规模(LSI) 5000到10万 20世纪70年代前期到后期

超大规模(VLSI) 10万到100万 20世纪70年代后期到80年代后期

甚大规模(ULSI) 大于100万 20世纪90年代后期到现在

2. 写出IC 制造的,个步骤,(15分)

Wafer preparation(硅片准备)

Wafer fabrication (硅片制造)

Wafer test/sort (硅片测试和拣选)

Assembly and packaging (装配和封装)

Final test(终测)

3. 写出半导体产业发展方向,什么是摩尔定律,(15分)

发展方向:提高芯片性能——提升速度(关键尺寸降低,集成度提高,研发采用新材料),降低功耗。

提高芯片可靠性——严格控制污染。

降低成本——线宽降低、晶片直径增加。

摩尔定律指:IC 的集成度将每隔一年翻一番。

1975年被修改为: IC 的集成度将每隔一年半翻一番。

4. 什么是特征尺寸CD,(10分) 最小特征尺寸,称为关键尺寸(Critical Dimension,CD)CD常用于衡量工艺难易的标志。

5. 什么是More moore定律和More than

Moore定律,(10分)

“More Moore”指的是芯片特征尺寸的不断缩小。

从几何学角度指的是为了提高密度、性能和可靠性在晶圆水平和垂直方向上的特征尺寸的继

续缩小。

与此关联的3D结构改善等非几何学工艺技术和新材料的运用来影响晶圆的电性能。

“More Than Moore”指的是用各种方法给最终用户提供附加价值,不一定要缩小特征尺寸如从系统组件级向3D集成或精确的封装级(SiP)或芯片级(SoC)转移。

6. 名词解释:high-k; low-k; Fabless; Fablite;

IDM; Foundry;Chipless(20分) high-k:高介电常数。

low-k:低介电常数。

IC 设计公司,只设计不生产。

Fabless:

Fablite:轻晶片厂,有少量晶圆制造厂的IC公司。

IDM:集成器件制造商(IDM-Integrated Device Manufactory Co.),从晶圆之设计、制造到以自有品牌行销全球皆一手包办。

Foundry:标准工艺加工厂或称专业代工厂商。

Chipless:既不生产也不设计芯片,而是设计IP内核,授权给半导体公司使用。

7. 例举出半导体产业的8种不同职业并简要描述. (15分)

1.硅片制造技师:负责操作硅片制造设备。

一些设备维护以及工艺和设备的基本故障查询。

2.设备技师:查询故障并维护先进设备系统,保证在硅片制造过程中设备能正确运行。

3.设备工程师:从事确定设备设计参数和优化硅片生产的设备性能。

4.工艺工程师:分析制造工艺和设备的性能以确定优化参数设置。

5.实验室技师:从事开发实验室工作,建立并进行试验。

6:成品率/失效分析技师:从事与缺陷分析相关的工作,如准备待分析的材料并操作分析设备以确定在硅片制造过程中引起问题的根源。

7.成品率提高工程师:收集并分析成品率及测试数据以提高硅片制造性能。