2016-2017秋季数字电子技术基础(B卷)

- 格式:doc

- 大小:195.00 KB

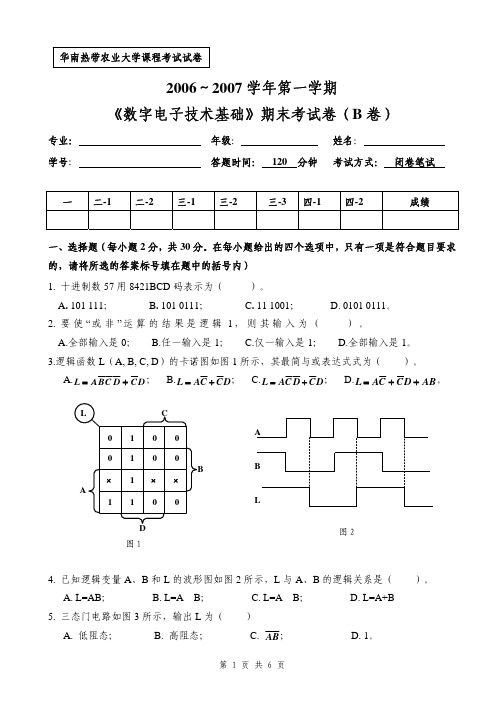

- 文档页数:4

第 1 页 共 12 页铜 陵 学 院2007-2008学年第二学期《数字电子技术基础》考试试卷(A 卷)(适用班级:06自动化本科)一、填空题(每空1分,共20分)1、数字信号是指在 和 上都不连续的信号。

2、二进制数11011转换为十进制数为 ,转换为十六进制数为 。

3、根据逻辑代数的运算规则有:A ·A = ,A ·A = 。

4、用4位二进制数表示一位十进制数,称为二-十进制代码,简称 码,最常用的二-十进制代码是 码。

5、按计数器中数值的增减分类,把计数器分为 、和可逆计数器。

6、计数器中,_____________计数器工作速度较快,_____________计数器电路结构简单。

7、一个容量为256×4位的RAM ,应有 个基本存储单元,每次访问 个基本存储单元,有 条数据线和 条地址线。

8、PROM 不可编程的逻辑阵列是 ,可编程的逻辑阵列是 。

9、逻辑代数中,最基本的三种逻辑运算是 运算、 运算和 运算。

二、判断题(第小题2分,共12分)1、真值表、逻辑代数式和逻辑电路图是同一逻辑功能的三种不同表达方式,只要知道其中一种,便可推出其它两种。

( )2、一个逻辑函数的所有最小项之积为1。

( )3、当用数码表示不同的事物时,这些数码已没有数量大小的含义。

( )4、TTL 门电路能带同类门的个数称为噪声容限。

( )5、计数器不仅能对时钟脉冲进行计数,还可以用于定时、分频、产生节拍脉冲等。

( ) 6、已知二输入端的TTL 与非门,将其中的一端经Ω100电阻接地,则当电源接通时,其输出端的状态为0。

( ) 三、选择题(每小题3分,共18分)1、若逻辑表达式F=C B A +·,则下列表达式中与F 功能相同的是( ) ①A B +C ②A B C ③AB C ④AB +C 2、函数F= AB+A C 的“或非-或非”表达式是( )①B A B A +++ ②(AB+A )·(AB+C ) ③C A B A + ④(A +B) ·(A+C) 3、一组合逻辑电路如用两级或非门实现,则其逻辑函数表达式应写成( )。

《数字电子技术基础》课后习题及参考答案(总90页)-CAL-FENGHAI.-(YICAI)-Company One1-CAL-本页仅作为文档封面,使用请直接删除第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)=177(2)=170(3)=241(4)=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)21(2)(9C)16=()2(3)(B1)16=(1011 0001)2(4)(AF)16=()2【题1-5】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)()2=(2)()2=(3)()2=【题1-6】将下列十进制数转换为二进制数。

(1);(2);(3);(4)解:(1)=()2(2)=()2(3)=()2(4)=()2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

(1)01101100;(2);(3);(4)解:(1)01101100是正数,所以其反码、补码与原码相同,为01101100(2)反码为,补码为(3)反码为,补码为(4)反码为,补码为【题1-8】将下列自然二进制码转换成格雷码。

数字电子技术基础试题及答案一TTA standardization office【TTA 5AB- TTAK 08- TTA 2C】数字电子技术基础期末考试试卷1. 时序逻辑电路一般由 和 两分组成。

2. 十进制数(56)10转换为二进制数为 和十六进制数为 。

3. 串行进位加法器的缺点是 ,想速度高时应采用 加法器。

4. 多谐振荡器是一种波形 电路,它没有稳态,只有两个 。

5. 用6个D 触发器设计一个计数器,则该计数器的最大模值M= 。

1.写出函数F (A,B,C,D) =A B C D E ++++的反函数。

2.证明逻辑函数式相等:()()BC D D B C AD B B D ++++=+ 3.已知逻辑函数F= ∑(3,5,8,9,10,12)+∑d(0,1,2) (1)化简该函数为最简与或式:(2)画出用两级与非门实现的最简与或式电路图: 4.555定时器构成的多谐振动器图1所示,已知R1=1KΩ,R2=Ω,C=μF 。

试求脉冲宽度T ,振荡频率f 和占空比q 。

图15.某地址译码电路如图2所示,当输入地址变量A7-A0的状态分别为什么状态 时,1Y 、6Y 分别才为低电平(被译中)。

………………………密……………………封…………………………装…………………订………………………线……………………… 学院 专业(班级) 姓名 学号……………………6.触发器电路就输入信号的波形如图3所示,试分别写出D触发器的Q和Q1的表达式,并画出其波形。

图D= Q n+1=Q1=7. 已知电路如图4所示,试写出:①驱动方程;②状态方程;③输出方程;④状态表;⑤电路功能。

图41.设计一个三变量偶检验逻辑电路。

当三变量A、B、C输入组合中的“1”的个数为偶数时F=1,否则F=0。

选用8选1数选器或门电路实现该逻辑电路。

要求:(1)列出该电路F(A,B,C)的真值表和表达式;(2)画出逻辑电路图。

A B C F2.试用74161、3-8译码器和少量门电路,实现图5所示波形VO1、VO2,其中CP为输入波形。

数字电子技术基础试题(一)一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

图 12.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

图2A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

图2A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析下列电路。

数字电子技术基础期末考试卷B卷答案GE GROUP system office room 【GEIHUA16H-GEIHUA GEIHUA8Q8-2.将十六进制数(FD)16转换为二进制数的结果是( B )A .()2B .()2C .(11111011)2D .()23.-0101的原码、反码和补码分别为( A )A .10101,11010,11011B .00101,11010,11011C .10101,11010,11010D .00101,01010,110114.逻辑函数式C AB AB )('+化简后的最简与或表达式为( D ) A .BC A +B .AC .C AB +')(D .C AB +5.逻辑函数)()(''+'+=E D C B A F 的反函数为 ( C )A . ))(('+''+E D CB A B . ))(('''+E DC B AC . ))((''+'+'ED C B A D . ))(('''+'E D C B A6.为实现将JK 触发器转换为D 触发器,应使( A )。

A . D K D J '==,B . D K D J ='=,C .D K J ==D .D K J '==7.一个4位移位寄存器原来的状态为0000,如果串行输入始终为1,则经过4个移位脉冲后寄存器的内容为( D )。

A . 0001B . 0111C . 1110D . 11118.石英晶体振荡器的主要优点是( B )A .电路简单B .频率稳定度高C .振荡频率高D .振荡频率低9.可以用来自动产生矩形波信号的是( D )A. 施密特触发器B. T 触发器C. 单稳态触发器D.多谐振荡器10.与非门...构成的SR 锁存器,使输出为“0”态的DS '、D R '端输入为:( C )A .0='='D DR S B .0='D S ,1='D R C .1='DS ,0='D R D .1='='D D R S 二、填空题(2分×15=30分) 1、 JK 触发器的特性方程为n n n Q K Q J Q +=+1。

数字电子技术基础考试试题B班级:学号:姓名:20分,每题2分,只答英文字母)同时应用隧道效应和雪崩击穿概念的存储单元是下列哪些?(A) 叠栅存储单元 (B) 隧道存储单元(C)闪速存储单元 (D) 动态存储单元2.下列哪些是无关项?(A) 最小项 (B) 最大项(C)任意项 (D) 乘积项3.TTL与非门集成电路输出晶体管处于深度饱和时,芯片具有哪些特征?(A) 抗干扰能力强 (B) 转换速度快(C)转换速度慢 (D) 较强的负载能力4.具有抗干扰能力最强的触发器是哪些?(A) 钟控RS触发器 (B) 主从RS触发器(C)延时边沿触发器 (D) 主从JK触发器 5.具有线与功能的电路有哪些?(A)普通TTL门(B)普通CMOS门(C)OC门(D)高速CMOS门6. 三态门的输出高阻和信号A在TTL门输入相与后,其结果是。

(A)0 (B)1(C)信号A(D)信号A取反7. 时序电路的原始状态转换表如表1所示,可简化为个状态。

表1 状态转换表S n+1/F(A)2 (B)1(C)3 (D)08. R-2R电阻网络D/A转换电路与权电阻网络D/A转换电路相比,克服 的缺点,提高了 。

(A )转换速度 (B )输出电流 (C )转换精度 (D )输出电压9. 集成555电路在控制电压端CO 处加控制电压U CO ,则5553个5k Ω对地的电阻的电压将为 。

(A )2U CO /3 (B )U CO /3 (C )U CO /2 (D )U CO 的信号通路固定,系统速度 。

(A )可以提供 (B )不可计算 (C )可以预测 (D )可以存储20分) 1. 用两个CMOS 传输门和一个CMOS 非门组成图二(1)框内电路,当输入X =1时,输出Z =C ;当输入X =0时,输出Z =B 。

2. 由边沿D 触发器组成的两个电路,如图二(2)(a )、(b )所示。

试分析两个电路在逻辑功能上的相同和不同之处。

A B CF铜 陵 学 院2007-2008学年第2学期《数字电子技术基础》考试试卷(B 卷)参考答案与评分细则一、真空题(每空1分,共20分)1、饱和,截止2、逢2进1,(1*23+1*21+1*20)3、A ,14、组合逻辑电路,时序逻辑电路5、存储数码,移位6、存储单元的总和,2048,8,117、与阵列,或阵列8、输入,输出9、n n Q K Q J +,D二、判断题(第小题2分,共12分) 2、4、正确,1、3、5、6错误三、选择题(每小题3分,共18分)1、③;2、③;3、②;4、②;5、④;6、①。

四、分析题(共50分) 1、(8分)解:最简逻函表达式为:BC B A ABC BC A C B A F +=++=2、(9分)解:逻函表达式为:AC BC AB AC BC AB F ++==真值表为:姓 班 ―――――――――装――――――――――订―――――――――线―――――――――――当A 、B 、C 中同时有两个或两个以上取1时,F 取值为1。

3、(8分) 解:4、(8分)解:由74LS138逻辑功能可写出其出入关系为:012701210120,,A A A Y A A A Y A A A Y ===要求实现的逻函表达式可化为:75431m m m m m ABC BC A C B A C B A C B A Z ++++=++++=若令C A B A A A ===012,,,则显然有:771100,,,m Y m Y m Y === ,于是逻函Z 可表为:75431Y Y Y Y Y Z =,由此可画出实现逻函Z 的电路如下:5、(9分)A C1 0 0解:根据74LS161的逻辑功能和题目要求,可设预置数为0101,并将进位信号经反相器反相后送给预置数控制端,这样计数器的状态便由0101→0110→0111→…→1111→0101,从而构成模9计数器,如图所示。

6、(8分)解:根据ROM 的逻辑功能和要求实现的逻函表达式可画出实现电路如下:1。

课目:数字电子技术专业:年级:学号:姓名:共2页第1页一、 填空题(每空一分,共20分)1.二进制(10110)2对应的十进制数为,十六进制数为。

2.二进制(0.1101)2对应的八进制数为,十六进制数为。

3.八进制(4.5)8对应的十进制数为,二进制数为。

4.十进制数(15.25)D对应的八进制数为,二进制数为。

5.余3码10010110.1100对应的8421码为,十进制数为。

6.逻辑代数三种基本运算为、、。

7.TTL三态电路的三种可能输出状态是,,。

8.负逻辑的特点是、。

9.时序逻辑电路当前输出不仅与当前输入,而且与过去的输入。

(a)有关(b)无关二、写出下列函数的对偶式G和反演式F。

(10分)()F A=+三、试求出下列逻辑函数的最简与或表达式。

(20分)1.1()()F A B C A B C =++++2.2()F A B C ABC ABC=⊕++3.3()F AD BC D A B C=+++4.4(,,,)(0,2,6,7,8,9,10,13,14,15)F A B C D m=∑5.5F AB AC BC BCD BE BCE BCF=++++++四、触发器电路如图(A)所示,已知CP、A、B波形如图(B),并设触发器初态为0,写出触发器的次态方程,并画出Q1,Q2端波形。

(10分)图(A)图(B)课 目:数字电子技术 专 业: 年 级: 学 号: 姓 名: 共2页 第 2页五、用8选1多路数据选择器实现一个组合电路,其输入是一位8421编码的十进制数。

要求当输入的数能被3整除时,电路输出为1。

要求列出真值表,并划出逻辑图。

(10分)六、一组合逻辑运算电路,其输入321X A A A =、输出321Y B B B =均为三位二进制数。

要求当04X ≤≤时,输出3Y X =+,而且X 不大于4。

试用“与非”门设计该运算电路,具体要求是:(1)列出真值表; (2)用K 图法化简; (3)用“与非”门写出各输出端的逻辑表达式。

第 - 1 -页 共 4 页

Xx 大学试卷

课程代码: 课程:数字电子技术基础(B 卷)

一、填空题(共30分,每空2分)

1、 (1100101.01)2=( )8=( )16

2、 逻辑函数 (,,)()()Y A B C A C B C =++的最大项表达式为(写成M ∏型) ;

F AB BC =+的最小项表达式为(写成m ∑型) 。

3、 循环码有两个显著特点,其一是 ,其二是 。

4、 TTL 或门多余输入端的处理方法是 。

5、 TTL 三态门的三种可能的输出状态分别是 、 、 。

6、 用来描述逻辑函数的四种常用方法有逻辑式描述、真值表描述、 、 。

7、 T '触发器的特性方程可以表示为 。

8、 脉冲宽度与脉冲周期的比值称为 。

9、 计数器可对 计数。

二、单项选择题(每题1分,共10分)

1、下列信号中( )是数字信号。

A )交流电压

B )开关状态

C )交流电流

D )无线电载波无

2、指出下列各式中,哪个是四变量A 、B 、C 、D 中最大项( ) A )(A C)(B+D)+ B )A B C D +++ C )ABCD D )AC BC +

3、以下代码中为有权码的是( )。

A )8421BCD 码

B )格雷码

C )余3码

D )余3循环码 4、AD AC BC AB +++中的冗余项为( )。

A )AD B ) AC C )BC D )AB

5、逻辑式Y AC AB AC =++中存在( )冒险。

A )0

B )1

C )0,1

D )无冒险 6、下列逻辑电路中,是组合逻辑电路的是( )。

A )数码寄存器

B )计数器

C )移位寄存器

D )加法器 7、一个8选一的数据选择器,其地址输入端有( )个。

A )2 B )3 C )4 D )5

8、当1,0,1D D CP R S ===,钟控RS 触发器的11,n n Q Q ++的值为( )。

A )1,0

B )0,1

C )1,1

D )0,0 9、4096×8位的RAM ,其存储容量为( )Kbits 。

A )64

B )32

C )16

D )8

10、若输入变量A ,B 取值相同时,输出F=0,否则F=1,则其输出与输入的关系是( )。

A )与或运算 B )异或运算 C )同或运算 D )与非运算

三、判断题(10分,每题2分)

1、 逻辑变量的取值,0比1小。

( )

2、 逻辑函数表达式的化简结果有可能不唯一。

( )

第 - 2 -页 共 4 页

3、 异或函数与同或函数在逻辑上符合对偶规则。

( )

4、 A+AB=A 成立,则AB=0成立。

( )

5、 组合逻辑电路的特点是任何时刻的输出只由当前的输入决定,与电路的其它状态无关。

( )

四、基础题(共30分)

1、代数化简法化简:Y AC ABC AC D CD =+++(5分)

2、卡诺图化简:(,,,)(0,2,6,7,8,10,14,15)F A B C D m =

∑(5分)

3、分析下图所示电路的输出逻辑式。

(5分)

4、画出下面电路的输出波形图,设JK 触发器的初始状态为0。

(5分)

5、写出如图所示电路的驱动方程和状态方程,列出状态表,画出状态图,判断电路能否自启动?(10分)

五、分析设计题(共20分)

1、用74LS161设计8进制计数器,允许添加适当的逻辑门电路,要求用同步置数LD端实现,预置数

3210

0011

D D D D=。

(5分)

(

32103

,

=⋅⋅⋅⋅

C Q Q Q Q ET Q为计数器的高位输出)

2、用与非门设计一个三变量的偶数判断电路,使当三个输入变量A、B、C中0的个数为偶数时,电路的输出Y为1。

(共7分)

(1)列出真值表。

(3分)

(2)求出逻辑式,并用最少的与非门实现该电路。

(4分)。

第- 3 -页共 4 页

第 - 4 -页 共 4 页

3、设计一位全加器,加数 A ,被加数 B ,和为S ,低位来的进位CI ,向高位的进位CO 。

(共8分)

要求: ①列出真值表; (4分)

②用译码器 74LS138 实现; (4分)。