VHDL参考程序4

- 格式:doc

- 大小:31.50 KB

- 文档页数:4

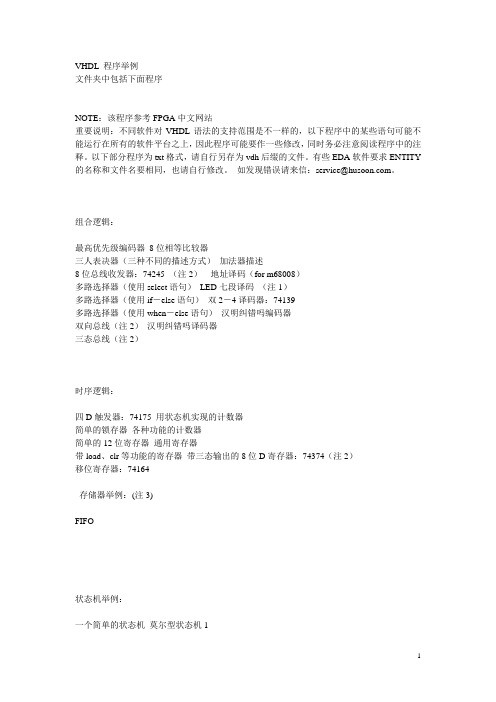

VHDL 程序举例文件夹中包括下面程序--------------------------------------------------------------------------------NOTE:该程序参考FPGA中文网站重要说明:不同软件对VHDL语法的支持范围是不一样的,以下程序中的某些语句可能不能运行在所有的软件平台之上,因此程序可能要作一些修改,同时务必注意阅读程序中的注释。

以下部分程序为txt格式,请自行另存为vdh后缀的文件。

有些EDA软件要求ENTITY 的名称和文件名要相同,也请自行修改。

如发现错误请来信:service@。

组合逻辑:最高优先级编码器8位相等比较器三人表决器(三种不同的描述方式)加法器描述8位总线收发器:74245 (注2)地址译码(for m68008)多路选择器(使用select语句)LED七段译码(注1)多路选择器(使用if-else语句)双2-4译码器:74139多路选择器(使用when-else语句)汉明纠错吗编码器双向总线(注2)汉明纠错吗译码器三态总线(注2)时序逻辑:四D触发器:74175 用状态机实现的计数器简单的锁存器各种功能的计数器简单的12位寄存器通用寄存器带load、clr等功能的寄存器带三态输出的8位D寄存器:74374(注2)移位寄存器:74164存储器举例:(注3)FIFO状态机举例:一个简单的状态机莫尔型状态机1使用列举类型的状态机莫尔型状态机2带同步复位的状态机米勒型状态机使用变量的状态机带莫尔/米勒输出的状态机测试向量(Test Bench)举例:加法器源程序相应加法器的测试向量(test bench)波形发生器(含test beach)(注1) 经典双进程状态机(含test beach)其他设计举例:伪随机数产生器一个简单的UART步进电机控制器一个游戏程序直流电机控制器布斯乘法器伪随机比特发生器注1:含有不可综合语句,请自行修改注2:一些PLD只允许I/O口对外三态,不支持内部三态,使用时要注意注3: 设计RAM的最好方法是利用器件厂家提供的软件自动生成RAM元件,并在VHDL 程序中。

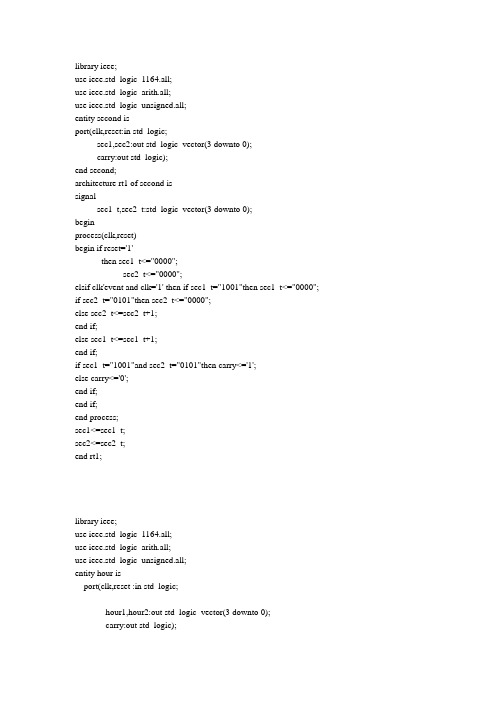

use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity second isport(clk,reset:in std_logic;sec1,sec2:out std_logic_vector(3 downto 0);carry:out std_logic);end second;architecture rt1 of second issignalsec1_t,sec2_t:std_logic_vector(3 downto 0);beginprocess(clk,reset)begin if reset='1'then sec1_t<="0000";sec2_t<="0000";elsif clk'event and clk='1' then if sec1_t="1001"then sec1_t<="0000"; if sec2_t="0101"then sec2_t<="0000";else sec2_t<=sec2_t+1;end if;else sec1_t<=sec1_t+1;end if;if sec1_t="1001"and sec2_t="0101"then carry<='1';else carry<='0';end if;end if;end process;sec1<=sec1_t;sec2<=sec2_t;end rt1;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity hour isport(clk,reset :in std_logic;hour1,hour2:out std_logic_vector(3 downto 0);carry:out std_logic);architecture rt1 of hour issignal hour1_t,hour2_t:std_logic_vector(3 downto 0);beginprocess(clk,reset)beginif reset='1' thenhour1_t<="0000";hour2_t<="0000";carry <='0';elsif clk'event and clk='1' thenif hour1_t="1001" then hour1_t<="0000";hour2_t<=hour2_t+1;carry <='0';elseif hour1_t="0011" and hour2_t="0010" thenhour1_t<="0000";hour2_t<="0000";carry <='1';elsehour1_t<=hour1_t+1;carry <='0';end if;end if;end if;end process;hour1<=hour1_t;hour2<=hour2_t;end rt1;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity xs isport(data :in std_logic_vector(3 downto 0);dout: out std_logic_vector(6 downto 0));end entity xs;architecture behav of xs isbegin process(data)begin case data iswhen"0000"=>dout<="1111110";when"0001"=>dout<="0110000";when"0010"=>dout<="1101101";when"0011"=>dout<="1111001";when"0100"=>dout<="0110011";when"0101"=>dout<="1011011";when"0110"=>dout<="1011111";when"0111"=>dout<="1110010";when"1000"=>dout<="1111111";when"1001"=>dout<="1111011";when others=>dout<="0000000";end case;end process;end behav;LIBRARY IEEE;--40M to 2HZUSE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY fenpin1 ISGENERIC (width :INTEGER :=26);PORT ( clk_in : IN ST·D_LOGIC;clk_out : OUT STD_LOGIC );END ENTITY fenpin1;ARCHITECTURE one OF fenpin1 ISSIGNAL count1 : STD_LOGIC_VECTOR (width -1 DOWNTO 0); BEGINPROCESS (clk_in)BEGINIF ( clk_in'EVENT AND clk_in='1' ) THENIF (count1 < 16#1312CFF# ) THENcount1 <= count1 +1;ELSE count1 <= (OTHERS =>'0') ;END IF;END IF;END PROCESS;PROCESS(count1)BEGINIF (count1 < 16#989680# ) THENclk_out <= '0';ELSEclk_out <= '1';END IF;END PROCESS;END one;LIBRARY IEEE;--2HZ to 1HZUSE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY fenpin2 ISPORT(clk_in:in std_logic;clk_out:buffer std_logic);end fenpin2;ARCHITECTURE one OF fenpin2 ISbeginPROCESS (clk_in)BEGINIF ( clk_in'EVENT AND clk_in='1') THENclk_out<=not clk_out;END IF;END PROCESS;END one;library ieee;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;entity mux61 isport(sec1,sec2,sec3,sec4,hour1,hour2:in std_logic_vector(3 downto 0);y:out std_logic_vector(3 downto 0);clk_in:in std_logic);end entity mux61;architecture rt1 of mux61 issignal s_t:std_logic_vector(2 downto 0); beginp1: process(clk_in,s_t)beginif clk_in'event and clk_in='1' thenif s_t="101" then s_t<="000";else s_t<=s_t+1;end if;end if;end process p1;p2: process(s_t)begincase s_t isWHEN "000" => y<=sec1;WHEN "001" => y<=sec2;WHEN "010" => y<=sec3;WHEN "011" => y<=sec4;WHEN "100" => y<=hour1;WHEN "101" => y<=hour2;WHEN OTHERS => null;END CASE;END PROCESS p2 ;end rt1;。

vhdl语言100例程序以下是100个关于VHDL语言的程序示例:1. 用VHDL编写一个计数器模块2. 用VHDL编写一个SR-Latch模块3. 用VHDL编写一个JK-Flip Flop模块4. 用VHDL编写一个D-Flip Flop模块5. 用VHDL编写一个T-Flip Flop模块6. 用VHDL编写一个复位计数器模块7. 用VHDL编写一个移位寄存器模块8. 用VHDL编写一个状态机模块9. 用VHDL编写一个MUX模块10. 用VHDL编写一个DeMUX模块11. 用VHDL编写一个加法器模块12. 用VHDL编写一个减法器模块13. 用VHDL编写一个乘法器模块14. 用VHDL编写一个除法器模块15. 用VHDL编写一个比较器模块16. 用VHDL编写一个位逻辑模块17. 用VHDL编写一个字逻辑模块18. 用VHDL编写一个数据选择器模块19. 用VHDL编写一个FIFO队列模块20. 用VHDL编写一个LIFO栈模块21. 用VHDL编写一个流水线模块22. 用VHDL编写一个中断控制器模块23. 用VHDL编写一个时钟分频器模块24. 用VHDL编写一个IO控制器模块25. 用VHDL编写一个SPI通信控制器模块26. 用VHDL编写一个I2C通信控制器模块27. 用VHDL编写一个UART通信控制器模块28. 用VHDL编写一个哈希函数模块29. 用VHDL编写一个随机数产生器模块30. 用VHDL编写一个CRC校验器模块31. 用VHDL编写一个AES加密算法模块32. 用VHDL编写一个DES加密算法模块33. 用VHDL编写一个SHA加密算法模块34. 用VHDL编写一个MD5加密算法模块35. 用VHDL编写一个RSA加密算法模块36. 用VHDL编写一个卷积滤波器模块37. 用VHDL编写一个峰值检测器模块38. 用VHDL编写一个平滑滤波器模块39. 用VHDL编写一个中值滤波器模块40. 用VHDL编写一个微处理器模块41. 用VHDL编写一个信号发生器模块42. 用VHDL编写一个信号采集器模块43. 用VHDL编写一个频率计算器模块44. 用VHDL编写一个相位计算器模块45. 用VHDL编写一个时序分析器模块46. 用VHDL编写一个正弦波产生器模块47. 用VHDL编写一个余弦波产生器模块48. 用VHDL编写一个数字滤波器模块49. 用VHDL编写一个数字信号处理器模块50. 用VHDL编写一个数字识别模块51. 用VHDL编写一个自动售货机模块52. 用VHDL编写一个二进制加法器模块53. 用VHDL编写一个二进制减法器模块54. 用VHDL编写一个二进制乘法器模块55. 用VHDL编写一个二进制除法器模块56. 用VHDL编写一个自然对数模块57. 用VHDL编写一个指数函数模块58. 用VHDL编写一个三角函数模块59. 用VHDL编写一个高斯滤波器模块60. 用VHDL编写一个激光传感器模块61. 用VHDL编写一个超声波传感器模块62. 用VHDL编写一个光电传感器模块63. 用VHDL编写一个温度传感器模块64. 用VHDL编写一个气压传感器模块65. 用VHDL编写一个陀螺仪模块67. 用VHDL编写一个电流传感器模块68. 用VHDL编写一个电容传感器模块69. 用VHDL编写一个磁场传感器模块70. 用VHDL编写一个通信电缆模块71. 用VHDL编写一个电源控制器模块72. 用VHDL编写一个电机控制器模块73. 用VHDL编写一个汽车控制器模块74. 用VHDL编写一个飞机控制器模块75. 用VHDL编写一个摄像头模块76. 用VHDL编写一个音频控制器模块77. 用VHDL编写一个扬声器控制器模块78. 用VHDL编写一个拨号器模块79. 用VHDL编写一个振动控制器模块80. 用VHDL编写一个压力控制器模块81. 用VHDL编写一个过滤器模块82. 用VHDL编写一个微波发射模块84. 用VHDL编写一个智能电表模块85. 用VHDL编写一个闹钟模块86. 用VHDL编写一个计时器模块87. 用VHDL编写一个时间戳模块88. 用VHDL编写一个脉冲宽度模块89. 用VHDL编写一个电路仿真模块90. 用VHDL编写一个电路控制模块91. 用VHDL编写一个电路测试模块92. 用VHDL编写一个电路优化模块93. 用VHDL编写一个电路布局模块94. 用VHDL编写一个电路验证模块95. 用VHDL编写一个数字信号发生器模块96. 用VHDL编写一个数字信号反演器模块97. 用VHDL编写一个数字信号滤波器模块98. 用VHDL编写一个数字信号加速器模块99. 用VHDL编写一个数字信号降噪器模块100. 用VHDL编写一个数字信号解调器模块VHDL语言是一种硬件描述语言,它用于描述数字电路和系统。

这是茄子求别人写的参考程序,不一定能实际运行。

但是可靠性在百分之九十左右。

大家做不出来的可以参考下。

做出来的看出错误请指正。

我作为学习委员既然把答案给大家,一方面是不想影响大家平时成绩,另一方面也是希望大家可以自己看看,学习一下,不要到最后结课了着急。

所以我晚上不收打印的作业,每个人都必须亲自抄写出来。

行为描述方式LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADD11 ISPORT(A:IN STD_LOGIC;B:IN STD_LOGIC;CIN:IN STD_LOGIC;CO:OUT STD_LOGIC;S:OUT STD_LOGIC);END ADD11;ARCHITECTURE BEHAVE OF ADD11 ISBEGINPROCESS(A,B,CIN)VARIABLE N: INTEGER RANGE 0 TO 3;CONSTANT S_VECTOR:STD_LOGIC_VECTOR(0 TO 3):="1010";CONSTANT CO_VECTOR:STD_LOGIC_VECTOR(0 TO 3):="1100";BEGINN:=0;IF(A='1') THEN N:=N+1;END IF;IF(B='1') THEN N:=N+1;END IF;IF(CIN='1') THEN N:=N+1;END IF;S<=S_VECTOR(N);CO<=CO_VECTOR(N);END PROCESS;END BEHAVE;数据流描述方式LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY ADD2 ISPORT(A:IN STD_LOGIC;B:IN STD_LOGIC;CIN:IN STD_LOGIC;CO:OUT STD_LOGIC;S:OUT STD_LOGIC);END ADD2;ARCHITECTURE DATAFLOW OF ADD2 IS SIGNAL TMP1,TMP2:STD_LOGIC; BEGINTMP1<=A XOR B;TMP2<=TMP1 AND CIN;S<=TMP1 XOR CIN;CO<=TMP2 OR(A AND B);END DATAFLOW;结构体描述方式LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY ADD3 ISPORT(A:IN STD_LOGIC;B:IN STD_LOGIC;CIN:IN STD_LOGIC;CO:OUT STD_LOGIC;S:OUT STD_LOGIC);END ADD3;ARCHITECTURE STRUCTURE OF ADD3 IS COMPONENT AND2PORT(A: IN STD_LOGIC;B: IN STD_LOGIC;C: OUT STD_LOGIC);END COMPONENT;COMPONENT OR2PORT(A: IN STD_LOGIC;B: IN STD_LOGIC;C: OUT STD_LOGIC);END COMPONENT;COMPONENT XOR2PORT(A: IN STD_LOGIC;B: IN STD_LOGIC;C: OUT STD_LOGIC);END COMPONENT;SIGNAL TMP1,TMP2,TMP3:STD_LOGIC; BEGINU1:XOR2 PORT MAP(A,B,TMP1);U2:AND2 PORT MAP(TMP1,CIN,TMP2); U3:XOR2 PORT MAP(TMP1,CIN,S);U4:AND2 PORT MAP(A,B,TMP3);U5:OR2 PORT MAP(TMP2,TMP3,CO); END STRUCTURE;。

VHDL语言设计与门:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY AN ISPORT ( A,B: IN STD_LOGIC ;Y : OUT STD_LOGIC );END ENTITY AN;ARCHITECTURE AC OF AN ISBEGINY<=A AND B;END ARCHITECTURE AC;或门:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY BN ISPORT ( A,B: IN STD_LOGIC ;Y : OUT STD_LOGIC );END ENTITY BN;ARCHITECTURE BC OF BN ISBEGINY<=A OR B;END ARCHITECTURE BC;非门:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY DN ISPORT ( B: IN STD_LOGIC ;Y : OUT STD_LOGIC );END ENTITY DN;ARCHITECTURE AC OF DN ISBEGINY<= NOT B;END ARCHITECTURE AC;与非:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ; ENTITY CN ISPORT ( A,B: IN STD_LOGIC ;Y : OUT STD_LOGIC );END ENTITY CN;ARCHITECTURE AC OF CN ISBEGINY<=A NAND B;END ARCHITECTURE AC;或非:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ; ENTITY HF ISPORT ( A,B: IN STD_LOGIC ;Y : OUT STD_LOGIC );END ENTITY HF; ARCHITECTURE AC OF HF ISBEGINY<=A NOR B;END ARCHITECTURE AC;异或:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ; ENTITY FN ISPORT ( A,B: IN STD_LOGIC ;Y : OUT STD_LOGIC );END ENTITY FN;ARCHITECTURE AC OF FN ISBEGINY<=A XOR B;END ARCHITECTURE AC;同或:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY EN ISPORT ( A,B: IN STD_LOGIC ;Y : OUT STD_LOGIC );END ENTITY EN;ARCHITECTURE AC OF EN ISBEGINY<=A XNOR B;END ARCHITECTURE AC;三线——八线译码器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY GN ISPORT ( A,B,C: IN STD_LOGIC ;Y0,Y1,Y2,Y3,Y4,Y5,Y6,Y7 : OUT STD_LOGIC ); END ENTITY GN;ARCHITECTURE DC OF GN ISBEGINY0<= NOT A AND NOT B AND NOT C;Y1<= NOT A AND NOT B AND C;Y2<= NOT A AND B AND NOT C;Y3<= NOT A AND B AND C;Y4<= A AND NOT B AND NOT C;Y5<= A AND NOT B AND C;Y6<= A AND B AND NOT C;Y7<= A AND B AND C;END ARCHITECTURE DC;八选一数据选择器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY H1N ISPORT ( A,B,C,D,E,F,G,H: IN STD_LOGIC ;Y1,Y2,Y3 : OUT STD_LOGIC );END ENTITY H1N;ARCHITECTURE AC OF H1N ISBEGINY1<= A OR B OR C OR D;Y2<= E OR F OR B OR A;Y3<= G OR E OR C OR A; END ARCHITECTURE AC;。

测频控制电路***************************************LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY FTCTRL ISPORT(CLK: IN STD_LOGIC;CNT_EN: OUT STD_LOGIC;RST_CNT: OUT STD_LOGIC;Load: OUT STD_LOGIC );END FTCTRL ;ARCHITECTURE behav OF FTCTRL ISSIGNAL Div2CLK :STD_LOGIC;BEGINPROCESS (CLK)BEGINIF CLK'EVENT AND CLK='1' THENDiv2CLK<=NOT Div2CLK;END IF;END PROCESS;PROCESS(CLK,Div2CLK)BEGINIF CLK='0' AND Div2CLK='0' THEN RST_CNT<='1';----产生计数器清零信号ELSE RST_CNT<='0';END IF;END PROCESS;Load <=NOT Div2CLK; CNT_EN <=Div2CLK;END behav;***************************************锁存器***************************************LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL;ENTITY REG32B ISPORT (LK:IN STD_LOGIC;DIN :IN STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END ENTITY REG32B;ARCHITECTURE behav OF REG32B ISBEGINPROCESS (LK,DIN)BEGINIF LK'EVENT AND LK = '1' THEN DOUT <=DIN;END IF;END PROCESS;END behav ;***************************************计数器***************************************LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY COUNTER32B ISPORT(FIN: IN STD_LOGIC;CLR: IN STD_LOGIC;ENABL: IN STD_LOGIC;COUT : OUT STD_LOGIC;DOUT: OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END COUNTER32B ;ARCHITECTURE behav OF COUNTER32B ISSIGNAL CQI :STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINPROCESS (FIN,CLR,ENABL)BEGINIF CLR='1' THEN CQI <=(OTHERS=>'0');ELSIF FIN'EVENT AND FIN='1' THENIF ENABL = '1' THEN CQI <=CQI+1;END IF;IF CQI =9 THEN CQI <="0000";COUT<='1';ELSE COUT<='0';END IF;END IF;END PROCESS;DOUT<=CQI;END behav;***************************************频率计顶层文件***************************************LIBRARY IEEE;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY FREQUTEST ISPORT ( CLK1HZ : IN STD_LOGIC;FSIN : IN STD_LOGIC;DOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT1 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT2 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT3 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) );END FREQUTEST;ARCHITECTURE struc OF FREQUTEST ISCOMPONENT FTCTRLPORT (CLK : IN STD_LOGIC; --1HzCNT_EN : OUT STD_LOGIC; --计数器时钟使能信号端RST_CNT : OUT STD_LOGIC; --计数器清零端Load : OUT STD_LOGIC ); --输出锁存信号端END COMPONENT;COMPONENT COUNTER32BPORT (FIN : IN STD_LOGIC; --时钟信号CLR : IN STD_LOGIC; --清零信号ENABL : IN STD_LOGIC; --计数器使能信号COUT : OUT STD_LOGIC;DOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); --计数结果输出END COMPONENT;COMPONENT REG32BPORT (LK : IN STD_LOGIC;DIN : IN STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) );END COMPONENT;SIGNAL TSTEN1 : STD_LOGIC;SIGNAL CLR_CNT1 : STD_LOGIC;SIGNAL Load1 : STD_LOGIC;SIGNAL CARRY_OUT1 : STD_LOGIC;SIGNAL CARRY_OUT2 : STD_LOGIC;SIGNAL CARRY_OUT3 : STD_LOGIC;SIGNAL DTO1 : STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL DTO2 : STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL DTO3 : STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL DTO4 : STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINU1 : FTCTRL PORT MAP(CLK =>CLK1Hz,CNT_EN =>TSTEN1,RST_CNT =>CLR_CNT1,Load =>Load1);U2 : REG32B PORT MAP( LK =>Load1,DIN=>DTO1,DOUT =>DOUT);U3 : COUNTER32B PORT MAP( FIN =>FSIN,CLR=>CLR_CNT1,ENABL=>TSTEN1,COUT=>CARRY_OUT1,DOUT =>DTO1);U4 : COUNTER32B PORT MAP( FIN =>CARRY_OUT1,CLR=>CLR_CNT1,ENABL=>TSTEN1,COUT=>CARRY_OUT2,DOUT =>DTO2);U5 : REG32B PORT MAP( LK =>Load1,DIN=>DTO2,DOUT =>DOUT1);U6 : COUNTER32B PORT MAP( FIN =>CARRY_OUT2,CLR=>CLR_CNT1,ENABL=>TSTEN1,COUT=>CARRY_OUT3,DOUT =>DTO3);U7 : REG32B PORT MAP( LK =>Load1,DIN=>DTO3,DOUT =>DOUT2);U8 : COUNTER32B PORT MAP( FIN =>CARRY_OUT3,CLR=>CLR_CNT1,ENABL=>TSTEN1,DOUT =>DTO4);U9 : REG32B PORT MAP( LK =>Load1,DIN=>DTO4,DOUT =>DOUT3);END struc;。

VHDL参考程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dz02 isport(clk:in std_logic;a:out std_logic_vector(4 downto 0);q:out std_logic_vector(7 downto 0));end;architecture qq of dz02 issignal output:std_logic_vector(7 downto 0);beginprocess(clk)variable address:std_logic_vector(4 downto 0);variable cnt:std_logic_vector(9 downto 0);variable word:std_logic_vector(1 downto 0);beginif clk'event and clk='1' thenaddress:=address+1;cnt:=cnt+1;if cnt="11111111111111" then cnt:="00000000000000";word:=word+1;if word="11" then word:="00";end if;end if;a<=address;end if;case word iswhen"00"=>case address iswhen"00001"=>output<="00000100";when"00000"=>output<="00000000";when"11111"=>output<="00000000";when"11110"=>output<="11111111";when"01010"=>output<="00000000";when"01001"=>output<="11000100";when"01000"=>output<="10110100";when"00111"=>output<="10001100";when"00110"=>output<="11100111";when"00101"=>output<="10000100";when"00100"=>output<="10000100";when"00011"=>output<="10000100";when"00010"=>output<="10000100";when"00000"=>output<="00000000";when"11111"=>output<="00000000";when"11110"=>output<="11111111";when"11101"=>output<="00000010";when"11100"=>output<="00000100";when"11011"=>output<="00100011";when"11010"=>output<="00010000";when"11001"=>output<="00001100";when"11000"=>output<="00100000";when"10111"=>output<="10000000";when"10110"=>output<="01111111";when"10101"=>output<="00000000";when"10100"=>output<="00000010";when"10011"=>output<="00000100";when"10010"=>output<="00011000";when"10001"=>output<="00110000";when"10000"=>output<="00000000";when others=>null;end case;when"01"=>case address iswhen"01111"=>output<="00000000";when"01110"=>output<="01111111";when"01101"=>output<="00100010";when"01100"=>output<="00100010";when"01011"=>output<="00100010";when"01010"=>output<="11111110";when"01001"=>output<="00000000";when"01000"=>output<="00000000";when"00111"=>output<="11111111";when"00110"=>output<="00010001";when"00101"=>output<="00010001";when"00100"=>output<="00010001";when"00011"=>output<="00010001";when"00010"=>output<="11111111";when"00001"=>output<="00000000";when"00000"=>output<="00000000";when"11111"=>output<="00000000";when"11110"=>output<="00000011";when"11101"=>output<="00000010";when"11100"=>output<="00000010";when"11011"=>output<="00000010";when"11010"=>output<="00100011";when"11000"=>output<="00011000"; when"10111"=>output<="00000111"; when"10110"=>output<="00000001"; when"10101"=>output<="00000001"; when"10100"=>output<="00100001"; when"10011"=>output<="10000001"; when"10010"=>output<="01111111"; when"10001"=>output<="00000000"; when"10000"=>output<="00000000"; when others=>null;end case;case word iswhen 10=>when"01111"=>output<="00000000"; when"01110"=>output<="11111110"; when"01101"=>output<="00100010"; when"01100"=>output<="01010010"; when"01011"=>output<="10001110"; when"01010"=>output<="00000000"; when"01001"=>output<="11000100"; when"01000"=>output<="10110100"; when"00111"=>output<="10001100"; when"00110"=>output<="11100111"; when"00101"=>output<="10000100"; when"00100"=>output<="10000100"; when"00011"=>output<="10000100"; when"00010"=>output<="10000100"; when"00001"=>output<="00000100"; when"00000"=>output<="00000000"; when"11111"=>output<="00000000"; when"11110"=>output<="11111111"; when"11101"=>output<="00000010"; when"11100"=>output<="00000100"; when"11011"=>output<="00100011"; when"11010"=>output<="00010000"; when"11001"=>output<="00001100"; when"11000"=>output<="00100000"; when"10111"=>output<="10000000"; when"10110"=>output<="01111111"; when"10101"=>output<="00000000"; when"10100"=>output<="00000010"; when"10011"=>output<="00000100"; when"10010"=>output<="00011000";when"10000"=>output<="00000000";when others=>null;end case;when others=>output<="00000000";end case;q<=output;end process;end;。