VHDL语言程序的基本结构

- 格式:ppt

- 大小:591.55 KB

- 文档页数:62

1、简述信号与变量的区别。

a.信号延时赋值,变量立即赋值b.信号的代入使用<=,变量的代入使用:=;c.信号在实际的硬件当中有对应的连线,变量没有2、简述可编程逻辑器件的优点。

a.集成度高,可以替代多至几千块通用IC芯片.极大减小电路的面积,降低功耗,提高可靠性b.具有完善先进的开发工具.提供语言、图形等设计方法,十分灵活.通过仿真工具来验证设计的正确性c.可以反复地擦除、编程,方便设计的修改和升级d.灵活地定义管脚功能,减轻设计工作量,缩短系统开发时间f.保密性好3、试比较moore状态机与mealy状态机的异同。

Moore输出只是状态机当前状态的函数. Mealy输出为有限状态机当前值和输入值的函数3、简述VHDL语言与计算机语言的差别。

a. 运行的基础。

计算机语言是在CPU+RAM构建的平台上运行。

VHDL设计的结果是由具体的逻辑、触发器组成的数字电路b.执行方式.计算机语言基本上以串行的方式执行.VHDL在总体上是以并行方式工作c.验证方式.计算机语言主要关注于变量值的变化.VHDL要实现严格的时序逻辑关系6、VHDL与计算机语言的区别?VHDL语言可以并行执行,计算机语言只能顺序执行。

3.1比较常用硬件描述语言VHDL、Verilog和ABEL语言的优劣。

1.VHDL:描述语言层次较高,不易控制底层电路,因而对综合器的性能要求较高。

有多种EDA工具选择,已成为IEEE标准。

应用VHDL进行工程设计的优点是多方面的,具体如下:(1) 与其他的硬件描述语言相比,VHDL具有更强的行为描述能力。

(2) VHDL具有丰富的仿真语句和库函数,使得在任何大系统的设计早期,就能查验设计系统的功能可行性,随时可对系统进行仿真模拟,使设计者对整个工程的结构和功能可行性做出判断。

(3) VHDL语句的行为描述能力和程序结构,决定了它具有支持大规模设计的分解和已有设计的再利用功能。

(4) 用VHDL完成一个确定的设计,可以利用EDA工具进行逻辑综合和优化,并自动把VHDL描述设计转变成门级网表(根据不同的实现芯片)。

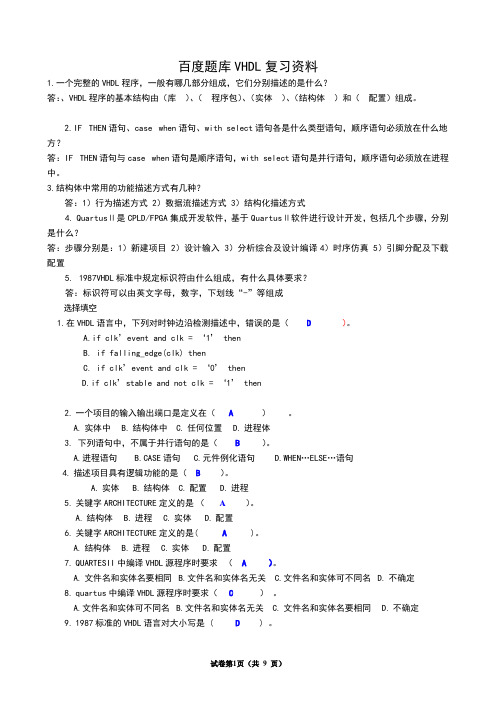

百度题库VHDL复习资料1.一个完整的VHDL程序,一般有哪几部分组成,它们分别描述的是什么?答:、VHDL程序的基本结构由(库)、(程序包)、(实体)、(结构体)和(配置)组成。

2.IF THEN语句、case when语句、with select语句各是什么类型语句,顺序语句必须放在什么地方?答:IF THEN语句与case when语句是顺序语句,with select语句是并行语句,顺序语句必须放在进程中。

3.结构体中常用的功能描述方式有几种?答:1)行为描述方式 2)数据流描述方式 3)结构化描述方式4.QuartusⅡ是CPLD/FPGA集成开发软件,基于QuartusⅡ软件进行设计开发,包括几个步骤,分别是什么?答:步骤分别是:1)新建项目 2)设计输入 3)分析综合及设计编译4)时序仿真 5)引脚分配及下载配置5.1987VHDL标准中规定标识符由什么组成,有什么具体要求?答:标识符可以由英文字母,数字,下划线“-”等组成选择填空1.在VHDL语言中,下列对时钟边沿检测描述中,错误的是( D )。

A.if clk’event and clk = ‘1’ thenB. if falling_edge(clk) thenC. if clk’event and clk = ‘0’ thenD.if clk’stable and not clk = ‘1’ then2.一个项目的输入输出端口是定义在( A )。

A.实体中B.结构体中C.任何位置D.进程体3. 下列语句中,不属于并行语句的是( B )。

A.进程语句B.CASE语句C.元件例化语句D.WHEN…ELSE…语句4.描述项目具有逻辑功能的是( B )。

A.实体B.结构体C.配置D.进程5.关键字ARCHITECTURE定义的是( A)。

A.结构体B.进程C.实体D.配置6.关键字ARCHITECTURE定义的是( A )。

A.结构体B.进程C.实体D.配置7.QUARTESII中编译VHDL源程序时要求( A )。

习题1)VHDL程序有哪些基本部分组成?2)什么进程的敏感信号?进程与赋值语句有何异同?3)什么是并行语句?什么是顺序语句?4)怎样使用库及库内的程序包?列举出三种常用的程序包。

5)BIT类型数据与STD_LOGIC类型数据有什么区别?6)信号与变量使用时有何区别?7)BUFFER与INOUT有何异同?8)为什么实体中定义的整数类型通常要加上一个范围限制?9)怎样将两个字符串hello和world组合为一个字符串?10)IF语句与CASE语句的使用效果有何不同?使用CASE语句时是否需要加语句WHEN OTHERS?为什么?11)进程语句是如何启动的?12)找出下面VHDL程序中的错误,并加以改正。

(a)ENTITY many_errors ISPORT(a:BIT_VECTOR(3 TO 0);b:OUT STD_LOGIC_VECTOR(0 TO 3);c:IN BIT_VECTOR(6 DOWNTO 0);)END many_errors;ARCHITECTURE not_so_good OF many_errors ISBEGINmy_label:PROCESSBEGINIF c = x "F" THENb< = aELSEb< = '0101';END IFEND PROCESS;END not_so_good(b)ENTITY basiccount ISPORT(clk: IN BIT;q: OUT BIT_VECTOR(7 DOWNTO 0));END basiccount;ARCHITECTURE a OF basiccount ISBEGINPROCESS(clk)IF clk'event AND clk='1' THENq<=q+1;END IF;END PROCESS;END a;13)已知逻辑表达式为f = a+bc,试用并行运算语句编写VHDL源程序,并进行时序仿真验证。

填空题(20分,每空格1 分)1、一个完整的VHDL语言程序通常包含实体(entity ) , 构造体(architecture ),酉己置 (configuration ),包集合(package)禾和库(library ) 5 各部分。

2、在一个实体的端口方向说明时,输入使用in表示,那么构造体内部不能再使用的输出是用out 表示;双向端口是用in out 表示;构造体内部可再次使用的输出是用buffer表示;3、一个构造体可以使用几个子结构,即相对比较独立的几个模块来构成。

VHDL语言可以有以下3种形式的子结构描述语句:BLOCK 语句结构;PROCESS语句结构和SUBPROGRAMS结构。

4、VHDL的客体,或称数据对象包括了常数、变量variable 和信号signal 。

5、请列出三个VHDL语言的数据类型,如实数、位等。

位矢量,字符,布尔量。

6、设D0 为'0', D1 为'0', D2为'1', D3为'0', D0 & D1 & D2 & D3 的运算结果是“ 0010”,D3 & D2 & D1 & D0 的运算结果是“ 0100 ”。

7、构造体的描述方式包括三种,分别是寄存器传输(RTL)描述方法或称数据流;构造体的结构描述方式和构造体的行为描述方式。

1、传统的系统硬件设计方法是采用自上而下(top down )的设计方法,利用硬件描述语言(HDL的硬件电路设计方法采用自下而上 (bottom up)的设计方法。

(X )传统的系统硬件设计方法是采用自下而上(bottom up)的设计方法,利用硬件描述语言(HDL 的硬件电路设计方法采用自上而下(top down )的设计方法2、VHDL可以采用层次化的设计,一个高层的结构体中可以调用低层的实体(V )3、一个VHAL程序中仅能使用一个进程(process )语句。