PPC汇编入门指南

- 格式:doc

- 大小:43.50 KB

- 文档页数:9

汇编基础知识

嘿,朋友们!今天咱来聊聊汇编基础知识。

你知道吗,汇编就像是计算机世界里的神秘密码!

咱就说,假如计算机是一个庞大的工厂,那汇编语言就是这个工厂里最精细、最关键的操作指南。

比如说,你想让计算机快速地执行一个特定任务,这时候汇编语言就可以像一把精准的钥匙,打开通往高效运行的大门。

你可能会问,那汇编基础知识到底有啥魔力呢?哇,这可就太重要啦!它让我们能更深入地理解计算机的运作原理,就像你了解了汽车发动机的构造,开起车来就更得心应手一样。

想象一下,别人还在表面摸索,而你已经直达核心,多酷啊!

学习汇编基础知识就像是一场冒险,每一步都充满刺激。

当你搞懂一个指令的作用,就像在迷宫中找到了正确的通道,那种成就感简直爆棚!而且,一旦你掌握了这些基础知识,你就能像个超级英雄一样,随心所欲地指挥计算机为你做事。

来看看这个例子,当你需要让计算机快速处理大量数据时,懂汇编基础知识的你就能精准地编写代码,让计算机像闪电一样飞速运行。

这难道不让人兴奋吗?

朋友,别再犹豫啦!加入学习汇编基础知识的队伍吧,一起探索这个神奇的计算机世界。

你会发现,它比你想象得还要精彩千万倍!相信我,你绝对不会后悔的!

我的观点就是:汇编基础知识是打开计算机神秘之门的关键钥匙,学习它会给你带来无尽的惊喜和收获!。

汇编语言入门指南汇编语言是底层编程语言中最接近真正机器语言的一种语言。

它绝非易懂,但学习它对于理解计算机系统的运作方式和底层编程原理非常重要。

本文将介绍汇编语言的基本概念和入门指南。

一、汇编语言的基本原理汇编语言是基于机器语言的汇编程序进行的开发。

机器语言是计算机硬件直接可以识别的一种语言,通常被写成16进制格式如:A1 2F 3B。

懂机器语言的程序员可以直接对计算机进行编程,但机器语言由于难以理解和排版混乱,让很多人望而却步。

但是汇编语言就是一种将机器语言“翻译”成人类可读的格式的语言。

它使用助记符(mnemonic)代替了机器指令的数字编码,提高了代码的可读性和可维护性。

比如,以下是对应于一个存储器位置8EDAH的机器指令:10101111 10011100而以下是同一指令的汇编语言代码:MOV AL,[8EDAH]也就是说,汇编语言是将人类易读易理解的语言转化为机器语言的语言。

二、汇编语言的语法和基本组成部分1. 语法汇编语言的语法可以说是冷酷无情的。

它的每个指令都必须遵循一定的格式,包括必须的指令名称、指令操作数及其类型、分隔符、注释等元素,否则会编译报错。

以下是一条典型的汇编指令语法格式:指令名称目的操作数,源操作数;注释其中:- 操作数可以是常数、变量或寄存器。

操作数类型可以是字节、字或者双字等不同字节长度。

- 每个语句必须以分号开始,这个分号通常用来分隔指令和注释。

- 注释是可选的,但是它对于解释代码目的或给他人看代码时非常有用。

2. 寄存器汇编语言使用寄存器来存储和操作数据。

寄存器只能存储很小的数据变量,但它们非常快,因为它们存储在CPU内部。

汇编语言中有许多种寄存器,其中32位和64位系统的寄存器不同。

以下是一些常用的寄存器:- eax:32位寄存器,被用来存储函数返回值、与I/O设备通信时使用的数据等等。

- ebx:用来存储一般性的数据、存放指针相关数据。

- ecx:存储循环计数器。

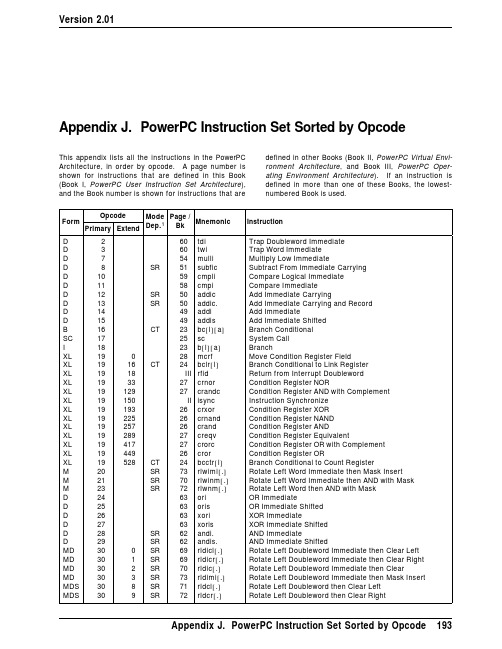

Appendix J.PowerPC Instruction Set Sorted by OpcodeThis appendix lists all the instructions in the PowerPC Architecture,in order by opcode.A page number is shown for instructions that are defined in this Book (Book I,PowerPC User Instruction Set Architecture), and the Book number is shown for instructions that are defined in other Books(Book II,PowerPC Virtual Envi-ronment Architecture,and Book III,PowerPC Oper-ating Environment Architecture).If an instruction is defined in more than one of these Books,the lowest-numbered Book is used.FormOpcode ModeDep.1Page/BkMnemonic Instruction Primary ExtendD260tdi Trap Doubleword ImmediateD360twi Trap Word ImmediateD754mulli Multiply Low ImmediateD8SR51subfic Subtract From Immediate CarryingD1059cmpli Compare Logical ImmediateD1158cmpi Compare ImmediateD12SR50addic Add Immediate CarryingD13SR50addic.Add Immediate Carrying and RecordD1449addi Add ImmediateD1549addis Add Immediate ShiftedB16CT23bc[l][a]Branch ConditionalSC1725sc System CallI1823b[l][a]BranchXL19028mcrf Move Condition Register FieldXL1916CT24bclr[l]Branch Conditional to Link RegisterXL1918III rfid Return from Interrupt DoublewordXL193327crnor Condition Register NORXL1912927crandc Condition Register AND with ComplementXL19150II isync Instruction SynchronizeXL1919326crxor Condition Register XORXL1922526crnand Condition Register NANDXL1925726crand Condition Register ANDXL1928927creqv Condition Register EquivalentXL1941727crorc Condition Register OR with ComplementXL1944926cror Condition Register ORXL19528CT24bcctr[l]Branch Conditional to Count RegisterM20SR73rlwimi[.]Rotate Left Word Immediate then Mask InsertM21SR70rlwinm[.]Rotate Left Word Immediate then AND with MaskM23SR72rlwnm[.]Rotate Left Word then AND with MaskD2463ori OR ImmediateD2563oris OR Immediate ShiftedD2663xori XOR ImmediateD2763xoris XOR Immediate ShiftedD28SR62andi.AND ImmediateD29SR62andis.AND Immediate ShiftedMD300SR69rldicl[.]Rotate Left Doubleword Immediate then Clear LeftMD301SR69rldicr[.]Rotate Left Doubleword Immediate then Clear RightMD302SR70rldic[.]Rotate Left Doubleword Immediate then ClearMD303SR73rldimi[.]Rotate Left Doubleword Immediate then Mask InsertMDS308SR71rldcl[.]Rotate Left Doubleword then Clear LeftMDS309SR72rldcr[.]Rotate Left Doubleword then Clear RightAppendix J.PowerPC Instruction Set Sorted by Opcode193Dep.BkPrimary ExtendX31058cmp CompareX31461tw Trap WordXO318SR51subfc[o][.]Subtract From CarryingXO319SR55mulhdu[.]Multiply High Doubleword UnsignedXO3110SR51addc[o][.]Add CarryingXO3111SR55mulhwu[.]Multiply High Word UnsignedXFX311980mfcr Move From Condition RegisterXFX3119118mfocrf Move From One Condition Register FieldX3120II lwarx Load Word And Reserve IndexedX312137ldx Load Doubleword IndexedX312335lwzx Load Word and Zero IndexedX3124SR74slw[.]Shift Left WordX3126SR67cntlzw[.]Count Leading Zeros WordX3127SR74sld[.]Shift Left DoublewordX3128SR64and[.]ANDX313259cmpl Compare LogicalXO3140SR50subf[o][.]Subtract FromX315337ldux Load Doubleword with Update IndexedX3154II dcbst Data Cache Block StoreX315535lwzux Load Word and Zero with Update IndexedX3158SR67cntlzd[.]Count Leading Zeros DoublewordX3160SR65andc[.]AND with ComplementX316861td Trap DoublewordXO3173SR55mulhd[.]Multiply High DoublewordXO3175SR55mulhw[.]Multiply High WordX3183III mfmsr Move From Machine State RegisterX3184II ldarx Load Doubleword And Reserve IndexedX3186II dcbf Data Cache Block FlushX318732lbzx Load Byte and Zero IndexedXO31104SR53neg[o][.]NegateX3111932lbzux Load Byte and Zero with Update IndexedX31124SR65nor[.]NORXO31136SR52subfe[o][.]Subtract From ExtendedXO31138SR52adde[o][.]Add ExtendedXFX3114480mtcrf Move To Condition Register FieldsXFX31144118mtocrf Move To One Condition Register FieldX31146III mtmsr Move To Machine State RegisterX3114941stdx Store Doubleword IndexedX31150II stwcx.Store Word Conditional IndexedX3115140stwx Store Word IndexedX31178III mtmsrd Move To Machine State Register Doubleword X3118141stdux Store Doubleword with Update IndexedX3118340stwux Store Word with Update IndexedXO31200SR53subfze[o][.]Subtract From Zero ExtendedXO31202SR53addze[o][.]Add to Zero ExtendedX3121032III mtsr Move To Segment RegisterX31214II stdcx.Store Doubleword Conditional IndexedX3121538stbx Store Byte IndexedXO31232SR52subfme[o][.]Subtract From Minus One ExtendedXO31233SR54mulld[o][.]Multiply Low DoublewordXO31234SR52addme[o][.]Add to Minus One ExtendedXO31235SR54mullw[o][.]Multiply Low WordX3124232III mtsrin Move To Segment Register IndirectX31246II dcbtst Data Cache Block Touch for StoreX3124738stbux Store Byte with Update IndexedXO31266SR50add[o][.]AddX31278II dcbt Data Cache Block TouchX3127933lhzx Load Halfword and Zero Indexed194PowerPC User Instruction Set ArchitectureDep.BkPrimary ExtendX31284SR65eqv[.]EquivalentX3130664III tlbie TLB Invalidate EntryX31310II eciwx External Control In Word IndexedX3131133lhzux Load Halfword and Zero with Update IndexedX31316SR64xor[.]XORXFX3133979mfspr Move From Special Purpose RegisterX3134136lwax Load Word Algebraic IndexedX3134334lhax Load Halfword Algebraic IndexedX31370III tlbia TLB Invalidate AllXFX31371II mftb Move From Time BaseX3137336lwaux Load Word Algebraic with Update IndexedX3137534lhaux Load Halfword Algebraic with Update IndexedX31402III slbmte SLB Move To EntryX3140739sthx Store Halfword IndexedX31412SR65orc[.]OR with ComplementXS31413SR76sradi[.]Shift Right Algebraic Doubleword ImmediateX31434III slbie SLB Invalidate EntryX31438II ecowx External Control Out Word IndexedX3143939sthux Store Halfword with Update IndexedX31444SR64or[.]ORXO31457SR57divdu[o][.]Divide Doubleword UnsignedXO31459SR57divwu[o][.]Divide Word UnsignedXFX3146778mtspr Move To Special Purpose RegisterX31476SR64nand[.]NANDXO31489SR56divd[o][.]Divide DoublewordXO31491SR56divw[o][.]Divide WordX31498III slbia SLB Invalidate AllX31512131mcrxr Move to Condition Register from XERX3153346lswx Load String Word IndexedX3153442lwbrx Load Word Byte-Reverse IndexedX3153598lfsx Load Floating-Point Single IndexedX31536SR75srw[.]Shift Right WordX31539SR75srd[.]Shift Right DoublewordX31566III tlbsync TLB SynchronizeX3156798lfsux Load Floating-Point Single with Update IndexedX3159532III mfsr Move From Segment RegisterX3159746lswi Load String Word ImmediateX31598II sync SynchronizeX3159999lfdx Load Floating-Point Double IndexedX3163199lfdux Load Floating-Point Double with Update IndexedX3165932III mfsrin Move From Segment Register IndirectX3166147stswx Store String Word IndexedX3166243stwbrx Store Word Byte-Reverse IndexedX31663101stfsx Store Floating-Point Single IndexedX31695101stfsux Store Floating-Point Single with Update IndexedX3172547stswi Store String Word ImmediateX31727102stfdx Store Floating-Point Double IndexedX31759102stfdux Store Floating-Point Double with Update IndexedX3179042lhbrx Load Halfword Byte-Reverse IndexedX31792SR77sraw[.]Shift Right Algebraic WordX31794SR77srad[.]Shift Right Algebraic DoublewordX31824SR76srawi[.]Shift Right Algebraic Word ImmediateX31851III slbmfev SLB Move From Entry VSIDX31854II eieio Enforce In-order Execution of I/OX31915III slbmfee SLB Move From Entry ESIDX3191843sthbrx Store Halfword Byte-Reverse IndexedX31922SR66extsh[.]Extend Sign HalfwordX31954SR66extsb[.]Extend Sign ByteAppendix J.PowerPC Instruction Set Sorted by Opcode195Dep.BkPrimary ExtendX31982II icbi Instruction Cache Block InvalidateX31983103stfiwx Store Floating-Point as Integer Word IndexedX31986SR66extsw[.]Extend Sign WordX311014II dcbz Data Cache Block set to ZeroD3235lwz Load Word and ZeroD3335lwzu Load Word and Zero with UpdateD3432lbz Load Byte and ZeroD3532lbzu Load Byte and Zero with UpdateD3640stw Store WordD3740stwu Store Word with UpdateD3838stb Store ByteD3938stbu Store Byte with UpdateD4033lhz Load Halfword and ZeroD4133lhzu Load Halfword and Zero with UpdateD4234lha Load Halfword AlgebraicD4334lhau Load Halfword Algebraic with UpdateD4439sth Store HalfwordD4539sthu Store Halfword with UpdateD4644lmw Load Multiple WordD4744stmw Store Multiple WordD4898lfs Load Floating-Point SingleD4998lfsu Load Floating-Point Single with UpdateD5099lfd Load Floating-Point DoubleD5199lfdu Load Floating-Point Double with UpdateD52101stfs Store Floating-Point SingleD53101stfsu Store Floating-Point Single with UpdateD54102stfd Store Floating-Point DoubleD55102stfdu Store Floating-Point Double with UpdateDS58037ld Load DoublewordDS58137ldu Load Doubleword with UpdateDS58236lwa Load Word AlgebraicA5918106fdivs[.]Floating Divide SingleA5920105fsubs[.]Floating Subtract SingleA5921105fadds[.]Floating Add SingleA5922120fsqrts[.]Floating Square Root SingleA5924120fres[.]Floating Reciprocal Estimate SingleA5925106fmuls[.]Floating Multiply SingleA5928107fmsubs[.]Floating Multiply-Subtract SingleA5929107fmadds[.]Floating Multiply-Add SingleA5930108fnmsubs[.]Floating Negative Multiply-Subtract SingleA5931108fnmadds[.]Floating Negative Multiply-Add SingleDS62041std Store DoublewordDS62141stdu Store Doubleword with UpdateX630113fcmpu Floating Compare UnorderedX6312109frsp[.]Floating Round to Single-PrecisionX6314111fctiw[.]Floating Convert To Integer WordX6315111fctiwz[.]Floating Convert To Integer Word with round toward Zero A6318106fdiv[.]Floating DivideA6320105fsub[.]Floating SubtractA6321105fadd[.]Floating AddA6322120fsqrt[.]Floating Square RootA6323121fsel[.]Floating SelectA6325106fmul[.]Floating MultiplyA6326121frsqrte[.]Floating Reciprocal Square Root EstimateA6328107fmsub[.]Floating Multiply-SubtractA6329107fmadd[.]Floating Multiply-AddA6330108fnmsub[.]Floating Negative Multiply-SubtractA6331108fnmadd[.]Floating Negative Multiply-Add196PowerPC User Instruction Set ArchitectureDep.BkPrimary ExtendX6332113fcmpo Floating Compare OrderedX6338116mtfsb1[.]Move To FPSCR Bit1X6340104fneg[.]Floating NegateX6364114mcrfs Move to Condition Register from FPSCRX6370116mtfsb0[.]Move To FPSCR Bit0X6372104fmr[.]Floating Move RegisterX63134115mtfsfi[.]Move To FPSCR Field ImmediateX63136104fnabs[.]Floating Negative Absolute ValueX63264104fabs[.]Floating Absolute ValueX63583114mffs[.]Move From FPSCRXFL63711115mtfsf[.]Move To FPSCR FieldsX63814110fctid[.]Floating Convert To Integer DoublewordX63815110fctidz[.]Floating Convert To Integer Doubleword with round towardZeroX63846112fcfid[.]Floating Convert From Integer Doubleword1See key to mode dependency column,on page203.Appendix J.PowerPC Instruction Set Sorted by Opcode197198PowerPC User Instruction Set ArchitectureAppendix K.PowerPC Instruction Set Sorted by MnemonicThis appendix lists all the instructions in the PowerPC Architecture,in order by mnemonic.A page number is shown for instructions that are defined in this Book (Book I,PowerPC User Instruction Set Architecture), and the Book number is shown for instructions that are defined in other Books(Book II,PowerPC Virtual Environment Architecture,and Book III,PowerPC Operating Environment Architecture).If an instruction is defined in more than one of these Books,the lowest-numbered Book is used.FormOpcode ModeDep.1Page/BkMnemonic Instruction Primary ExtendXO31266SR50add[o][.]AddXO3110SR51addc[o][.]Add CarryingXO31138SR52adde[o][.]Add ExtendedD1449addi Add ImmediateD12SR50addic Add Immediate CarryingD13SR50addic.Add Immediate Carrying and RecordD1549addis Add Immediate ShiftedXO31234SR52addme[o][.]Add to Minus One ExtendedXO31202SR53addze[o][.]Add to Zero ExtendedX3128SR64and[.]ANDX3160SR65andc[.]AND with ComplementD28SR62andi.AND ImmediateD29SR62andis.AND Immediate ShiftedI1823b[l][a]BranchB16CT23bc[l][a]Branch ConditionalXL19528CT24bcctr[l]Branch Conditional to Count RegisterXL1916CT24bclr[l]Branch Conditional to Link RegisterX31058cmp CompareD1158cmpi Compare ImmediateX313259cmpl Compare LogicalD1059cmpli Compare Logical ImmediateX3158SR67cntlzd[.]Count Leading Zeros DoublewordX3126SR67cntlzw[.]Count Leading Zeros WordXL1925726crand Condition Register ANDXL1912927crandc Condition Register AND with ComplementXL1928927creqv Condition Register EquivalentXL1922526crnand Condition Register NANDXL193327crnor Condition Register NORXL1944926cror Condition Register ORXL1941727crorc Condition Register OR with ComplementXL1919326crxor Condition Register XORX3186II dcbf Data Cache Block FlushX3154II dcbst Data Cache Block StoreX31278II dcbt Data Cache Block TouchX31246II dcbtst Data Cache Block Touch for StoreX311014II dcbz Data Cache Block set to ZeroXO31489SR56divd[o][.]Divide DoublewordXO31457SR57divdu[o][.]Divide Doubleword UnsignedXO31491SR56divw[o][.]Divide WordXO31459SR57divwu[o][.]Divide Word UnsignedX31310II eciwx External Control In Word IndexedAppendix K.PowerPC Instruction Set Sorted by Mnemonic199Dep.BkPrimary ExtendX31438II ecowx External Control Out Word IndexedX31854II eieio Enforce In-order Execution of I/OX31284SR65eqv[.]EquivalentX31954SR66extsb[.]Extend Sign ByteX31922SR66extsh[.]Extend Sign HalfwordX31986SR66extsw[.]Extend Sign WordX63264104fabs[.]Floating Absolute ValueA6321105fadd[.]Floating AddA5921105fadds[.]Floating Add SingleX63846112fcfid[.]Floating Convert From Integer DoublewordX6332113fcmpo Floating Compare OrderedX630113fcmpu Floating Compare UnorderedX63814110fctid[.]Floating Convert To Integer DoublewordX63815110fctidz[.]Floating Convert To Integer Doubleword with roundtoward ZeroX6314111fctiw[.]Floating Convert To Integer WordX6315111fctiwz[.]Floating Convert To Integer Word with round toward Zero A6318106fdiv[.]Floating DivideA5918106fdivs[.]Floating Divide SingleA6329107fmadd[.]Floating Multiply-AddA5929107fmadds[.]Floating Multiply-Add SingleX6372104fmr[.]Floating Move RegisterA6328107fmsub[.]Floating Multiply-SubtractA5928107fmsubs[.]Floating Multiply-Subtract SingleA6325106fmul[.]Floating MultiplyA5925106fmuls[.]Floating Multiply SingleX63136104fnabs[.]Floating Negative Absolute ValueX6340104fneg[.]Floating NegateA6331108fnmadd[.]Floating Negative Multiply-AddA5931108fnmadds[.]Floating Negative Multiply-Add SingleA6330108fnmsub[.]Floating Negative Multiply-SubtractA5930108fnmsubs[.]Floating Negative Multiply-Subtract SingleA5924120fres[.]Floating Reciprocal Estimate SingleX6312109frsp[.]Floating Round to Single-PrecisionA6326121frsqrte[.]Floating Reciprocal Square Root EstimateA6323121fsel[.]Floating SelectA6322120fsqrt[.]Floating Square RootA5922120fsqrts[.]Floating Square Root SingleA6320105fsub[.]Floating SubtractA5920105fsubs[.]Floating Subtract SingleX31982II icbi Instruction Cache Block InvalidateXL19150II isync Instruction SynchronizeD3432lbz Load Byte and ZeroD3532lbzu Load Byte and Zero with UpdateX3111932lbzux Load Byte and Zero with Update IndexedX318732lbzx Load Byte and Zero IndexedDS58037ld Load DoublewordX3184II ldarx Load Doubleword And Reserve IndexedDS58137ldu Load Doubleword with UpdateX315337ldux Load Doubleword with Update IndexedX312137ldx Load Doubleword IndexedD5099lfd Load Floating-Point DoubleD5199lfdu Load Floating-Point Double with UpdateX3163199lfdux Load Floating-Point Double with Update IndexedX3159999lfdx Load Floating-Point Double IndexedD4898lfs Load Floating-Point SingleD4998lfsu Load Floating-Point Single with UpdateX3156798lfsux Load Floating-Point Single with Update Indexed200PowerPC User Instruction Set ArchitectureDep.BkPrimary ExtendX3153598lfsx Load Floating-Point Single IndexedD4234lha Load Halfword AlgebraicD4334lhau Load Halfword Algebraic with UpdateX3137534lhaux Load Halfword Algebraic with Update IndexedX3134334lhax Load Halfword Algebraic IndexedX3179042lhbrx Load Halfword Byte-Reverse IndexedD4033lhz Load Halfword and ZeroD4133lhzu Load Halfword and Zero with UpdateX3131133lhzux Load Halfword and Zero with Update IndexedX3127933lhzx Load Halfword and Zero IndexedD4644lmw Load Multiple WordX3159746lswi Load String Word ImmediateX3153346lswx Load String Word IndexedDS58236lwa Load Word AlgebraicX3120II lwarx Load Word And Reserve IndexedX3137336lwaux Load Word Algebraic with Update IndexedX3134136lwax Load Word Algebraic IndexedX3153442lwbrx Load Word Byte-Reverse IndexedD3235lwz Load Word and ZeroD3335lwzu Load Word and Zero with UpdateX315535lwzux Load Word and Zero with Update IndexedX312335lwzx Load Word and Zero IndexedXL19028mcrf Move Condition Register FieldX6364114mcrfs Move to Condition Register from FPSCRX31512131mcrxr Move to Condition Register from XERXFX311980mfcr Move From Condition RegisterXFX3119118mfocrf Move From One Condition Register FieldX63583114mffs[.]Move From FPSCRX3183III mfmsr Move From Machine State RegisterXFX3133979mfspr Move From Special Purpose RegisterX3159532III mfsr Move From Segment RegisterX3165932III mfsrin Move From Segment Register IndirectXFX31371II mftb Move From Time BaseXFX3114480mtcrf Move To Condition Register FieldsXFX31144118mtocrf Move To One Condition Register FieldX6370116mtfsb0[.]Move To FPSCR Bit0X6338116mtfsb1[.]Move To FPSCR Bit1XFL63711115mtfsf[.]Move To FPSCR FieldsX63134115mtfsfi[.]Move To FPSCR Field ImmediateX31146III mtmsr Move To Machine State RegisterX31178III mtmsrd Move To Machine State Register DoublewordXFX3146778mtspr Move To Special Purpose RegisterX3121032III mtsr Move To Segment RegisterX3124232III mtsrin Move To Segment Register IndirectXO3173SR55mulhd[.]Multiply High DoublewordXO319SR55mulhdu[.]Multiply High Doubleword UnsignedXO3175SR55mulhw[.]Multiply High WordXO3111SR55mulhwu[.]Multiply High Word UnsignedXO31233SR54mulld[o][.]Multiply Low DoublewordD754mulli Multiply Low ImmediateXO31235SR54mullw[o][.]Multiply Low WordX31476SR64nand[.]NANDXO31104SR53neg[o][.]NegateX31124SR65nor[.]NORX31444SR64or[.]ORX31412SR65orc[.]OR with ComplementD2463ori OR ImmediateD2563oris OR Immediate ShiftedAppendix K.PowerPC Instruction Set Sorted by Mnemonic201Dep.BkPrimary ExtendXL1918III rfid Return from Interrupt DoublewordMDS308SR71rldcl[.]Rotate Left Doubleword then Clear LeftMDS309SR72rldcr[.]Rotate Left Doubleword then Clear RightMD302SR70rldic[.]Rotate Left Doubleword Immediate then ClearMD300SR69rldicl[.]Rotate Left Doubleword Immediate then Clear Left MD301SR69rldicr[.]Rotate Left Doubleword Immediate then Clear Right MD303SR73rldimi[.]Rotate Left Doubleword Immediate then Mask Insert M20SR73rlwimi[.]Rotate Left Word Immediate then Mask InsertM21SR70rlwinm[.]Rotate Left Word Immediate then AND with MaskM23SR72rlwnm[.]Rotate Left Word then AND with MaskSC1725sc System CallX31498III slbia SLB Invalidate AllX31434III slbie SLB Invalidate EntryX31915III slbmfee SLB Move From Entry ESIDX31851III slbmfev SLB Move From Entry VSIDX31402III slbmte SLB Move To EntryX3127SR74sld[.]Shift Left DoublewordX3124SR74slw[.]Shift Left WordX31794SR77srad[.]Shift Right Algebraic DoublewordXS31413SR76sradi[.]Shift Right Algebraic Doubleword ImmediateX31792SR77sraw[.]Shift Right Algebraic WordX31824SR76srawi[.]Shift Right Algebraic Word ImmediateX31539SR75srd[.]Shift Right DoublewordX31536SR75srw[.]Shift Right WordD3838stb Store ByteD3938stbu Store Byte with UpdateX3124738stbux Store Byte with Update IndexedX3121538stbx Store Byte IndexedDS62041std Store DoublewordX31214II stdcx.Store Doubleword Conditional IndexedDS62141stdu Store Doubleword with UpdateX3118141stdux Store Doubleword with Update IndexedX3114941stdx Store Doubleword IndexedD54102stfd Store Floating-Point DoubleD55102stfdu Store Floating-Point Double with UpdateX31759102stfdux Store Floating-Point Double with Update IndexedX31727102stfdx Store Floating-Point Double IndexedX31983103stfiwx Store Floating-Point as Integer Word IndexedD52101stfs Store Floating-Point SingleD53101stfsu Store Floating-Point Single with UpdateX31695101stfsux Store Floating-Point Single with Update IndexedX31663101stfsx Store Floating-Point Single IndexedD4439sth Store HalfwordX3191843sthbrx Store Halfword Byte-Reverse IndexedD4539sthu Store Halfword with UpdateX3143939sthux Store Halfword with Update IndexedX3140739sthx Store Halfword IndexedD4744stmw Store Multiple WordX3172547stswi Store String Word ImmediateX3166147stswx Store String Word IndexedD3640stw Store WordX3166243stwbrx Store Word Byte-Reverse IndexedX31150II stwcx.Store Word Conditional IndexedD3740stwu Store Word with UpdateX3118340stwux Store Word with Update IndexedX3115140stwx Store Word IndexedXO3140SR50subf[o][.]Subtract FromXO318SR51subfc[o][.]Subtract From Carrying202PowerPC User Instruction Set ArchitectureVersion2.01FormOpcode ModeDep.1Page/BkMnemonic Instruction Primary ExtendXO31136SR52subfe[o][.]Subtract From ExtendedD8SR51subfic Subtract From Immediate Carrying XO31232SR52subfme[o][.]Subtract From Minus One Extended XO31200SR53subfze[o][.]Subtract From Zero ExtendedX31598II sync SynchronizeX316861td Trap DoublewordD260tdi Trap Doubleword ImmediateX31370III tlbia TLB Invalidate AllX3130664III tlbie TLB Invalidate EntryX31566III tlbsync TLB SynchronizeX31461tw Trap WordD360twi Trap Word ImmediateX31316SR64xor[.]XORD2663xori XOR ImmediateD2763xoris XOR Immediate Shifted1Key to Mode Dependency ColumnExcept as described below and in Section 1.12.2,“Effective Address Calculation”on page14,allinstructions are independent of whether the processoris in32-bit or64-bit mode.CT If the instruction tests the Count Register,it tests the low-order32bits in32-bit mode andall64bits in64-bit mode.SR The setting of status registers(such as XER and CR0)is mode-dependent.32The instruction must be executed only in 32-bit mode.64The instruction must be executed only in 64-bit mode.Appendix K.PowerPC Instruction Set Sorted by Mnemonic203Version2.01 204PowerPC User Instruction Set Architecture。

本文主要描述PPC的整数运算和跳转方面的指令,不涉及浮点数和系统指令如MMU、Cache、Exception等。

PPC的由来1991年,IBM、Motorola、Apple联合定义了PowerPC 架构。

PowerPC的主要特点有:采用RISC技术,同时引入少量复杂指令。

这样降低计算机硬件设计复杂性,但对编译器和操作系统的要求更高;应用并行指令(超标量)处理技术. 指令集和CPU硬件协调发展,编译器可以更好地调整指令, 发挥超标量处理的性能;汇编指令集和编程语言结合得更好。

CISC是早先内存受限的条件下发展的, 因为复杂的指令带来代码的减少.但目前内存已经不是关键问题,解码复杂和执行时间长成了指令处理的瓶颈.另外,IBM Berkely Stanford研究表明,如果指令集简单且大部分在一个周期内完成,运算性能会提高。

因此采用RISC技术,可以降低指令复杂度,达到path length和cycle time number of cycles的平衡.相关背景资料:/books/proc/ppc/cwg/intro.html详细介绍了PPC结构下编译器的指令调整技术。

PPC寄存器描述为了方便指令流水线处理,PPC的汇编指令是等宽的,均为4字节,所以指令地址一定是4字节对齐的。

PPC的一个特点是定义了大量的通用寄存器,如用于整数运算和寻址的通用寄存器GPR0-GPR31(General-Purpose Registers)共32个。

在ABI(Application Binary Interface)规范中,GPR1用于堆栈指针、GPR3-GPR4用于函数返回值、GPR3-GPR10用于函数参数传递。

用于浮点数运算的FPR0-FPR31(Floating-Point Registers)共32个,本文不做描述。

状态寄存器CR(Condition Register),用于反映运算结果、跳转判断条件等。

分为如下8组:每组4位,分别为LT(小于)、GT(大于)、EQ(等于)、SO(Summary overflow)。

汇编语言速成指南

《汇编语言速成指南》

嘿,朋友们!今天咱就来聊聊这汇编语言,给大家整一个速成指南。

你们知道吗,我之前啊,就跟汇编语言来了一场“亲密接触”。

那时候我刚开始学,看着那一堆堆的指令和代码,我脑袋都大了!就好像走进了一个满是奇怪符号的迷宫一样。

我记得有一次,我坐在电脑前,对着那些代码苦思冥想,感觉自己就像个在代码海洋里迷失的小船。

我试着去理解那些指令,什么 mov 啊,add 啊,简直让我晕头转向。

我一边挠着头,一边嘴里嘟囔着:“哎呀呀,这可咋办呀!”然后我就一个指令一个指令地去研究,去尝试,就跟解谜题似的。

有时候好不容易弄明白了一点,心里那个高兴啊,就跟找到了宝藏一样。

随着时间慢慢过去,我也逐渐摸到了一些门道。

我发现只要静下心来,一点点去钻研,汇编语言也没那么可怕嘛。

就像那句话说的,世上无难事,只怕有心人。

现在啊,我虽然说不上是汇编语言的大师,但也算是有点小收获啦。

所以啊,大家别害怕,勇敢地去和汇编语言过过招,相信你们也能在这个奇妙的代码世界里找到属于自己的乐趣和成就。

加油吧,朋友们!让我们一起在汇编语言的海洋里畅游,征服那些复杂又有趣的代码!嘿嘿!。

汇编语言入门指南在计算机科学领域中,汇编语言被认为是一门底层的编程语言。

尽管近年来高级编程语言的流行度逐渐上升,但了解汇编语言仍然是一项重要的技能。

本文将探讨汇编语言的基础知识,以及为什么学习汇编语言对于一个程序员来说是至关重要的。

1. 什么是汇编语言?在深入了解汇编语言之前,我们先来了解一下它是什么。

汇编语言是一种能够与计算机硬件直接交互的低级编程语言。

它是由一系列符号和指令组成的,这些指令可以告诉计算机执行特定的操作。

汇编语言相对于高级编程语言而言更接近计算机的底层,直接操作内存和寄存器。

因此,了解汇编语言对于理解计算机的工作原理非常重要。

2. 为什么要学习汇编语言?尽管高级编程语言用起来更加方便快捷,但学习汇编语言仍有许多好处。

首先,学习汇编语言可以帮助程序员更好地理解计算机的底层运行方式。

当我们使用高级编程语言编写代码时,我们往往不知道代码被编译成机器代码之后实际发生了什么。

而通过学习汇编语言,我们能够更加清楚地了解代码是如何被翻译成机器代码并在计算机上执行的。

其次,学习汇编语言可以提高对其他编程语言的理解能力。

尽管现代高级编程语言提供了许多高级的抽象概念和数据结构,但它们最终会被转化为汇编语言程序。

通过理解汇编语言,我们可以更好地理解高级编程语言在底层是如何运作的,这将使我们在编写代码时能够更加高效和优化。

最后,学习汇编语言可以使程序员具备更强大的调试能力。

当我们遇到复杂的Bug或性能问题时,理解汇编语言将使我们能够更深入地分析问题所在。

我们可以通过阅读和理解汇编代码来定位问题,并优化相关的程序部分。

3. 汇编语言的基础知识现在让我们来了解一些汇编语言的基础知识。

首先是汇编器,它是一种将汇编语言翻译成机器语言的工具。

汇编器将我们编写的汇编代码翻译成计算机硬件能够理解执行的指令。

每个处理器架构都有自己的汇编语言,因此我们需要根据特定的处理器来选择相应的汇编语言。

其次是汇编语言的语法。

汇编语言的语法通常包括指令操作码(Opcode)、标号(Label)、寄存器(Register)和操作数(Operand)等。

看懂PowerPC汇编,需要如下3方面的知识:1.PowerPC指令集架构即Power ISA,可以从获得,包括寄存器定义,数据模型,寻址方式和指令定义以及指令助记符;2.PowerPC ABI即应用程序二进制接口,即寄存器的使用规范和栈调用结构;3.PowerPC Pseudo-ops,即.text, .align n等汇编语言中常用的伪操作符。

PowerPC ISA分为3个级别即“Book”,分别对应于用户指令集体系结构,虚拟环境体系结构和操作环境体系结构。

其中Book III分化出了服务器版本Book III-S(经典PowerPC架构)和嵌入式版本Book III-E(专门为嵌入式优化的版本)。

1.寄存器定义:PowerPC处理器寄存器分为2大类-专用寄存器和非专用寄存器。

其中,非专用寄存器包括32个通用目的寄存器(GPR),32个浮点寄存器(FPR),条件寄存器(CR),浮点状态和控制寄存器(FPSCR);专用寄存器主要包括连接寄存器(LR),计数寄存器(CTR),机器状态寄存器(MSR)以及时间基准寄存器(TBL/TBU)等等。

PPC4xx系列处理器还有DCR寄存器,需要用专门的指令访问。

这里有两点需要注意:1. PowerPC处理器可以运行于两个级别,即用户模式和特权模式。

用户模式下,仅有GPR,FPR,CR,FPSC R,LR,CTR,XER以及TBL/TBU可以访问。

从Power ISA2.05开始,DCR寄存器也可以在通过用户模式DC R访问指令进行访问。

2.PowerPC处理器没有专用的栈指针寄存器和PC指针寄存器,也就是说硬件不负责维护调用栈。

2.数据模型:PowerPC支持如下数据格式:byte, halfword, word, doubleword,quadword, 同时默认支持big-endian 字节序,即MSB(最高有效字节,例如0x12345678中0x12即MSB)保存在低地址。

little-endian字节序可以通过修改设置支持。

注意:PowerPC习惯, msb(最高有效位)为bit0,lsb为bit31.3.寻址方式PowerPC没有专门的IO操作指令,所有地址访问一视同仁,并且只支持地址和寄存器之间的访问。

因此寻址方式非常简单,可以概括为2类6种:3.1 Load/store/算术/逻辑/cache指令:a)寄存器间接寻址模式,通常写作RA或者RB;b)寄存器间接立即数索引寻址模式,即(基址寄存器+立即数偏移)寻址模式,通常写作d(RA);c)寄存器间接索引寻址模式(基址寄存器 + 偏移寄存器)寻址模式,通常写作RA,RB。

注意:对于三种模式,若寄存器为GPR0,则其内容被忽略,并以0代替其内容。

3.2 跳转指令:a)立即数寻址模式;b)链接寄存器(LR)模式,即目的地址被保存在LR中;c)计数寄存器(CTR)模式,即目的地址保存在CTR中。

注意:实际上还有一些特殊的跳转指令rfi/rfci/rfmci,其目的地址保存在SRR0/CSRR0/MCSRR0中。

4.指令定义和指令助记符:PowerPC指令的长度都是4字节,但是种类繁多,而且有些指令极其复杂。

因此,通常情况下,PowerPC汇编编程中采用指令和助记符混用的方式。

助记符主要用来简化内存访问、算术运算、逻辑运算等常用指令,例如用b ne target代替bc 4,2,target表示不为零则跳转。

下面仅以一些常见的汇编代码片段来做一些简单的归纳,具体信息请参考相应的处理器core用户手册或者Power ISA。

注意,cache和MMU指令会跟其实现一起介绍,此处不再赘述。

4.1 读取一个word(0x12345678)到目的寄存器lis RA,0x12345678@h /* 高16位(0x1234)偏移16位后变成0x12340000放进RA */ori RB, RA, 0x12345678@l /* RA与低16位(0x5678)相或后构成完整数据放进RA */注意:PowerPC指令中,i后缀表示立即数,s后缀表示左移16位。

例如addi、addis、ori、oris等。

这段代码也可以用来读取某个变量的值,只需要把立即数替换成变量名。

2.从某个地址(0x56789abc)读取数据lis RA,0x56789abc@ha /* 调整后的高16位(0x5679)偏移16位后变成(0x56790000)放进RA */ lwz RB, 0x56789abc@l (RA) /* RA加上低16位(0xffff9abc)构成完整数据地址,然后将其内容放进RB */注意:∙@l,@h和@ha:用于算术运算的操作数(包括addi的操作数)时,@l获取的是符号扩展的低16位数据(0xffff9abc) ,因此高16位必须进行根据bit15进行调整,而不能简单的使用@h来获取。

∙load/store指令的通常格式为(l/st)(w/h/b)(z/br)(u/x) RA,… . 其中l代表读取数据到RA 中;st代表将RA的内容写入内存;w/h/b分别代表针对word、halfword/byte进行操作;z仅用于读取数据,代表字或者半字读到寄存器中后将其高位清零(注意:对word的读取无意义,但必须加);br代表读取后或者存入前对数据进行字节序反转;u代表从某个内存地址读取数据后,同时更新保存内存地址的寄存器;x代表使用寄存器间接索引寻址模式(基址寄存器 + 偏移寄存器)寻址模式(默认使用寄存器间接立即数索引寻址模式)∙这段代码也可以用来访问数组或者结构中的某个成员,或者指针指向的地址块中的数据,只需把立即数换成相应的数组名、结构名或者指针即可。

3.入栈/出栈操作入栈:stwu 1, –16(1) /* 原始栈指针GPR1保存在新栈顶(原始栈指针减去16)*/mflr 0 /* LR暂存在GPR1 */stw 0, 20(1) /* 保存LR到调用者的栈中 */出栈:lwz 0, 20(1) /* LR出栈 */mtlr 0 /* 恢复LR */addi r1, r1, 16 /* 销毁栈 */注意:栈定义会在ABI部分详细解释,此处不再赘述。

4.循环li 0, 10 /* 循环次数暂存入GPR0 */mtctr 0 /* 更新计数寄存器 CTR*/label:… /* 需要重复执行的指令 */bdnz label /* 递减计数器,不等于0则跳转到标号处重复执行 */注意:∙label类似于C语言中的标号,因此在同一段代码中,不能重复。

因此,习惯中使用数字标号来代替。

数字标号作为跳转指令的目的地址时,通常在其后一个b表示向最近的低地址数字标号跳转,加f 表示向最近的高地址数字标号跳转。

例如beq 1f或者blt 2b。

注意,标号,不管是数字形式还是字母形式,都可以用作一个代表标号所对应行的地址的变量使用。

例如,可以用lis RA, 1f@ha; lwz RB, 1f@l(RA)可以用来获取标号1f处的指令内容。

∙跳转指令分为条件跳转和无条件跳转两种:无条件跳转主要有b(跳转到相对地址)\ba(跳转到绝对地址)\blr(跳转到连接寄存器)\bctr(跳转到计数寄存器)4种;(注意,rfi、rfci、rfmci等异常返回指令也可以看做是特殊的无条件跳转。

)条件跳转指令分为两种:需要配合比较指令/算术指令/逻辑运算指令使用的beq(相等或者为0则跳转)/bne(不等或者非0则跳转)/blt(小于则跳转)/bgt(大于则跳转)/ble(小于等于则跳转)/ bge(大于等于则跳转)/bnl(不小于则跳转)/bng(不小于则跳转)等和需要配合计数寄存器CTR 使用的bdz(CTR递减到0则跳转)/bdnz(CTR没有递减到0则跳转)等。

此外条件跳转指令还可以增加后缀a表示跳转到绝对地址;所有跳转指令增加后缀l表示同时更新连接寄存器(LR),用于子程序调用。

∙配合条件跳转指令使用的比较指令主要是cmp(l)w(i),其中l表示逻辑比较既无符号数比较,w表示比较2个word,i表示寄存器内容跟立即数进行比较;∙配合条件跳转指令使用的算术指令必须加上后缀“.”用以表示更新条件寄存器CR,主要有add(寄存器内容相加)/addi(寄存器内容跟立即数相加)/addis(立即数左移16位后跟寄存器内容相加)和subi(寄存器内容减去立即数)/subis(寄存器内容减去左移16位后的立即数)/subf(从RB(第三个参数)中减去RA(第二个参数)的内容放入RT(第一个参数));∙配合条件跳转指令使用的逻辑指令也必须加上后缀“.”用以表示更新条件寄存器CR,主要包括and(i) (s)/or(i)(s)。

∙CTR等专用寄存器必须通过专用命令mfspr rD,SPR和mtspr SPR,rS或者mfctr/mtctr/mflr/ mtlr/mfspr/mtspr/mftbl/mftbu/mttbl/mttbu鞥助记符进行操作。

此外,DCR寄存器必须通过m fdcr/mtdcr/mfdcrx/mtdcrx/mfdcrux/mtdcrux等进行操作。

注意,后面4条DCR指令仅在Pow er ISA 2.05及更高版本支持。

5.强大的位操作指令PowerPC有3条强大的位操作指令,几乎能实现你能想象的所有位操作。

a)rlwinm(.) rA,rS,SH,MB,ME寄存器RS的内容循环左移立即数SH位,然后跟立即数MB和ME形成的MA SK相与后放进RAb)rlwnm(.) rA,rS,RB,MB,ME类似于上一条指令,只是把左移的位数放到了寄存器RB中c)rlwimi(.) rA,rS,SH,MB,ME寄存器RS的内容循环左移立即数SH位,然后跟立即数MB和ME形成的MAS K相与,再把RA的内容跟立即数MB和ME形成的MASK的补码相与,即清掉RA中MASK对应的位,最后把处理后的RS和RA的内容相或,放入RA中注意:MASK形成的规则是,如果MB小于等于ME,则MB到ME之间的位全部置1,包括这两位,形成MASK;否则,MB到ME之间的位清0,其他位包括这两位置1,形成MASK。

下面给出几个例子:a)从立即数0x12345678(RS)中抽取bit 20-23,并左移16位,从而得到0x06000000. rlwinm rA, rS, 16, 4, 7具体过程如下:0x12345678循环左移16位得到0x56781234,然后与MASK0x0f00 0000 (MASK[4,7])相与。

* 该指令可以用来抽取C语言代码或者寄存器中的位域。

b)清除立即数0x12345678(RS)的bit 28 - 31,并右移24位,从而得到0x0012 3456rlwinm rA, rS, 24, 8, 31具体过程如下:0x12345678循环左移24位得到0x78123456,然后与MASK0x00ff ffff (MASK[8,31])相与。