nandflash用法

- 格式:doc

- 大小:1.58 MB

- 文档页数:20

NANDFlash原理和使用一、NAND Flash的原理NAND Flash基于浮栅效应晶体管(Floating Gate Field Effect Transistor)的工作原理进行存储数据。

每个存储单元包含一个浮动栅和一个控制栅,通过对控制栅施加电压,可以改变浮动栅中电子的分布状态。

当浮动栅的电荷状态表示0时,电子充分存储在浮动栅中;而当浮动栅的电荷状态表示1时,几乎没有电子存储在浮动栅中。

数据的写入和擦除是NAND Flash的两个重要操作。

写入数据时,首先需要根据所需的数据位序列确定相应的单元位置,然后通过施加一定的电压对浮动栅进行充、放电,以改变电子的位状态。

擦除数据时,需要对整个块进行一次性的擦除操作,将所有存储单元的电子位状态恢复为0。

同时,为了提高存储密度和读写性能,NAND Flash还使用了一些技术,如多层单元(Multi-Level Cell,MLC)和三层单元(Triple-Level Cell,TLC)来实现在每个存储单元中存储多位数据。

二、NAND Flash的使用1. 存储器层面:NAND Flash因其非易失性和快速读写性能被广泛应用于存储器中,取代了传统的硬盘驱动器。

固态硬盘(SSD)是其中的典型应用,它不仅在电脑中使用,也可以用于服务器、云存储等领域。

2. 智能手机和平板电脑:NAND Flash被广泛应用于智能手机和平板电脑中的存储器,用于存储操作系统、应用程序和用户数据。

由于NAND Flash具有快速的读写速度和较小的体积,可实现轻薄设计,因此非常适合移动设备。

3. 数字相机和摄像机:NAND Flash也用作数码相机和摄像机中的存储媒介,用于保存拍摄的照片和视频。

相比于传统的存储卡,NAND Flash 存储器具有更高的读写速度和更大的容量,可以满足高清拍摄的需求。

4. 汽车电子:随着汽车电子的普及,NAND Flash也开始在汽车的娱乐系统、导航系统和车载电子控制单元中得到应用。

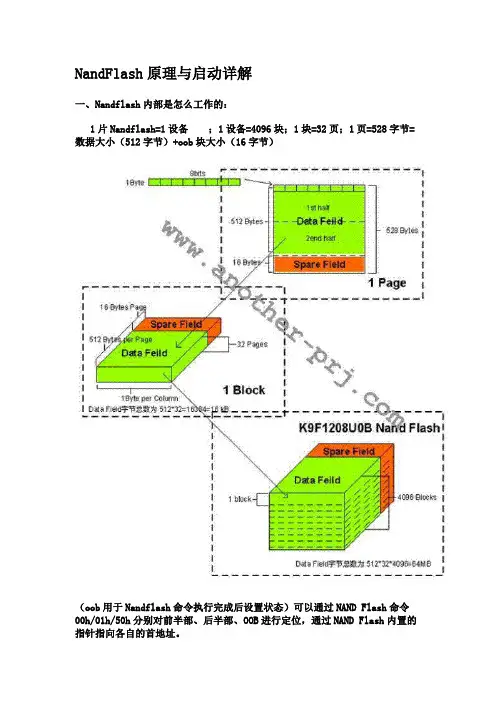

NandFlash原理与启动详解一、Nandflash内部是怎么工作的:1片Nandflash=1设备;1设备=4096块;1块=32页;1页=528字节=数据大小(512字节)+oob块大小(16字节)(oob用于Nandflash命令执行完成后设置状态)可以通过NAND Flash命令00h/01h/50h分别对前半部、后半部、OOB进行定位,通过NAND Flash内置的指针指向各自的首地址。

存储操作特点有:擦除操作的最小单位是块;NAND Flash芯片每一位只能从1变为0,而不能从0变为1,所以在对其进行写入操作之前一定要将相应块擦除(擦除即是将相应块的位全部变为1);OOB部分的第6字节(即517字节)标志是否是坏块,值为FF时不是坏块,否则为坏块。

除OOB第6字节外,通常至少把OOB的前3字节用来存放NAND Flash硬件ECC码。

(ECC:"Error Correcting Code" "错误检查纠正",带有奇偶校验的内存的主要功能。

)1.Nand flash以page为单位进行读写,以block为单位进行擦除,没页分为main区和spare区,main区用于存放正常的数据,spare区用于存放一些附加信息2.S3c2440 支持从Nand 启动是因为内部有一个叫做Steppingstone的SRAM buffer,当启动的时候,nand 的前4k的将会代码将被拷贝到steppingstone中执行,注意前4k代码是不会经过ECC校验的,所以必须确保这些代码的准确3.对nand的操作都是通过使用命令来实现,有的操作只要一个命令就可以完成,而有的需要两个命令才能完成,下面是K9F1G08U0B的命令表:4 Flash烧写程序原理及结构基本原理:将在SDRAM中的一段存储区域中的数据写到NAND Flash存储空间中。

烧写程序在纵向上分三层完成。

nandflash read reclaim机制

NAND Flash是一种非易失性存储器技术,用于存储和读取数据。

NAND Flash读取数据时,会使用一种称为“reclaim机制”

的方法来处理失效或坏块。

当一个块在NAND Flash上失效或变成坏块后,系统会将其中

的数据移动到其他可用的块中。

这个过程称为“reclaim机制”。

reclaim机制的步骤包括:

1. 标记坏块:当一个块失效后,系统会将其标记为坏块,以防止将来使用。

2. 复制数据:为了保存原始数据,系统会将坏块中的数据复制到其他可用的块中。

3. 更新元数据:系统会更新NAND Flash上的元数据信息,以

确保之后的读取操作能够正确地找到和访问数据。

使用reclaim机制的好处是,即使NAND Flash上出现坏块或

失效的情况,系统仍然能够保持数据的完整性和可访问性。

这有助于提高存储系统的可靠性和数据一致性。

S3C2440的启动时读取的第一条指令是在0x00上,分为成nand flash和nor flash上启动。

Nor flash的有自己的地址线和数据线,可以采用类似于memory的随机访问方式,在nor flash上可以直接运行程序,所以nor flash可以直接用来做boot,采用nor flash启动的时候会把地址映射到0x00上。

mini2440就是直接把vivi直接烧录在nor flash上。

Nand flash是IO设备,数据、地址、控制线都是共用的,需要软件区控制读取时序,所以不能像nor flash、内存一样随机访问,不能EIP(片上运行),因此不能直接作为boot。

S3C2440把Bootloader烧到nand flash上启动,因为在S3C2440里有一个内置的SRAM,叫做stepping stone(垫脚石,很形象…),系统启动加电后,会把nand flash上的起始4KB 的内容拷贝到SRAM里执行,这样就实现了从nand flash启动。

如果bootloader小于4KB 的话(像vboot),在SRAM里就能boot,大于4KB的话(u-boot,vivi),在SRAM里做一些基本初始化后,再把bootloader的剩余部分拷贝到SDRAM里(>0x30000000)。

我们使用S3C2440的时候,经常通过nor flash启动,进入vivi的菜单(S3C2440的Nor flash 已经烧录好了vivi),之后通过vivi的usb下载功能,把其他的bootloader下载到nand flash 里,下载完成后,再通过nand flash启动,测试我们的bootloader。

NOR flash适合做代码存储并EIP的,NAND适合用来作大量数据存储的。

NANDFlash启动: NANDFlash存储器的前4K将被自动加载到Steppingstone(内部SRAM缓冲器),然后系统自动执行这些载入的启动代码,这4K的启动代码需要将NANDFlash中的内容复制到SDRAM中执行。

nand flash 读写流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!NAND Flash 读写流程。

1. 擦除块(Erase Block)。

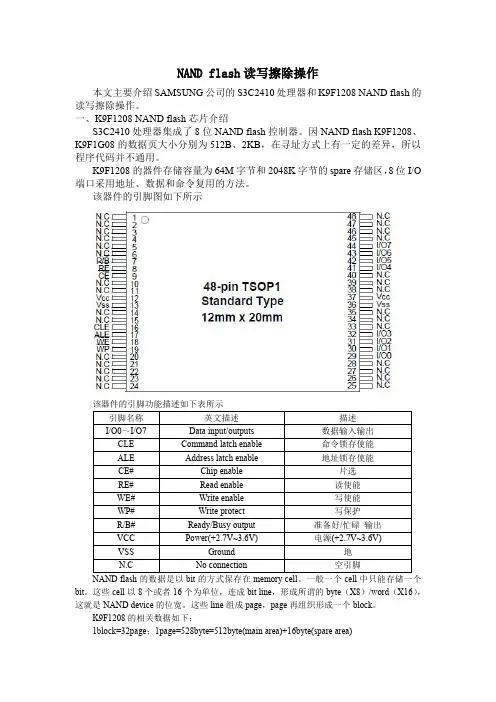

NAND flash读写擦除操作本文主要介绍SAMSUNG公司的S3C2410处理器和K9F1208NAND flash的读写擦除操作。

一、K9F1208NAND flash芯片介绍S3C2410处理器集成了8位NAND flash控制器。

因NAND flash K9F1208、K9F1G08的数据页大小分别为512B、2KB,在寻址方式上有一定的差异,所以程序代码并不通用。

K9F1208的器件存储容量为64M字节和2048K字节的spare存储区,8位I/O 端口采用地址、数据和命令复用的方法。

该器件的引脚图如下所示该器件的引脚功能描述如下表所示引脚名称英文描述描述I/O0~I/O7Data input/outputs数据输入输出CLE Command latch enable命令锁存使能ALE Address latch enable地址锁存使能CE#Chip enable片选RE#Read enable读使能WE#Write enable写使能WP#Write protect写保护R/B#Ready/Busy output准备好/忙碌输出VCC Power(+2.7V~3.6V)电源(+2.7V~3.6V)VSS Ground地N.C No connection空引脚NAND flash的数据是以bit的方式保存在memory cell。

一般一个cell中只能存储一个bit。

这些cell以8个或者16个为单位,连成bit line,形成所谓的byte(X8)/word(X16),这就是NAND device的位宽。

这些line组成page,page再组织形成一个block。

K9F1208的相关数据如下:1block=32page;1page=528byte=512byte(main area)+16byte(spare area)总容量为=4096(block)*32(page/block)*512(byte/page)=64MBNAND flash以页为单位读写数据,而以块为单位擦除数据。

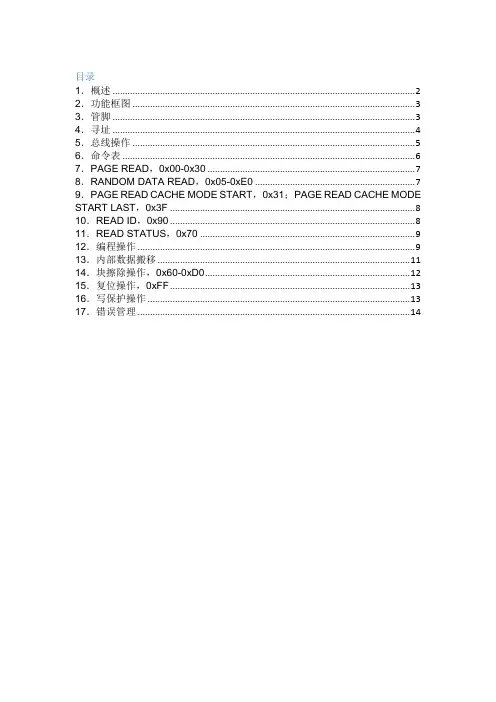

目录1.概述 (2)2.功能框图 (3)3.管脚 (3)4.寻址 (4)5.总线操作 (5)6.命令表 (6)7.PAGE READ,0x00-0x30 (7)8.RANDOM DATA READ,0x05-0xE0 (7)9.PAGE READ CACHE MODE START,0x31;PAGE READ CACHE MODE START LAST,0x3F (8)10.READ ID,0x90 (8)11.READ STATUS,0x70 (9)12.编程操作 (9)13.内部数据搬移 (11)14.块擦除操作,0x60-0xD0 (12)15.复位操作,0xFF (13)16.写保护操作 (13)17.错误管理 (14)以Micron公司的MT29F2G08为例介绍NAND Flash原理和使用。

1.概述MT29F2G08使用一个高度复用的8-bit总线(I/O[7:0])来传输数据、地址、指令。

5个命令脚(CLE、ALE、CE#、WE#)实现NAND命令总线接口规程。

3个附加的脚用作: 控制硬件写保护(WP#)、监视芯片状态(R/B#),和发起上电自动读特征(PRE-仅3V芯片支持)。

注意, PRE功能不支持宽温芯片。

MT29F2G08内部有2048个可擦除的块,每个块分为64个可编程的页,每个页包含2112字节(2048个字节作为数据存储区,64个备用字节一般作为错误管理使用)。

每个2112个字节的页可以在300us内编程,每个块(64x2112=132K)可以在2ms内被擦除。

片上控制逻辑自动进行PROGRAM和ERASE操作。

NAND的内部存储阵列是以页为基本单位进行存取的。

读的时候,一页数据从内部存储阵列copy到数据寄存器,之后从数据寄存器按字节依次输出。

写(编程)的时候,也是以页为基本单位的:起始地址装载到内部地址寄存器之后,数据被依次写入到内部数据寄存器,在页数据写入之后,阵列编程过程启动。

Mini2440 nand flash 操作总结首先要感谢CSDN论坛的赵春江老师的文章。

这篇文章基本上是他文章的内容。

百度上搜“CSDN 赵春江”就能找到。

一:硬件连接Nand flash操作对于自己编写mini2440启动代非常关键。

因为一般来说,嵌入式系统都有一片nand flash用来作为存储器。

所以掌握nand flash 的操作非常的必要和关键。

在操作之前,首先应该对nand flash 的硬件上有一定的了解。

我的mini2440板子自带的是K9F1G08U0A。

大小是128M。

其芯片上的重要引脚如下:I/O0~I/O7:数据总线,用于nandflash的所有命令,地址的输入,和数据的双向传输.CE:芯片使能引脚CLE (Command Latch Enable):命令锁存允许引脚ALE(Address Latch Enable):地址锁存允许引脚WE/:写芯片允许引脚RE/:读芯片允许引脚RB:状态读取引脚(低电平表示忙;高电平表示空闲)其他引脚:诸如电源之类因为S3C2440硬件自带有nand flash控制器,所以具有相对应的引脚可以和nand flash 芯片连接。

系统总线引脚DA TA0~DA TA7:直接与I/O0~I/O7相连接nFCE/GPA22 :直接与CE引脚相连CLE/GPA17:直接与CLE引脚相连ALE/GPA18 :直接与ALE引脚相连nFWE/GPA19:直接与WE/引脚相连nFRE/GPA20 :直接与WE/引脚相连FRnB:直接与RB引脚相连除此之外,S3C2440还有另外几个引脚用于配置nandflash控制器。

比如页大小,地址周期数等等。

这些引脚主要有如下:OM[1:0] ; NCON ; GPG13 ; GPG14 ; GPG15。

他们的配置方式在S3C2440说明书上已经很详细。

所以综上所述,S3C2440 与nandflash(K9F1G08U0A)的硬件连接图如下所示:二:nand flsah 工作原理简介Nand flash 主要是用于大容量的存储。

NandFlash启动过程详解NAND Flash是一种流行的非易失性存储技术,它可以用于嵌入式系统的启动过程中。

以下是NAND Flash启动过程的详细解释。

1. 电源投入:启动过程始于将电源连接到系统上。

一旦电源被投入,NAND Flash芯片便开始工作。

芯片内部会进行一系列初始化操作,以确保其正常运行。

2. 主控器初始化:NAND Flash芯片的主控器是其核心部分,它控制着所有数据的读取和写入操作。

在启动过程中,主控器需要进行初始化,以确保它可以正确地与系统中的其他组件进行通信。

3. 片选操作:由于可能存在多个NAND Flash芯片连接到同一个总线上,因此需要使用片选操作来选择要进行读取和写入操作的特定芯片。

在启动过程中,首先需要选择正确的芯片。

4. 地址传输:NAND Flash芯片存储数据的方式是按块存储,而不是按字节存储。

因此,在进行读取和写入操作之前,需要先传输正确的地址以指示要操作的块和页。

5. 读取操作:在启动过程中,通常需要从NAND Flash芯片中读取引导程序代码。

读取操作涉及到将芯片中的数据按照正确的地址传输到系统的内存中。

6. 缓冲区操作:由于NAND Flash芯片的读取速度相较于内存较慢,因此在读取操作中通常会使用缓冲区来提高读取速度。

在读取操作期间,数据会首先存储在缓冲区中,然后再传输至系统的内存中。

7. 写入操作:除了读取操作外,启动过程中还可能需要将数据写入到NAND Flash芯片中。

写入操作涉及将数据从系统的内存中传输到合适的块和页。

8. 擦除操作:NAND Flash芯片的数据存储是按块而不是按页进行的。

因此,在进行写入操作之前,可能需要先擦除芯片中的一些块。

擦除操作会将一些块中的所有数据都清除,以便进行写入操作。

9. 引导加载:启动过程的最后阶段是引导加载,它涉及将引导程序代码从NAND Flash芯片中加载至系统的内存中。

一旦引导程序代码被加载,系统便可以开始执行并启动其他组件。

nand flash架构读取操作原理

NAND Flash是一种非易失性存储器,其读取操作原理如下:

1. 数据存储:NAND Flash将数据存储在一组互相连接的存储单元(或称为“存储块”),每个存储单元存储一个或多个数据位。

2. 读取操作:当进行读取操作时,控制器发送一个读取命令给NAND Flash芯片。

读取命令包括存储单元的地址,用于指示需要读取的数据位在哪个存储单元中。

3. 地址解码:NAND Flash芯片通过解码器将接收到的地址信号解码为特定的存储单元。

4. 数据传输:一旦解码,NAND Flash芯片会将请求的数据位传输给控制器。

数据传输是通过读取线路进行的,其中包括数据线和引脚,以便将数据传输到控制器。

5. 数据返回:NAND Flash芯片将请求的数据位返回给控制器后,控制器可以根据需要将数据传输到主机系统的内存中。

需要注意的是,NAND Flash芯片的读取操作是以块为单位进行的,而不是以字节或位为单位。

这是因为每个存储单元中的数据位是同时读取的。

因此,如果需要读取少于一个存储块的数据,控制器仍会读取整个存储块,并从中提取所需数据,这会导致一定的浪费。

NAND Flash 读写操作(三)2009-03-26 13:02Fisrt part :NAND flash和NOR flash的不同NOR flash采用位读写,因为它具有sram的接口,有足够的引脚来寻址,可以很容易的存取其内部的每一个字节。

NAND flash使用复杂的I/O口来穿行地存取数据。

8个引脚用来传送控制、地址和数据信息。

NAND的读和写单位为512Byte 的页,擦写单位为32页的块。

● NOR的读速度比NAND稍快一些。

● NAND的写入速度比NOR快很多。

● NAND的4ms擦除速度远比NOR的5s快。

● 大多数写入操作需要先进行擦除操作。

● NAND的擦除单元更小,相应的擦除电路更少。

在NOR器件上运行代码不需要任何的软件支持,在NAND器件上进行同样操作时,通常需要驱动程序,也就是内存技术驱动程序(MTD),NAND和NOR器件在进行写入和擦除操作时都需要MTD。

---------摘抄自网上流传很广的《NAND 和 NOR flash的区别》Second part:NAND Flash结构与驱动分析一、NAND flash的物理组成NAND Flash 的数据是以bit的方式保存在memory cell,一般来说,一个cell 中只能存储一个bit。

这些cell 以8个或者16个为单位,连成bit line,形成所谓的byte(x8)/word(x16),这就是NAND Device的位宽。

这些Line会再组成Page,(NAND Flash 有多种结构,我使用的NAND Flash 是K9F1208,下面内容针对三星的K9F1208U0M),每页528Bytes(512byte(MainArea)+16byte(Spare Area)),每32个page形成一个Block(32*528B)。

具体一片flash上有多少个Block视需要所定。

我所使用的三星k9f1208U0M具有4096个block,故总容量为4096*(32*528B)=66MB,但是其中的2MB是用来保存ECC校验码等额外数据的,故实际中可使用的为64MB。

这篇文章不是介绍nand flash的物理结构和关于nand flash的一些基本知识的。

你需要至少了解你手上的nand flash的物理结构和一些诸如读写命令操作的大概印象,你至少也需要看过s3c2440中关于nand flash控制寄存器的说明。

由于本人也没有专门学过这方面的知识,下面的介绍也是经验之谈。

这里我用的K9F2G08-SCB0 这款nand flash 来介绍时序图的阅读。

不同的芯片操作时序可能不同,读的命令也会有一些差别。

当然其实有时候像nand flash这种s3c2440内部集成了他的控制器的外设。

具体到读写操作的细节时序(比如CLE/ALE的建立时间,写脉冲的宽度。

数据的建立和保持时间等),不明白前期也没有多大的问题。

因为s3c2440内部的nand flash控制器做了大部分的工作,你需要做的基本就是设置几个时间参数而已。

然后nand flash会自动进行这些细节操作。

当然如果处理器上没有集成nand flash的控制器那么久必须要自己来写时序操作了。

所以了解最底层的时序操作总是好的但是上层一点的,比如读写操作的步骤时序(比如读操作,你要片选使能,然后发命令,然后发地址,需要的话还需发一个命令,然后需要等待操作完成,然后再读书数据)。

是必须要明白的。

这都不明白的话,怎么进行器件的操作呢也就是说s3c2440 可以说在你设置很少的几个时间参数后,将每一个步骤中细微的操作都替你做好了。

(比如写命令,你只要写个命令到相应寄存器中,cpu内部就会协各个引脚发出适应的信号来实现写命令的操作)。

而我们所需要做的就是把这些写命令,写地址,等待操作完成。

等步骤组合起来。

从而完成一个读操作就像上面说的,虽然我们不会需要去编写每个步骤中的最细微的时序。

但是了解下。

会让你对每个操作步骤的底层细节更加明了先来看一个命令锁存的时序。

也就是上面说的读nand flash操作中不是有一个写命令步骤吗。

NandFlash存储结构及控制方法Nand Flash存储结构及控制方法(K9F1G08)2011-02-26 15:05:59| 分类:默认分类 | 标签:mini2440nandflash k9f1g08 |字号订阅一、NAND Flash介绍和NAND Flash控制器的使用NAND Flash在嵌入式系统中的作用,相当于PC上的硬盘常见的Flash有NOR Flash和NAND Flash,NOR Flash上进行读取的效率非常高,但是擦除和写操作的效率很低,容量一般比较小;NAND Flash进行擦除和写操作的效率更高,并且容量更大。

一般NOR Flash用于存储程序,NAND Flash 用于存储数据。

1)NAND Flash的物理结构笔者用的开发板上NAND Flash型号是K9F1G08,大小为128M,下图为它的封装和外部引脚I/O0-I/O7 数据输入/输出CLE 命令锁存使能ALE 地址锁存使能CE 芯片使能RE 读使能WE 写使能WP 写保护R/B 就绪/忙输出信号Vcc 电源Vss 地N.C 不接K9F1G08功能结构图如下K9F1G08内部结构有下面一些功能部件①X-Buffers Latches & Decoders:用于行地址②Y-Buffers Latches & Decoders:用于列地址③Command Register:用于命令字④Control Logic & High Voltage Generator:控制逻辑及产生Flash所需高压⑤Nand Flash Array:存储部件⑥Data Register & S/A:数据寄存器,读、写页时,数据存放此寄存器⑦Y-Gating⑧I/O Buffers & Latches⑨Global Buffers⑩Output DriverNAND Flash 存储单元组织结构图如下:K9F1G08容量为1056Mbit,分为65536行(页)、2112列,每一页大小为2kb,外加64字节的额外空间,这64字节的额外空间的列地址为2048-2111 命令、地址、数据都通过IO0-IO7输入/输出,写入命令、地址或数据时,需要将WE、CE信号同时拉低,数据在WE 信号的上升沿被NAND FLash锁存;命令锁存信号CLE、地址锁存信号ALE用来分辨、锁存命令或地址。

nand flash读写原理

NAND Flash是一种非易失性存储器,存储数据的方式采用了NAND门的逻辑结构。

其读写原理如下:

读取数据:

1. 首先,控制器会向NAND Flash发送要读取的数据的地址信息。

2. NAND Flash读取到地址信息后,开始查找所需的数据,将数据以页的形式发送给控制器。

3. 控制器对收到的数据进行校验,确保读取的数据没有错误。

写入数据:

1. 接收到数据后,控制器会将要写入的数据分成数据块,并分别进行处理。

2. 控制器将数据块写入NAND Flash中。

3. NAND Flash先将原有的数据进行擦除,并将新数据写入擦除后的空页面。

4. 写入操作结束,控制器对写入的数据进行校验,确保写入的数据没有错误。

需要注意的是,NAND Flash是按页进行读写操作的,一个页面的大小一般为512字节或1KB,因此每次读写操作的数据都必须是页面的整数倍。

同时,每次写入操作会导致该页面的原有数据被擦除,因此需要谨慎选择写入时机。

nandflash基础——基本操作

nand flash最基本的操作就是读写擦。

读

对于处于被擦除状态的cell, Vth都在0V(Vread)以下;而被写之后的cell,Vth则处于0V(Vread)和Vpassr之间。

Vpassr在4V以下。

根据这样的特性,则可以通过设置偏置电压来使cell处于导通状态。

当需要读取一个cell时,在栅极(gate)上需要提供一个Vread 电压(0V),在其他的cell上加上一个Vpass,r电压,通常在4-5V,这个电压是大于Vpassr的,足以使cell导通,无论是在被擦除状态和被写的状态。

这样的话,string上的导通情况就由被读取的cell状态决定。

如果这个cell是被擦除的,0V的电压就足以导通;如果这个cell是被写过的,则0V不足以使其导通。

于是存在两种状态,可以代表一个bit 的信息。

导通状态下,string上就存在电流,通过sense amplifier可以转换为电压信号。

写。

6 NAND FLASH CONTORLLER

OVERVIEW

In recent times, NOR flash memory gets high in price while an SDRAM and a NAND flash memory is comparatively economical , motivating some users to execute the boot code on a NAND flash and execute the main code on an SDRAM.

S3C2440A boot code can be executed on an external NAND flash memory. In order to support NAND flash boot loader, the S3C2440A is equipped with an internal SRAM buffer called ‘Steppingstone’.

When booting, the first 4K Bytes of the NAND flash memory will be loaded into Steppingstone and the boot code loaded into Steppingstone will be executed.

Generally, the boot code will copy NAND flash content to SDRAM. Using hardware ECC, the NAND flash data validity will be checked. Upon the completion of the copy, the main program will be executed on the SDRAM.

comparatively 比较地、相当地

motivating v. 激励;刺激;调动…的积极性(motivate的ing形式)

execute vt. 实行;执行;处死

internal n. 内脏;本质adj. 内部的;里面的;体内的;(机构)内部的

Steppingstone n. 踏脚石;进身之阶;达到目的的手段

validity n. [计] 有效性;正确;正确性

content n. 内容,目录;满足;容量adj. 满意的;vt. 使满足

FEATURES

1. Auto boot: The boot code is transferred into 4-kbytes Steppingstone during reset.

After the transfer, the boot

code will be executed on the Steppingstone.

2. NAND Flash memory I/F: Support 256Words, 512Bytes, 1KWords and 2KBytes Page.

3. Software mode: User can directly access NAND flash memory, for example this

feature can be used in read/erase/program NAND flash memory.

4. Interface: 8 / 16-bit NAND flash memory interface bus.

5. Hardware ECC generation, detection and indication (Software correction).

6. SFR I/F: Support Little Endian Mode, Byte/half word/word access to Data and ECC

Data register, and Word

access to other registers

7. SteppingStone I/F: Support Little/Big Endian, Byte/half word/word access.

8. The Steppingstone 4-KB internal SRAM buffer can be used for another purpose after

NAND flash booting.

特性

1。

自动引导:在复位时,引导代码写入4-k字节的中转区,在转移后启动

代码将在中转区上执行。

2。

NAND闪存接口:支持256字,512字节,1k字和2KB字节页。

3。

软件模式:用户可以直接访问NAND闪存,例如这个特性可以用于

读/写/擦除NAND闪存。

4。

接口:8/16位NAND闪存接口总线。

5。

硬件ECC的生成、检测和指示(软件校正)。

6。

SFR/f : 支持小端模式、按照字节/半字/字访问数据和ECC数据寄存器,以及按字访问其他寄存器

7.中转区接口:支持大小端模式下字节/半字/字的访问。

8。

在NAND闪存引导启动后,中转区的4 kb内部SRAM缓冲区可以用于另一个用途

systembus:系统总线

AHB Slave I/F:AHB系统总线,系统从属接口

SFR:

bootloader功能:

在重置期间,Nand闪存控制器将通过Pin状态获取相关的Nand闪存的信息。

ping状态:(NCON(flash),GPG13(页面大小),GPG14(地址循环),GPG15(总线宽度)-指针配置).

在发生电源或系统复位后,NAND闪存控制器自动加载4-KBytes引导加载程序代码并在中转区执行。

请注意

在自动引导期间,ECC不会去检测。

因此,第一个4 kb的NAND闪存应该没有错误.

pin-NCON引脚配置:

OM[1:0]=00:使能闪存引导

NCON:NAND闪存的模式选择(常规/超前先进)

0: NAND闪存常规模式(256word/512字节页面大小,3/4地址循环)

1: NAND闪存先进模式(1kword/2kbytes页面大小,4/5地址循环)

GPG13:NAND闪存页面容量选择

0:页面=256字(NCON=0)或页面=1k字(NCON=1)

1:页面=512字节(NCON=0)或页面=2KBytes(NCON=1)

GPG14:NAND闪存地址循环选择

0:3个地址循环(NCON=0)或4个地址循环(NCON=1)

1:4个地址循环(NCON=0)或5个地址循环(NCON=1)

GPG15:NAND闪存总线宽度选择

0:8位总线宽度

1:16位总线宽度

请注意

配置pin-NCON,GPG 15:13-将在重置时获取。

在正常状态下,这些引脚必须被设置为输入,以便在输入时不改变pin状态。

这是为了防止在睡眠模式下这些引脚的状态被改变,这种改变都是由软件或意想不到不可预知的的原因造成。

在4位以上的情况下,可能的总组合是16,但并不是所有的值都可以使用。

中转区(4K 字节 SRAM )

NAND Flash 控制器在引导启动时将 Steppingstone 作为缓冲器,你也可以使用此区域为其它用途

上表是28位校验码,奇偶校验码

EEC (错误纠正码)

NAND Flash 控制器由 4 个 ECC(错误纠正码)模块组成。

其中两个 ECC 模块:

一个模块可以被用于2048 字节的 ECC 奇偶校验码的生成。

另一个模块可以被用于16 字节的 ECC 奇偶校验码的生成。

28 位 ECC 奇偶校验码= 22位行奇偶校验+6位列校验码。

14 位 ECC 奇偶校验码= 8 位行奇偶校验+6位列校验码。