3-8译码器的VHDL设计

- 格式:doc

- 大小:15.00 KB

- 文档页数:3

实验三-quartus-ii的设计处理(3-8译码器设计)

《可编程逻辑器件的设计与仿真》

实验报告

实验项目实验三Quartus II的设计处理(3-8译码器设计)

实验目的1.设计一个3-8译码器;

2.学习用VHDL进行逻辑描述。

实验器材PC机,Quartus II

授课形式集中训练任课教师:彭铁牛实验时间:2013-03-17

实验说明本设计实现一个3-8译码器,其逻辑功能如表所示

C B A Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0

0 0 0 1 1 1 1 1 1 1 0

0 0 1 1 1 1 1 1 1 0 1

***********

0 1 1 1 1 1 1 0 1 1 1

1 0 0 1 1 1 0 1 1 1 1

1 0 1 1 1 0 1 1 1 1 1

1 1 0 1 0 1 1 1 1 1 1

1 1 1 0 1 1 1 1 1 1 1

本设计练习用VHDL语言描述仿真译码器。

要求编写3-8译码器的VHDL设计文件。

注意VHDL文件的结构和语法,并掌Quartus II 平台中文本编辑器的使用方法。

实验内容和体会

1

Ⅰ.VHDL源程序Ⅱ.仿真波形Ⅲ.元件符号Ⅳ.实验体会。

《EDA技术》课程实验报告学生姓名:张叶所在班级:通信1301指导教师:黄科老师记分及评价:一、实验名称实验4:3-8译码器的设计二、任务及要求【基本部分】1、在QuartusII平台上,采用文本输入设计方法,通过编写VHDL语言程序,完成3-8译码器的设计并进行时序仿真。

2、设计完成后生成一个元件,以供更高层次的设计调用。

3、实验箱上进行验证。

【发挥部分】设计4-8译码器,完成仿真并封装成一个元件;新建原理图,调用一片74161和所设计的4-8译码器,完成具有16种花样的循环LED灯控制器的设计,并在实验箱上进行验证。

三、实验程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity ky isport(A :in std_logic_vector(2 downto 0);Y :out std_logic_vector(7 downto 0));end entity ky;architecture ky_a of ky isbeginprocess(A)begincase A iswhen "000" => Y<="11111110";when "001" => Y<="11111101";when "010" => Y<="11111011";when "011" => Y<="11110111";when "100" => Y<="11101111";when "101" => Y<="11011111";when "110" => Y<="10111111";when others => Y<="01111111"; end case;end process;end architecture ky_a;四、仿真及结果分析仿真结果五、硬件验证1、引脚锁定情况表:引脚情况锁定表六、小结在本次实验中,老师教我们用QuartusII软件设计并仿真了3-8译码器。

《在VHDL中用多种方法描述3线-8线译码器》沈明山2011-01-033_8译码器元件符号:addres[2..0]: 地址信号线3根;sta: 选择信号,高电平有效;stbn: 选择信号,低电平有效;stcn:选择信号,低电平有效;yout[7..0]: 译码器输出信号,8位,每位的输出低电平有效。

功能表:同74LS138相同。

一、条件信号赋值语句法。

1、条件信号赋值语句格式沈明山《EDA技术及可编程器件应用实训》科学出版社2004年10月第1版p185;王传新《FPGA设计基础》高等教育出版社2007年9月第1版P742、文本范例:decoder3_8_1.vhdLIBRARY ieee;USE IEEE.STD_LOGIC_1164.ALL;ENTITY decoder3_8_1 ISPORT(addres : IN STD_LOGIC_VECTOR(2 downto 0);sta, stbn, stcn: IN STD_LOGIC;yout : OUT STD_LOGIC_VECTOR(7 downto 0));END decoder3_8_1;ARCHITECTURE a OF decoder3_8_1 ISSIGNAL ytemp : STD_LOGIC_vector(7 downto 0);SIGNAL st_temp : STD_LOGIC_vector(2 downto 0);BEGINst_temp<= sta&stbn&stcn;ytemp<="11111110" WHEN (addres="000") ELSE"11111101" WHEN (addres="001") ELSE"11111011" WHEN (addres="010") ELSE"11110111" WHEN (addres="011") ELSE"11101111" WHEN (addres="100") ELSE"11011111" WHEN (addres="101") ELSE"10111111" WHEN (addres="110") ELSE"01111111" WHEN (addres="111") ;yout<=ytemp WHEN (st_temp="100")ELSE "11111111";END a; --3_8译码器的设计方法1条件信号赋值语句法3、仿真波形图二、选择信号赋值语句法1、选择信号赋值语句格式沈明山《EDA技术及可编程器件应用实训》科学出版社2004年10月第1版p185;王传新《FPGA设计基础》高等教育出版社2007年9月第1版P742、文本范例:decoder3_8_2.vhdLIBRARY ieee;USE IEEE.STD_LOGIC_1164.ALL;ENTITY decoder3_8_2 ISPORT(addres : IN STD_LOGIC_VECTOR(2 downto 0);sta,stbn,stcn: IN STD_LOGIC;yout : OUT STD_LOGIC_VECTOR(7 downto 0));END decoder3_8_2;ARCHITECTURE a OF decoder3_8_2 ISSIGNAL ytemp : STD_LOGIC_vector(7 downto 0);SIGNAL st_temp : STD_LOGIC_vector(2 downto 0);BEGINst_temp<= sta&stbn&stcn;WITH addres SELECTytemp<="11111110" WHEN "000","11111101" WHEN "001","11111011" WHEN "010","11110111" WHEN "011","11101111" WHEN "100","11011111" WHEN "101","10111111" WHEN "110","01111111" WHEN "111","11111111" WHEN OTHERS; --必须加此句,以便对U、Z等情况做出限定yout<=ytemp WHEN (st_temp="100")ELSE "11111111";END a; --3_8译码器的设计方法2:选择信号赋值法。

《电子设计自动化》实验报告实验一实验名称:3-8译码器的设计专业及班级:姓名:学号:一、实验目的:1.掌握组合逻辑电路的设计方法。

2.掌握 VHDL 语言的基本构造及设计的输入方法。

3.掌握 VHDL 语言的基本描绘语句的使用方法。

二、实验步骤(附源代码及仿真结果图):1.成立工程, Quartus II -- project wizard (注意工程目录中不可以出现中文字符,不可以成立在桌面上);弹出窗口如图 2-3 所示。

图 2-3 New Project Wizard 窗口2.点击next,在出现的对话框中输入以下项目信息:a.项目路径,如: D:\EDA experiment\decoder38; b.项目名称,如: decoder38。

如图 2-4 所示:图 2-4 项目路径和项目名称对话框3.点击 2 次 next 后,出现如图 2-5 所示的对话框:a.Device family 中选择 Cyclone IV E;b.Available devices 中选择 EP4CE115F29C7.图 2-5器件选择窗口4.点击next后,出现EDA工具设置对话框。

在Simulation一行中, Tool Name 选择ModelSim-Altera , Fomat(s)选择 VHDL ,如图 2-6 所示。

图 2-6 EDA 工具设置对话框5.点击 next,出现如图 2-7 所示的对话框:图 2-7 新建项目汇总对话框6. 点击 Finish 后,出现如图2-8 所示的界面:图 2-8 decoder38 项目界面7.点击 File->New->VHDL File ,如图 2-9 所示。

点击 ok 封闭对话框。

图 2-9 新建 VHDL 文件窗口8.在文本编写框内键入以下程序:LIBRARY ieee;USE ieee.std_logic_1164.ALL;ENTITY decoder38 ISPORT(A, B,C,G1,G2A,G2B: IN STD_LOGIC;Y: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END decoder38;ARCHITECTURE Behavior OF decoder38 ISSIGNAL indata: STD_LOGIC_VECTOR(2 DOWNTO 0); BEGINindata <= C&B&A;PROCESS (indata, G1, G2A,G2B)BEGINIF (G1='1' AND G2A='0' AND G2B='0') THENCASE indata ISWHEN "000"=>Y<="11111110";WHEN "001"=>Y<="11111101";WHEN "010"=>Y<="11111011";WHEN "011"=>Y<="11110111";WHEN "100"=>Y<="11101111";WHEN "101"=>Y<="11011111";WHEN "110"=>Y<="10111111";WHEN "111"=>Y<="01111111";WHEN OTHERS =>Y<="XXXXXXXX";END CASE;ELSEY<="11111111";END IF;END PROCESS;END Behavior;9. 将文件保留为decoder38.vhd 后,开始编译,点击Processing->Start Compilation ,编译成功后,出现如图2-10 所示界面:图 2-10 编译成功界面10.再次新建一个 vhdl 文件,键入以下的 modelsim 测试程序:LIBRARY ieee;USE ieee.std_logic_1164.ALL;ENTITY decoder38_tb ISEND decoder38_tb;ARCHITECTURE Behavior OF decoder38_tb ISCOMPONENT decoder38PORT (A,B,C,G1,G2A,G2B: IN STD_LOGIC;Y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END COMPONENT;SIGNAL A: STD_LOGIC:='0';SIGNAL B : STD_LOGIC:='0';SIGNAL C: STD_LOGIC:='0';SIGNAL G1: STD_LOGIC:='1';SIGNAL G2A: STD_LOGIC:='0';SIGNAL G2B: STD_LOGIC:='0';SIGNAL Y: STD_LOGIC_VECTOR(7 DOWNTO 0);CONSTANT CLK_PERIOD: TIME:=10ns;BEGINA<=not A after CLK_PERIOD;B<=not B after 20ns;C<=not C after 40ns;U1: decoder38 port map(A=>A,B=>B,C=>C,G1=>G1,G2A=>G2A,G2B=>G2B,Y=>Y);END behavior;11.将文件保留为 decoder38_tb.vhd ,编译经过。

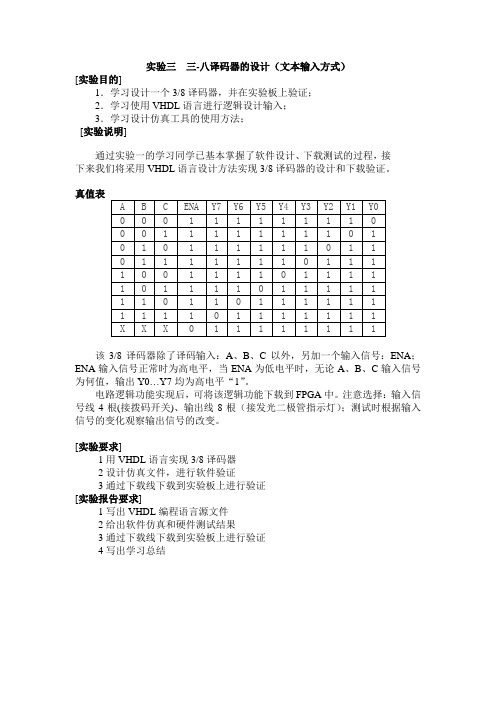

实验三三-八译码器的设计(文本输入方式)[实验目的]1.学习设计一个3/8译码器,并在实验板上验证;2.学习使用VHDL语言进行逻辑设计输入;3.学习设计仿真工具的使用方法;[实验说明]通过实验一的学习同学已基本掌握了软件设计、下载测试的过程,接下来我们将采用VHDL语言设计方法实现3/8译码器的设计和下载验证。

真值表该3/8译码器除了译码输入:A、B、C以外,另加一个输入信号:ENA;ENA输入信号正常时为高电平,当ENA为低电平时,无论A、B、C输入信号为何值,输出Y0…Y7均为高电平“1”。

电路逻辑功能实现后,可将该逻辑功能下载到FPGA中。

注意选择:输入信号线4根(接拨码开关)、输出线8根(接发光二极管指示灯);测试时根据输入信号的变化观察输出信号的改变。

[实验要求]1用VHDL语言实现3/8译码器2设计仿真文件,进行软件验证3通过下载线下载到实验板上进行验证[实验报告要求]1写出VHDL编程语言源文件2给出软件仿真和硬件测试结果3通过下载线下载到实验板上进行验证4写出学习总结library IEEE;use IEEE.std_logic_1164.all;entity seg38 isport (data_in : in std_logic_vector (2 downto 0);ENA : in std_logic;data_out : out std_logic_vector (7 downto 0) );end entity;architecture seg38_arch of seg38 isbeginprocess(data_in, ENA)beginif ENA='1' thencase data_in iswhen "000" => data_out <= "11111110"; -- 0when "001" => data_out <= "11111101"; -- 1when "010" => data_out <= "11111011"; -- 2when "011" => data_out <= "11110111"; -- 3when "100" => data_out <= "11101111"; -- 4when "101" => data_out <= "11011111"; -- 5when "110" => data_out <= "10111111"; -- 6when "111" => data_out <= "01111111"; -- 7when others => NULL;end case;end if;end process;end architecture;管脚说明:ABC 分别对应data_2,1,0,锁定为:29,30,31 输出Y0-Y7非别对应data_out0-7,锁定为:灯1到8实验五BCD/七段显示译码器实验(文本输入方式)[实验目的]1.学习设计一个BCD/七段显示译码器,并在实验板上验证;2.掌握使用VHDL语言进行逻辑设计输入;3.掌握设计仿真工具的使用方法;[实验说明],C,D、ENA共5根,信号ENA的功能与3/8译码器功能相同,7段译码器的逻辑表同学自行设计,要求实现功能为:输入“0…15 ”(二进制),输出“0…9…F ”(显示数码),输出结果应在数码管上显示出来。

实验一3-8译码器设计实验目的:掌握3-8译码器的设计方法;掌握if else语句和case语句的使用方法;掌握VHDL电路的设计,仿真和硬件测试方法设计描述:端口描述:输入变量为A,B,C,输出变量有8个,即Y0-Y7.G1,G2A,G2B为选通输入,仅当G1=1,G2A=0,G2B=0时,译码器能正确工作,否则,译码器输出无效,即Y0-Y7均为高电平。

真值表:编译的程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY shiyan1 ISPORT(A : IN STD_LOGIC_vector(2 downto 0);G1,G2A,G2B:IN STD_LOGIC;Y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END shiyan1;ARCHITECTURE yimaqi OF shiyan1 ISSIGNAL S : STD_LOGIC_VECTOR(2 DOWNTO 0); BEGINS<=G1&G2A&G2B;PROCESS(A,S)BEGINIF(S="100")THENCASE A ISWHEN "000"=>Y<="11111110";WHEN "001"=>Y<="11111101";WHEN "010"=>Y<="11111011";WHEN "011"=>Y<="11110111";WHEN "100"=>Y<="11101111";WHEN "101"=>Y<="11011111";WHEN "110"=>Y<="10111111";WHEN "111"=>Y<="01111111";WHEN OTHERS=>Y<="11111111";END CASE;END IF;END PROCESS;END ARCHITECTURE yimaqi;时序仿真图RTL电路图分析:3-8译码器有3个使能端,3个地址输入端,8个输出端,则在实体中定义三个地址输入端口A2、A1、A0;三个使能输入端口G1、G2A、G2B及八个输出端口Y7~Y0。

实验2 3/8译码器实验一、实验目的1.设计一个3/8译码器;2.学习用VHDL进行逻辑描述;3.学习设计仿真工具的使用方法。

二、实验说明本实验实现一个3/8译码器。

其逻辑功能如表7.1所示。

表7.1 3/8译码器的逻辑功能表实验仍利用拨动开关和发光二极管进行信号输入和显示。

实验板上的开关和发光二极管的管脚分布见实验板说明。

本实验练习用VHDL语言描述并仿真译码器。

要求编写3/8译码器的VHDL设计文件。

注意VHDL文件的结构和语法,并掌握MAX+plusⅡ平台中文本编辑器的使用方法。

三、实验要求1.要求用VHDL编写3/8译码器;2.设计输入波形文件,并进行模块的功能仿真;3.编程并实验验证;四、总结报告要求1.写出VHDL文件;2.写出测试向量文件;3.写出仿真和测试结果。

附3:实现3/8译码器LIBRARY IEEE;--库使用说明USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY yima38 isPORT(A:IN STD_LOGIC_VECTOR(2 DOWNTO 0);--输入端口Y:OUT STD_LOGIC_VECTOR(7 downto 0));--输出端口END;ARCHITECTURE BEHA VIOR OF yima38 ISBEGINWITH A SELECT --译码:并行语句实现Y<=“11111110”WHEN“000”,“11111101”WHEN“001”,“11111011”WHEN“010”,“11110111”WHEN“011”,“11101111”WHEN“100”,“11011111”WHEN“101”,“10111111”WHEN“110”,“01111111”WHEN“111”,“00000000”WHEN OTHERS;END BEHA VIOR;。

摘要EDA技术是以微电子技术为物理层面,现代电子设计技术为灵魂,计算机软件技术为手段,最终形成集成电子系统或专用集成电路ASIC为目的的一门新兴技术。

而VHDL语言是硬件描述语言之一,其广泛应用性和结构的完整性使其成为硬件描述语言的代表。

随着社会经济和科技的发展,越来越多的电子产品涌如我们的日常生活当中,在日常生活中译码器起着不可忽视的作用。

本设计就是运用VHDL语言设计的3-8译码器。

3-8译码器电路的输入变量有三个即D0,D1,D2,输出变量有八个Y0-Y7,对输入变量D0,D1,D2译码,就能确定输出端Y0-Y7的输出端变为有效(低电平),从而达到译码目的。

关键词 EDA 输入,输出,译码器AbstractEDA technology is for the physical plane microelectronics technology, modern electronic design technology for the soul, and computer software technology as the means, and finally form integrated electronic system or application-specific integrated circuit ASIC for the purpose of a new technology. And VHDL language is one of the hardware description language, which are widely applied and theintegrity of the structure to make it a hardware description language representative.Along with the social economy and the development of science and technology, more and more electronic product surged into our daily life in the daily life of decoder plays an important role. This design is theuse of the design of 3-VHDL language 8 decoder. 3-8 decoder circuit, input variables have three namely D0, D1, D2, output variable has eight Y0-Y7, D0 to input variables, D1, D2 decoding, can determine the output, the output terminal of the Y0-Y7 into effective (low level), so as to achieve the purpose decoding.Key word EDA input output decode目录引言EDA(Electronic Design Automation)技术是现代电子工程领域的一门新技术。

3-8译码器VHDL设计实验报告一、设计原理:先判断使能端口EN状态,当其满足高电平时,判断三个输入端口A2,A1,A0的状态来决定输出。

若使能端口为低电平则固定输出不受逻辑输出A2,A1,A0的影响。

使能有效时按照三个输入状态决定八个输出的状态。

真值表:A2 A1 A0 Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y00 0 0 0 0 0 0 0 0 0 10 0 1 0 0 0 0 0 0 1 00 1 0 0 0 0 0 0 1 0 00 1 1 0 0 0 0 1 0 0 01 0 0 0 0 0 1 0 0 0 01 0 1 0 0 1 0 0 0 0 01 1 0 0 1 0 0 0 0 0 01 1 1 1 0 0 0 0 0 0 0二、实验程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY demo ISPORT(A:IN STD_LOGIC_VECTOR(2 DOWNTO 0);EN:IN STD_LOGIC;Y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END demo;ARCHITECTURE DEC_BEHAVE OF demo ISSIGNAL SEL:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINSEL(0)<=EN;SEL(1)<=A(0);SEL(2)<=A(1);SEL(3)<=A(2);WITH SEL SELECTY<= "00000001" WHEN "0001","00000010" WHEN "0011","00000100" WHEN "0101","00001000" WHEN "0111","00010000" WHEN "1001","00100000" WHEN "1011","01000000" WHEN "1101","10000000" WHEN "1111","11111111" WHEN OTHERS;END DEC_BEHAVE;三、实验步骤(一)、设计输入1 、创建新工程(1) 打开QuartusII软件,在主界面中执行FILE—>New project Wizard(2) 在向导的第一页设置工程文件夹,工程名称及顶层实体名称。

3-8译码器的VHDL设计

1.实体框图

2.程序设计

正确的程序

LIBRARY IEEE;

USE DECODER38A IS

PORT(A2,A1,A0,S1,S2,S3:IN STD_LOGIC;

Y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY DECODER38A;

ARCHITECTURE ONE OF DECODER38A IS

SIGNAL S: STD_LOGIC_VECTOR(5 DOWNTO 0);

BEGIN

S<=A2&A1&A0&S1&S2&S3;

WITH S SELECT

Y<="" WHEN "000100",

"" WHEN "001100",

"" WHEN "010100",

"" WHEN "011100",

"" WHEN "100100",

"" WHEN "101100",

"" WHEN "110100",

"01111111" WHEN "111100",

"" WHEN OTHERS;

END ARCHITECTURE ONE;

3.仿真波形图

4.仿真波形分析

当S1 S2 S3=100时,只有当A2 A1 A0=111时,Y[7]才输出低电平,否则为

高电平,当A2 A1 A0=110时,Y[6]才输出低电平,否则为高电平,当A2 A1 A0=101时,Y[5]才输出低电平,否则为高电平,Y[4]到Y[0]同理。

可见该程序设计的是3-8译码器

三、共阳极数码管七段显示译码器的VHDL设计

1.实体框图

2.程序设计

正确的程序

LIBRARY IEEE;

USE DISPLAY_DECODER IS

PORT(A3,A2,A1,A0:IN STD_LOGIC;

Y:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));

END ENTITY DISPLAY_DECODER;

ARCHITECTURE ONE OF DISPLAY_DECODER IS

SIGNAL S: STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

S<=A3&A2&A1&A0;

WITH S SELECT

Y<="1111110" WHEN "0000",

"0110000" WHEN "0001",

"1101101" WHEN "0010",

"1111001" WHEN "0011",

"0110011" WHEN "0100",

"1011011" WHEN "0101",

"1011111" WHEN "0110",

"1110000" WHEN "0111",

"1111111" WHEN "1000",

"1111011" WHEN "1001",

"0000000" WHEN OTHERS;

END ARCHITECTURE ONE;

3.仿真波形图

4.仿真波形分析

由图可知,当A3 A2 A1 A0=0000时,输出Y[6]到Y[0]对应为1111110,即只有g不亮,数码管显示为0,

A3 A2 A1 A0=0001时,输出对应为0110000,数码管显示为1,

A3 A2 A1 A0=0010时,输出对应为1101101,数码管显示为2,

其他同理,当A3 A2 A1 A0>1001,即大于9,数码管无显示。

由此可知,程序设计的是七段显示译码管。