基于GSM标准的零中频接收机设计

- 格式:pdf

- 大小:2.68 MB

- 文档页数:57

零中频接收机设计2013年09月24日13:09eechina分享关键词:零中频,接收机作者在:冷爱国,TI公司China Telecom system摘要相较传统的超外差接收机,零中频接收机具有体积小,功耗和成本低,以及易于集成化的特点,正受到越来越广泛关注,本文结合德州仪器(TI)的零中频接收方案(TRF3711),详细分析介绍了零中频接收机的技术挑战以及解决方案。

概述零中频接收机在几十年前被提出来,工程中经历多次的应用实践,但是多以失败告终,近年来,随着通信系统要求成本更低,功耗更低,面积更小,集成度更高,带宽更大,零中方案能够很好的解决如上问题而被再次提起。

本文将详细介绍零中频接收机的问题以及设计解决方案,结合TI的零中频方案TRF3711测试结果证明,零中频方案在宽带系统的基站中是可以实现的。

1、超外差接收机1.1超外差接收机问题为了更好理解零中频接收的优势,本节将简单总结超外差接收机的一些设计困难和缺点。

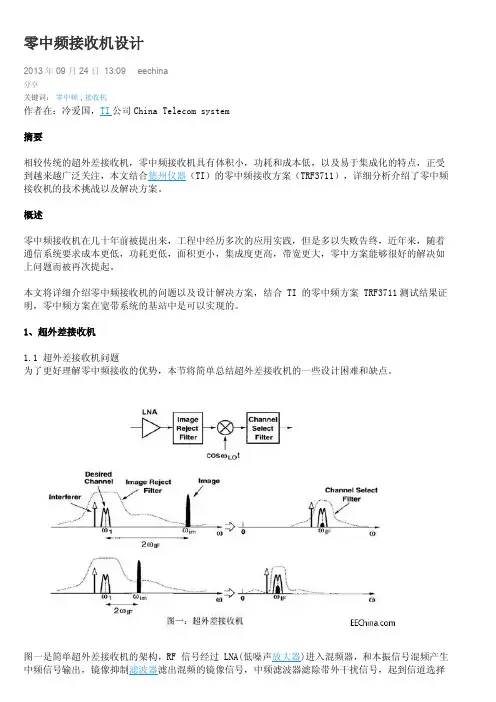

图一是简单超外差接收机的架构,RF信号经过LNA(低噪声放大器)进入混频器,和本振信号混频产生中频信号输出,镜像抑制滤波器滤出混频的镜像信号,中频滤波器滤除带外干扰信号,起到信道选择的作用,图中标示了频谱的搬移过程及每一部分的功能。

在超外差接收机种最重要的问题是怎样在镜像抑制滤波器和信号选择滤波器的设计上得到平衡,如图一所示,对滤波器而言,当其品质因子和插损确定,中频越高,其对镜像信号的抑制就越好,而对干扰信号的抑制就比较差,相反,如果中频越低,其对镜像信号的抑制就变差,而对干扰信号的抑制就非常理想,由于这个原因,超外差接收机对镜像滤波器和信道滤波器的选择传输函数有非常高的要求,通常会选用声表滤波器(SAW),或者是采用高阶LC滤波器,这些都不利于系统的集成化,同时成本也非常高。

在超外差接收机中,由于镜像抑制滤波器是外置的,LNA必须驱动50R负载,这样还会导致面积和放大器噪声,增益,线性度,功耗的平衡性问题。

一种中频数字接收机设计一种实用的中频数字接收机设计摘要:针对后三代移动通信系统研究所需硬件平台的要求,提出了一种灵活性强的可扩展中频接收机设计方案。

这种方案可以在较高的中频频率上实现信号的数字化接收,且适用于多种输入信号。

该方案以自顶向下的思路,吸取其它方案的优点,完成了基于软件无线电思想的数字化接收机设计。

该系统结构简单,成本低,有良好的实用性和通用性。

关键词:带通采样采样速率数字下变频近年来,移动通信的发展十分迅速。

应对更高速率业务的要求,我国对于后三代移动通信系统(B3G)的研究也逐渐兴起,但是目前多局限于对仿真数据进行理论研究和模拟阶段,有必要建立一个硬件实验平台,以便寻找研究成果的应用方法。

此硬件平台应具有适合于软件无线电的体系,在硬件结构上与无线通信的通用功能模块相一致:不仅可以接收现存通信标准规定的信号,还可以处理由用户自定义的信号,为未来研究提供可靠的实测数据。

该平台还应具有高度的灵活性、开放性以支持多种通信体制和不同的QoS(Quality of Service)要求。

从软件无线电的观点来看,受宽带天线、高速A/D转换器及数字信号处理器等发展水平的限制,实现一个理想的软件无线电平台[1]的条件目前还不具备。

因此,本文根据系统提出的中频频率为70MHz、信号带宽为10MHz的设计要求,在分析比较了几个方案优缺点的基础上,着重研究了在现有器件情况下最大限度地实现中频数字化这一关键问题,最终设计了一种可用于所述实验平台的中频数字化接收机。

在使用该方案的实际系统上,可以对新一代蜂窝移动通信系统中的关键技术进行研究和实验评估。

1 初步设计方案站在系统灵活性的角度,本文暂不考虑使用模拟解调器的中频接收方案,而采用数字化的处理,先提出两种方案。

1.1 单路带通采样方案,根据系统的中频频率和带宽两项参数指标,若进行低通采样,由Nyquist定理知,采样速率至少要150Msps才能保证频谱不会发生混迭。

零中频接收机设计冷爱国--- China Telecom system摘要相较传统的超外差接收机,零中频接收机具有体积小,功耗和成本低,以及易于集成化的特点,正受到越来越广泛关注,本文结合德州仪器(TI)的零中频接收方案(TRF3711),详细分析介绍了零中频接收机的技术挑战以及解决方案。

概述零中频接收机在几十年前被提出来,工程中经历多次的应用实践,但是多以失败告终,近年来,随着通信系统要求成本更低,功耗更低,面积更小,集成度更高,带宽更大,零中方案能够很好的解决如上问题而被再次提起。

本文将详细介绍零中频接收机的问题以及设计解决方案,结合TI 的零中频方案 TRF3711测试结果证明,零中频方案在宽带系统的基站中是可以实现的。

1、超外差接收机1.1 超外差接收机问题为了更好理解零中频接收的优势,本节将简单总结超外差接收机的一些设计困难和缺点。

图一是简单超外差接收机的架构,RF 信号经过LNA(低噪声放大器)进入混频器,和本振信号混频产生中频信号输出,镜像抑制滤波器滤出混频的镜像信号,中频滤波器滤除带外干扰信号,起到信道选择的作用,图中标示了频谱的搬移过程及每一部分的功能。

在超外差接收机种最重要的问题是怎样在镜像抑制滤波器和信号选择滤波器的设计上得到平衡,如图一所示,对滤波器而言,当其品质因子和插损确定,中频越高,其对镜像信号的抑制就越好,而对干扰信号的抑制就比较差,相反,如果中频越低,其对镜像信号的抑制就变差,而对干扰信号的抑制就非常理想,由于这个原因,超外差接收机对镜像滤波器和信道滤波器的选择传输函数有非常高的要求,通常会选用声表滤波器(SAW),或者是采用高阶 LC 滤波器,这些都不利于系统的集成化,同时成本也非常高。

在超外差接收机中,由于镜像抑制滤波器是外置的,LNA 必须驱动 50R 负载,这样还会导致面积和放大器噪声,增益,线性度,功耗的平衡性问题。

镜像滤波器和选择滤波器的平衡设计也可采用镜像抑制架构,如图二所示的 Hartley(1)和 Weaver(2)拓扑架构,在 A 点和 B 点的输出是相同极性的有用信号和极性相反的镜像信号,这样通过后面的加法器,镜像信号就可以被抵消掉,从而达到简化镜像滤波器的设计,但是这种架构由于相位和幅度不平衡,其镜像信号没有办法完全抑制,如证明(6),镜像抑制比 IIR。

第25卷第4期增刊仪器仪表学报2004年8月零中频宽带数字接收机方案的设计+靳明林明秀宋建中(中国科学院长春光学精密机械与物理研究所长春130033)摘要通过应用软件无线电的思想,搭建了一个用于宽带中频(射频)信号接收的硬件平台,将处于中频(射频)段的高速宽带的模拟信号以下变频的方式变成处于基带的数字信号,同时以正交I,Q信号的形式输出,以便于后续的DSP对其进行软件算法的调解和处理。

该接收机设计输出的单通道带宽可达20MHz,适合宽带中频(射频)信号的接收,是目前硬件条件受到限制的情况下,宽带中频(射频)信号接收方法中一个可行的实施方案。

关键词软件无线电零中频数字下变频器宽带数字接收机DesignandImplementationofZero—IFWidebandDigitalReceiverJinMingLinMingxiuSongJianzhong(ChangchunInstituteofOptics,FineMechanicsandPhysics,ChineseAcademyofSciences,Changchun130033,China)AbstractAhardwarestructureusedtOreceivethewidebandIF(RF)signalswasbuiltbyusingtheideaofsoft—wareradio.ItcandownconverttheIF(RF)analogwidebandsignalstodigitalbasebandones.Inordertodemod—u|atethesignalsbyDSPsoftwarealgorithmic,thesignalwasoutputtedwiththeformatofIQ.Thedesignedsin—glechannelwidthofthereceiveris20MHzanditisaavailableschemeofwidebandIF(RF)signalreceivemeth—odspresentlythatthehardwareconditionisconfined.KeywordsSoftwareradioZero—IFDigitaldownconverterWidebanddigitalreceiver1引言软件无线电由天线,射频前端,宽带A/D、D/A转换器,通用和专用数字信号处理器及配套软件组成。

一种GSM接收机设计与实现作者:刘之光王星来源:《硅谷》2011年第12期摘要:介绍一种GSM接收机设计与实现方案,该设计中采用AD9445实现GSM信号的模数变换,将采集后数据送到FPGA和DSP中进行后续基带信号处理。

给出系统总体设计,并对其中的主要电路设计进行详细阐述。

由于该GSM接收机系统采用FPGA+DSP结构,因此系统具有较强的设计灵活性和较高的实用价值。

关键词: GSM;接收机;现场可编程门阵列;数字信号处理器中图分类号:TM92文献标识码:A文章编号:1671-7597(2011)0620070-010 引言GSM是全球使用最为广泛的一种无线通信标准,属于第2代蜂窝移动通信技术,GSM电话的市场份额占到全球移动电话市场份额的70%[1]。

传统的GSM接收设备一般采用专用ASIC芯片实现基带信号处理算法,该方法难以实现基带算法的灵活可调,可移植性不强。

随着软件无线电技术的发展,以及现场可编程门阵列(FPGA)和数字信号处理器(DSP)的进步,其被广泛应用于GSM接收设备中[2]。

本文介绍了一种GSM接收机的设计与实现,该设计采用FPGA+DSP结构,构建了一个便于修改、灵活性好的通用硬件平台。

1 GSM接收机系统总体设计本设计中GSM接收机采用了FPGA+DSP结构,其中FPGA采用了ALTERA公司StratixII 系列EP2S60,DSP采用了TI公司TMS320C6021芯片。

对于A/D转换器的选择,按照带通采样定理,选择为信号带宽的2倍或以上即可,因此本设计中A/D转换器采用了美国模拟器件公司生产的AD9445,为了给AD9445提供高速时钟,设计中采用了PLL芯片ADF4360提供所需时钟,同时为了满足AD9445差分输入需求,信号调理部分实现了单端信号转差分功能,具体GSM接收机硬件系统设计如图1所示。

图1GSM接收机硬件系统设计2 GSM接收机各主要电路设计与实现2.1 信号调理电路设计信号调理电路主要是完成信号单端输入转换成差分输出,采用了Mini-Circuits公司生产的单端-差分转换器ADTT1-6,其中VIN_A为单端输入信号,VIN-A和VIN+A为差分输出信号,具体电路设计如图2所示。

零中频接收机的研究和硬件设计零中频接收机是一种重要的通信设备,它在无线通信系统中扮演着至关重要的角色。

零中频接收机的主要作用是将接收到的射频信号转换为基带信号,以便后续的信号处理。

随着通信技术的不断发展,零中频接收机的研究和应用也越来越广泛。

本文旨在研究和设计一种高性能的零中频接收机,并对其性能进行实验验证。

零中频接收机的工作原理是将接收到的射频信号通过天线或传输线转换为交流电信号,然后经过低噪声放大器进行放大,最后经过解调器解调为基带信号。

其中,信号的解调是零中频接收机的核心环节。

常见的解调方法包括平方律解调、平方律检波、同步解调等。

本文所设计的零中频接收机将采用同步解调的方法进行解调。

零中频接收机的硬件设计包括多个组成部分,如天线、滤波器、放大器、混频器、检测器等。

其中,天线的作用是接收射频信号;滤波器的作用是滤除噪声和干扰信号;放大器的作用是对信号进行放大,以便后续处理;混频器的作用是将信号从射频频段搬移到基带频段;检测器的作用是检测信号的幅度和相位。

在硬件设计过程中,我们需要根据具体的系统要求,对各个组成部分进行详细的设计和选型。

例如,对于放大器,我们需要考虑其噪声性能、线性度和增益;对于混频器,我们需要考虑其变频损耗、噪声系数、端口隔离度等参数。

零中频接收机的软件设计主要是对硬件进行控制和配置,同时对信号进行数字处理。

软件设计的主要流程包括初始化、参数配置、数据采集、信号处理等。

在软件设计中,我们需要使用相关的编程语言和开发工具进行开发和调试。

同时,我们还需要考虑软件的可扩展性和可维护性。

为了验证本文所设计的零中频接收机的性能和可靠性,我们进行了一系列实验测试。

实验结果表明,该零中频接收机在低信噪比条件下仍能保持良好的性能,同时具有较低的相位噪声和较高的频率稳定度。

我们还对该零中频接收机的功耗和体积进行了测量和评估,结果表明该设计具有较高的集成度和较低的功耗。

在实验结果分析中,我们发现该零中频接收机的性能主要受到放大器噪声、混频器变频损耗等因素的影响。

基于零中频信道化接收机的研究与实现作者:***来源:《卫星电视与宽带多媒体》2020年第04期【摘要】接收机一直以来都是通信系统的一个重要组成部分,而随着数字化集成电路的发展,高速数字电路的设计逐步代替大部分模拟电路的工作,而收发信道后零中频架构接收电路显得尤为重要,本文详细介绍了一种通用的零中频信道化接收机的实现方法,并且已经在L波段某型通信系统中应用。

【关键词】零中频接收机;FPGA;DSP零中频(Zero Intermediate Frequency)接收机一般也被称为直接下变频接收机,它意味着接收到的中频信号会被直接下变频为基带信号,或者说这种接收机不存在中频处理。

当接收机的本振頻率与接收信号的载波相位锁定时,我们称其为零外差。

零中频接收架构之所以能吸引大量的关注是因为它具备超外差接收机所不具备的一些特点,首先就是接收架构中省去了中频处理单元,因而可以减少那些造价昂贵的中频无源滤波器(声表面波 SAW 滤波器),降低收发器件的成本和面积。

零中频接收机采用有源低通滤波器来完成信道低通滤波,这种滤波器的带宽可以根据需要设计为可调,针对常见的模拟基带电路,接收机很容易被设计成多种模式,包括处理常见的射频前端信号。

一方面,由于大部分的数字信号处理都发生在低频段,因而功率消耗可以降至最小化。

另一方面,需要剩余的所有模拟器件都保持较低的噪声,因为,来自射频部分的增益并不是很高。

需要注意的是,这种直接零中频接收机不需要频谱规划(需要耗费大量时间且有效性难以保证),适用性也更广。

1. 接收端整体框图输入信号为瞬时带宽10MHz,范围900-1300MHz的跳频信号。

射频信号经过4路下变频器与带通滤波器后经4路AD采样。

4路AD采样后的数据送入FPGA进行处理。

FPGA中有4路下变频器,其频率由跳频库控制4个DDS产生。

4路AD数据经过选择器与4路下变频器相连,信号在FPGA中完成下变频抽取滤波后送入同步解调和译码模块。

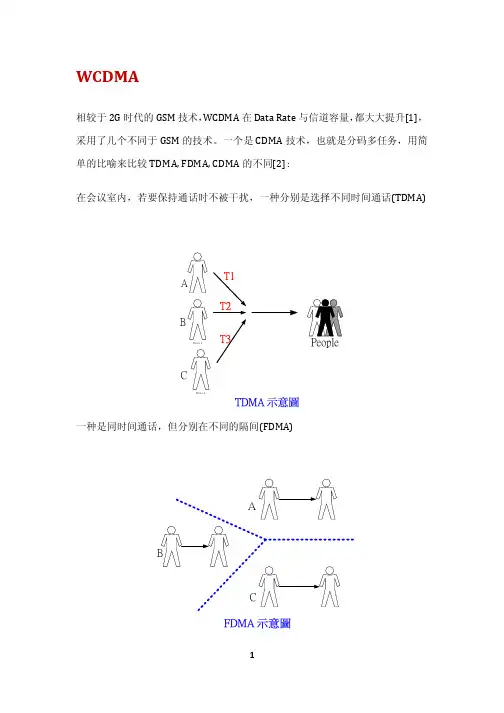

WCDMA相较于2G时代的GSM技术,WCDMA在Data Rate与信道容量,都大大提升[1],采用了几个不同于GSM的技术。

一个是CDMA技术,也就是分码多任务,用简单的比喻来比较TDMA, FDMA, CDMA的不同[2] :在会议室内,若要保持通话时不被干扰,一种分别是选择不同时间通话(TDMA)一种是同时间通话,但分别在不同的隔间(FDMA)还有一种是同时间又同隔间通话,但讲不同语言(CDMA)这三种技术,分别在时域跟频域的比较 :由上图可知,CDMA 不分时也不分频,但因为分码,采正交码技术,不同码之间完全没有相关,因此大大提高了安全性。

C另外则是展频技术,将讯号的带宽拓宽,使其带以拓宽,与前述的正交码有送数据没有关系,故的传送数据,因此使得讯号得知,带宽拓宽后,其信道由上式可知,信道容量也跟个位的SNR ,b E 即每个位的式 :便可算出系统的SNR ,使其带宽远大于未作展频调变之原始数据带宽交码有关。

由于Tx 端会采用一组正交码,且该Rx 端也需使用该组正交码,才能解开展频,得讯号不易被干扰与撷取[3],同时也由Shanno 其信道容量也提升了,连带提高了Data Rate[4]量也跟SNR 有关,但在CDMA 中,会先以EN个位的能量,而0N 即噪声的功率频谱密度,其中b f 是Data Rate ,因此若提升0bE N ,则可提升另外,由于原始数据的Chip Rate ,会在展频后大大提升,使得讯号会额外获得增益,进而再提高SNR ,该增益称为处理增益,Processing Gain ,P G()10log()CP R G dB R=R 是原始资料的Chip Rate ,C R 是展频后的Chip Rate ,由[5]可知,R 与C R 分别为12.2Kbps 与3.84Mcps ,带入上式,而得知0bE N 与P G 后,便可算出JM (Jamming Margin) :()10log()10log(bP E JM dB G N =−当然JM 值越大,则表示抗干扰能力越好[3]。