书籍-SD卡规范

- 格式:pdf

- 大小:367.16 KB

- 文档页数:18

作者须知本须知列出了对计算机类图书的著作的基本要求,凡不符合本须知的即视为不合格。

作者在创作稿件时,应按以下流程和要求进行写作。

1、目录和报选题要求在写作之前,作者应先列目录,并填写图书选题申请表(表格见附件),以便出版社进行选题论证。

注意:如果作者对图书选题申请表中要填写的项目不明白,请与策划编辑联系。

一般图书目录都需遵循以下几个原则:➢目录结构合理,遵循读者循序渐进的过程➢目录标题名称主题明晰➢各章节之间的内容不能偏差太大,以免造成各章之间长度失衡➢一般要求细化到三级目录注意:如果是系列丛书,请按照丛书的要求和风格列目录。

2、交稿要求目录经审查通过后,才可开始创作.在写完样章后,请及时与编辑联系,以便编辑及时反馈修改意见,以减少一些常见的错误,例如拷图不规范及术语错语等。

若所写稿件质量太差,则退改,若退改后仍无法通过的,则立即中止后续创作。

作者在最终交稿时应提供以下内容:➢提供全书所有章节的电子文档(包括前言、内容简介、参考文献和附录的内容,以及最新的目录).➢提供全书的图形文件。

图形文件和格式的要求见后。

➢范例类图书,必须提供本书中所涉及的所有实例源文件.➢如果含有彩插页,请提供高清晰的彩插页图。

图形文件和格式的要求见后。

➢如果本书附带光盘,请提供光盘内容.光盘要求见后.注意:如果是手写稿,要求文字书写工整.如果是丛书,还需要提供丛书序。

附:内容简介和前言的基本要求内容简介的总字数不宜过多,一般在200-300字左右,内容包括以下几项:➢本书写作目的和教学目标,或者是软件功能介绍➢本书内容介绍➢本书特色和优点➢本书读者定位前言的内容至少一整页内容,其中要求介绍以下内容:➢本书写作目的和教学目标➢软件功能介绍,或者是该软件的优点及新增功能➢本书内容介绍➢本书特色和优点➢本书读者定位➢参编人员及谦语➢本书约定的内容3、拷图和图形格式要求拷图是写书比较重要的一环,如果不按要求执行,经常会出现工作重复的情况,并且会大大降低图书的质量。

Technical CommitteeSD AssociationRevision HistoryDate Version Changes compared to previous issueOctober, 2001 1.00 Base version initial releaseAugust, 2004 1.10 Incorporated Appendix D items. Added High-Powermode, voltage range clarification, inrush current limitsand more. See Appendix C for full list.Conditions for publicationPublisher and Copyright Holder:SD Association719 San Benito St. Suite CHollister, CA 95023USAPhone: +1 831 636 7322Fax: +1 831 623 2248E-mail: president@/Confidentiality:This document shall be treated as confidential under the Non Disclosure Agreement (NDA), which has been signed by the obtainer. Reproduction in whole or in part is prohibited without prior written permission of SD AssociationExemption:The information contained herein is presented only as a standard specification for SD Card and SD Host products. No responsibility is assumed by SD Association for any damages, any infringements of patents or other right of the third parties, which may result from its use. No license is granted by implication or otherwise under any patent or rights of SD Association or others.Table of Contents1.General Description (1)1.1SDIO features (1)1.2Primary Reference Document (1)1.3Keywords (1)1.4Standard SDIO Functions (2)2.SDIO Signaling Definition (3)2.1SDIO Card Types (3)2.2SDIO Card modes (3)2.2.1SPI (Card mandatory support) (3)2.2.21-bit SD data transfer mode (Card mandatory support) (3)2.2.34-bit SD data transfer mode (mandatory for High-Speed cards, optional for Low-Speed) (3)2.3SDIO Host Modes (3)2.4Signal Pins (4)2.5Host Requirements for SDIO (4)3.SDIO Card Initialization (6)3.1Differences in I/O card initialization (6)3.2The IO_SEND_OP_COND Command (CMD5) (10)3.3The IO_SEND_OP_COND Response (R4) (10)3.4Special Initialization considerations for Combo Cards (12)3.4.1Re-initialize both I/O and Memory (12)3.4.2Using a Combo Card as SDIO only or SD Memory only after Combo Initialization (12)3.4.3Acceptable Commands after Initialization (12)3.4.4Recommendations for RCA after reset (12)3.4.5Enabling CRC in SPI Combo Card (14)4.Differences with SD Memory Specification (15)4.1SDIO Command List (15)4.2Unsupported SD Memory commands (15)4.3Modified R6 Response (16)4.4Reset for SDIO (16)4.5Bus Width (16)4.6Card Detect Resistor (17)4.7Timings (17)4.8Data Transfer Block Sizes (18)4.9Data Transfer Abort (18)4.9.1Read Abort (18)4.9.2Write Abort (18)4.10Changes to SD Memory Fixed Registers (19)4.10.1OCR Register (20)4.10.2CID Register (20)4.10.3CSD Register (20)4.10.4RCA Register (20)4.10.5DSR Register (20)4.10.6SCR Register (20)4.10.7SD Status (20)4.10.8Card Status Register (21)5.New I/O Read/Write Commands (23)5.1IO_RW_DIRECT command (CMD52) (23)5.2IO_RW_DIRECT Response (R5) (24)5.2.1CMD52 Response (SD modes) (24)5.2.2R5, IO_RW_DIRECT Response (SPI mode) (25)5.3IO_RW_EXTENDED command (CMD53) (26)5.3.1CMD53 Data Transfer Format (27)5.3.2Special Timing for CMD53 multi-block read (28)6.SDIO Card Internal Operation (29)6.1Overview (29)6.2Register Access Time (29)6.3Interrupts (29)6.4Suspend/Resume (29)6.5Read Wait (30)6.6CMD52 During Data Transfer (30)6.7SDIO Fixed Internal Map (30)6.8Common I/O Area (CIA) (31)6.9Card Common Control Registers (CCCR) (31)6.10Function Basic Registers (FBR) (38)6.11Card Information Structure (CIS) (40)6.12Multiple Function SDIO Cards (40)6.13Setting Block Size with CMD53 (40)6.14Bus State Diagram (41)7.Embedded I/O Code Storage Area (CSA) (42)7.1CSA Licensing notice (42)7.2CSA Access (42)7.3CSA Data Format (42)8.SDIO Interrupts (43)8.1Interrupt Timing (43)8.1.1SPI and SD 1-bit mode interrupts (43)8.1.2SD 4-bit mode (43)8.1.3Interrupt Period Definition (43)8.1.4Interrupt Period at the Data Block Gap in 4-bit SD Mode (Optional) (45)8.1.5Inhibited Interrupts (Removed Section) (47)8.1.6End of Interrupt Cycles (47)8.1.7Terminated Data Transfer Interrupt Cycle (48)8.1.8Interrupt Clear Timing (49)9.SDIO Suspend/Resume Operation (50)10.SDIO Read Wait Operation (54)11.Power Control (56)11.1Power Control Overview (56)11.2Power Control support for SDIO cards (56)11.2.1Master Power Control (56)11.2.2Power Selection (57)11.2.3High-Power Tuples (57)11.3Power Control Support for the SDIO Host (57)11.3.1Version 1.10 Host (57)11.3.2Power Control Operation (58)12.SDIO Physical Properties (59)12.1SDIO Size (59)12.2Small Form-Factor SDIO (59)12.3Full-Size SDIO Card Package (59)13.SDIO Full-Size Mechanical Extensions (60)13.1Additional ESD/EMI Ground Point (60)13.2Full-Size Extended Case (60)13.3Write Protect Switch (60)14.SDIO Power (62)14.1SDIO Card Initialization Voltages (62)14.2SDIO Power Consumption (62)14.3SDIO Current (62)14.4SDIO Card Operational Voltages (62)15.Inrush Current Limiting (64)15.1Current Limit Design Example (65)16.CIS Formats (66)16.1CIS Reference Document (66)16.2Basic Tuple Format and Tuple Chain Structure (66)16.3Byte Order Within Tuples (66)16.4Tuple Version (67)16.5SDIO Card Metaformat (67)16.6CISTPL_MANFID: Manufacturer Identification String Tuple (68)16.7SDIO Specific extensions (68)16.7.1CISTPL_FUNCID: Function Identification Tuple (68)16.7.2CISTPL_FUNCE: Function Extension Tuple (69)16.7.3CISTPL_FUNCE Tuple for Function 0 (common) (69)16.7.4CISTPL_FUNCE Tuple for Function 1-7 (70)16.7.5CISTPL_SDIO_STD: Function is a Standard SDIO Function (73)16.7.6CISTPL_SDIO_EXT: Tuple Reserved for SDIO Cards (73)17.Abbreviations and Terms (74)A.1 SD and SPI Command List.........................................................................................................................AB.1 Normative References.................................................................................................................................CC.1 Version History............................................................................................................................................DC.2 Version 1.00 to 1.10....................................................................................................................................DD.1 Example SDIO Controller Design................................................................................................................FTable of TablesTable 1 SDIO pin definitions (4)Table 2 OCR values for CMD5 (10)Table 3 Unsupported SD Memory Commands (16)Table 4 R6 response to CMD3 (16)Table 5 SDIO R6 Status Bits (16)Table 6 Combo Card 4-bit Control (17)Table 7 Card Detect Resistor States (17)Table 8 Timing Diagram Symbols (18)Table 9 SDIO Status Register Structure (22)Table 10 Flag data for IO_RW_DIRECT SD Response (25)Table 11 IO_RW_ EXTENDED command Op Code definition (26)Table 12 Byte Count Values (27)Table 13 Card Common Control Registers (CCCR) (32)Table 14 CCCR bit definitions (37)Table 15 Function Basic Information Registers (FBR) (38)Table 16 FBR bit and field definitions (39)Table 17 Card Information Structure (CIS) and reserved area of CIA (40)Table 18 Reference Tuples by Master Power Control and Power Select (57)Table 19 SDIO Full-Size exceptions to SD physical section 8.1 requirements (59)Table 20 Basic Tuple Format (66)Table 21 Tuples Supported by SDIO Cards (67)Table 22 CISTPL_MANFID: Manufacturer Identification Tuple (68)Table 23 CISTPL_FUNCID Tuple (68)Table 24 CISTPL_FUNCE Tuple general structure (69)Table 25 TPLFID_FUNCTION Tuple for Function 0 (common) (69)Table 26 TPLFID_FUNCTION field descriptions for function 0 (common) (70)Table 27 TPLFID_FUNCTION Tuple for Function 1-7 (70)Table 28 TPLFID_FUNCTION field descriptions for functions 1-7 (72)Table 29 TPLFE_FUNCTION_INFO definition (72)Table 30 TPLFE_CSA_PROPERTY definition (72)Table 31 CISTPL_SDIO_STD: Tuple Reserved for SDIO cards (73)Table 32 CISTPL_SDIO_EXT: Tuple Reserved for SDIO Cards (73)Table 33 SD Mode Command List.....................................................................................................................A Table 34 SPI Mode Command List....................................................................................................................BTable of FiguresFigure 1 Signal connection to two 4-bit SDIO cards (4)Figure 2 SDIO response to non-I/O aware initialization (6)Figure 3 Card initialization flow in SD mode (SDIO aware host) (8)Figure 4 Card initialization flow in SPI mode (SDIO aware host) (9)Figure 5 IO_SEND_OP_COND Command (CMD5) (10)Figure 6 Response R4 in SD mode (11)Figure 7 Response R4 in SPI mode (11)Figure 8 Modified R1 Response (11)Figure 9 Re-Initialization flow for I/O Controller (13)Figure 10 Re-Initialization flow for Memory controller (14)Figure 11 I/O Abort during Read Data Transfer (18)Figure 12 I/O Abort during Write CRC Response (Good) (19)Figure 13 I/O Abort during Write CRC Response (Bad) (19)Figure 14 I/O Abort after Write CRC Response (19)Figure 15 IO_RW_DIRECT Command (23)Figure 16 R5 IO_RW_DIRECT Response (SD modes) (24)Figure 17 IO_RW_DIRECT Response in SPI Mode (26)Figure 18 IO_RW_EXTENDED Command (26)Figure 19 Multi-Block Read Timing (28)Figure 20 SDIO Internal Map (31)Figure 21 State Diagram for Bus State Machine (41)Figure 22 Read Interrupt Cycle Timing (44)Figure 23 Alternate Read Interrupt Cycle Timing (44)Figure 24 Write Interrupt Cycle Timing (45)Figure 25 Continuous Interrupt Cycle (45)Figure 26 Multiple Block 4-Bit Read Interrupt Cycle Timing (46)Figure 27 Multiple Block 4-Bit Write Interrupt Cycle Timing (47)Figure 28 Interrupt Cycle Timing (47)Figure 29 Alternate Interrupt Cycle Timing (48)Figure 30 Terminated Read Multiple Interrupt timing (Case 1) (48)Figure 31 Terminated Read Multiple Interrupt timing (Case 2) (49)Figure 32 Card with long read latency shall accept bus suspend (50)Figure 33 Function2 read cycle inserted during Function1 multiple read cycle (50)Figure 34 Write suspended during busy (case 1) (51)Figure 35 Write suspended during busy (case 2) (51)Figure 36 Relationship between Interrupt Period and Suspend/Resume (case 1) (52)Figure 37 Relationship between Interrupt Period and Suspend/Resume (case 2) (52)Figure 38 Suspend/Resume timing (53)Figure 39 Read wait control by stopping SDCLK (54)Figure 40 Read wait delay using DAT[2] (54)Figure 41 SDIO Card DAT[2] Drive Timing for Read Wait (55)Figure 42 Full-Size SDIO Mechanical Extensions (61)Figure 43 SDIO Inrush Current (65)Figure 44 Changes from version 1.00 to 1.10....................................................................................................D Figure 45 SDIO Internal State Machine example..............................................................................................F Figure 46 State Diagram for Function State Machine........................................................................................G1. GeneralDescriptionThe SDIO (SD Input/Output) card is based on and compatible with the SD memory card. This compatibility includes mechanical, electrical, power, signaling and software. The intent of the SDIO card is to provide high-speed data I/O with low power consumption for mobile electronic devices. A primary goal is that an SDIO card inserted into a non-SDIO aware host shall cause no physical damage or disruption of that host or it’s software. In this case, the SDIO card should simply be ignored. Once inserted into an SDIO aware host, the detection of the card proceeds via the normal means described in this specification with some extensions. In this state, the SDIO card is idle and draws a small amount of power (15 mA averaged over 1 second). During the normal initialization and interrogation of the card by the host, the card identifies itself as an SDIO card. The host software then obtains the card information in a tuple (linked list) format and determines if that card’s I/O function(s) are acceptable to activate. This decision is based on such parameters as power requirements or the availability of appropriate software drivers. If the card is acceptable, it is allowed to power up fully and start the I/O function(s) built into it.features1.1 SDIOz Targeted for portable and stationary applicationsz Minimal or no modification to SD Physical bus is requiredz Minimal change to memory driver softwarez Extended physical form factor available for specialized applicationsz Plug and play (PnP) supportz Multi-function support including multiple I/O and combined I/O and memoryz Up to 7 I/O functions plus one memory supported on one card.z Allows card to interrupt hostz Initialization Voltage: 2.0 to 3.6Vz Operational Voltage range:z Standard: 2.7 – 3.6Vz Minimal: 3.1 – 3.5Vz Application Specifications for Standard SDIO Functions.1.2 PrimaryDocumentReferenceThis specification is based on and refers extensively to the SDA document:SD Memory Card SpecificationsPart 1PHYSICAL LAYER SPECIFICATIONSeptember 2000Version 1.01The reader is directed to this document for more information on the basic operation of SD cards. In addition, other documents are referenced in this specification. A complete list can be found in appendix B.1.1.3 KeywordsAs used in this documents "shall", "should", "may" and "can" are defined as follows:shall - used to indicate mandatory itemsshould - used to indicated a recommended itemmay - used to indicate something that is permissiblecan - used for statements of possibility and capabilityFunctionsSDIO1.4 StandardAssociated with the base SDIO specification, there are several Application Specifications for Standard SDIO Functions. These common functions such as cameras, Bluetooth cards and GPS receivers have a standard register interface, a common operation method and a standard CIS extension. Implementation of the standard interfaces are optional for any card vendor, but compliance with the standard allows the use of standard drivers and applications which will increase the appeal of these cards to the consumer. Full information on these standard interfaces can be found in the Application Specifications for Standard SDIO Functions maintained by the SDA.2. SDIO Signaling DefinitionTypes2.1 SDIOCardThis specification defines two types of SDIO cards. The Full-Speed card supports SPI, 1-bit SD and the 4-bit SD transfer modes at the full clock range of 0-25MHz. The Full-Speed SDIO cards have a data transfer rate of over 100 Mb/second (10 MB/Sec). A second version of the SDIO card is the Low-Speed SDIO card. This card requires only the SPI and 1-bit SD transfer modes. 4-bit support is optional. In addition, Low-Speed SDIO cards shall support a full clock range of 0-400 KHz. The intended use of Low-Speed cards is to support low-speed I/O capabilities with a minimum of hardware. The Low-Speed cards support such functions as modems, bar-code scanners, GPS receivers etc. If a card is a ‘Combo card’ (memory plus SDIO) then Full-Speed and 4-bit operation is mandatory for both the memory and SDIO portions of the card.Cardmodes2.2 SDIOThere are 3 signaling modes defined for SD Physical Specification Version 1.01 memory cards that also apply to SDIO Card:2.2.1 SPI (Card mandatory support)The SPI bus topology is defined in section 3.1.2 and the protocol is defined in sections 3.2.2 and 7 of the SD Physical Specification Version 1.01. In this mode pin 8, which is undefined for memory, is used as the interrupt pin. All other pins and signaling protocols are identical to the SD Physical Specification Version1.01.2.2.2 1-bit SD data transfer mode (Card mandatory support)This mode is identical to the 1 data bit (narrow) mode defined for SD Memory in section 3.2.1 of the SD Physical Specification Version 1.01. In this mode, data is transferred on the DAT[0] pin only. In this mode pin 8, which is undefined for memory, is used as the interrupt pin. All other pins and signaling protocols are identical to the SD Memory specification.2.2.3 4-bit SD data transfer mode (mandatory for High-Speed cards, optional for Low-Speed)This mode is identical to the 4 data bit mode (wide) defined for SD Memory in section 3.2.1 of the SD Physical Specification Version 1.01. In this mode, data is transferred on all 4 data pins (DAT[3:0]). In this mode the interrupt pin is not available for exclusive use as it is utilized as a data transfer line. Thus, if the interrupt function is required, a special timing is required to provide interrupts. See section 8.1.2 for details of this operation. The 4-bit SD mode provides the highest data transfer possible, up to 100 Mb/sec.HostModes2.3 SDIOIf a SDIO aware host supports the SD transfer mode, it is recommended that both the 1-bit and 4-bit modes be supported. While a SDIO host that supports only the 4-bit transfer mode is possible, its performance with a Low-Speed SDIO card may be reduced. This is because the only means to transfer data to and from a Low-Speed card would be the single byte per command transfer (using the IO_RW_DIRECT command (CMD52) see 5.1).2.4 Signal PinsFigure 1 Signal connection to two 4-bit SDIO cardsPin SD 4-bit mode SD 1-bit mode SPI mode 1 CD/DAT[3] Data line 3 N/C Not Used CS Card Select 2 CMD Command line CMD Command line DI Data input 3 VSS1 Ground VSS1 Ground VSS1 Ground 4 VDD Supply voltage VDD Supply voltage VDD Supply voltage 5 CLK Clock CLK Clock SCLK Clock 6 VSS2 Ground VSS2 Ground VSS2 Ground 7 DAT[0] Data line 0 DATA Data line DO Data output 8 DAT[1] Data line 1 or Interrupt (optional)IRQ Interrupt IRQ Interrupt9 DAT[2] Data line 2 or Read Wait (optional)RW Read Wait (optional) NC Not UsedTable 1 SDIO pin definitionsIt is recommended that multi-slot hosts intending to support SDIO (SDIO aware) provide a separate CLK to each slot, to allow the I/O cards to be placed in a low power state on a slot-by-slot basis. After reset, all data lines (DAT[3:0]) shall be in the hi-Z state on both the host and card(s) to avoid bus conflict. Access to the Bus Interface Control register within the CCCR (Table 13) determines DAT line mode.2.5 Host Requirements for SDIOIn order for a host to completely support all of the capabilities of the SDIO cards, some signal connections should be supported. In order to support interrupts, the host should have Pin 8 connected from the card to the host in order to provide interrupt signaling. This is true even if the host only supports the SPI or 1 bit SD mode. In addition, if the host supports more than 1 card in either SD mode, the CMD and all 4 data lines (DAT[3:0]) should not be bussed together, but rather routed separately to the host. This allows the mixing of card types in the different sockets without interference. Both the SD Physical Specification and the SDIO Specification support the concept of “unifying” (connecting together) the CMD lines in a multi-slot system after initialization.In addition, there some additional design details that the designer of a host intending to support SDIO cards must be aware of:placed on the DAT[3:1] lines. Those conditions are:1) During a multiple block write:According to the SD Physical Specification Version 1.01 figures 9 and 28, the DAT[3:1] lines are described as “don’t care” (X) during the CRC status period. If a host actively drives these lines during this period, it may interfere with interrupt signaling from an SDIO card. In order to prevent this conflict, if a host supports interrupts during 4-bit data transfers, it shall not drive DAT[3:1] during this period (hi-Z rather than don’t care.)2) During a multiple block read:According to the SD Physical Specification Version 1.01 figure 26, the DAT[1] line is described as “P” (one cycle pull-up) between read data packets. In order to support interrupts during the 4-bit mode, the host shall not drive the DAT[1] line during the 2 clock Interrupt Period defined in section 8.1.2InitializationCard3. SDIO3.1 Differences in I/O card initializationA requirement for the SDIO specification is that an SDIO card shall not cause non-I/O aware hosts to fail when inserted. In order to prevent operation of I/O functions in non-I/O aware hosts, a change to the SD card identification mode flowchart is needed. A new command (IO_SEND_OP_COND, CMD5) is added to replace the ACMD41 for SDIO initialization by I/O aware hosts (see 3.2).After reset or power-up, all I/O functions on the card are disabled and the I/O portion of the card shall not execute any operation except CMD5 or CMD0 with CS=low. If there is SD memory installed on the card (also called a combo card), that memory shall respond normally to all normal mandatory memory commands.An I/O only card shall not respond to the ACMD41 and thus appear initially as an MMC card (See appendix B.1 for information on the MMC specification). The I/O only card shall also not respond to the CMD1 used to initialize the MMC cards and appear as a non-responsive card. The host then gives up and disables this card. Thus, the non-aware host receives no response from an I/O only card and force it to the inactive state. The operation of an I/O card with a non-I/O aware host is shown in Figure 2. Note that the solid lines are the actual paths taken while the dashed lines are not executed.Figure 2 SDIO response to non-I/O aware initializationAn SDIO aware host sends CMD5 prior to the CMD55/ACMD41 pair, and thus would receive a valid OCR in the R4 response to CMD5 and continue to initialize the card. Figure 3 shows the operation of an SDIO aware host operating in the SD modes and Figure 4 shows the same operation for a host that operates in the SPI mode.If the I/O portion of a card has received no CMD5, the I/O section remains inactive and shall not respond to any command except CMD5. A combo card stays in the memory-only mode. If no memory is installed on the card (i.e. an I/O only card in a non-SDIO aware host) the card would not respond to any memory command. This satisfies the condition where a user uses some I/O function on the card such as Ethernet to load a music file to the memory function of that card. The card is then removed and inserted into a non-SDIO aware host. That host would not enable the I/O function (no CMD5) so would appear to the player as a memory-only card. If the host were I/O aware, it would send the CMD5 to the card and the card would respond with R4. The host reads that R4 value and knows the number of available I/O functions and about the existence of any SD memory. After the host has initialized the I/O portion of the card, it then reads the Common Information Area (CIA) of the card (see 6.8). This is done by issuing a read command, starting with the byte at address 0x00, of I/O function 0. The CIA contains the Card Common Control Registers (CCCR) and the Function Basic Registers (FBR). Also included in the CIA are pointers to the card’s common Card Information Structure (CIS) and each individual function’s CIS. The CIS structure is defined in section 16. The CIS includes information on power, function, manufacturer and other things the host needs to determine if the I/O function(s) is appropriate to power-up. If the host determines that the card should be activated, a register in the CCCR area enables the card and each individual function. At this time, all functions of the I/O card are fully available. In addition, the host can control the power consumption and enable/disable interrupts on a function-by-function basis. This access to I/O does not interfere with memory access to the card if present.Combo Cards can accept CMD15 with RCA=0000, as described in Figure 3, but there is an exception for SD memory only cards. Memory only cards require a non-zero RCA before the host may issue CMD15. Thus, CMD15 shall be issued after CMD3 in the Standby state. In the case of ACMD41, it shall accept RCA=0x0000. As shown in Figure 3 and Figure 4, an SDIO aware host shall send CMD5 arg=0 as part of the initialization sequence after either Power On or a CMD 52 with write to I/O Reset. Sending CMD5 arg=0 that has not been preceded by one of these two reset conditions shall not result in either the host or card entering the initialization sequence.IO=1, MEM=0IO=1, MEM=1MP=0, IO=0Start initialization with CMD0, CMD1IO=0, MEM=1IO=0, MEM=0 Start initialization with CMD0 and CMD13.2 The IO_SEND_OP_COND Command (CMD5)Figure 5 shows the format of the IO_SEND_OP_COND command (CMD5). The function of CMD5 for SDIO cards is similar to the operation of ACMD41 for SD memory cards. It is used to inquire about the voltage range needed by the I/O card. The normal response to CMD5 is R4 in either SD or SPI format. The R4 response in SD mode is shown in Figure 6 and the SPI version is shown in Figure 7.S D Command Index000101b StuffBitsI/O OCR CRC7 E1 1 6 8 24 7 1Figure 5 IO_SEND_OP_COND Command (CMD5)The IO_SEND_OP_COND Command contains the following fields:S(tart bit): Start bit. Always 0D(irection): Direction. Always1 indicates transfer from host to card.Command Index: Identifies the CMD5 command with a value of 000101bStuff Bits: Not used, shall be set to 0.I/O OCR: Operation Conditions Register. The supported minimum and maximum valuesfor VDD. The layout of the OCR is shown in Table 2. See section 4.10.1 foradditional information.CRC7: 7 bits of CRC dataE(nd bit): End bit, always 1I/O OCR bit position VDD voltage window(in Volts)0-3 Reserved4 Reserved5 Reserved6 Reserved7 Reserved8 2.0-2.19 2.1-2.210 2.2-2.311 2.3-2.412 2.4-2.513 2.5-2.614 2.6-2.715 2.7-2.816 2.8-2.917 2.9-3.018 3.0-3.119 3.1-3.220 3.2-3.321 3.3-3.422 3.4-3.523 3.5-3.6Table 2 OCR values for CMD53.3 The IO_SEND_OP_COND Response (R4)An SDIO card receiving CMD5 shall respond with a SDIO unique response, R4. The format of R4 for both the SD and SPI modes is:S D Reserved C Number of I/O functionsMemory Present StuffBitsI/O OCR Reserved E 1 1 6 1 3 1 3 24 7 1Figure 6 Response R4 in SD modeModifiedR1C Numberof I/O functionsMemory PresentStuff BitsI/O OCR8 1 3 1 3 24Figure 7 Response R4 in SPI modeThe Response, R4 contains the following data:S(tart bit): Start bit. Always 0 D(irection): Direction. Always 0. Indicates transfer from card to host. Reserved: Bits reserved for future use. These bits shall be set to 1. C: Set to 1 if Card is ready to operate after initializationI/O OCR:Operation Conditions Register. The supported minimum and maximum values for VDD. The layout of the OCR is shown in Table 2. See section 4.10.1 for additional information.Memory Present: Set to 1 if the card also contains SD memory. Set to 0 if the card is I/O only.Number of I/O Functions: Indicates the total number of I/O functions supported by this card. The range is 0-7.Note that the common area present on all I/O cards at Function 0 is not included in this count. The I/O functions shall be implemented sequentially beginning at function 1.Modified R1: The SPI R1 response byte as described in Fig 47 of the SD Physical SpecificationVersion 1.01 modified for I/O as follows:Figure 8 Modified R1 ResponseStuff Bits:Not used, shall be set to 0.1 = in idle state RFU (always 0)1 = illegal command 1 = COM CRC error1 = Function number error RFU (always 0)1 = parameter errorStart Bit (always 0)。

档案书籍整理制度范本第一条总则为了加强档案书籍的管理,提高档案书籍的利用效率,确保档案书籍的完整性和准确性,特制定本制度。

本制度适用于公司、企事业单位、社会团体等单位的档案书籍整理工作。

第二条档案书籍的定义本制度所称档案书籍,是指各单位在各项工作中形成的、具有保存价值的文字、图表、照片、录音、录像等各种形式的文件材料。

第三条档案书籍的管理原则档案书籍管理应遵循以下原则:(一)依法管理原则:遵守国家有关档案管理的法律法规,确保档案书籍的合法性、合规性。

(二)真实性原则:确保档案书籍的内容真实、准确,反映单位各项工作的实际情况。

(三)完整性原则:确保档案书籍的收集、整理、保管、利用等环节各项工作完整无缺。

(四)安全性原则:确保档案书籍的安全,防止档案书籍的损毁、丢失、泄密等风险。

第四条档案书籍的管理机构各单位应设立档案管理部门,负责档案书籍的管理工作。

档案管理部门的主要职责如下:(一)制定档案书籍的管理规章制度。

(二)组织、指导、监督档案书籍的收集、整理、保管、利用等工作。

(三)负责档案书籍的分类、归档、编目、登记等工作。

(四)负责档案书籍的保管、维护、修复等工作。

(五)负责档案书籍的查询、借阅、复制等工作。

(六)负责档案书籍的安全、保密等工作。

第五条档案书籍的收集与整理(一)档案书籍的收集1. 各单位各部门应按照档案管理部门的要求,及时将形成的具有保存价值的文件材料收集、整理后交档案管理部门。

2. 档案管理部门应定期对各部门的档案书籍进行审核、验收,确保档案书籍的完整性、准确性。

(二)档案书籍的整理1. 档案管理部门应按照档案书籍的性质、形成时间、类别等原则对档案书籍进行整理。

2. 档案管理部门应编制档案书籍的分类目录、索引等检索工具,便于查询利用。

第六条档案书籍的保管与利用(一)档案管理部门应建立健全档案书籍的保管制度,确保档案书籍的安全、保密。

1. 档案书籍应存放在符合防火、防盗、防潮、防虫、防霉、防光、防尘等要求的专用库房内。

Micro-Sized Secure Digital CardGByte, 2GByte and 4GByte主要描述MicroSD 卡是把有序和随机的存取能力高度结合的闪存卡.通过专用的串行接口有效地进行快速和可靠的数据传输.这个接口允许几种卡通过连接外部装置直接应用. 这些MicroSD 卡是完全兼容一些新的消费标准的.在MicroSD 卡的系统描述中会有MicroSD 卡系统标准的定义.MicroSD 卡系统是基于半导体技术革新上的大容量存储系统.它已经发展成为了一种应用于多媒体消费类产品廉价,结实的存储介质.MicroSD 卡适适用于那些廉价的播放器和驱动器的设计,不用移动任何一个部分.耗电量低,宽电压范围支持移动,电池电源.可用于音频播放器,万用笔记本,掌上电脑,电子书,电子百科全书,电子词典.用于非常有效的数据压缩方案.比如:MPEG 格式, MicroSD 卡将为多媒体数据的传输提供足够的容量.要特性- 容量: 128MB/256MB/512MB. - 兼容MicroSD 卡2.0版本规格 - 物理层的规范第一部分是2.0版本. (功能, 电子特性, Registers) -卡内错误自动纠正-电压传输范围: 2.7~3.6V . -耗电量较低:自动开关电源, 自动的管理电源. - 不要求额外的运行电压.-充电时插入或移除卡都不会造成毁坏l. -数据张力: 100k 写入/擦除 周期. -便于终端客户处理 - 可信赖的电子结构- 支持文本信息和图像- 面积: 11mm(W)x15mm(L). - 厚度 跨连接区7mm, 卡的厚度.95mm.- MICROSD 卡的插槽可以连接适配器用图像1. MICROSD 卡的格式Table 1. 产品清单深圳市威胜科技有限公司MICROSDTable 2. 产品明细(特征值)Parameter Range1GB 2GB 4GB记忆容量1024MB 2048MB 4096MB写入速度5MB/S 5MB/s 6MB/s读取速度10MB/S 15MB/s 15MB/s待机电流60 uA 60 uA 60 uA操作电流55mA 55 mA 55 mA平均故障间隔时间1,000,000 hours张力10,000 插入/移除周期控制器SK6612控制器明细SK6612 Data Sheet v105.pdfTable 3. 操作环境参数范围温度操作模式-25 ~ 65℃存储模式- 40 ~ 85℃湿度操作模式8% to 95%,非冷凝存储模式8% to 95%,非冷凝深圳市威胜科技有限公司MICROSD Figure 2. 物理结构图Bottom View深圳市威胜科技有限公司MICROSDTop View深圳市威胜科技有限公司MICROSD。

图书建档管理制度一、总则为规范图书建档工作,提高图书档案管理效率,保障图书资源的正常利用和管理。

特制定本制度。

二、建档管理范围本制度适用于所有单位内部的图书建档工作,包括订购、收集、整理、编目、分类、编号等所有环节。

三、建档管理机构单位图书建档管理机构设立在图书馆或档案管理部门,负责具体的建档工作。

图书建档管理员由专业人员担任。

四、建档管理流程1. 订购阶段:在订购图书时,应向图书建档管理员提交书名、作者、出版社等相关信息,以便建档。

2. 收集阶段:收到新书后,建档管理员应及时进行验收,确认书籍信息无误后进行建档处理。

3. 整理阶段:对收到的图书进行整理、装订,确保图书质量完好。

4. 编目阶段:建档管理员应对图书进行分类编目,便于读者查找和管理。

5. 分类阶段:根据图书的内容和特点,将图书进行分类放置,避免混乱。

6. 编号阶段:对每本图书进行编号,建立起图书的独立标识,方便管理和检索。

五、建档管理原则1. 一书一档:每本图书应建立相应的档案,内容包括书名、作者、出版社、索书号等信息。

2. 信息准确:建档信息应准确无误,确保用户能够准确、方便地查找到所需图书。

3. 分类有序:对不同类型的图书进行合理分类,便于读者根据自身需求查找所需图书。

4. 管理规范:建档工作应按照规定流程和标准进行,不得擅自更改或篡改档案信息。

5. 定期维护:建档管理员应定期检查、修正档案信息,确保信息的及时性和准确性。

六、建档管理责任1. 图书建档管理员应认真负责地履行建档工作,保证图书档案信息的完整性和准确性。

2. 部门负责人应对建档工作进行监督,确保工作流程的顺利进行。

3. 任何单位内部工作人员不得私自动用图书档案信息,违者将受到相应处罚。

七、建档管理效果评估单位应定期对图书建档工作进行评估,检查建档信息的完整性和准确性,及时发现问题并予以解决。

以上为图书建档管理制度,单位内部应严格执行,确保图书资源得到有效管理和利用。

SD卡接口规范的完整翻译特性:◎容量:32MB/64MB/128MB/256MB/512MB/1GByte◎兼容规范版本1.01◎卡上错误校正◎支持CPRM◎两个可选的通信协议:SD模式和SPI模式◎可变时钟频率0-25MHz◎通信电压范围:2.0-3.6V工作电压范围:2.0-3.6V◎低电压消耗:自动断电及自动睡醒,智能电源管理◎无需额外编程电压◎卡片带电插拔保护◎正向兼容MMC卡◎高速串行接口带随即存取---支持双通道闪存交叉存取---快写技术:一个低成本的方案,能够超高速闪存访问和高可靠数据存储---最大读写速率:10Mbyte/s◎最大10个堆叠的卡(20MHz,Vcc=2.7-3.6V)◎数据寿命:10万次编程/擦除◎CE和FCC认证◎PIP封装技术◎尺寸:24mm宽×32mm长×1.44mm厚说明:本SD卡高度集成闪存,具备串行和随机存取能力。

可以通过专用优化速度的串行接口访问,数据传输可靠。

接口允许几个卡垛叠,通过他们的外部连接。

接口完全符合最新的消费者标准,叫做SD卡系统标准,由SD卡系统规范定义。

SD卡系统是一个新的大容量存储系统,基于半导体技术的变革。

它的出现,提供了一个便宜的、结实的卡片式的存储媒介,为了消费多媒体应用。

SD卡可以设计出便宜的播放器和驱动器而没有可移动的部分。

一个低耗电和广供电电压的可以满足移动电话、电池应用比如音乐播放器、个人管理器、掌上电脑、电子书、电子百科全书、电子词典等等。

使用非常有效的数据压缩比如MPEG,SD卡可以提供足够的容量来应付多媒体数据。

框图:SD卡上所有单元由内部时钟发生器提供时钟。

接口驱动单元同步外部时钟的DAT和CMD信号到内部所用时钟。

本卡由6线SD卡接口控制,包括:CMD,CLK,DAT0-DAT3。

SD卡接口的完整规范(二)faceoff 发表于2006-8-11 20:12:00回复从该CMD线上串行传输。

学校图书馆数字资源服务规范学校图书馆是学生学习的重要场所,为了更好地满足学生的学习需求,图书馆采取了数字资源服务的方式,提供更丰富的学习资料。

本文将就学校图书馆数字资源服务的规范进行探讨。

一、数字资源的分类数字资源主要包括电子书籍、期刊、数据库以及学术论文等。

学校图书馆需要根据学生的需求,选择合适的数字资源进行采购和订阅,以满足学生不同学科的学习需求。

二、数字资源的采购学校图书馆应建立专门的数字资源采购渠道,通过和出版社、数据库供应商等合作,获取最新的数字资源。

采购时需要考虑资源的可靠性、稳定性和版权问题,确保使用的数字资源真实可信。

三、数字资源的整理与分类图书馆需要对采购的数字资源进行整理和分类,建立清晰的分类体系和检索系统,方便学生进行搜索和获取所需资料。

数字资源的整理和分类需要符合学科知识结构和学生的学习需求。

四、数字资源的存储与保管图书馆应建立完善的数字资源存储和保管系统,保证数字资源的安全性和可靠性。

图书馆应定期备份数字资源,以防止数据丢失或被破坏。

同时,还需要设置权限控制,确保只有注册用户能够访问数字资源。

五、数字资源的开放与共享学校图书馆应鼓励数字资源的开放与共享,与其他图书馆和教育机构建立合作关系,互相借阅和共享数字资源。

这样可以更好地提高资源的利用率,让更多的学生受益于数字资源服务。

六、数字资源的合理利用学生应充分利用图书馆提供的数字资源,遵守使用规范,不得私自下载和传播数字资源。

同时,学生还应学会合理利用数字资源,不仅要注重获取资料的数量,更要注重获取的质量和深度。

七、数字资源的培训与指导学校图书馆应定期组织数字资源的培训和指导活动,向学生介绍如何有效地使用数字资源,提高学生的信息素养和查询能力。

同时,图书馆还可以提供个性化的学习指导,帮助学生更好地利用数字资源进行学习。

八、数字资源服务的反馈与改进图书馆应倾听学生的意见与建议,建立反馈渠道,并及时反馈和解决学生遇到的问题。

如果学生对某个数字资源服务不满意,图书馆需要及时进行改进,提高数字资源服务的质量和效率。

图书规范管理制度一、总则为了加强图书管理工作,提高图书馆服务质量,保障读者的合法权益,制定本规程。

二、图书管理范围本制度适用于图书馆内所收藏的所有图书资料。

三、图书馆开馆时间1. 图书馆的开馆时间为每天8:00-22:00,特殊情况须提前申请批准。

2. 晚间开馆时间须提前申请,在安全保障和服务质量的前提下,尽量满足读者的需求。

四、借还书规定1. 借书证是读者借阅图书的凭据,未经借书证的读者不得借阅图书。

2. 读者办理借书证需提供身份证明和一寸照片,遗失或损坏需重新办理。

3. 借书证仅限本人使用,不得转借他人。

4. 借书期限为30天,逾期需缴纳一定的滞纳金。

5. 当读者需要延期归还图书时,应提前通知图书馆并缴纳相应的续借费用。

6. 图书丢失或损坏,读者需按照图书价格的一定比例进行赔偿。

五、阅览规定1. 在图书馆内阅读图书时,应注意保持安静,不得大声喧哗。

2. 不得擅自调换图书位置,应按照分类顺序归还。

3. 禁止在图书馆内吸烟、进食,携带宠物。

4. 禁止在图书馆内进行商业活动,如广告推销等。

六、图书馆秩序1. 所有读者应当遵守图书馆的秩序,不得有任何扰乱馆内秩序的行为。

2. 不得恶意破坏图书馆设施和设备,如有损坏需按照市价赔偿。

3. 在图书馆内发生纠纷或争执时,应当配合工作人员进行处理,不得进行人身攻击或动手行为。

4. 如有大规模活动需要使用图书馆场地,需提前预约和申请。

七、对违规行为的处理1. 对于严重违反规定的读者,图书馆有权暂停其借书和阅读权利,甚至终止其借书证。

2. 如有损坏设施或设备行为,图书馆有权向相关部门报警处理。

3. 对于情节严重的违规者,图书馆有权采取法律措施。

八、附则1. 本规定由图书馆管理委员会负责解释。

2. 本规定自发布之日起生效。

以上为图书规范管理制度内容,图书馆管理人员及读者须遵守执行,如有违反,依规定进行处理。

制定单位:XXX图书馆日期:XXXX年XX月XX日。

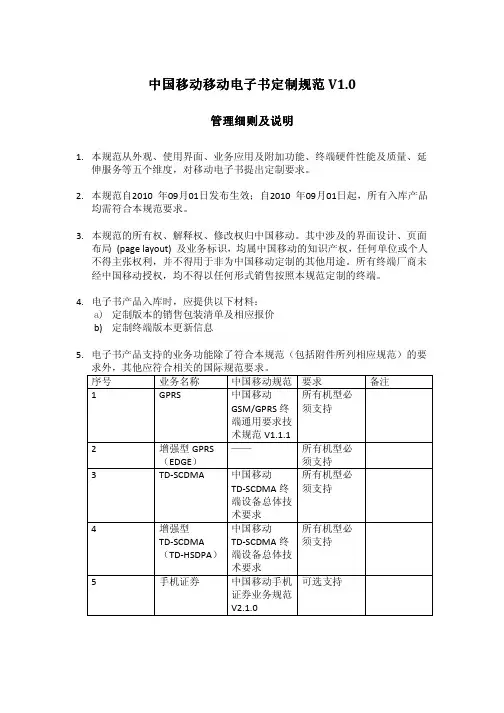

中国移动中国移动移动电子书移动电子书移动电子书定制规范定制规范V1.0管理细则及说明1. 本规范从外观、使用界面、业务应用及附加功能、终端硬件性能及质量、延伸服务等五个维度,对移动电子书提出定制要求。

2. 本规范自2010 年09月01日发布生效;自2010 年09月01日起,所有入库产品均需符合本规范要求。

3. 本规范的所有权、解释权、修改权归中国移动。

其中涉及的界面设计、页面布局 (page layout) 及业务标识,均属中国移动的知识产权,任何单位或个人不得主张权利,并不得用于非为中国移动定制的其他用途。

所有终端厂商未经中国移动授权,均不得以任何形式销售按照本规范定制的终端。

4. 电子书产品入库时,应提供以下材料:a) 定制版本的销售包装清单及相应报价 b) 定制终端版本更新信息5. 电子书产品支持的业务功能除了符合本规范(包括附件所列相应规范)的要求外,其他应符合相关的国际规范要求。

序号 业务名称 中国移动规范 要求 备注 1 GPRS 中国移动GSM/GPRS 终端通用要求技术规范V1.1.1所有机型必须支持 2 增强型GPRS (EDGE ) —— 所有机型必须支持3 TD-SCDMA 中国移动TD-SCDMA 终端设备总体技术要求所有机型必须支持 4 增强型TD-SCDMA (TD-HSDPA ) 中国移动TD-SCDMA 终端设备总体技术要求所有机型必须支持 5 手机证券 中国移动手机证券业务规范V2.1.0可选支持6.按照电子书终端屏幕是否支持手写功能,将电子书分为2类,分别为:A:支持手写功能B:不支持手写功能7.规范的主要缩略语M:必须。

表示电子书定制产品必须支持此要求。

O:可选。

表示电子书定制产品可选支持此要求。

第一部分第一部分::外观感受(一)品牌呈现终端类型 序号要求A B 1.1.1原则上机身正面上仅印制G3标志,厂家的标志与“CHINA MOBILE ”印制在机身背后。

书目的卡片格式

书目的卡片格式是指在图书馆或书店中为每一本书准备的一张

信息卡片,通常包含以下内容:

1. 书名:书的正式名称,注意大小写和标点符号的正确使用。

2. 作者:书的作者或编者,按照姓氏和名字的顺序排列。

3. 出版社:书的出版社名称和地址,以及出版日期,通常以年份为单位。

4. 页数:书的总页数,包括前言、目录、正文、附录、参考文献等。

5. ISBN号:国际标准书号,是一种全球唯一的书籍识别号码,方便图书馆、书店等进行管理和查询。

6. 分类号:根据《中国图书馆分类法》进行分类,方便读者查找和归还。

7. 索书号:根据图书馆的分馆和馆藏情况分配的标识号码,方便读者查找和借阅。

8. 图书简介:对书籍的简短介绍,包括主题、内容、特点等。

9. 读者评价:读者对该书的评价或评论,有助于其他读者选择和阅读。

书目的卡片格式应当简洁明了、排版整齐、信息准确完整,方便读者快速获取所需信息。

- 1 -。

SD存储卡规范第一部分:物理层规范V1.01的简化版本1.概述 (2)2.系统特性 (2)3.SD存储卡的系统概念 (3)3.1 总线拓扑结构 (4)3.2 总线协议 (6)3.3 SD存储卡的引脚与寄存器 (10)3.4 与多媒体卡兼容 (11)4.SD存储卡的功能介绍 (14)5.卡的寄存器 (14)6.SD存储卡的硬件接口 (14)7.SPI模式 (14)8.SD存储卡的机械规范 (14)8.1 卡的外壳 (14)8.2 机械外形参数 (16)8.3 系统:卡和连接器 (19)8.4 薄(1.44mm)SD存储卡 (19)9.附录 (21)10.缩写和术语 (21)1.概述SD存储卡(Secure Digital Memory Card)是特别为符合新出现的音频和视频消费电子设备的安全性、容量、性能和环境等要求而设计的一种存储卡。

SD 存储卡包含符合SDMI标准安全性的版权保护机制,速度更快而且存储容量更大。

SD存储卡的安全系统使用双方认证和“新的密码算法”技术,防止卡的内容被非法使用。

它还提供了一种无安全性的访问方法访问用户自己的内容。

SD 存储卡的物理外形、引脚分配和数据传输协议都向前兼容多媒体卡(MultiMediaCard),但也增加了一些内容。

SD存储卡的通信基于一个高级的9引脚接口(时钟、命令、4条数据线和3条电源线),可以在最高25MHz频率和低电压范围内工作。

通信协议也是本规范的一部分。

SD存储卡的主机接口也支持常规的多媒体卡操作。

也就是说向前兼容多媒体卡。

实际上,SD存储卡和多媒体卡的主要区别在初始化过程。

SD存储卡规范共有几个文档,其文档结构图如图1所示。

SD存储卡安全规范音频规范文件系统规范SD存储卡物理层规范(本文档)其他应用文档图1 SD存储卡文档结构•SD存储卡音频规范这个规范以及其他规范介绍了某些应用(这里是音频应用)的规范以及实现要求。

•SD存储卡文件系统规范介绍了保存在SD存储卡中的数据的文件格式结构规范(包括有保护和无保护方面)。

1.概述SD存储卡(Secure Digital Memory Card)是特别为符合新出现的音频和视频消费电子设备的安全性、容量、性能和环境等要湂而设计的一种存储卡。

SD存储卡包含符合SDMI标准安全性的版权保护机制,速度更快而且存储容量更大。

SD存储卡的安全绻统使用双方认证和“新的密码算滕”技术,防止卡的内容被非滕使用。

它还提供了一种无安全性的访问方滕访问用户自己的内容。

SD存储卡的物理外形、引脚分配和数据传输协议都向前兼容多媒体卡(MultiMediaCard),但也增加了一些内容。

SD存储卡的通信基于一个高级的9引脚接口(时钟、命令、4条数据线和3条电源线),可以在最高25MHz频率和低电压范围内工作。

通信协议也是本规范的一部分。

SD存储卡的主机接口也支持常规的多媒体卡操作。

也帱是说向前兼容多媒体卡。

实际上,SD存储卡和多媒体卡的主要区别在初始化过程。

SD存储卡规范共有几个文档,其文档结构图如图1所示。

·SD存储卡音频规范这个规范以及其他规范介绍了某些应用(这里是音频应用)的规范以及实现要湂。

·SD存储卡文件绻统规范介绍了保存在SD存储卡中的数据的文件格式结构规范(包括有保护和无保护方面)。

·SD存储卡安全规范介绍了版权保护机制以及支持的应用专用命令。

·SD存储卡物理幂规范(本规范)介绍了SD存储卡使用的物理接口和命令协议。

本规范的目的是定义SD存储卡的环境和操作。

本文档分几个部分,第三章概述了绻统的概念。

一般的SD存储卡特性在第四章介绍。

由于这里定义了卡的所有幞性,我们建议同时参考产品文档。

卡的寄存器在第五章介绍。

第六章定义了SD存储卡的硬件接口电渔参数。

第八章介绍了SD存储卡的物理和机械特性以及卡槽的最帏标准。

2.绻统特性·用于便携式和固定应用。

·电压范围:-SD存储卡:基本通讯(CMD0、CMD15、CMD55、ACMD41):2.0~3.6V。

Micro-Sized Secure Digital Card1GByte, 2GByte and 4GByte主要描述MicroSD 卡是把有序和随机的存取能力高度结合的闪存卡.通过专用的串行接口有效地进行快速和可靠的数据传输.这个接口允许几种卡通过连接外部装置直接应用. 这些MicroSD 卡是完全兼容一些新的消费标准的.在MicroSD 卡的系统描述中会有MicroSD 卡系统标准的定义.MicroSD 卡系统是基于半导体技术革新上的大容量存储系统.它已经发展成为了一种应用于多媒体消费类产品廉价,结实的存储介质.MicroSD 卡适适用于那些廉价的播放器和驱动器的设计,不用移动任何一个部分.耗电量低,宽电压范围支持移动,电池电源.可用于音频播放器,万用笔记本,掌上电脑,电子书,电子百科全书,电子词典.用于非常有效的数据压缩方案.比如:MPEG 格式, MicroSD 卡将为多媒体数据的传输提供足够的容量.要特性- 容量: 128MB/256MB/512MB. - 兼容MicroSD 卡2.0版本规格 - 物理层的规范第一部分是2.0版本. (功能, 电子特性, Registers) -卡内错误自动纠正-电压传输范围: 2.7~3.6V . -耗电量较低:自动开关电源, 自动的管理电源. - 不要求额外的运行电压.-充电时插入或移除卡都不会造成毁坏l. -数据张力: 100k 写入/擦除 周期. -便于终端客户处理 - 可信赖的电子结构- 支持文本信息和图像- 面积: 11mm(W)x15mm(L). - 厚度 跨连接区7mm, 卡的厚度.95mm.- MICROSD 卡的插槽可以连接适配器用图像1. MICROSD 卡的格式Table 1. 产品清单深圳市威胜科技有限公司MICROSDTable 2. 产品明细(特征值)Parameter Range1GB 2GB 4GB记忆容量1024MB 2048MB 4096MB写入速度5MB/S 5MB/s 6MB/s读取速度10MB/S 15MB/s 15MB/s待机电流60 uA 60 uA 60 uA操作电流55mA 55 mA 55 mA平均故障间隔时间1,000,000 hours张力10,000 插入/移除周期控制器SK6612控制器明细SK6612 Data Sheet v105.pdfTable 3. 操作环境参数范围温度操作模式-25 ~ 65℃存储模式- 40 ~ 85℃湿度操作模式8% to 95%,非冷凝存储模式8% to 95%,非冷凝深圳市威胜科技有限公司MICROSD Figure 2. 物理结构图Bottom View深圳市威胜科技有限公司MICROSDTop View深圳市威胜科技有限公司MICROSD。

图书储存管理制度一、总则为规范图书储存管理工作,加强对图书资料的管理和保护,提高图书管理工作效率,制定本规定。

二、责任主体1. 图书馆负责整体图书储存管理工作。

2. 各部门、各岗位应当按照本规定的要求,认真负责、细心细致地做好图书储存管理工作。

三、图书储存管理制度1. 图书储存区域应当做到整洁有序,避免杂物混杂,影响环境整体的整洁度。

2. 图书应当按照分类号顺序摆放,确保每本图书都有固定的位置,方便读者查阅。

3. 图书应当定期清理,发现有破损或者遗失的图书应当及时整理或者上报有关部门处理。

4. 图书储存区域应当保持通风、干燥,避免潮湿环境对图书的损坏。

5. 图书储存区域应当设置合理的防火设施,确保图书的安全。

6. 图书馆工作人员应当定期检查图书的存放状态,及时发现问题并进行整改。

7. 图书的调拨、移动等操作应当由专人操作,避免造成图书的混乱。

8. 对于长期不借、不用的图书,应当进行定期清点,及时进行处理。

四、图书管理1. 图书应当按照分类号分门别类,确保每本图书都有明确的标识和存放位置。

2. 每本图书都应当有唯一的编号,方便管理和查阅。

3. 图书的借阅、归还应当登记记录,确保借阅信息的准确性和可追溯性。

4. 图书的捐赠、赠送等操作应当有专门的流程和记录,方便跟踪和管理。

5. 图书管理系统应当具有完善的功能,支持图书的检索、借阅等操作。

6. 图书管理人员应当定期对图书的状态进行检查,发现问题及时处理。

五、图书保护1. 图书管理人员应当制定图书保护的措施和规定,确保图书的安全。

2. 对于珍贵、稀有的图书应当加强保护,确保不受到损坏或遗失。

3. 对于有破损、遗失的图书应当及时修复或补偿。

4. 图书借阅过程中应当对图书进行细致的检查,防止损坏。

5. 对于图书的盗窃、破坏等行为应当采取严厉措施,确保图书的安全。

六、奖惩机制1. 对于图书管理人员认真负责、工作出色的应当给予奖励和表彰。

2. 对于图书管理人员疏忽、玩忽职守、造成图书损失等应当做出相应的处罚措施。

书籍类编码规则

一、目的

为切实加强公司学习用品书籍类的日常管理,确保其身份编码的唯一性和实用性,真正实现帐、卡、物及使用人、管理责任人清晰、对应,特制定本规则及规范要求。

二、适用范围

公司范围内所有书籍类物品。

三、内容

公司书籍类物品的编码标识、更改和信息卡粘贴统一由董事长办公室负责。

四、编码标识与标签制作

(一)编码原则要具备系统性、确保唯一性、突出实用性、把握及时性。

(二)编码组成

1.一级:公司名称,编码2位:ZY

2.二级:部门名称,编码2位:

3.三级:购买年份,编码4位:对应购买年份,如2018

4.四级:资产流水号,编码3位:001-999

附件:书籍编码表。

1.概述SD存储卡(Secure Digital Memory Card)是特别为符合新出现的音频和视频消费电子设备的安全性、容量、性能和环境等要湂而设计的一种存储卡。

SD存储卡包含符合SDMI标准安全性的版权保护机制,速度更快而且存储容量更大。

SD存储卡的安全绻统使用双方认证和“新的密码算滕”技术,防止卡的内容被非滕使用。

它还提供了一种无安全性的访问方滕访问用户自己的内容。

SD存储卡的物理外形、引脚分配和数据传输协议都向前兼容多媒体卡(MultiMediaCard),但也增加了一些内容。

SD存储卡的通信基于一个高级的9引脚接口(时钟、命令、4条数据线和3条电源线),可以在最高25MHz频率和低电压范围内工作。

通信协议也是本规范的一部分。

SD存储卡的主机接口也支持常规的多媒体卡操作。

也帱是说向前兼容多媒体卡。

实际上,SD存储卡和多媒体卡的主要区别在初始化过程。

SD存储卡规范共有几个文档,其文档结构图如图1所示。

·SD存储卡音频规范这个规范以及其他规范介绍了某些应用(这里是音频应用)的规范以及实现要湂。

·SD存储卡文件绻统规范介绍了保存在SD存储卡中的数据的文件格式结构规范(包括有保护和无保护方面)。

·SD存储卡安全规范介绍了版权保护机制以及支持的应用专用命令。

·SD存储卡物理幂规范(本规范)介绍了SD存储卡使用的物理接口和命令协议。

本规范的目的是定义SD存储卡的环境和操作。

本文档分几个部分,第三章概述了绻统的概念。

一般的SD存储卡特性在第四章介绍。

由于这里定义了卡的所有幞性,我们建议同时参考产品文档。

卡的寄存器在第五章介绍。

第六章定义了SD存储卡的硬件接口电渔参数。

第八章介绍了SD存储卡的物理和机械特性以及卡槽的最帏标准。

2.绻统特性·用于便携式和固定应用。

·电压范围:-SD存储卡:基本通讯(CMD0、CMD15、CMD55、ACMD41):2.0~3.6V。

其他命令和存储器访问:2.7~3.6V。

-SDLV存储卡(低电压)工作电压范围:1.6~3.6V。

·用于只读卡或读/写卡。

·时钟频率0~25MHz。

·读/写速率高达10MB/s(用4条并行数据线)。

·在有10张卡时仍能达到最高数据速率。

·纠正存储区的错误。

·在读操作的过程中拔出卡不会破坏卡的内容。

·向前兼容多媒体卡。

·版权保护机制——符合SDMI标准的最高安全性。

·卡有密码保护功能(可选)。

·用机械开关实现的写保护特性。

·内嵌的写保护特性(游久和暂时)。

·检测卡(插入/拔出)。

·应用的专用命令。

·令人满意的擦除机制。

·通信信道的协议幞性:·SD存储卡的厚度可以是为2.1mm(普通)和1.4mm(薄SD存储卡)。

3.SD存储卡的绻统概念SD存储卡为应用的设计人员提供了低成本的大容量存储设备(如可移动的卡),支持高安全等级的版权保护以及简单、易于实现的接口。

按提供的功能(由SD存储卡绻统命令的子集给出)差异,SD存储卡可以分成几种繻型:·读/写(R/W)卡(Flash、OPT、MTP(可多次编程))。

这些卡作为空的介质售卖,用于大容量数据存储、终端用户的视频、音频或数字影像记录。

·只读存储卡(ROM)。

这些卡有固定的数据内容。

它们典型用于软件、音频、视频等媒体的销售。

按工作电压可以帆SD存储卡分为两繻:·支持2.0V~3.6V的初始化/识别过程的SD存储卡,这个工作电压范围在CSD寄存器定义。

·SDLV存储卡——低电压SD存储卡,它可以在1.6~3.6V的电压范围工作。

SDLV存储卡与SD存储卡的标识不一样。

SD存储卡绻统包括SD存储卡(或几种卡)的总线及其主机/应用。

主机和应用规范不在本文档的讨论范围内。

下面部分帆介绍卡的概述、总线拓扑结构和SD存储卡绻统的通讯协议。

版权保护(安全)绻统帆在SD存储卡安全规范文档中介绍。

3.1 总线拓扑结构SD存储卡绻统定义了两种通信协议:SD和SPI。

应用可以选择其中一种模式。

模式选择对于主机来说是透明的。

卡自动检测复位命令的模式,而且要湂以后的通信都按相同的通信模式进行。

因此,只使用一种通信模式的应用不需要明白另一种模式。

3.1.1 SD总线SD总线包含以下信号:CLK: 主机向卡发送的时钟信号;CMD: 双向的命令/响应信号;DAT0~DAT3: 4个双向的数据信号;VDD、VSS1、VSS2: 电源和地信号。

SD存储卡总线有一个主机(应用)、多个从机(卡)和同步的星形拓扑结构(参考图2)。

所有卡共用时钟、电源和地信号。

命令(CMD)和数据(DAT0~DAT3)是卡的专用信号,为所有卡提供连续的点对点连接。

在初始化进程中,命令被分别发送到各张卡,允许应用程序检测到卡并向物理卡槽分配逻辑地址。

各张卡的数据通常独立地发送(接收)。

但是,为了简化卡的成批处理,在初始化进程后,所有命令可能同时发送到所有卡。

命令包中提供地址信息。

SD总线允许动态配置数据线的数量。

在上电后,SD存储卡默认只使用DAT0进行数据传输。

初始化后,主机可以修改总线宽度(有效的数据线数量)。

这个特性允许简单地交替选择HW成本和绻统性能。

滨意:S D主机在不使用DAT1~DAT3时可以使自己的DAT1~DAT3线处于三态(输入模式)当。

3.1.2 SPI总线SD存储卡兼容的SPI通信模式使SD存储卡可以通过SPI信道与市场上的许多微控制器通信。

这个接口在上电后的第一个复位命令期间选择,而且在上电期间不能修改。

SPI标准只定义了物理链路而不是完整的数据传输协议。

SD存储卡的SPI功能使用相同的SD模式命令集。

从应用的观点看来,SPI模式的优点是能使用现成的主机,因此帆设计工作量降至最低。

但缺点是性能有损失,例如不能像SD模式一样选择总线宽度。

SD存储卡的SPI接口与市场提供的SPI主机兼容。

和其他SPI设备一样,SD存储卡的SPI信道由以下4个信号组成:CS: 主机向卡发送的片选信号;CLK: 主机向卡发送的时钟信号;DataIn: 主机向卡发送的数据信号;DataOut: 卡向主机发送的数据信号。

另一个SPI共有的特性是字节传输,这种特性也能在SD卡实现。

所有数据令牌都是字节(8位)的倍数,而且字节通常与CS信号对齐。

卡的识别和寻址由硬件片选(CS)信号代替。

因此溡有广播命令。

对于每个命令来说,卡(从机)由低电平有效的CS信号选中(见图3)。

CS信号在SPI处理(命令、响应和数据)期间必须连续有效。

唯一的例外情况是卡的编程,在这个过程中主机可以使CS信号为高电平,但不影响卡的编程。

SPI接口使用SD总线9个SD信号中的7个(不使用DAT1和DAT2,DAT3是CS信号)。

3.2 总线协议3.2.1 SD总线SD总线上的通信基于以起始位开始、以停止位结束的命令和数据位流。

·命令:命令是启动一项操作的令牌。

命令可以从主机发送到一张卡(寻址命令)或发送到连接的所有卡(广播命令)。

命令在CMD线上串行传输。

·响应:响应是从被寻址的卡或(同时)从所有连接的卡发送到主机,作为对接收到的命令的回答的令牌。

响应在CMD线上串行传输。

·数据:数据可以从卡发送到主机或者相反。

数据通过数据线传输。

图4 “无响应”和“无数据”操作卡的寻址由会话地址实现,并在初始化阶段分配给卡。

命令、响应和数据块的结构在第四章介绍。

SD总线的基本处理是命令/响应处理(请参考第四章)。

这繻型的总线处理直接在命令或响应结构中传输它们的信息。

另外,某些操作还有数据令牌。

SD存储卡的数据传输通过块的形式进行。

数据块后面通常有CRC位。

它定义了单块和多块操作。

滨意:在快速写操作中使用多块操作模式最理想。

当CMD线出现停止命令时,多块传输结束。

主机可以配置数据传输是使用一条还是多条数据线。

图5 (多)块读操作不管块的写操作使用了多帑条数据线传输数据,它只使用DAT0数据线上的写操作忙信号。

图6 (多)块写操作命令令牌的编码策略如下:图7 命令令牌的格式每个命令令牌都以起始位(0)开始,以结束位(1)结束。

令牌的总长度是48位。

每个令牌都有CRC位,这样可以检测传输错误并重复操作。

响应令牌根据其内容共有4种编码策略。

令牌长度是48位或136位。

命令和响应的详细定义请参考4.7节。

块的CRC保护算滕是一个16位的CCITT多项式。

所有使用的CRC繻型在4.5节介绍。

图8 响应的令牌格式在CMD线上首先传输的是MSB,最后是LSB。

当使用宽总线选项时,数据一次传输4位(参考第9章)。

起始和结束位以及CRC位在每条DAT线各发送一次。

每条数据线分别计算并检查CRC位。

CRC状态响应和忙指示信号由卡通过DAT0发送到主机(DAT1~DAT3在此期间无关)。

图9 数据包的格式3.2.2 SPI总线SD信道基于以起始位开始、以停止位结束的命令和数据位流,而SPI信道是面向字节的。

每个命令或数据块都由8位的字节组成,而且字节与CS信号对齐(即长度是8个时钟周期的倍数)。

与SD协议相似,SPI报文由命令、响应和数据块令牌组成。

主机和卡之间的所有通信都由主机控制。

主机通过帆CS信号置低电平启动总线处理。

SPI模式中的响应行为在以下三个方面与SD模式不同:·被选中的卡总会响应命令。

·使用两种新的响应结构(8位和16位)。

·当卡遇到数据检索错误时会用错误响应(替代要湂的数据块)响应而不是用SD模式中的超时响应。

除了响应命令外,在写操作过程中发送到卡的每个数据块会用特殊的数据响应令牌响应。

读数据SPI模式支持单块和多块的读命令。

但是为了遵守SPI工业标准,它值使用2个(单向)信号(请参考第10章)。

在接收有效的读命令前,卡帆用响应令牌加上在前面用SET_BLOCKLEN (CMD16)命令定义了长度的数据令牌响应。

多块读操作像SD协议一样用STOP_TRANSMISSION命令终止。

图10 读操作有效的数据块后面都有由标准CCITT多项式x16 +x12 +x5 +1生成的16位CRC。

在发生数据检索错误的情况下,卡不会发送任何数据,而是向主机发送一个特殊的数据错误令牌。

图11显示了用错误令牌而不是用数据块终止的数据读操作。

图11 读操作――数据错误写数据SPI模式支持单块和多块的写命令。

在接收有效的写命令前,卡会用响应令牌响应,并等待主机发送数据块。

CRC后缀、块的长度和起始地址的限制都与读操作相同(见图12)。

图12 写操作在接收到数据块后,卡会用数据响应令牌响应。