仿真增益带宽-通用运算放大器模型

- 格式:doc

- 大小:2.62 KB

- 文档页数:1

一款高增益、低功耗、宽带宽全差分运放设计周吉;龚敏;高博【摘要】基于SMIC 0.18 μm工艺模型设计了一种低电压1.8 V下的高增益、低功耗、宽输出摆幅、宽带宽的运算放大器电路.采用增益自举技术的折叠共源共栅结构极大地提高了增益,并采用辅助运放电流缩减技术有效地降低了功耗,且具有开关电容共模反馈(SC-CMFB)电路.在Cadence spectre平台上仿真得到运放具有极高的开环直流增益(111.2 dB)和1.8V的宽输出摆幅,单位增益带宽576 MHz,相位裕度为58.4°,功耗仅为0.792 mW,在1 pF的负载时仿真得到0.1%精度的建立时间为4.597 ns,0.01%精度的建立时间为4.911 ns.【期刊名称】《电子与封装》【年(卷),期】2016(016)005【总页数】5页(P26-30)【关键词】低功耗;运算放大器;高增益;宽带宽;折叠共源共栅【作者】周吉;龚敏;高博【作者单位】四川省微电子技术重点实验室,四川大学物理学院,成都610064;四川省微电子技术重点实验室,四川大学物理学院,成都610064;四川省微电子技术重点实验室,四川大学物理学院,成都610064【正文语种】中文【中图分类】TN402运算放大器(简称运放)是许多模拟系统和混合信号系统中一个完整且关键的部分,随着无线通讯技术和CMOS集成电路制造工艺技术的迅猛发展,电源电压越来越低,功耗要求越来越小,但数模混合信号系统对分辨率和速度的要求却越来越高,因此高性能的运放设计成为了必要[1]。

根据模拟电路设计的“八边形法则[1]”,运放的关键性能参数如增益、速度、功耗、输出摆幅等参数相互制约,这对高性能放大器的设计提出了许多难题。

因此,设计同时具有高增益、宽带宽、宽输出摆幅并且低功耗的放大器便成为了本设计的难点[1,2,3]。

高速、高精度的应用需要运放具有很高的增益和带宽,而这必然会增加运放的功耗,Mersi A.等发表的文献中采用两级带补偿结构的运放功耗仅为0.86 mW[4],而这种结构对进一步提高运放带宽等有一定的局限性,本文采用了一种不同的低功耗运放结构,希望解决这个问题。

集成运放同相放大器的带宽测量(设计与仿真)实验报告一、实验目的1、熟悉放大器幅频特性的测量方法。

2、掌握集成运算放大器的带宽与电压放大倍数的关系。

3、了解掌握Proteus 软件的基本操作与应用。

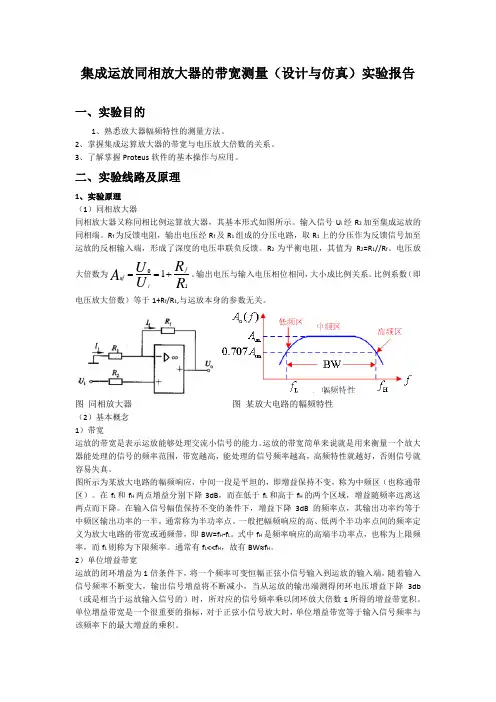

二、实验线路及原理1、实验原理 (1)同相放大器同相放大器又称同相比例运算放大器,其基本形式如图所示。

输入信号U i 经R 2加至集成运放的同相端。

R f 为反馈电阻,输出电压经R f 及R 1组成的分压电路,取R 1上的分压作为反馈信号加至运放的反相输入端,形成了深度的电压串联负反馈。

R 2为平衡电阻,其值为R 2=R 1//R f 。

电压放大倍数为RR UU Afiuf101+==。

输出电压与输入电压相位相同,大小成比例关系。

比例系数(即电压放大倍数)等于1+R f /R 1,与运放本身的参数无关。

图 同相放大器 图 某放大电路的幅频特性(2)基本概念 1)带宽运放的带宽是表示运放能够处理交流小信号的能力。

运放的带宽简单来说就是用来衡量一个放大器能处理的信号的频率范围,带宽越高,能处理的信号频率越高,高频特性就越好,否则信号就容易失真。

图所示为某放大电路的幅频响应,中间一段是平坦的,即增益保持不变,称为中频区(也称通带区)。

在f L 和f H 两点增益分别下降3dB ,而在低于f L 和高于f H 的两个区域,增益随频率远离这两点而下降。

在输入信号幅值保持不变的条件下,增益下降3dB 的频率点,其输出功率约等于中频区输出功率的一半,通常称为半功率点。

一般把幅频响应的高、低两个半功率点间的频率定义为放大电路的带宽或通频带,即BW=f H -f L 。

式中f H 是频率响应的高端半功率点,也称为上限频率,而f L 则称为下限频率。

通常有f L <<f H ,故有BW≈f H 。

2)单位增益带宽运放的闭环增益为1倍条件下,将一个频率可变恒幅正弦小信号输入到运放的输入端,随着输入信号频率不断变大,输出信号增益将不断减小,当从运放的输出端测得闭环电压增益下降3db (或是相当于运放输入信号的)时,所对应的信号频率乘以闭环放大倍数1所得的增益带宽积。

增益为1的放大器仿真增益为1的放大器是一种特殊的放大器,其输出信号的幅度与输入信号的幅度相等,但是为了实现这种增益,放大器需要提供一定的功率增益。

在本文中,我们将详细讨论增益为1的放大器的工作原理、设计和仿真。

1. 引言放大器是电子电路中常见的一个模块,它可以将输入信号的幅度放大到所需的水平。

增益为1的放大器是一种特殊的放大器,它不改变输入信号的幅度,但是仍然需要提供一定的功率放大。

2. 工作原理增益为1的放大器可以被看作是一个信号放大器和功率放大器的组合。

它首先接收输入信号并将其放大到所需的水平,然后通过一个功率放大器将放大后的信号输出。

3. 设计设计增益为1的放大器可以通过两个步骤完成:选择一个合适的信号放大器并选择一个合适的功率放大器。

3.1 信号放大器选择在选择信号放大器时,我们需要考虑以下几个因素:a. 增益:选择一个增益为1的放大器,我们需要选择一个具有单位增益的信号放大器。

b. 带宽:选择一个具有足够带宽的放大器,以便能够放大输入信号的所有频率成分。

c. 噪声:选择一个具有较低噪声的放大器,以保持输出信号的清晰度。

3.2 功率放大器选择在选择功率放大器时,我们需要考虑以下几个因素:a. 输出功率:选择一个能够提供所需输出功率的功率放大器。

b. 效率:选择一个能够提供高效转换的功率放大器,以减少功率损耗。

c. 稳定性:选择一个具有稳定性的功率放大器,以避免任何不稳定性对输出信号的影响。

4. 仿真在设计完成后,我们可以使用仿真软件来验证增益为1的放大器的性能。

仿真可以帮助我们评估放大器的带宽、噪声和功率输出等方面。

4.1 仿真软件选择选择一个适合的仿真软件对于仿真增益为1的放大器是非常重要的。

常见的仿真软件包括MATLAB、LTspice和ADS等。

4.2 仿真设置在进行仿真之前,我们需要设置仿真参数,包括放大器的输入信号、电源电压和负载等。

仿真参数的选择应该基于实际应用需求。

4.3 仿真结果分析仿真结果将给出增益为1的放大器的输入输出特性、频率响应和功率输出等信息。

集成运算放大器主要参数及理想模型分析详解正确使用集成运算放大器必须了解影响其工作性能的主要参数,其中输入误差信号是影响运放工作性能的重要参数之一。

本文主要研究引起集成运放输入误差信号的主要参数及减小其影响的方法。

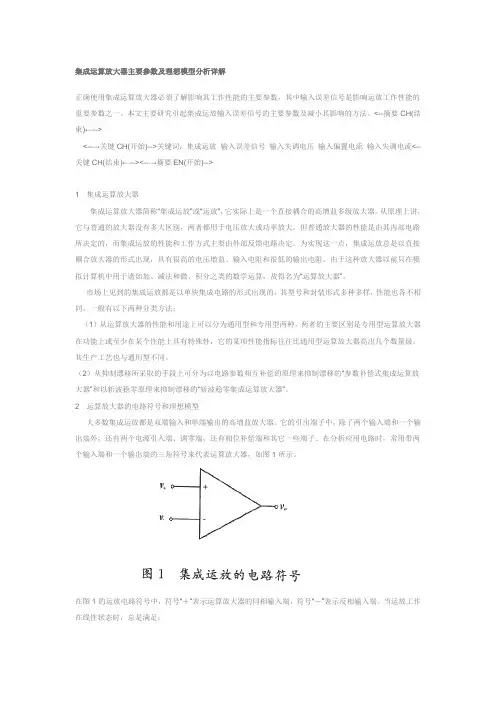

<--摘要CH(结束)←--><--→关键CH(开始)-->关键词:集成运放输入误差信号输入失调电压输入偏置电流输入失调电流<--关键CH(结束)←--><--→摘要EN(开始)-->1集成运算放大器集成运算放大器简称“集成运放”或“运放”,它实际上是一个直接耦合的高增益多级放大器。

从原理上讲,它与普通的放大器没有多大区别,两者都用于电压放大或功率放大。

但普通放大器的性能是由其内部电路所决定的,而集成运放的性能和工作方式主要由外部反馈电路决定。

为实现这一点,集成运放总是以直接耦合放大器的形式出现,具有很高的电压增益、输入电阻和很低的输出电阻。

由于这种放大器以前只在模拟计算机中用于诸如加、减法和微、积分之类的数学运算,故得名为“运算放大器”。

市场上见到的集成运放都是以单块集成电路的形式出现的,其型号和封装形式多种多样,性能也各不相同,一般有以下两种分类方法:(1)从运算放大器的性能和用途上可以分为通用型和专用型两种。

两者的主要区别是专用型运算放大器在功能上或至少在某个性能上具有特殊性,它的某项性能指标往往比通用型运算放大器高出几个数量级。

其生产工艺也与通用型不同。

(2)从抑制漂移所采取的手段上可分为以电路参数相互补偿的原理来抑制漂移的“参数补偿式集成运算放大器”和以斩波稳零原理来抑制漂移的“斩波稳零集成运算放大器”。

2运算放大器的电路符号和理想模型大多数集成运放都是双端输入和单端输出的高增益放大器。

它的引出端子中,除了两个输入端和一个输出端外,还有两个电源引入端、调零端,还有相位补偿端和其它一些端子。

在分析应用电路时,常用带两个输入端和一个输出端的三角符号来代表运算放大器,如图1所示。

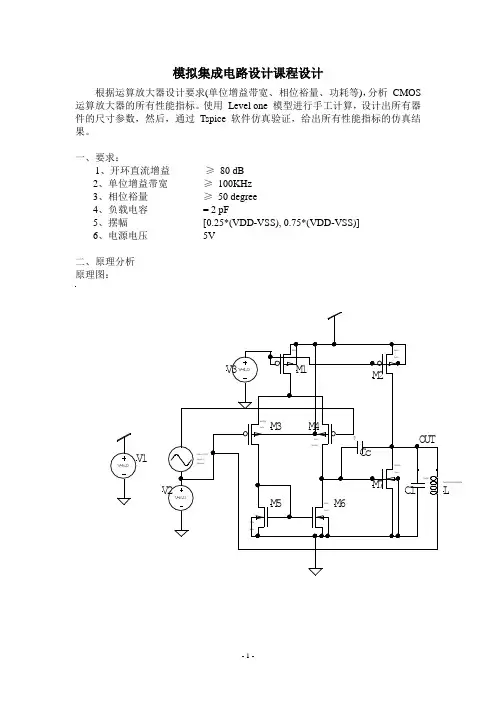

模拟集成电路设计课程设计根据运算放大器设计要求(单位增益带宽、 相位裕量、 功耗等),分析 CMOS 运算放大器的所有性能指标。

使用 Level one 模型进行手工计算,设计出所有器件的尺寸参数,然后,通过 Tspice 软件仿真验证,给出所有性能指标的仿真结果。

一、要求:1、开环直流增益 ≥ 80 dB2、单位增益带宽 ≥ 100KHz3、相位裕量 ≥ 50 degree4、负载电容 = 2 pF5、摆幅 [0.25*(VDD-VSS), 0.75*(VDD-VSS)]6、电源电压 5V二、原理分析 原理图:LV 1V 00000000000000V =5.0实验原理:电路选用二级米勒补偿,其中一级放大主要是放大增益,二级是放大摆幅,将电路分三部分来看左边:用直流电压为m1,m2提供偏置电压中间:m3,m4,m5,m6,m1一路选用差分放大电路作为一级放大 右边:m2,m7一路是提高输出摆幅电路部分 Cc 为补偿电容,而电感L 起稳压作用 为达到设计指标,对运算放大器的每个moS 管都要在饱和区工作,通过对原理图的小信号分析得到这种结构的增益为Gain = gm1×gm6/(gds2 + gds4)/(gds6 + gds7)表示,其中gds2 , gds4, gds6 , gds7,分别为M2,M4,M6,M7管的相关电导。

gm1,gm6分别M1、M6的跨导。

而输出电压摆幅为Vincm.max=Vdd-|V GS3|+Vthn ,Vincm.min=V od5-V GS1=V od5+V od1+Vthn1,其中Vod1、Vod5分别为M1和M5的过驱动电压。

21()(1)2D n ox GS TH DS WI C V V V Lμλ=-+2()112()()D m n oxGS TH DS GS THDDDSGS TH on n oxGS TH I W g C V V V L V V I L I V V V R WC V V Lμγλγμ=-==-∝-=-饱和饱和=时三、设计步骤:1. 由已知的C L 并根据转换速率的要求(或功耗要求)选择I SS (I 9)的范围;2. 计算满足频率要求的R out 范围,否则,改变I SS ;3. 设计W 3/L 3( W 4/L 4)、W 5/L 5( W 6/L 6 )满足上ICMR (或输出摆幅)要求;4. 设计W 2/L 2 、 W 7/L 7满足增益要求;满足下ICMR (或输出摆幅)要求;5. 若达不到设计要求,重复上述过程。

一、模拟电路的仿真案例1. 整体电路功能说明过流检测电路用于监视电路工作电流的大小,当电路负载上的电流超过某一数值,电路会给出报警信号。

检测电流可以在流入负载一侧取样,也可以在流出负载一侧取样,这两种检测方法可以分别称为高端和低端电流检测。

它们都是通过取样电阻采样电流然后通过电压放大器放大,都要求放大器有较高的输入阻抗、放大倍数线性度和一定的共模范围。

以下时一个可能的应用场景,0.1欧姆的电阻串接在1.8V电源和负载之间,一个仪表放大器将0.1欧姆电阻上的电压放大100倍(实际略低)后输入给运放的正相输入端,带隙电路产生的基准电压输入给运放的反相输入端,3.3V的电源给仪表放大器、基准和运算放大器供电,其中仪表放大器是由三个运算放大器组成的。

该电路一共由4个运算放大器模块和1个带隙基准模块组成,电路元件总数超过300个。

1.8V电源上的负载电流超过某一个设定值,运算放大器会输出一个高电平的报警信号。

总体电路的电路图如图1-1所示,总电路包括偏置电压模块bandgaptest1、由3个基本运放组成的仪表放大器yifang和输出级运放cmop。

图1-1 过流检测总电路图2.使用自建模型进行可靠性仿真本方案使用reliability.scs可靠性模型文件传递所需的模型参数,建模的所有步骤都是基于Cadence软件的Spectre中的URI接口,接下来分别用自建模型对偏置电压模块、运算放大器、总体电路进行可靠性仿真。

2.1 带隙基准电压电路可靠性仿真打开已经设计完整的带隙基准电压电路,界面显示如图1-2:图1-2带隙基准电压源电路图图1-3 等效电路结构图(a)图1-4 等效电路结构图(b)错误!未找到引用源。

-2是详细电路图,该电路是一个带隙基准结构。

带隙基准的工作原理是根据硅材料的带隙电压与电压和温度无关的特性,利用△V BE的正温度系数与双极型晶体管V BE的负温度系数相互抵消,实现低温漂、高精度的基准电压。

目录1 引言 (1)2 软件介绍 (3)3 运算放大器设计基础 (5)3.1运放的主要性能指标 (5)3.2运算放大器的基本结构 (6)3.2.1全差分运放 (6)3.2.2套筒式结构 (7)3.2.3折叠式结构 (8)4 系统总体设计 (10)4.1电路设计的整体结构 (10)4.2 主放大电路设计 (11)4.3 偏置电路的设计 (13)4.4 输出级的设计 (13)4.5 共模反馈的设计 (14)4.6 总体布局 (15)5 仿真与分析 (17)5.1运放直流与交流特性 (17)5.2噪声特性分析 (19)5.3电源抑制比 (19)5.4设计指标 (20)5.5放大器参数 (21)6 版图设计与分析 (22)6.1 L-Edit介绍 (22)6.2版图设计规则 (22)6.3基本器件版图设计 (23)6.3.1 NMOS版图设计 (23)6.3.2 电容电阻版图设计 (24)6.4版图的总体设计 (26)6.4.1主电路模块版图 (26)6.4.2偏置模块版图 (27)6.4.3输出模块版图 (27)6.4.4整体模块版图 (28)6.5 LVS版图比对 (29)7 结论 (31)谢辞 ................................................................................................... 错误!未定义书签。

参考文献 .. (32)附录1 (33)附录2 (35)1 引言集成运算放大器(Integrated Operational Amplifier)简称集成运放,是由多个CMOS管与电容电阻通过耦合方式实现提高增益的模拟集成电路[1]。

集成运放具有增益高、输入阻抗大、输出阻抗低、共模抑制比高和失调与漂移性小等优点,而且当输入电压值为零时,输出值也为零。

集成运放是构成常用集成电路系统的通用模块[2] [3]。

运算放大器的设计与仿真设计要求:1.增益稳定性:运算放大器的增益应该能够在所需的频率范围内保持稳定。

2.输入阻抗:运算放大器应具备较高的输入阻抗,以减少对输入信号的干扰。

3.输出阻抗:运算放大器应具备较低的输出阻抗,以减小对外界负载的影响。

4.带宽:运算放大器应具备较宽的带宽,以满足对高频信号的放大需求。

5.稳定性:运算放大器应具备较高的稳定性,以避免产生自激振荡或输入偏移。

电路结构:差分输入级:差分输入级是运算放大器的核心部分,用于接受差分输入信号。

它由两个差分对组成,每个差分对由两个晶体管连接而成。

差分输入级的输入阻抗较高,能够减小对输入信号的干扰,提高共模抑制比。

共模放大级:共模放大级用于放大输入信号的共模部分。

它由一对电流镜电路和一个差分放大电路组成。

共模放大级的放大倍数影响运算放大器的共模抑制比和输入选择性。

输出级:输出级用于提供对外的放大信号。

它由输入级的晶体管、电源和输出级负载组成。

输出级应具备较低的输出阻抗,以便与外界负载匹配。

参数选择:参数选择是运算放大器设计的重要环节。

下面是几个常见参数的选择方法:增益:增益可以根据具体应用需求来设定。

一般来说,增益越高,对输入信号的放大效果越好,但也容易引入噪声和干扰。

带宽:带宽取决于应用的特定频率范围。

选择较高的带宽可以满足对高频信号的放大需求,但也可能引入频率抖动和畸变。

输入阻抗:输入阻抗应根据信号源的特性来选择。

如果信号源的输出阻抗较高,则需要选择较低的输入阻抗以保证信号传输。

输出阻抗:输出阻抗应根据负载的特性来选择。

如果负载的输入阻抗较高,则需要选择较低的输出阻抗以提供足够的电流输出。

稳定性:稳定性可以通过选择合适的电容和电阻来提高。

一般来说,通过增加补偿电容和添加反馈电阻可以提高运算放大器的稳定性。

仿真:对于运算放大器的设计,可以使用电子设计自动化软件进行仿真验证。

主要包括以下步骤:1.输入基本电路参数,如晶体管的参数、电源电压等。

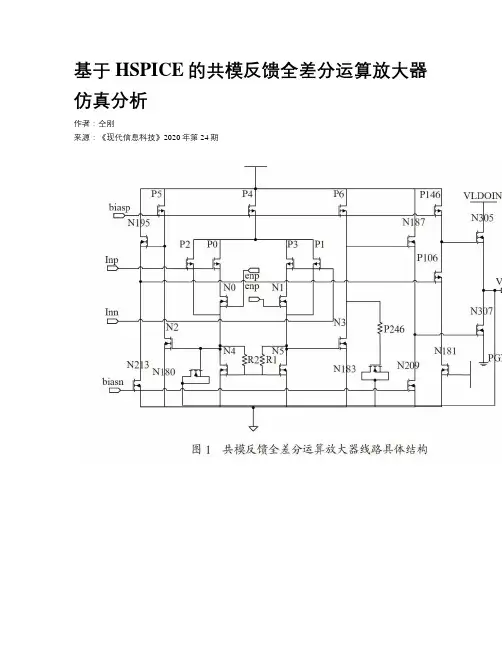

基于HSPICE的共模反馈全差分运算放大器仿真分析作者:仝刚来源:《现代信息科技》2020年第24期摘要:全差分运算放大器因其噪声较低、输出电压摆幅较大,共模噪声抑制及谐波失真抑制性能较好而得到大面积推广应用,HSPICE是目前应用较广的的模拟集成电路设计辅助工具,基于HSPICE对设计的共模反馈全差分运算放大器进行交流参数、直流参数、瞬态特性等主要性能参数进行了仿真分析,仿真分析结果表明,该电路各方面均具有综合良好的特性。

关键词:HSPICE;共模反馈;运算放大器中图分类号:TN722.7;TP342 文献标识码:A 文章编号:2096-4706(2020)24-0053-05Simulation Analysis of Common Mode Feedback Fully Differential Operational Amplifier Based on HSPICETONG Gang(Xiamen Shunfuxin Technology Co.,Ltd.,Xiamen 361006,China)Abstract:Fully differential operational amplifier has been widely popularization and application because of its low noise,big output voltage swing,and better performance in common mode noise suppression and harmonic distortion suppression. HSPICE is the auxiliary tool for analog integrated circuit design that is used more widely at present. Based on HSPICE,an simulation analysis is made to the main performance such as the AC parameters,DC parameters,instantaneous characteristic of the designed common mode feedback fully differential operational amplifier. The simulation analysis results show that the circuit has good comprehensive characteristics in all aspects.Keywords:HSPICE;common mode feedback;operational amplifier0 引言在实际的芯片设计工作中,作者所从事的电源管理类集成电路芯片设计基本上都会用到运算放大器(也称作“运放”)。

一种提高放大器增益和带宽的设计技术分析黄晓宗;黄文刚;刘凡;刘志伟【期刊名称】《太赫兹科学与电子信息学报》【年(卷),期】2015(013)003【摘要】运算放大器是信号处理中的基础模块,是高性能混合信号数据转换器、片上系统(SoC)等的重要组成部分.低功耗和高性能的基础电路模块成为系统发展的瓶颈,因此对增益和带宽增强型运算放大器的研究成为业界关注的焦点.为了研究运算放大器增益和带宽优化设计技术,实现低功耗高性能的解决方案,对电流重用技术的产生背景和技术演进作了较为详细的分析,体现了在技术进步过程中对结构的优化和改进,对高性能系统集成设计具有重要的参考意义.【总页数】5页(P468-472)【作者】黄晓宗;黄文刚;刘凡;刘志伟【作者单位】电子科技大学微电子学与固体电子学学院,四川成都610054;中国电子科技集团公司第24研究所,重庆400060;中国电子科技集团公司第24研究所,重庆400060;电子科技大学微电子学与固体电子学学院,四川成都610054;中国电子科技集团公司第24研究所,重庆400060;电子科技大学微电子学与固体电子学学院,四川成都610054【正文语种】中文【中图分类】TN722【相关文献】1.一种高增益大带宽的增益自举型折叠共源共栅放大器设计 [J], 王停;唐海林;赵宗佑;于跃宝2.一种高增益、大带宽跨阻放大器的设计 [J], 杨赟秀;袁菲;明鑫;邓世杰;路小龙;景立;呙长冬3.一种提高放大器增益和带宽的设计技术分析 [J], 黄晓宗;黄文刚;刘凡;刘志伟;4.一种高输出电压的增益带宽可调的程控放大器设计 [J], 赵中琦; 崔鸣; 张新5.一种提高GaAs HBT放大器增益带宽积的技术 [J], 李杰;胡善文;张晓东;高怀因版权原因,仅展示原文概要,查看原文内容请购买。

运算放大器参数的基本仿真方法示例(2nd edition)刘泰源,LTC1733 GROUPROOM 237,SOC DESIGN CENTRE目的:仿真一个两级的运放,熟悉模拟电路仿真软件的使用。

采用软件:workview ,hspice 2005.03工艺库的说明:采用韩国MagnaChip 0.5umCMOS工艺库对所采用电路描述:首先在workview中生成一个两级的运算放大器,并导出网表,第一级是差分的输入放大器,其作用是放大差模信号,抑制共模信号,第二级是一个共源放大器,提供更大的增益。

在第一级里,m1、m2为差动输入管,m5提供由基准电压产生的偏置电流,m3、m4两管是一对电流镜,保证m3,m4两管为两个输入端提供相等的电流。

第二级m8是负载管,m7是倒相器的输入管。

主要仿真的运算放大器特性:增益,增益带宽,建立时间,摆率,ICMR,CMRR,PSRR,输出摆幅,失调电压 运放电路结构图:图1运放电路静态工作点的调节在整个模拟电路的设计中是非常重要的,因为不同功能的模块对器件的工作状态有不同的要求,在电路设计初期确定下的管子的工作状态就在这个阶段与以实现。

实现的语句在hspice里面是.op语句。

这个语句会在仿真生成的.lis文件里面形成一个关于管子工作状态的理解,查找.lis文件中的region关键字,就能找到各个管子工作点的列表。

静态工作点的调节:采用的方法,先设计第一级的的工作点,再设计第二级的工作点。

第一级工作点设计要求五个管子都工作在饱和区,并且保证电路的对称,在vcc,in1,in2和bias上要加上适当的偏置电压。

我设定的bias为 1.5v,in1=in2=2.5v,这个时候要注意调节各管子的宽长比使管子达到饱和,如果m3,m4是线形区,则应该调节减小m3,m4的宽长比,同时通过增加m5的宽长比增大偏置电流,如果m5处于线形区,则应该采取与上面所说的相反的方法,如果输入管处于线形区,要考虑输入的偏置电压是否合适,同时折中上面的调节方法。

一种宽带可编程增益放大器设计张博;王云娜;孙景业;吴昊谦【摘要】基于台积电0.18μm工艺,设计一款频率为0~100 MHz的宽带可编程增益放大器(program-mable gain amplifier,PGA).采用闭环反馈结构,主要设计运算放大器(operational amplifier,OPA)、电阻反馈网络、2-4译码器和直流失调校准电路(direct current offset cancellation,DCOC)4部分电路.仿真结果表明:该PGA 电路的动态范围为0~18 dB,步进为6 dB,带宽为100 MHz,噪声系数(noise factor,NF)低于15 dB,芯片面积为247μm×180μm.【期刊名称】《电子设计工程》【年(卷),期】2018(026)020【总页数】5页(P119-123)【关键词】可编程增益放大器;闭环反馈结构;运算放大器;直流失调校准【作者】张博;王云娜;孙景业;吴昊谦【作者单位】西安邮电大学电子工程学院,陕西西安710121;西安邮电大学电子工程学院,陕西西安710121;西安邮电大学电子工程学院,陕西西安710121;西安邮电大学电子工程学院,陕西西安710121【正文语种】中文【中图分类】TN402随着无线通信技术的高速发展,集成电路的发展越来越快。

可编程增益放大器(Programmable Gain Amplifier,PGA)作为集成电路中的重要模块,也就被广泛应用于无线通信系统等领域[1-6]。

其中,PGA在电路中起着变化增益、调整信号动态范围和稳定信号的作用[1-2],如在射频前端电路的信号太弱时,PGA可提供一定增益使信号被放大到适当的信号水平[3-4]。

由于增益步进和增益误差是PGA的两项重要指标,不同PGA针对不同应用场景,增益步进和误差要求不同,所以这两项指标的优化设计电路已经相当成熟[7-9]。

但是一般会对带宽和噪声系数(noise factor,NF)的设计要求比较低,如文献[6]中的带宽为20 MHz,NF 为28 dB,文献[10]中的带宽为57 MHz,NF 为 19.3 dB,文献[11]中的带宽仅为40 MHz。

Bandwidth –3带宽-3TIPL 1213TI Precision Labs –Op AmpsPresented by Jason WuPrepared by Art Kay, Pete Semig, and Tim Green●Hello, and welcome to the TI Precision Lab discussing op amp bandwidth, part 3.●In this video we’ll discuss why you should always use the non-inverting gain tocalculate bandwidth and secondary effects (namely high-frequency pole location) on bandwidth.●大家好, 欢迎来到TI Precision Labs (德州仪器高精度实验室)。

本次视频将介绍运算放大器的bandwidth(带宽) 第三部分。

●我们将探讨为何运用non-inverting gain(同相增益)来计算带宽, 及高频极点的位置对带宽的二次效应。

Dominant Polefp = 11.03Hz2●In part 2 of this series we discussed the definition of gain bandwidth product.We demonstrated how to graphically determine the bandwidth of a circuit for a particular gain using the open-loop gain, or Aol, graph from a data sheet.However, we did not discuss the low-frequency, or dominate pole that appears in the graph.●The dominate pole is the point on the Aol graph where Aol begins to roll off withfrequency. This parameter is important when developing macromodels. The frequency of the pole can be estimated from the Aol curve, but a more accurate approach is to calculate it using this equation, where GBW is the gain bandwidth product and Avol is the open loop gain of the device.●Using the OPA827 as an example, we find the device has a gain bandwidthproduct of 22MHz and open loop gain of 126 decibels. We can convert 126dB to its linear representation using this equation.Substituting 22MHz and 1.995 times 10 to the 6th for gain bandwidth and open loop gain, respectively, yields a dominate pole frequency of 11.03Hz. This calculation is consistent with the graph from the data sheet.●在带宽系列视频的第2部分,我们讨论gain bandwidth product(增益带宽积)的定义。

0中国集成电路设计♦China lntegrated Circult一种具有高增益和超带宽的全差分跨导运算放大器罗杨贵1,曾以成1,邓欢2,唐金波21.湘潭大学物理与光电工程学院;2.湖南毂梁微电子有限公司摘要:基于GSMC0.18um CM OS工艺,设计了一种应用于12位ADC的全差分运算放大器。

为了提高增益,在套筒式共源共栅结构上运用了增益提高技术。

为了提高输入跨导,采用隔离效果更好的深N阱CMOS作为输入端,从而提升增益带宽。

为了降低功耗,利用单端放大器作为辅助运放。

整体电路结构简单优化。

仿真结果表明,运算放大器直流开环增益大于100dB,单位增益带宽大于800M H z,相位裕度大于70毅,完全满足目标ADC的性能要求,是一种新型且质量较高的运放,也可应用于其它场合。

关键词:增益提高;套筒式共源共栅;高增益带宽;深N阱中图分类号:TN432文献标识码:AA Fully Differential Transconductance Operational Amplifierwith high Gain and ultra GBWLUO Yang-gui,ZENG YirCheng1,DENG Huan2,TANG Jn-bo21.SchoolofPhysicsand Opibe]ectronics,X iangtan University;2.H unan Greai-Leo M icroe]ectronicsCO.LTDAbstract:Based on theGM SC0.18um CM OS process,a fuUy differentialoperationalam plifierlbr12-bitADC is designed.In orderto increase the gain,a gain-enhancing technique is used on the te]escopic cascode structure.In order to increase input transconductance,the deep N-W elltansistorwith better isolation function was used as the input,thereby to enhance the gain bandwidth.In order to reduce power consumption,a single-ended amplifier is used as an auxiliary operational amplifier.The overall circuit structure is simple and optimized.The simulation results show that the operational amplifier DC open-loop gain is greater than100dB,the unity gain bandwidth is greater than800MHz, and the phase margin is greater than70毅,which fully meets the performance requirements of ADC.It is a new and high-quality operational amplifier that can also be applied to other applications.Keywords:Gain enhancement;Telescopic cascode;High gain bandwidth;Deep N_well0引言模数转换器作为连接模拟信号与数字信号的桥梁,越来越显示出其重要性。

仿真增益带宽-通用运算放大器模型

信号信号链工程师 David Zhao (赵大伟)

运算放大器的增益带宽积(GBW)会怎样影响你的电路并不总是显而易见。

宏模型有固定的增益带宽积。

虽然你可以深入观察这些模型,当然最好不要瞎弄它们。

那么你可以做什么?

你可以使用SPICE中的通用放大器的模型来检测你的电路对增益带宽积的灵敏度。

大多数基于SPICE的电路仿真器包含一个简单的运算放大器模型,因此你很容易就可以修改。

TINA的仿真界面。

首先将DC开环增益设置为1M(120dB)。

然后,主极点的频率(单位为Hz)与其相乘将得到放大器的增益带宽积(单位为MHz)。

在这个例子中,10Hz的主极点对应10MHz的增益带宽积。

对于5MHz,10MHz和100MHz三种不同的增益带宽积,图2分别给出了对应的开环响应。

注意这个简单的模型存在第二个极点(有些人称它为不受欢迎的极点)。

有时候,你会想要第二个极点处在一个非常高的频率,比如说10GHz。

对于任何合理的增益带宽积,这将会形成一个理想的90°的相位裕量。

在这个范例中,我将第二个极点设定为100MHz,等于我仿真时最大的增益带宽积的值。

在100MHz增益带宽积的响应中,你可以看到第二个极点的影响,它将会使得开环响应在100MHz的地方开始弯曲。

它使得单位增益带宽大约为78MHz,和一个具有78MHz增益带宽积的运算放大器的情况很相似。

运算放大器的单位增益带宽和增益带宽积并不一定是相同的值。

对于有源滤波器的设计,很难判断增益带宽积的需求,它是一个可以应用这种技术的很好的例子。

图3中使用FilterPro来设计切比雪夫滤波器,它会给出一些增益带宽积值的推荐,然而它的设计准则可能会比一些情况更严格。

对于这个设计而言,它推荐了100MHz或更大的增益带宽积来达到近乎理想的滤波器设计特性。

,我设定三种增益带宽积(5MHz,10MHz,100MHz)来对设计进行仿真。

从结果中可以得出小于100MHz的增益带宽积已经是符合要求的。

对于最终的仿真,你应该使用你所选择的运算放大器的宏模型。

我使用了TINA中的参数步进功能,改变主极点从而改变增益带宽积。

其它仿真器也有类似的功能。

当然,也可以手动地修改参数。

无论是哪种方式,改变通用运算放大器的增益带宽积将帮助你洞察增益带宽积对电路的影响。

你曾经使用运算放大器模型来修改其它参数吗?欢迎给出建议。