数字电路与数字电子技术 课后答案第四章

- 格式:doc

- 大小:1.32 MB

- 文档页数:19

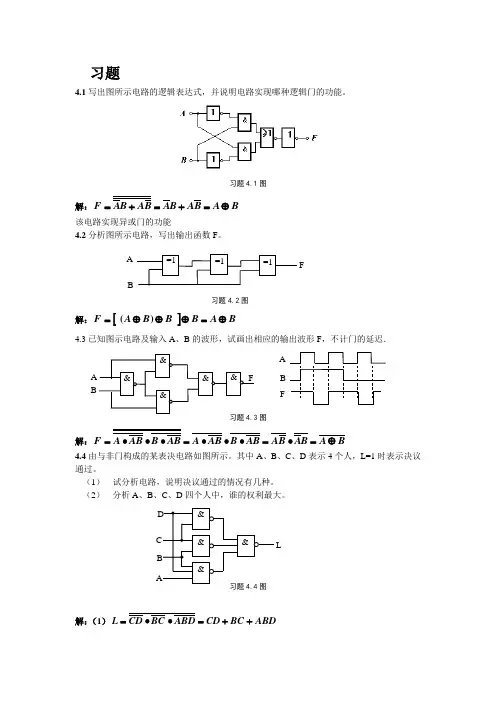

习题4.1写出图所示电路的逻辑表达式,并说明电路实现哪种逻辑门的功能。

习题4.1图解:B A B A B A B A B A F ⊕=+=+= 该电路实现异或门的功能4.2分析图所示电路,写出输出函数F 。

习题4.2图 解:[]B A B BB A F ⊕=⊕⊕⊕=)(4.3已知图示电路及输入A 、B 的波形,试画出相应的输出波形F ,不计门的延迟.习题4.3图解:B A B A B A AB B AB A AB B AB A F ⊕=∙=∙∙∙=∙∙∙=4.4由与非门构成的某表决电路如图所示。

其中A 、B 、C 、D 表示4个人,L=1时表示决议通过。

(1) 试分析电路,说明决议通过的情况有几种。

(2) 分析A 、B 、C 、D 四个人中,谁的权利最大。

习题4.4图解:(1)ABD BC CD ABD BC CD L ++=∙∙=B AC & && & D L B A =1 =1 =1FF A B & && & & F B AABCD L ABCD L 0000 0001 0010 0011 0100 0101 0110 01110 0 0 1 0 0 1 11000 1001 1010 1011 1100 1101 1110 11110 0 0 1 0 1 1 1(3)根据真值表可知,四个人当中C 的权利最大。

4.5分析图所示逻辑电路,已知S 1﹑S 0为功能控制输入,A ﹑B 为输入信号,L 为输出,求电路所具有的功能。

习题4.5图解:(1)011011)(S S B S A S S B S A L ⊕⊕+⊕=⊕⊕∙⊕= (2)S 1S 0 L 00 01 10 11A+BB A +ABAB4.6试分析图所示电路的逻辑功能。

习题4.6图解:(1)ABC C B A F )(++=A BS 1S 0L =1 =1 &=1& & & & &FA BC电路逻辑功能为:“判输入ABC 是否相同”电路。

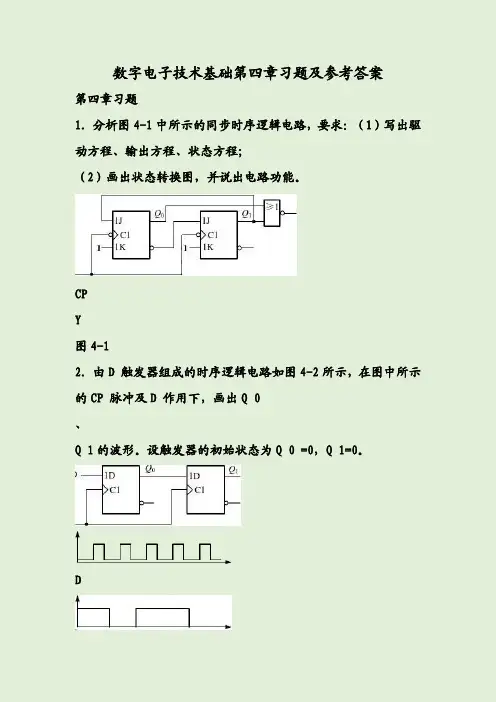

数字电子技术基础第四章习题及参考答案第四章习题1.分析图4-1中所示的同步时序逻辑电路,要求:(1)写出驱动方程、输出方程、状态方程;(2)画出状态转换图,并说出电路功能。

CPY图4-12.由D触发器组成的时序逻辑电路如图4-2所示,在图中所示的CP脉冲及D作用下,画出Q0、Q1的波形。

设触发器的初始状态为Q0=0,Q1=0。

D图4-23.试分析图4-3所示同步时序逻辑电路,要求:写出驱动方程、状态方程,列出状态真值表,画出状态图。

CP图4-34.一同步时序逻辑电路如图4-4所示,设各触发器的起始状态均为0态。

(1)作出电路的状态转换表;(2)画出电路的状态图;(3)画出CP作用下Q0、Q1、Q2的波形图;(4)说明电路的逻辑功能。

图4-45.试画出如图4-5所示电路在CP波形作用下的输出波形Q1及Q0,并说明它的功能(假设初态Q0Q1=00)。

CPQ1Q0CP图4-56.分析如图4-6所示同步时序逻辑电路的功能,写出分析过程。

Y图4-67.分析图4-7所示电路的逻辑功能。

(1)写出驱动方程、状态方程;(2)作出状态转移表、状态转移图;(3)指出电路的逻辑功能,并说明能否自启动;(4)画出在时钟作用下的各触发器输出波形。

CP图4-78.时序逻辑电路分析。

电路如图4-8所示:(1)列出方程式、状态表;(2)画出状态图、时序图。

并说明电路的功能。

1C图4-89.试分析图4-9下面时序逻辑电路:(1)写出该电路的驱动方程,状态方程和输出方程;(2)画出Q1Q0的状态转换图;(3)根据状态图分析其功能;1B图4-910.分析如图4-10所示同步时序逻辑电路,具体要求:写出它的激励方程组、状态方程组和输出方程,画出状态图并描述功能。

1Z图4-1011.已知某同步时序逻辑电路如图4-11所示,试:(1)分析电路的状态转移图,并要求给出详细分析过程。

(2)电路逻辑功能是什么,能否自启动?(3)若计数脉冲f CP频率等于700Hz,从Q2端输出时的脉冲频率是多少?CP图4-1112.分析图4-12所示同步时序逻辑电路,写出它的激励方程组、状态方程组,并画出状态转换图。

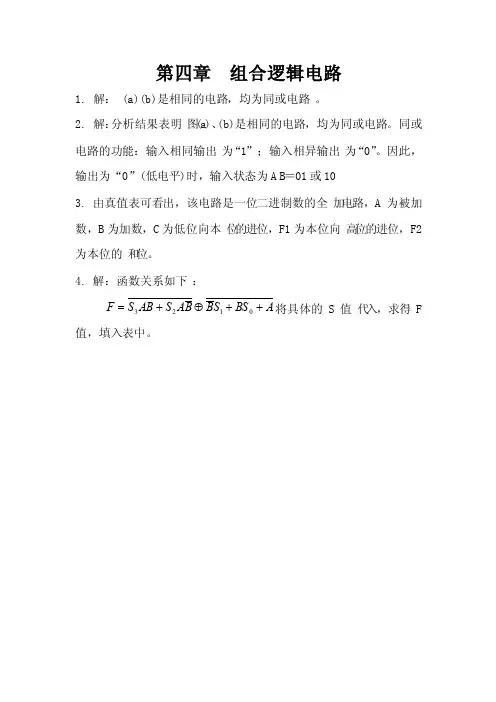

第四章组合逻辑电路1. 解: (a)(b)是相同的电路,均为同或电路。

2. 解:分析结果表明图(a)、(b)是相同的电路,均为同或电路。

同或电路的功能:输入相同输出为“1”;输入相异输出为“0”。

因此,输出为“0”(低电平)时,输入状态为AB=01或103. 由真值表可看出,该电路是一位二进制数的全加电路,A为被加数,B为加数,C为低位向本位的进位,F1为本位向高位的进位,F2为本位的和位。

4. 解:函数关系如下:SF++⊕=+ABSABS BABS将具体的S值代入,求得F 312值,填入表中。

A A FB A B A B A A F B A B A A F A A F AB AB F B B A AB F AB B A B A B A AB F B A A AB F B A B A B A F B A AB AB B A B A F B B A B A B A B A B A B A F AB BA A A B A A B A F F B A B A F B A B A F A A F S S S S =⊕==+==+⊕===+⊕===⊕===⊕===+⊕===+=+⊕===⊕==+==⊕==Θ=+=+⊕===+++=+⊕===+=⊕===⊕==+=+⊕==+=+⊕===⊕==01111111011010110001011101010011000001110110)(01010100101001110010100011000001235. (1)用异或门实现,电路图如图(a)所示。

(2) 用与或门实现,电路图如图(b)所示。

6. 解因为一天24小时,所以需要5个变量。

P变量表示上午或下午,P=0为上午,P=1为下午;ABCD表示时间数值。

真值表如表所示。

利用卡诺图化简如图(a)所示。

化简后的函数表达式为D C A P D B A P C B A P A P DC A PD B A P C B A P A P F =+++=用与非门实现的逻辑图如图(b )所示。

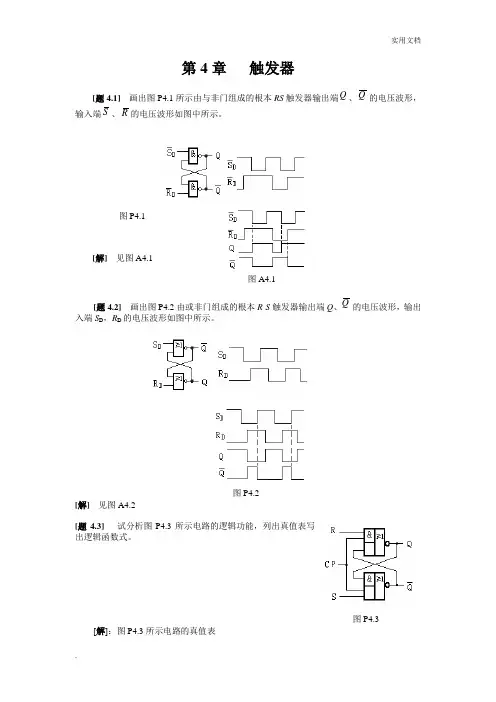

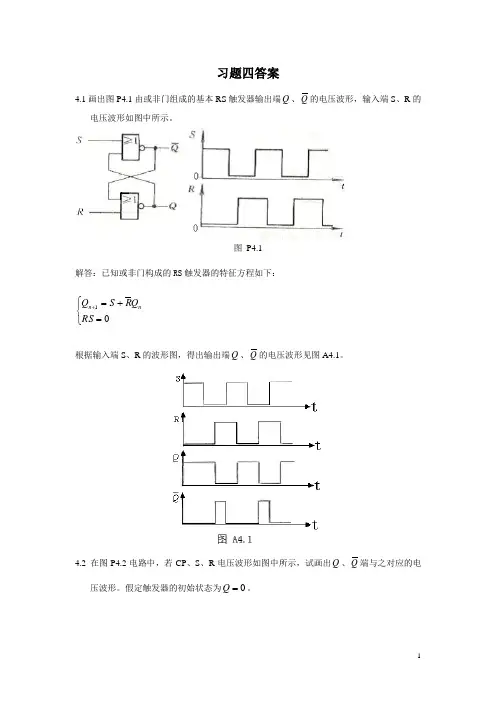

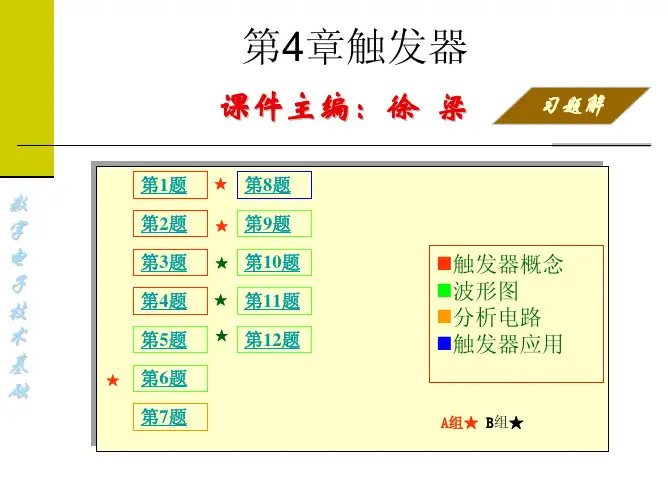

第4章触发器[题4.1]画出图P4.1所示由与非门组成的根本RS触发器输出端Q、Q的电压波形,输入端S、R的电压波形如图中所示。

图P4.1[解]见图A4.1图A4.1[题4.2]画出图P4.2由或非门组成的根本R-S触发器输出端Q、Q的电压波形,输出入端S D,R D的电压波形如图中所示。

图P4.2[解]见图A4.2[题4.3]试分析图P4.3所示电路的逻辑功能,列出真值表写出逻辑函数式。

图P4.3 [解]:图P4.3所示电路的真值表S R Q n Q n+1 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 0* 1 110*由真值表得逻辑函数式 01=+=+SR Q R S Q nn[题4.4] 图P4.4所示为一个防抖动输出的开关电路。

当拨动开关S 时,由于开关触点接触瞬间发生振颤,D S 和D R 的电压波形如图中所示,试画出Q 、Q 端对应的电压波形。

图P4.4[解] 见图A4.4图A4.4[题4.5] 在图P4.5电路中,假设CP 、S 、R 的电压波形如图中所示,试画出Q 和Q 端与之对应的电压波形。

假定触发器的初始状态为Q =0。

图P4.5[解]见图A4.5图A4.5[题4.6]假设将同步RS触发器的Q与R、Q与S相连如图P4.6所示,试画出在CP 信号作用下Q和Q端的电压波形。

己知CP信号的宽度t w = 4 t Pd 。

t Pd为门电路的平均传输延迟时间,假定t Pd≈t PHL≈t PLH,设触发器的初始状态为Q=0。

图P4.6图A4.6[解]见图A4.6[题4.7]假设主从结构RS触发器各输入端的电压波形如图P4.7中所给出,试画Q、Q端对应的电压波形。

设触发器的初始状态为Q=0。

图P4.7[解] 见图A4.7图A4.7[题4.8]假设主从结构RS触发器的CP、S、R、DR各输入端的电压波形如图P4.8所示,1DS。

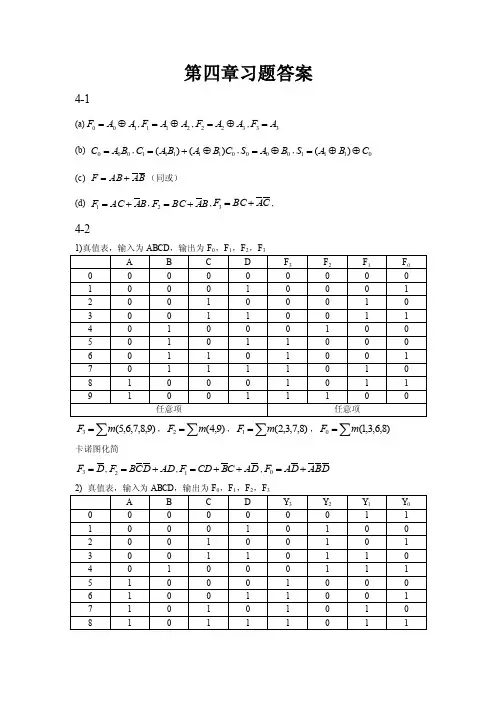

第四章习题答案4-1(a)100A A F ⊕=,211A A F ⊕=,322A A F ⊕=,33A F =(b) 000B A C =,011111)()(C B A B A C ⊕+=,000B A S ⊕=,0111)(C B A S ⊕⊕= (c) B A AB F +=(同或)(d) B A AC F +=1,B A BC F +=2,C A BC F+=3, 4-2,F ,F ,F∑=)9,8,7,6,5(3m F ,∑=)9,4(2m F ,∑=)8,7,3,2(1m F ,∑=)8,6,3,1(0m F卡诺图化简D F =3,AD D C B F +=2,D A C B CD F ++=1,D B A D A F +=0,F ,F ,F∑=)9,8,7,6,5(3m Y ,∑=)9,4,3,2,1(2m Y , ∑=)8,7,4,3,0(1m Y ,∑=)8,6,4,2,0(0m Y用4-16线译码器实现987653F F F F F Y =,943212F F F F F Y =,874301F F F F F Y =,864200F F F F F Y =4-3将四片138译码器级联,ST 接高电平,ST 接低电平,ST 由译码控制3442A A ST =,3432A A ST =,3432A A ST =,3432A A ST =4-4113471347(1,3,4,7)F m m m m m F F F F ===∑ 2046046(0,4,6)F m m m m F F F ===∑4-51)一片8选1,输入A 、B 、C 分别接8选1的地址A 2,A 1,A 00,,1,17563420========D D D D D D D D D D2)两片8选1,输入A 、B 、C ,D 分别接4选1的地址012,,,A A A E1,01413121197651151084320================D D D D D D D D D D D D D D D D4-6A S SB A S S B A S S AB S S F 01010101)()(+⊕+++= A S S B A S S B A S S B S S A S S AB S S F 010*********+++++=将A S S ,,01分别接8选1的地址012,,A A A ,则输入端分别是0,1,,70635421========D D D D B D B D D D4-71) 输入A,B,C,D 分别接加法器的A 3,A 2,A 1,A 0, 加法器的B 3B 2B 1B 0=0011,CI=0 2) 输入A,B,C,D 分别接加法器的A 3,A 2,A 1,A 0, 加法器的B 3B 2B 1B 0=1101,CI=04-8假设四位被加数为ABCD ,加数为EFGH 输入A,B,C,D 分别接加法器的A 3,A 2,A 1,A 0, 加法器的B 3,B 2,B 1,B 0如下:M CI M H B M G B M F B M E B =⊕=⊕=⊕=⊕=,,,,01234-9真值表∑=)15,14,13,11,7(m F1)8选1数据选择器,将B A M ,,分别接8选1的地址012,,A A A ,则输入端分别是0,1,42107653========D D D D D C D D D2)用3-8译码器151413117151413117F F F F F m m m m m F ==4-10设三个开关分别为A,B,C ,开关的关闭为1,打开为0;灯的输出为F ,灯的亮为1,灭为0真值表C B A F =输入ABCD 分别接4-16译码器的地址段A 3,A 2,A 1,A 0 1) a 端:0158421=====D D D D D , 其余数据端接1 2) b 端:所有数据端均接1,1150=D D3) c 端:012109653======D D D D D D ,其余数据端接1 4) d 端:0158421=====D D D D D ,其余数据端接15) e 端:01514131187421=========D D D D D D D D D ,其余数据端接1 6) f 端:1150==D D ,其余数据端接07) g 端:08421====D D D D ,其余数据端接1设输出灯亮为1,灭为0真值表如下:1)4-16输入ABCD 分别接4-16译码器的地址段A 3,A 2,A 1,A 0(1) F 1端:143210=====D D D D D , 其余数据端接0 (2) F 2端:198765=====D D D D D , 其余数据端接0 (3) F3端:1151413121110======D D D D D D , 其余数据端接0 2)4位数据比较器实现用两片数据选择器,输入端ABCD 分别接两个比较器的A 3A 2A 1A 0,第一片比较器的B 3B 2B 1B 0=0101,第二片的B 3B 2B 1B 0=1001,两片的级联端0,1===<>=B A B A B A I I I ,则:B A I F <=11,B A I F >=23,212F F F =用4-16输入A 1A 0B 1B 0分别接4-16译码器的地址段A 3,A 2,A 1,A 0 (1) F 0端:1151375====D D D D , 其余数据端接0(2) F 1端:1141311976======D D D D D D , 其余数据端接0 (3) F 2端:1141110===D D D , 其余数据端接0 (4) F 3端:115=D , 其余数据端接04-141)只要把两片的B A I =直接相连就可以判断三个输入数据是否相等,假定输入为ABCD 四门课程,及格为1,不及格为0;输出F 为能否毕业,能够毕业为1,不能毕业为0。

数字电路第四章答案【篇一:数字电路答案第四章时序逻辑电路2】p=1,输入信号d被封锁,锁存器的输出状态保持不变;当锁存命令cp=0,锁存器输出q?d,q=d;当锁存命令cp出现上升沿,输入信号d被封锁。

根据上述分析,画出锁存器输出q及 q的波形如习题4.3图(c)所示。

习题4.4 习题图4.4是作用于某主从jk触发器cp、j、k、 rd及 sd 端的信号波形图,试绘出q端的波形图。

解:主从jk触发器的 rd、且为低有效。

只有当rd?sd?1 sd端为异步清零和复位端,时,在cp下降沿的作用下,j、k决定输出q状态的变化。

q端的波形如习题4.4图所示。

习题4.5 习题4.5图(a)是由一个主从jk触发器及三个非门构成的“冲息电路”,习题4.5图(b)是时钟cp的波形,假定触发器及各个门的平均延迟时间都是10ns,试绘出输出f的波形。

cpf cp100ns10nsq(a)f30ns10ns(b)(c)习题4.5图解:由习题4.5图(a)所示的电路连接可知:sd?j?k?1,rd?f。

当rd?1时,在cp下降沿的作用下,且经过10 ns,状态q发生翻转,再经过30ns,f发生状态的改变,f?q。

rd?0时,经过10ns,状态q=0。

根据上述对电路功能的分析,得到q和f的波形如习题4.5图(c)所示。

习题4.6 习题4.6图(a)是一个1检出电路,图(b)是cp及j端的输入波形图,试绘出 rd端及q端的波形图(注:触发器是主从触发器,分析时序逻辑图时,要注意cp=1时主触发器的存储作用)。

cpj(a)qd(c)cp j(b)习题图解:分析习题4.6图(a)的电路连接:sd?1,k?0,rd?cp?q;分段分析习题4.6图(b)所示cp及j端信号波形。

(1)cp=1时,设q端初态为0,则rd?1。

j信号出现一次1信号,即一次变化的干扰,且k=0,此时q端状态不会改变;(2)cp下降沿到来,q端状态变为1,rd?cp,此时cp=0,异步清零信号无效;(3)cp出现上升沿,产生异步清零信号,使q由1变为0,在很短的时间里 rd又恢复到1;(4)同理,在第2个cp=1期间,由于j信号出现1信号,在cp下降沿以及上升沿到来后,电路q端和 rd端的变化与(2)、(3)过程的分析相同,其波形如习题4.6图(c)所示。

第四章组合逻辑电路1. 解: (a)(b)是相同的电路,均为同或电路。

2. 解:分析结果表明图(a)、(b)是相同的电路,均为同或电路。

同或电路的功能:输入相同输出为“1”;输入相异输出为“0”。

因此,输出为“0”(低电平)时,输入状态为AB=01或103. 由真值表可看出,该电路是一位二进制数的全加电路,A为被加数,B为加数,C为低位向本位的进位,F1为本位向高位的进位,F2为本位的和位。

4. 解:函数关系如下:ABSF+⊕=++ABSSSABB将具体的S值代入,求得F 312值,填入表中。

A A FB A B A B A A F B A B A A F A A F AB AB F B B A AB F AB B A B A B A AB F B A A AB F B A B A B A F B A AB AB B A B A F B B A B A B A B A B A B A F AB BA A A B A A B A F F B A B A F B A B A F A A F S S S S =⊕==+==+⊕===+⊕===⊕===⊕===+⊕===+=+⊕===⊕==+==⊕==Θ=+=+⊕===+++=+⊕===+=⊕===⊕==+=+⊕==+=+⊕===⊕==01111111011010110001011101010011000001110110)(01010100101001110010100011000001235. (1)用异或门实现,电路图如图(a)所示。

(2) 用与或门实现,电路图如图(b)所示。

6. 解因为一天24小时,所以需要5个变量。

P变量表示上午或下午,P=0为上午,P=1为下午;ABCD表示时间数值。

真值表如表所示。

利用卡诺图化简如图(a)所示。

化简后的函数表达式为D C A P D B A P C B A P A P DC A PD B A P C B A P A P F =+++=用与非门实现的逻辑图如图(b)所示。

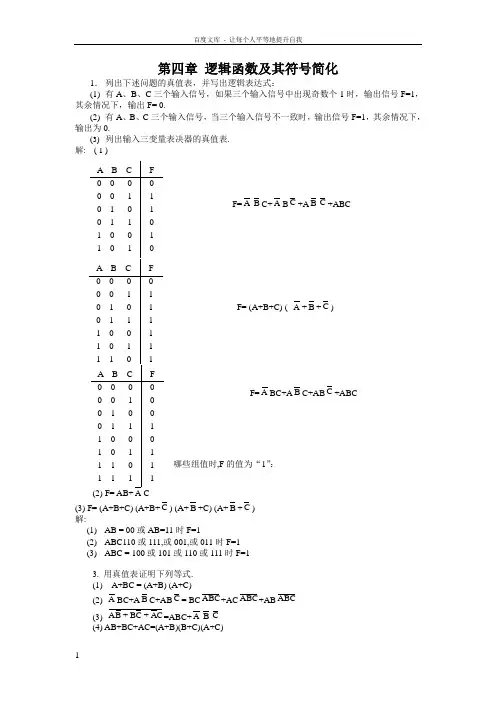

第四章逻辑函数及其符号简化1.列出下述问题的真值表,并写出逻辑表达式:(1)有A、B、C三个输入信号,如果三个输入信号中出现奇数个1时,输出信号F=1,其余情况下,输出F= 0.(2)有A、B、C三个输入信号,当三个输入信号不一致时,输出信号F=1,其余情况下,输出为0.(3)列出输入三变量表决器的真值表.解: ( 1 )F=A B C+A B C+A B C+ABC( 2 )F= (A+B+C) ( A+B+C)( 3 )F=A BC+A B C+AB C+ABC2. 对下列函数指出变量取哪些组值时,F的值为“1”:(1) F= AB+A B (2) F= AB+A C(3) F= (A+B+C) (A+B+C ) (A+B +C) (A+B +C ) 解:(1) AB = 00或AB=11时F=1(2) ABC110或111,或001,或011时F=1 (3) ABC = 100或101或110或111时F=13. 用真值表证明下列等式. (1) A+BC = (A+B) (A+C)(2) A BC+A B C+AB C = BC ABC +AC ABC +AB ABC (3) C A +C B +B A =ABC+A B C (4) AB+BC+AC=(A+B)(B+C)(A+C) (5) ABC+A +B +C =1 证: ( 1 ) ( 2 )( 3 )( 4 ) ( 5 )4. 直接写出下列函数的对偶式F ′及反演式F 的函数表达式. (1) F= [A B (C+D)][B C D +B (C +D)] (2) F= A BC + (A +B C ) (A+C) (3) F= AB+CD +E +D +E C +D +BC (4) F=D +B A •B A +C 解:(1) F`= [A +B+CD]+[(B+C +D )(•B+C D]]F = [A+B +C D ]+[(B +C+D)(•B +C D ]](2) F`= (A+C +B )]AC )C +B (•A [•F = (A +C +B )]C A +)C +B (•A [•(3) F`=)B +A (•C +D •)B +A (F =)B +A (•C +D •)B +A (5. 若已知x+y = x+z ,问y = z 吗?为什么? 解:y 不一定等于z,因为若x=1时,若y=0,z=1,或y=1,z=0,则x+y = x+z = 1,逻辑或的特点,有一个为1则为1。

习题44-1 分析图P4-1所示的各组合电路,写出输出函数表达式,列出真值表,说明电路的逻辑功能。

解:图(a ):1F AB =;2F A B =e ;3F AB = 真值表如下表所示: A B 1F2F3F0 0 0 1 0 0 1 0 0 1 1 0 1 0 0 111其功能为一位比较器。

A>B 时,11F =;A=B 时,21F =;A<B 时,31F = 图(b ):12F AB AB F AB =+=; 真值表如下表所示: A B 1F2F功能:一位半加器,1F 为本位和,2F 为进位。

图(c ):1(0,3,5,6)(1,2,4,7)F M m ==∑∏2(0,1,2,4)(3,5,6,7)F M m ==∑∏真值表如下表所示:功能:一位全加器,1F 为本位和,2F 为本位向高位的进位。

图(d ):1F AB =;2F A B =e ;3F AB =功能:为一位比较器,A<B 时,1F =1;A=B 时,2F =1;A>B 时,3F =14-2 分析图P4-2所示的组合电路,写出输出函数表达式,列出真值表,指出该电路完成的逻辑功能。

解:该电路的输出逻辑函数表达式为:100101102103F A A x A A x A A x A A x =+++因此该电路是一个四选一数据选择器,其真值表如下表所示:1A0AF0 0 0x 0 1 1x 1 0 2x 1 13x4-3 图P4-3是一个受M 控制的代码转换电路,当M =1时,完成4为二进制码至格雷码的转换;当M =0时,完成4为格雷码至二进制的转换。

试分别写出0Y ,1Y ,2Y ,3Y 的逻辑函数的表达式,并列出真值表,说明该电路的工作原理。

解:该电路的输入为3x 2x 1x 0x ,输出为3Y 2Y 1Y 0Y 。

真值表如下: 3x2x1x0x3Y2Y1Y0YM=10 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 1 0 0 1 1 0 0 1 0 0 1 0 0 0 1 1 0 0 1 0 1 0 1 1 1 0 1 1 0 0 1 0 1 01 1 0 0 1 0 0 M=0 1 0 0 0 1 1 1 1 1 0 0 1 1 1 1 0 1 0 1 0 1 1 0 0 1 0 1 1 1 1 0 1 1 1 0 0 1 0 0 0 1 1 0 1 1 0 0 1 1 1 1 0 1 0 1 1 111111由此可得:1M =当时,33232121010Y x Y x x Y x x Y x x =⎧⎪=⊕⎪⎨=⊕⎪⎪=⊕⎩ 完成二进制至格雷码的转换。