北航电子电路设计数字部分实验报告

- 格式:docx

- 大小:1008.88 KB

- 文档页数:31

《电子电路设计--模拟部分》实验一:共射放大器分析与设计1.实验目的:(1)进一步了解Multisim的各项功能,熟练掌握其使用方法,为后续课程打好基础。

(2)通过使用Multisim来仿真电路,测试如图1所示的单管共射放大电路的静态工作点、电压放大倍数、输入电阻和输出电阻,并观察静态工作点的变化对输出波形的影响。

(3)加深对放大电路工作原理的理解和参数变化对输出波形的影响。

(4)观察失真现象,了解其产生的原因。

图12.实验步骤:(1)请对该电路进行直流工作点分析,进而判断管子的工作状态。

Ub=2.96644mV Uc=9.08733mV Ue=2.34087mV因为Ub>Ue,Uc>Ub,所以工作在放大区。

(2)请利用软件提供的各种测量仪表测出该电路的输入电阻。

I=1.298uA U=7.692mV R=5.926KΩ(3)请利用软件提供的各种测量仪表测出该电路的输出电阻。

I=1.298uA U=7.692mV R=5.926KΩ(4)请利用软件提供的各种测量仪表测出该电路的幅频、相频特性曲线。

(5)请利用交流分析功能给出该电路的幅频、相频特性曲线。

(6)请分别在30Hz、1KHz、100KHz、4MHz和100MHz这5个频点利用示波器测出输入和输出的关系,并仔细观察放大倍数和相位差。

30Hz如图输入峰峰值26.453mV 输出峰峰值38.592mV 相位差20度左右1KHz如图输入峰峰值21.731mV 输出峰峰值213.626mV 相位差180度100KHz如图输入峰峰值21.421mV 输出峰峰值213.181mV 相位差180度4MHz如图输入峰峰值10.381mV 输出峰峰值104.492mV 相位差180度100MHz如图输入峰峰值529.081uV 输出峰峰值4.525mV 相位差150度数据分析:由数据可以看到,频率较低时,放大倍数较小;在中间频率段放大倍数较高,并能够维持稳定;而当频率超过一定值时,放大倍数下降。

实验六光电池的应用——光强计一.实验目的:1.了解硅光电池的基本应用。

二.实验原理:由光电池将待测的光信号转换为电信号,将电信号通过处理系统进行放大、滤波、细分,并从这些信号中提取信息。

然后将此类信息转化为所需要的格式,最后输送到显示器中。

三.实验所需部件:光电池、光强测试单元、数字电压表四.实验步骤:1.按照仪器面板所示,将“光电池”接入“光强测试单元”的“光电池入”两端,输出Vo 接数字电压表。

2.确认接线无误后,开启仪器电源,光电池在无光照时,电压输出基本为零。

3.选用高亮度卤素灯,按照从“弱-强”仔细调节光源电位器取得多种光照度,查看光电池在相对光照度为“弱光”到逐步增强的电压输出情况。

观察两个发光二极管不亮、稍亮、两个都很亮,这样就形成了一个简易的光强计。

4.更换另外一支光电池,重复上面的操作。

五.实验现象:按照从“弱-强”调节光源电位器取得多种光照度,观察到光电池在相对光照度为“弱光”到逐步增强时,两个发光二极管不亮、稍亮、两个都很亮的实验现象,结果如下图所示,实验分析:因为随着光照强度增加,光电流增大,所以发光二极管的功率增大,亮度变亮。

图1 两个二极管不亮图2 两个二极管稍亮图3 两个二极管都很亮更换另一支光电池,重复上面的操作时,所得到的结果一致。

六.思考题:1.如何将此电路改造成可更细分光照强度的光强计?答:在本实验中,是根据两个发光二级管的亮度变化,从而可判断出光照强度的强弱变化,其中共观察到两个光电二极管有三个发光状态,分别为两个光电二极管不亮、稍亮、两个都很亮,由这三个不同的发光状态定性的判断光照强度的强弱。

为了更加细分光照强度,将此电路改造成可更细分光照强度的光强计,则将此电路改为接入保护电阻和电流表的电路,由于光照强度与光电流成线性关系,因此,光电流的大小可说明光照强度的强弱,即可通过电流表的读数来细分光照强度。

实验七热释电红外传感器特性实验一.实验目的:1.了解热释电人体红外传感器的结构和基本原理。

实验一、组合逻辑电路一、实验目的(1)熟悉集成电路的引脚排列(2)掌握TTL门电路逻辑功能的测试方法(3)掌握TTL组合逻辑电路的实际方法,完成单元功能电路的设计(4)熟悉中规模集成电路译码器、数据译码器的性能与应用(5)掌握数字电子技术实验箱的功能及使用方法二、仪器设备(1)双踪示波器1台(2)500型万用表1台(3)数字逻辑实验箱(4)74LS00(5)74LS39(6)74LS153三、用两片74LS00自拟一个三人表决电路设三输入分别为A、B、C,当两人以上同意时发光二极管亮真值表如下1 0 0 0 1 0 1 1 1 1 0 1 1 1 1 1电路图如下:运行结果如下所示。

一人按下:二人按下:三人按下:2、设计一个三输入三输出的逻辑电路真值表如下用两个数据选择器74LS153设计电路,电路图如下:红绿灯亮:黄红灯亮:绿黄灯亮:实验二、时序逻辑电路一、实验目的(1)掌握D触发器和JK触发器逻辑功能的测试方法(2)掌握74LS161功能和引脚图,设计和实现具有一定功能的时序逻辑电路,体会不同控制端在电路设计中的作用(3)了解所用总规模集成器件的性能和应用二、仪器设备(1)双踪示波器1台(2)500型万用表1台(3)数字逻辑实验箱(4)74LS74(5)74LS20(6)74LS00(7)74LS161三、实验原理与内容1、利用2片74LS74、1片74LS20和2片74LS00设计一个4人抢答器。

电路图如下:主持人未按下抢答无效:A完成抢答其他选手按下无效:抢答完成后选手松开按钮灯保持不灭:2、利用中规模计数器74LS161实现任意进制计数器(1)用预置数置0实现七进制计数器电路图如下:计数为3的图片:计数为6的图片:,.。

电子电路设计实验仪器科学与光电工程131713尧爸爸2016.4.18实验一:共射放大器分析与设计一、实验目的(1)进一步了解Multisim的各项功能,熟练掌握其使用方法,为后续课程打好基础。

(2)通过使用Multisim来仿真电路,测试如图1所示的单管共射放大电路的静态工作点、电压放大倍数、输入电阻和输出电阻,并观察静态工作点的变化对输出波形的影响。

(3)加深对放大电路工作原理的理解和参数变化对输出波形的影响。

(4)观察失真现象,了解其产生的原因。

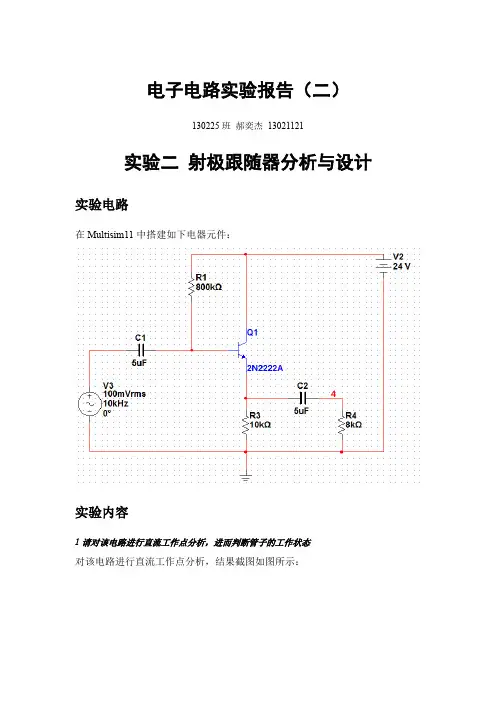

二、实验电路三、实验过程(1)请对该电路进行直流工作点分析,进而判断管子的工作状态。

操作步骤如下:Simulate-Analyses-DC Operating Point图1直流工作点为Ib=6.215uA,Ic=966.535uA,Uce=6.766V图2由上V(1)为c极;V(4)为b极;V(2)为e极由此可得Ube=0.619V,Ucb=6.14710V说明发射结正偏,集电结反偏,三极管工作在放大状态。

(2)请利用软件提供的各种测量仪表测出该电路的输入电阻。

用万用表测量输入端的电压和电流,电路图接法如图3所示(将万用表选为交流电压和交流电流档):图3测量结果为:图4经计算得到,输入电阻为3166Ω(3)请利用软件提供的各种测量仪表测出该电路的输出电阻。

这里注意一定要将输出回路断开,再接入万用表,采用测量开路电压和短路电流的方法测量输出电阻。

否则测量的是最后负载电阻的阻值。

用万用表测量输出端的电压和电流,接法如图如5所示(将万用表先后选为交流电压和交流电流档):图5测量结果为:图6经计算得到,输出电阻为2557.23Ω(4)请利用软件提供的各种测量仪表测出该电路的幅频、相频特性曲线。

采用波特测试仪如下图7搭接电路:图7该电路的幅频、相频特性曲线如图8所示图8(5)请利用交流分析功能给出该电路的幅频、相频特性曲线。

操作步骤如下:Simulate-Analyses-AC Operating,选择分析点为输出电压,得到下图9:图93dB带宽是指示数为最大值的0.707时,对应的fL和fH,图中测得最大值为19.1037V,则3dB带宽应对应纵轴为13.5063V,fH=283.1MHz,fL=79.4Hz(6)请分别在30Hz、1KHz、100KHz、4MHz和100MHz这5个频点利用示波器测出输入和输出的关系,并仔细观察放大倍数和相位差。

报告名称:电子电路设计训练数字部分学院:仪器科学与光电工程学院目录实验报告概述: (3)一、选做实验总结: (3)(1)补充练习2:楼梯灯设计 (3)(2)练习题6:用两种不同的设计方法设计一个功能相同的模块,完成4个数据的冒泡排序 (5)(3)练习题3:利用10MB的时钟,设计一个单周期形状的周期波形 (6)(4)练习题4:运用always块设计一个8路数据选择器 (6)(5)练习题5:设计一个带控制端的逻辑运算电路 (7)二、必做实验总结: (7)(1)练习一:简单组合逻辑设计 (7)(2)练习三:利用条件语句实现计数分频失序电路 (7)(3)练习四:阻塞赋值与非阻塞赋值得区别 (8)(4)练习五:用always块实现较复杂的组合逻辑电路 (8)(5)练习六:在verilog HDL中使用函数 (9)(6)练习七:在verilog HDL中使用任务 (9)(7)练习八:利用有限状态机进行时许逻辑设计 (10)三、实验总结及体会: (10)四、选作程序源代码 (11)(1)练习题3:利用10MB的时钟,设计一个单周期形状的周期波形 (11)(2)练习题4:运用always块设计一个8路数据选择器 (12)(3)练习题5:设计一个带控制端的逻辑运算电路 (13)(4)练习题6:用两种不同的设计方法设计一个功能相同的模块,完成4个数据的冒泡排序 (14)(5)补充练习2:楼梯灯设计 (16)图表目录Figure 1 楼梯灯任务4 (5)Figure 2 组合逻辑 (5)Figure 3 时序逻辑 (6)Figure 4 周期波形 (6)Figure 5 8路数据选择器 (6)Figure 6 逻辑运算电路 (7)Figure 7 组合逻辑设计 (7)Figure 8 计数分频时序电路 (8)Figure 9 阻塞赋值与非阻塞赋值得区别 (8)Figure 10 always块组合逻辑电路 (9)Figure 11 使用函数 (9)Figure 12 使用任务 (10)Figure 13 有限状态机 (10)电子电路设计训练(数字部分)实验报告实验报告概述:本实验报告为对四次电子电路设计训练(数字部分)实验的总结,主要包括以下四部分:第一部分为选做实验总结,主要包括每个选择实验的设计思路、运行结果、注意事项、心得体会;第二部分为必做实验总结,包括运行结果、总结、心得体会;第三部分为课程总结和体会,是对全部实验及课程的总结;第四部分为选做实验部分源代码;一、选做实验总结:(1)补充练习2:楼梯灯设计设计思路:本题给出楼梯的运行规则,并分别给与四个相应任务进行编程设计,考虑到程序的通用性及FPGA高速并行处理的优点,主要思路如下:根据运行规则(8s内和大于8s等),对每个灯的相应状态进行编程,设计时序逻辑及有限状态机;由于在总体上看,每个灯的状态变化相对独立(只有一个人上楼除外),故对每个灯编程所得到的程序代码可通用于其它灯(只需要改变相应寄存器定义即可),此即为灯控制模块,对4个不同的任务,只需设计其它部分判断逻辑,即可完成任务要求;如此设计,可大大提高程序设计效率、易用性,同时如果面对更多的灯控制需要,也可快速进行修改部署。

北航电气技术实践FPGA报告一、引言FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,广泛应用于数字电路设计和嵌入式系统中。

本报告旨在介绍北航电气技术实践课程中关于FPGA的学习和实践情况。

二、学习内容和方法在本课程中,我们学习了FPGA的基本概念、设计流程和相应的开发工具。

通过理论学习和实践操作,我们了解了FPGA的逻辑门、时序设计、硬件描述语言等基本知识,并掌握了使用Verilog HDL进行FPGA设计的方法。

三、实践项目在实践环节中,我们开展了一个基于FPGA的LED灯控制项目。

该项目要求使用FPGA设计一个电路,控制LED灯的亮灭。

通过按下按钮,可以实现LED灯的开关。

首先,我们进行了电路设计和仿真。

根据项目需求,我们设计了一个基于FPGA的计数器电路,通过每按下一次按钮,计数器就加1,当计数器的值为奇数时,LED灯亮;当计数器的值为偶数时,LED灯灭。

然后,我们使用Verilog HDL对电路进行了描述,并进行了功能仿真,以验证电路的正确性。

接着,我们进行了综合和布局布线。

通过综合,我们将Verilog HDL代码转化为逻辑门电路。

然后,我们对逻辑门电路进行布局布线,将逻辑门相互连接,形成电路板的物理布局,并进行布线优化,以提高电路的时序性能。

最后,我们进行了FPGA的烧录和调试。

将完成布局布线的电路通过JTAG接口烧录到FPGA芯片中,并使用开发板上的按钮进行了调试和验证。

通过调试,我们确保了LED灯的控制逻辑和亮灭效果的正确性。

四、实践收获与感悟通过这个FPGA实践项目,我收获了很多。

首先,我对FPGA的基本原理和设计流程有了更深入的理解。

其次,我学会了使用Verilog HDL进行FPGA设计,在实际操作中更加熟悉了FPGA开发工具的使用。

另外,我也意识到了FPGA在数字电路设计中的重要性和灵活性,它可以根据实际需求进行快速的硬件原型设计和验证。

北京航空航天大学电气实验报告FPGA实验张天130325班学号:13031220一.实验目的略二.实验要求略三.实验设备略四.实验内容略五.实验实例1.实例6-1思考题1:输出信号q3q2q1绑定接口电路的七段数码管或米字型数码管或LED点阵显示?答:思考题2:怎样修改成4位二进制减法计数器,具有清零,启动控制功能等?答:思考题3:把计数器修改成2位或更多位十进制计数功能,再用七段数码管进行显示等?答:2.实例6-2思考题:一位半加器电路采用VHDL语言实验答:library ieee;use ieee.std_logic_1164.all;use iee.std_logic_unsigned.all;entity halfadd isport (a,b;in std_logicsum,carry; out std_logic)end entity halfadd;architecture halfadd isbeginsum<=a and(not b)+b and (not a);carry<= a and b;end architecture halfadd;六.实验过程我们组做的是一个利用led点阵规律亮灭变化形成字体,并且字体产生变化,形成“自动化❤”的样子,实现图片如下图:1.实验分析:实验设计思路:本实验的设计思路是利用led灯的辉光效应,利用逐行扫描,在高频情况下就会显示所有行的亮灯,进而形成汉字,并且有时钟计数程序,当时钟数字达到规定值(本实验为111111111b)时,跳转到下一个状态,显示第二个憨子。

每个汉字的颜色由led灯决定,改led矩阵有红绿两种led灯,因此有红绿橙三种颜色显示。

2.实现过程对设计思路的实现并非一帆风顺,最初编写的时候遇到了一些问题。

首先,定义输入输出角是个繁琐的事情(需要定义40+次,每次必须手动),另外,在程序编写过程中,也出现了一些逻辑错误,对于错误,我们仔细逐条语句分析,最终解决了错误,解决过程中也加深了对FPGA的语言逻辑及硬件结构的理解。

电力电子实验报告学号姓名王天然实验一功率场效应晶体管(MOSFET)特性与驱动电路研究一.实验目的:1.熟悉MOSFET主要参数的测量方法2.掌握MOSEET对驱动电路的要求3.掌握一个实用驱动电路的工作原理与调试方法二.实验设备和仪器1.NMCL-07电力电子实验箱中的MOSFET与PWM波形发生器部分2.双踪示波器3.安培表(实验箱自带)4.电压表(使用万用表的直流电压档) 三.实验方法1.MOSFET 主要参数测试 (1)开启阀值电压V GS(th)测试开启阀值电压简称开启电压,是指器件流过一定量的漏极电流时(通常取漏极电流I D =1mA)的最小栅源极电压。

在主回路的“1”端与MOS 管的“25”端之间串入毫安表(箱上自带的数字安培表表头),测量漏极电流I D ,将主回路的“3”与“4”端分别与MOS 管的“24”与“23”相连,再在“24”与“23”端间接入电压表, 测量MOS 管的栅源电压Vgs ,并将主回路电位器RP 左旋到底,使Vgs=0。

图2-2 MOSFET实验电路将电位器RP逐渐向右旋转,边旋转边监视毫安表的读数,当漏极电流I D=1mA时的栅源电压值即为开启阀值电压V GS(th)。

读取6—7组I D、Vgs,其中I D=1mA必测,填入下表中。

I D0.2 0.5 1 5 100 200 500 (mA)Vgs2.64 2.72 2.863.04 3.50 3.63 3.89 (V)(2)跨导g FS测试双极型晶体管(GTR)通常用h FE(β)表示其增益,功率MOSFET器件以跨导g FS表示其增益。

跨导的定义为漏极电流的小变化与相应的栅源电压小变化量之比,即g FS=△I D/△V GS。

★注意典型的跨导额定值是在1/2额定漏极电流和V DS=15V下测得,受条件限制,实验中只能测到1/5额定漏极电流值,因此重点是掌握跨导的测量及计算方法。

根据上一步得到的测量数值,计算gFS=0.0038ΩI D(mA)0.2 0.5 1 5 10 100 200 500Vgs(V) 2.64 2.72 2.86 3.04 3.13 3.5 3.63 3.89g FS0.0038 0.0036 0.0222 0.0556 0.2432 0.7692 1.1538DS导通电阻定义为R DS=V DS/I D将电压表接至MOS 管的“25”与“23”两端,测量U DS,其余接线同上。

目录实验一 (2)实验二 (8)实验三 (14)实验四 (27)实验一实验目的:熟悉硬件开发流程,掌握Modelsim设计与仿真环境,学会简单组合逻辑电路、简单时序逻辑电路设计,不要求掌握综合和综合后仿真。

实验内容:必做实验:练习一、简单的组合逻辑设计练习二、简单分频时序逻辑电路的设计选做实验:选做一、练习一的练习题选做二、7段数码管译码电路练习一、简单的组合逻辑设计描述一个可综合的数据比较器,比较数据a 、b的大小,若相同,则给出结果1,否则给出结果0。

实验代码:模块源代码:module compare(equal,a,b);input a,b;output equal;assign equal=(a==b)?1:0;endmodule测试模块源代码:`timescale 1ns/1ns`include "./compare.v"module t;reg a,b;wire equal;initialbegina=0;b=0;#100 a=0;b=1;#100 a=1;b=1;#100 a=1;b=0;#100 a=0;b=0;#100 $stop;endcompare m(.equal(equal),.a(a),.b(b));endmodule实验波形练习二、简单分频时序逻辑电路的设计用always块和@(posedge clk)或@(negedge clk)的结构表述一个1/2分频器的可综合模型,观察时序仿真结果。

实验代码:模块源代码:module halfclk(reset,clkin,clkout);input clkin,reset;output clkout;reg clkout;always@(posedge clkin)beginif(!reset) clkout=0;else clkout=~clkout;endendmodule测试模块源代码:`timescale 1ns/100ps`define clkcycle 50module tt;reg clkin,reset;wire clkout;always#`clkcycle clkin=~clkin;initialbeginclkin=0;reset=1;#10 reset=0;#110 reset=1;#100000 $stop;endhalfclk m0(.reset(reset),.clkin(clkin),.clkout(clkout));endmodule练习题1:设计一个字节(8位)的比较器。

北航电力电子实验报告一、实验目的电力电子是指能够对电能进行控制、调节和变换的设备和技术。

本实验旨在通过对电力电子元件和电路的实际操作,了解电力电子的基本原理和工作特性,掌握电力电子技术的应用。

二、实验内容1.了解电力电子元件的工作原理和特性,包括二极管、晶闸管、MOSFET等。

2.使用电力电子元件搭建基本电力电子实验电路,包括电压倍增器、交流调压电路等。

3.对电力电子元件和电路进行实验调试,观察和测量电路中电压、电流等参数。

4.记录实验结果,撰写实验报告。

三、实验步骤1.根据实验要求和提供的材料,准备实验所需的电力电子元件和电路板。

2.根据实验指导书的要求,依次搭建不同的电力电子电路。

3.使用万用表、示波器等测试仪器,对电路中的电压、电流等参数进行测量和观察。

4.调试电路,观察电力电子元件的工作情况,并记录实验数据。

5.完成实验后,将实验所用的设备归还到指定位置,整理实验报告。

四、实验结果分析本实验以搭建电压倍增器为例,观察和测量了电压倍增器电路中的输入电压、输出电压和负载电流等参数。

通过实验发现,当输入电压为直流电压时,输出电压比输入电压高;当输入电压为交流电压时,输出电压也为交流电压,但其幅值大于输入电压。

此外,当负载电流增加时,电路中的电流也相应增加,但电压倍增器的输出稳定性有一定的局限性,不适用于所有场合。

五、实验总结通过本次实验,我深入了解了电力电子元件和电路的工作原理和特性,通过实际操作和测量,进一步加深了对电力电子技术的理解。

实验过程中,我掌握了搭建和调试电力电子电路的方法和技巧,提高了实际操作的能力。

同时,也意识到了电力电子技术在现代工程和生活中的广泛应用,对工程实践有着重要的意义。

在未来的学习和实践中,我将进一步探索和应用电力电子技术,为工程和生活提供更好的解决方案。

同时,也要不断学习和更新电力电子技术的知识,跟随科技的发展,不断提升自己的专业素养和技能水平。

北航电路实验报告北航电路实验报告引言北航电路实验是电子信息工程专业学生必修的一门实践课程,旨在帮助学生理解和掌握电路的基本原理和实验技巧。

本文将对北航电路实验进行详细的报告和分析,以便更好地总结和应用所学知识。

实验一:电路基础实验电路基础实验是北航电路实验的第一次实践活动,通过搭建简单的电路并测量电流和电压,学生可以对电路的基本概念和特性有一个初步的了解。

首先,我们使用面包板搭建了一个简单的电路,包括电源、电阻和电流表。

然后,我们通过改变电阻的大小,测量了电路中的电流和电压。

实验结果表明,电流与电压成正比,而电阻则影响电流的大小。

实验二:交流电路实验交流电路实验是北航电路实验的第二个实践环节,通过使用交流电源和各种电路元件,学生可以研究交流电路的特性和行为。

我们首先搭建了一个简单的交流电路,包括交流电源、电感和电容。

然后,我们测量了电路中的电流和电压,并绘制了电流和电压随时间变化的波形图。

实验结果表明,电感和电容对交流电路的行为有重要影响,可以产生滤波、延时等效果。

实验三:放大电路实验放大电路实验是北航电路实验的第三个实践环节,通过使用放大器和各种电路元件,学生可以研究电路的放大效果和信号处理。

我们首先搭建了一个简单的放大电路,包括放大器、电阻和信号源。

然后,我们输入不同幅度和频率的信号,并测量输出信号的幅度和频率。

实验结果表明,放大器可以放大输入信号的幅度,同时也会对信号的频率产生一定的影响。

实验四:滤波电路实验滤波电路实验是北航电路实验的第四个实践环节,通过使用滤波器和各种电路元件,学生可以研究电路的滤波效果和频率响应。

我们首先搭建了一个简单的滤波电路,包括滤波器、电容和电阻。

然后,我们输入不同频率的信号,并测量输出信号的幅度和相位。

实验结果表明,滤波器可以对输入信号进行频率选择,滤除不需要的频率成分。

实验五:数字电路实验数字电路实验是北航电路实验的最后一个实践环节,通过使用数字电路元件和逻辑门,学生可以研究电路的逻辑运算和数字信号处理。

电力电子技术实验报告XX:学号:1203100 5班级:12031 1实验二三相半波可控整流电路的研究一.实验目的了解三相半波可控整流电路的工作原理,研究可控整流电路在电阻负载和电阻—电感性负载时的工作。

二.实验线路及原理三相半波可控整流电路用三只晶闸管,与单相电路比拟,输出电压脉动小,输出功率大,三相负载平衡。

缺乏之处是晶闸管电流即变压器的二次电流在一个期只有1/3时间有电流流过,变压器利用率低。

实验线路见图1-5。

三.实验容1.研究三相半波可控整流电路供电给电阻性负载时的工作。

2.研究三相半波可控整流电路供电给电阻—电感性负载时的工作。

四.实验设备及仪表1.教学实验台主控制屏2.NMCL—33组件3.NMEL—03组件4.二踪示波器5.万用表五.考前须知1.整流电路与三相电源连接时,一定要注意相序。

2.整流电路的负载电阻不宜过小,应使Id不超过0.8A,同时负载电阻不宜过大,保证Id 超过0.1A,防止晶闸管时断时续。

3.正确使用示波器,防止示波器的两根地线接在非等电位的端点上,造成短路事故。

六.实验法按图接线,未上主电源之前,检查晶闸管的脉冲是否正常。

〔1〕用示波器观察MCL-33的双脉冲观察,应有间隔均匀,幅度一样的双脉冲〔2〕检查相序,用示波器观察“1〞,“2〞单脉冲观察,“1〞脉冲超前“2〞脉冲600,那么相序正确,否那么,应调整输入电源。

〔3〕用示波器观察每只晶闸管的控制极,阴极,应有幅度为1V—2V的脉冲。

2.研究三相半波可控整流电路供电给电阻性负载时的工作〔a〕合上主电源,接上电阻性负载:改变控制电压Uct,观察在不同触发移相角α时,可控整流电路的输出电压Ud=f〔t〕与输导通角30°60°90°105°120°150°Uct/V 4.1 2 1 0.7 0.2 0Ud/V 131.9 86.0 41.4 24.7 11.3 0.0Id/A 0.42 0.30 0.15 0.10 0.05 0〔bUd=f〔t〕电阻负载i d= f〔t〕:〔与U d= f〔t〕一样,只是小R倍〕〔c〕求取三相半波可控整流电路的输入—输出特性Ud/U2=f〔α〕。

电子电路设计数字部分实验报告、学院:姓名:实验一简单组合逻辑设计(实验内容描述一个可综合的数据比较器,比较数据a 、b的大小,若相同,则给出结果1,否则给出结果0。

实验仿真结果实验代码主程序module compare(equal,a,b);input[7:0] a,b;>output equal;assign equal=(a>b)1:0;endmodule测试程序module t;reg[7:0] a,b;reg clock,k;?wire equal;initialbegina=0;b=0;clock=0;k=0;end,always #50 clock = ~clock;always @ (posedge clock)begina[0]={$random}%2;a[1]={$random}%2;a[2]={$random}%2;a[3]={$random}%2;a[4]={$random}%2;#a[5]={$random}%2;a[6]={$random}%2;a[7]={$random}%2;b[0]={$random}%2;b[1]={$random}%2;b[2]={$random}%2;b[3]={$random}%2;b[4]={$random}%2;、b[5]={$random}%2;b[6]={$random}%2;b[7]={$random}%2;endinitialbegin #100000 $stop;endcompare m(.equal(equal),.a(a),.b(b)); endmodule%实验二简单分频时序逻辑电路的设计实验内容用always块和@(posedge clk)或@(negedge clk)的结构表述一个1/2分频器的可综合模型,观察时序仿真结果。

实验仿真结果实验代码主程序module half_clk(reset,clk_in,clk_out);^input clk_in,reset;output clk_out;reg clk_out;always@(negedge clk_in)beginif(!reset)clk_out=0;;elseclk_out=~clk_out;endendmodule测试程序`timescale 1ns/100ps`define clk_cycle 50;module top;reg clk,reset;wire clk_out;always #`clk_cycle clk=~clk;initialbegin!clk=0;reset=1;#10 reset=0;#110 reset=1;#100000 $stop;endhalf_clk m0(.reset(reset),.clk_in(clk),.clk_out(clk_out));-endmodule实验三利用条件语句实现计数分频时序电路实验内容利用10MHz的时钟,设计一个单周期形状的周期波形。

实验仿真结果实验代码主程序'module fdivision(RESET,F10M,out); input F10M,RESET;output out;reg out;reg[7:0] i;always @(posedge F10M)if(!RESET)begin{out<=0;i<=0;endelse if(i==2||i==3)beginout=~out;i<=i+1;end(else if(i==5)i<=1;elsei<=i+1;endmodule测试程序`timescale 1ns/100ps(module division_top;reg F10M,RESET;wire out;always #50 F10M=~F10M;initialbeginRESET=1;&F10M=0;#90 RESET=0;#100 RESET=1;#10000 $stop;endfdivision fdivision(.RESET(RESET),.F10M(F10M),.out(out));endmodule实验四阻塞赋值与非阻塞赋值的区别:实验内容比较四种不同的写法,观察阻塞与非阻塞赋值的区别。

Blocking:always @(posedge clk)beginb=a;c=b;end—Blocking1:always @(posedge clk)beginc=b;b=a;end`Blocking2:always @(posedge clk) b=a; always @(posedge clk) c=b;non_Blocking:always@(posedge clk)beginb<=a;!c<=b;End实验仿真结果实验代码主程序module blocking(clk,a,b,c); output[3:0] b,c;】input[3:0] a;input clk;reg[3:0] b,c;always @(posedge clk)beginb=a;c=b;end…endmodule测试部分`timescale 1 ns/100 ps`include "./"`include "./"`include "./"`include "./"%module compareTop;wire[3:0]b11,c11,b12,c12,b13,c13,b2,c2; reg[3:0]a;reg clk;initialbeginclk=0;}forever#50 clk=~clk;endinitialbegina=4'h3;$display("%d",a);#100 a=4'h7;$display("%d",a);`#100 a=4'hf;$display("%d",a);#100 a=4'ha;$display("%d",a);#100 a=4'h2;$display("%d",a);#100 $stop;end"blocking blocking(clk,a,b11,c11);blocking1 blocking1(clk,a,b12,c12);blocking2 blocking2(clk,a,b13,c13);non_blocking non_blocking(clk,a,b2,c2);endmodule实验五用always块实现较复杂的组合逻辑实验目的运用always块设计一个8路数据选择器。

要求:每路输入数据与输出数据均为4位2进制数,当选择开关(至少3位)或输入数据发生变化时,输出数据也相应地变化。

…实验仿真结果实验代码主程序module alu(out,opcode,a1,a2,a3,a4,a5,a6,a7,a8);output[3:0] out;reg[3:0] out;input[3:0] a0,a1,a2,a3,a4,a5,a6,a7;<input[2:0] opcode;always@(opcode or a1 or a2 or a3 or a4 or a5 or a6 or a7 or a0) begincase(opcode)3'd0: out=a0;3'd1: out=a1;3'd2: out=a2;3'd3: out=a3;…3'd4: out=a4;3'd5: out=a5;3'd6: out=a6;3'd7: out=a7;default:out=4'b0000;endcaseendendmodule;测试程序`timescale 1ns/1ns`include "./"module alutext;wire[3:0] out;reg[3:0] a1,a2,a3,a4,a5,a6,a7,a8;reg[2:0] opcode;~initialbegina1={$random}%16;a2={$random}%16;a3={$random}%16;a4={$random}%16;a5={$random}%16;a6={$random}%16;(a7={$random}%16;a8={$random}%16;repeat(100)begin#100 opcode={$random}%8;a1={$random}%16;a2={$random}%16;a3={$random}%16;}a4={$random}%16;a5={$random}%16;a6={$random}%16;a7={$random}%16;a8={$random}%16;end#100 $stop;end】alu alu(out,opcode,a1,a2,a3,a4,a5,a6,a7,a8);endmodule实验六在 Verilog HDL中使用函数实验目的设计一个带控制端的逻辑运算电路,分别完成正整数的平方、立方和最大数为5的阶乘运算。

实验仿真结果—实验代码主程序module tryfunct(clk,n,result1,result2,result3,reset); output[31:0]result1,result2,result3;input[3:0]n;input reset,clk;reg[31:0]result1,result2,result3;always@(posedge clk);beginif(!reset)beginresult1<=0;result2<=0;result3<=0;endelse·beginresult1<=fun1(n);result2<=fun2(n);result3<=fun3(n);endendfunction[31:0]fun1;¥input[3:0]operand;fun1=operand*operand;endfunctionfunction[31:0]fun2;input[3:0]operand;beginfun2=operand*operand;[fun2=operand*fun2;endendfunctionfunction[31:0]fun3;input[3:0]operand;reg[3:0]index;begin]fun3=1;if(operand<11)for(index=2;index<=operand;index=index+1)fun3=index*fun3;elsefor(index=2;index<=10;index=index+1)fun3=index*fun3;end、endfunctionendmodule测试程序`include"./"`timescale 1ns/100psmodule tryfunctTop;®[3:0] n,i;reg reset,clk;wire[31:0]result1,result2,result3;initialbeginclk=0;n=0;reset=1;`#100 reset=0;#100 reset=1;for(i=0;i<=15;i=i+1)begin#200 n=i;end#100 $stop;end;always#50 clk=~clk;tryfunctm(.clk(clk),.n(n),.result1(result1),.result2(result2),.result3(result3),.reset(reset));endmodule实验七在Verilog HDL中使用任务(task)实验目的用两种不同方法设计一个功能相同的模块,该模块能完成四个8位2进制输入数据的冒泡排序。